Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$= K \in$

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp306a-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

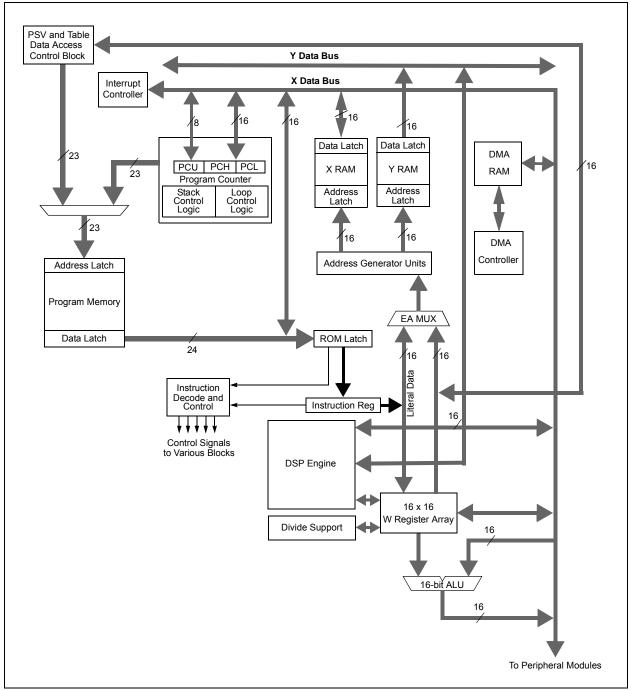

#### FIGURE 3-1: dsPIC33FJXXXGPX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

### 4.2.7 SOFTWARE STACK

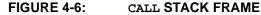

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-35 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file reg-

ister or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where:

Operand 1 is always a working register (i.e., the addressing mode can only be register direct) which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- Register Indirect

- Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

| Note: | Not all instructions support all the  |

|-------|---------------------------------------|

|       | addressing modes given above.         |

|       | Individual instructions may support   |

|       | different subsets of these addressing |

|       | modes.                                |

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

### TABLE 4-35: FUNDAMENTAL ADDRESSING MODES SUPPORTED

### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the Addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (Register Offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following Addressing modes are supported by move and accumulator instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not all instructions support all the                                         |

|-------|------------------------------------------------------------------------------|

|       | Addressing modes given above.                                                |

|       | Individual instructions may support<br>different subsets of these Addressing |

|       | modes.                                                                       |

### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and

SR: CPU STATUS REGISTER<sup>(1)</sup>

| R-0                  | R-0                  | R/C-0                | R/C-0 | R-0                                | R/C-0 | R -0  | R/W-0 |  |

|----------------------|----------------------|----------------------|-------|------------------------------------|-------|-------|-------|--|

| OA                   | OB                   | SA                   | SB    | OAB                                | SAB   | DA    | DC    |  |

| bit 15               |                      | ÷                    |       |                                    |       |       | bit 8 |  |

|                      |                      |                      |       |                                    |       |       |       |  |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N                                  | OV    | Z     | С     |  |

| bit 7                |                      |                      |       |                                    |       |       | bit 0 |  |

|                      |                      |                      |       |                                    |       |       |       |  |

| Legend:              |                      |                      |       |                                    |       |       |       |  |

| C = Clear only bit   |                      | R = Readable bit     |       | U = Unimplemented bit, read as '0' |       |       |       |  |

| S = Set only bit     |                      | W = Writable         | bit   | -n = Value at POR                  |       |       |       |  |

|                      |                      |                      |       |                                    |       |       |       |  |

x = Bit is unknown

bit 7-5

1' = Bit is set

**REGISTER 7-1:**

### IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

'0' = Bit is cleared

- 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0                                                                  | U-0          | U-0                | R/W-0            | R/W-0                              | R-0   | R-0     | R-0   |  |

|----------------------------------------------------------------------|--------------|--------------------|------------------|------------------------------------|-------|---------|-------|--|

|                                                                      | _            |                    | US               | EDT                                |       | DL<2:0> |       |  |

| bit 15                                                               |              |                    |                  |                                    |       |         | bit 8 |  |

|                                                                      |              |                    |                  |                                    |       |         |       |  |

| R/W-0                                                                | R/W-0        | R/W-1              | R/W-0            | R/C-0                              | R/W-0 | R/W-0   | R/W-0 |  |

| SATA                                                                 | SATB         | SATDW              | ACCSAT           | IPL3 <sup>(2)</sup>                | PSV   | RND     | IF    |  |

| bit 7                                                                |              |                    |                  |                                    |       |         | bit 0 |  |

| Legend:                                                              |              | C = Clear onl      | y bit            |                                    |       |         |       |  |

| R = Readable bit                                                     |              | W = Writable       | bit              | -n = Value at POR '1' = Bit is set |       |         |       |  |

| 0' = Bit is cleared 'x = Bit is unknown                              |              |                    | nown             | U = Unimplemented bit, read as '0' |       |         |       |  |

|                                                                      |              |                    |                  |                                    |       |         |       |  |

| bit 3 IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup> |              |                    |                  |                                    |       |         |       |  |

|                                                                      | 1 = CPU inte | rrupt priority lev | /el is greater t | han 7                              |       |         |       |  |

|                                                                      | 0 = CPU inte | rrupt priority lev | el is 7 or less  | ;                                  |       |         |       |  |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| REGISTER 7      | '-8: IFS3: I    | INTERRUPT                                                                           | FLAG STAT       | US REGIST        | ER 3             |                 |       |  |  |  |

|-----------------|-----------------|-------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|

| U-0             | U-0             | R/W-0                                                                               | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |  |  |  |

| _               | _               | DMA5IF                                                                              | DCIIF           | DCIEIF           | _                | —               | C2IF  |  |  |  |

| bit 15          |                 |                                                                                     |                 | •                |                  |                 | bit 8 |  |  |  |

| R/W-0           | R/W-0           | R/W-0                                                                               | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| C2RXIF          | INT4IF          | INT3IF                                                                              | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |  |  |  |

| bit 7           |                 |                                                                                     |                 |                  |                  |                 | bit 0 |  |  |  |

| Legend:         |                 |                                                                                     |                 |                  |                  |                 |       |  |  |  |

| R = Readable    | bit             | W = Writable                                                                        | bit             | U = Unimple      | mented bit, read | as '0'          |       |  |  |  |

| -n = Value at I |                 | '1' = Bit is set                                                                    |                 | '0' = Bit is cle |                  | x = Bit is unkn | own   |  |  |  |

|                 |                 |                                                                                     |                 |                  |                  |                 |       |  |  |  |

| bit 15-14       | Unimplemen      | ted: Read as '                                                                      | 0'              |                  |                  |                 |       |  |  |  |

| bit 13          | DMA5IF: DM      | A Channel 5 D                                                                       | ata Transfer (  | Complete Inter   | rupt Flag Status | bit             |       |  |  |  |

|                 |                 | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

| bit 12          | DCIIF: DCI E    | vent Interrupt I                                                                    | -lag Status bit |                  |                  |                 |       |  |  |  |

|                 | 1 = Interrupt   | request has oc                                                                      | curred          |                  |                  |                 |       |  |  |  |

|                 | •               | request has no                                                                      |                 |                  |                  |                 |       |  |  |  |

| bit 11          |                 | Error Interrupt                                                                     | U               | it               |                  |                 |       |  |  |  |

|                 |                 | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

| bit 10-9        | Unimplemen      | ted: Read as '                                                                      | 0'              |                  |                  |                 |       |  |  |  |

| bit 8           | C2IF: ECAN2     | 2 Event Interrup                                                                    | ot Flag Status  | bit              |                  |                 |       |  |  |  |

|                 | •               | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

| bit 7           | C2RXIF: ECA     | AN2 Receive D                                                                       | ata Ready Int   | errupt Flag Sta  | atus bit         |                 |       |  |  |  |

|                 |                 | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

| bit 6           | •               | rnal Interrupt 4                                                                    |                 | it               |                  |                 |       |  |  |  |

|                 | 1 = Interrupt i | request has oc<br>request has no                                                    | curred          |                  |                  |                 |       |  |  |  |

| bit 5           | INT3IF: Exter   | rnal Interrupt 3                                                                    | Flag Status b   | it               |                  |                 |       |  |  |  |

|                 | •               | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

| bit 4           | -               | -                                                                                   |                 |                  |                  |                 |       |  |  |  |

|                 | 1 = Interrupt i | <b>T9IF:</b> Timer9 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                 |                  |                  |                 |       |  |  |  |

|                 | 0 = Interrupt   | request has no                                                                      | t occurred      |                  |                  |                 |       |  |  |  |

| bit 3           |                 | Interrupt Flag                                                                      |                 |                  |                  |                 |       |  |  |  |

|                 |                 | request has oc                                                                      |                 |                  |                  |                 |       |  |  |  |

| bit 2           | -               | request has no<br>2 Master Even                                                     |                 | ag Status bit    |                  |                 |       |  |  |  |

| SIL Z           |                 | request has oc                                                                      | •               | ug oluluo bit    |                  |                 |       |  |  |  |

|                 |                 | request has no                                                                      |                 |                  |                  |                 |       |  |  |  |

| bit 1           | SI2C2IF: 12C    | 2 Slave Events                                                                      | Interrupt Flag  | g Status bit     |                  |                 |       |  |  |  |

|                 |                 | request has oc                                                                      |                 |                  |                  |                 |       |  |  |  |

|                 | -               | request has no                                                                      |                 |                  |                  |                 |       |  |  |  |

| bit 0           |                 | Interrupt Flag                                                                      |                 |                  |                  |                 |       |  |  |  |

|                 |                 | request has oc<br>request has no                                                    |                 |                  |                  |                 |       |  |  |  |

|                 |                 | iequest nas no                                                                      |                 |                  |                  |                 |       |  |  |  |

### 10.0 POWER-SAVING FEATURES

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) in "dsPIC33F/PIC24H Familv the Reference Manual", which is available the site from Microchip web (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXGPX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXGPX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXGPX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into SLEEP modePWRSAV#IDLE\_MODE; Put the device into IDLE mode

| R/W-0         | R/W-0                                                       | R/W-0                                 | R/W-0   | R/W-0             | U-0              | U-0            | R/W-0                |

|---------------|-------------------------------------------------------------|---------------------------------------|---------|-------------------|------------------|----------------|----------------------|

| T5MD          | T4MD                                                        | T3MD                                  | T2MD    | T1MD              |                  | _              | DCIMD                |

| bit 15        |                                                             |                                       |         |                   |                  |                | bit 8                |

|               |                                                             |                                       |         |                   |                  |                |                      |

| R/W-0         | R/W-0                                                       | R/W-0                                 | R/W-0   | R/W-0             | R/W-0            | R/W-0          | R/W-0                |

| I2C1MD        | U2MD                                                        | U1MD                                  | SPI2MD  | SPI1MD            | C2MD             | C1MD           | AD1MD <sup>(1)</sup> |

| bit 7         |                                                             |                                       |         |                   |                  |                | bit                  |

| Legend:       |                                                             |                                       |         |                   |                  |                |                      |

| R = Readabl   | e bit                                                       | W = Writable                          | bit     | U = Unimplen      | nented bit, read | d as '0'       |                      |

| -n = Value at | POR                                                         | '1' = Bit is set                      |         | '0' = Bit is clea |                  | x = Bit is unk | nown                 |

|               |                                                             |                                       |         |                   |                  |                |                      |

| bit 15        | T5MD: Timer                                                 | 5 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                                             | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 14        | T4MD: Timer                                                 | 4 Module Disat                        | ole bit |                   |                  |                |                      |

|               | -                                                           | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 13        |                                                             | 3 Module Disat                        |         |                   |                  |                |                      |

|               | 1 = Timer3 m                                                | nodule is disable                     | ed      |                   |                  |                |                      |

|               | 0 = Timer3 m                                                | nodule is enable                      | d       |                   |                  |                |                      |

| bit 12        | -                                                           | 2 Module Disat                        |         |                   |                  |                |                      |

|               | -                                                           | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 11        | T1MD: Timer                                                 | 1 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                                             | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 10-9      | Unimplemer                                                  | ted: Read as '                        | כ'      |                   |                  |                |                      |

| bit 8         | DCIMD: DCI                                                  | Module Disable                        | e bit   |                   |                  |                |                      |

|               |                                                             | ule is disabled<br>ule is enabled     |         |                   |                  |                |                      |

| bit 7         | <b>I2C1MD:</b> I <sup>2</sup> C                             | 1 Module Disab                        | le bit  |                   |                  |                |                      |

|               |                                                             | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

| bit 6         |                                                             | T2 Module Disa                        | ble bit |                   |                  |                |                      |

|               | 1 = UART2 module is disabled<br>0 = UART2 module is enabled |                                       |         |                   |                  |                |                      |

| bit 5         |                                                             | T1 Module Disa                        |         |                   |                  |                |                      |

|               |                                                             | nodule is disabl                      |         |                   |                  |                |                      |

|               | 0 = UART1 n                                                 | nodule is enable                      | ed      |                   |                  |                |                      |

| bit 4         | SPI2MD: SP                                                  | I2 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                                             | dule is disabled                      |         |                   |                  |                |                      |

|               |                                                             | dule is enabled                       |         |                   |                  |                |                      |

| bit 3         |                                                             | 11 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                                             | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

| U-0             | U-0                                                                                                                                                  | R/W-0            | R/W-0         | r-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|

| _               | —                                                                                                                                                    | CSIDL            | ABAT          | —                 |                  | REQOP<2:0>      |       |  |  |  |

| bit 15          |                                                                                                                                                      |                  |               |                   |                  |                 | bit   |  |  |  |

| R-1             | R-0                                                                                                                                                  | R-0              | U-0           | R/W-0             | U-0              | U-0             | R/W-0 |  |  |  |

|                 | OPMODE<2:0                                                                                                                                           |                  | _             | CANCAP            | _                | _               | WIN   |  |  |  |

| bit 7           |                                                                                                                                                      |                  |               |                   |                  |                 | bit   |  |  |  |

| Legend:         |                                                                                                                                                      |                  |               |                   |                  |                 |       |  |  |  |

| R = Readable    | hit                                                                                                                                                  | W = Writable     | hit           | II = I Inimplen   | nented bit, read | 1 as 'N'        |       |  |  |  |

| -n = Value at I |                                                                                                                                                      | '1' = Bit is se  |               | '0' = Bit is clea |                  | r = Bit is Rese | erved |  |  |  |

|                 | Ölt                                                                                                                                                  | 1 Dit io oo      |               |                   |                  |                 |       |  |  |  |

| bit 15-14       | Unimplemer                                                                                                                                           | nted: Read as    | '0'           |                   |                  |                 |       |  |  |  |

| bit 13          | CSIDL: Stop                                                                                                                                          | o in Idle Mode I | oit           |                   |                  |                 |       |  |  |  |

|                 |                                                                                                                                                      |                  |               | levice enters Idl | e mode           |                 |       |  |  |  |

|                 |                                                                                                                                                      | module opera     |               |                   |                  |                 |       |  |  |  |

| bit 12          |                                                                                                                                                      | All Pending Tr   |               |                   |                  |                 |       |  |  |  |

|                 | <ul> <li>1 = Signal all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul> |                  |               |                   |                  |                 |       |  |  |  |

| bit 11          | Reserved: D                                                                                                                                          |                  |               |                   | bontou           |                 |       |  |  |  |

| bit 10-8        |                                                                                                                                                      |                  | peration Mode | bits              |                  |                 |       |  |  |  |

|                 | <b>REQOP&lt;2:0&gt;:</b> Request Operation Mode bits<br>111 = Set Listen All Messages mode                                                           |                  |               |                   |                  |                 |       |  |  |  |

|                 | 110 = Reserved - do not use                                                                                                                          |                  |               |                   |                  |                 |       |  |  |  |

|                 | 101 = Reserved - do not use                                                                                                                          |                  |               |                   |                  |                 |       |  |  |  |

|                 | 100 = Set Configuration mode                                                                                                                         |                  |               |                   |                  |                 |       |  |  |  |

|                 | 011 = Set Listen Only Mode<br>010 = Set Loopback mode                                                                                                |                  |               |                   |                  |                 |       |  |  |  |

|                 | 001 = Set Disable mode                                                                                                                               |                  |               |                   |                  |                 |       |  |  |  |

|                 | 000 <b>= Set N</b> o                                                                                                                                 | ormal Operatio   | n mode        |                   |                  |                 |       |  |  |  |

| bit 7-5         | OPMODE<2                                                                                                                                             | :0>: Operation   | Mode bits     |                   |                  |                 |       |  |  |  |

|                 | 111 = Module is in Listen All Messages mode                                                                                                          |                  |               |                   |                  |                 |       |  |  |  |

|                 | 110 = Reserved<br>101 = Reserved                                                                                                                     |                  |               |                   |                  |                 |       |  |  |  |

|                 |                                                                                                                                                      | e is in Configu  | ration mode   |                   |                  |                 |       |  |  |  |

|                 | 011 = Module is in Listen Only mode                                                                                                                  |                  |               |                   |                  |                 |       |  |  |  |

|                 |                                                                                                                                                      | e is in Loopba   |               |                   |                  |                 |       |  |  |  |

|                 | 001 = Module is in Disable mode<br>000 = Module is in Normal Operation mode                                                                          |                  |               |                   |                  |                 |       |  |  |  |

| bit 4           |                                                                                                                                                      | nted: Read as    | -             |                   |                  |                 |       |  |  |  |

| bit 3           | -                                                                                                                                                    |                  |               | Capture Event     | Enable bit       |                 |       |  |  |  |

| bit o           |                                                                                                                                                      | •                |               | nessage receive   |                  |                 |       |  |  |  |

|                 | 0 = Disable  0                                                                                                                                       |                  |               |                   |                  |                 |       |  |  |  |

| bit 2-1         | Unimplemer                                                                                                                                           | nted: Read as    | '0'           |                   |                  |                 |       |  |  |  |

| bit 0           | WIN: SFR M                                                                                                                                           | lap Window Se    | elect bit     |                   |                  |                 |       |  |  |  |

|                 | WIN: SFR Map Window Select bit<br>1 = Use filter window                                                                                              |                  |               |                   |                  |                 |       |  |  |  |

|                 | 0 = Use buffe                                                                                                                                        |                  |               |                   |                  |                 |       |  |  |  |

### REGISTER 19-1: CiCTRL1: ECAN™ CONTROL REGISTER 1

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------------|----------------------------------|---------------------------------------|------------------|------------------|-----------------|--------|

| F15M          | SK<1:0>                              | F14MS                            | <<1:0>                                | F13M             | SK<1:0>          | F12MSI          | K<1:0> |

| bit 15        |                                      | ł                                |                                       |                  |                  | ł               | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| F11M          | SK<1:0>                              | F10MS                            | <<1:0>                                | F9MS             | SK<1:0>          | F8MSK           | (<1:0> |

| bit 7         |                                      |                                  |                                       |                  |                  |                 | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| Legend:       |                                      |                                  |                                       |                  |                  |                 |        |

| R = Readable  |                                      | W = Writable I                   | bit                                   | -                | mented bit, read |                 |        |

| -n = Value at | POR                                  | '1' = Bit is set                 |                                       | '0' = Bit is cle | eared            | x = Bit is unkn | own    |

|               |                                      |                                  |                                       | ,                |                  |                 |        |

| bit 15-14     |                                      | >: Mask Source                   | e for Filter 15                       | DIT              |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 13-12     | F14MSK<1:0                           | >: Mask Source                   | e for Filter 14                       | bit              |                  |                 |        |

|               | 11 = Reserve                         | -,                               |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 11-10     | -                                    | >: Mask Source                   |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | -                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 9-8       | <b>F12MSK&lt;1:0</b><br>11 = Reserve | >: Mask Source                   | e for Filter 12                       | bit              |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | •                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 7-6       |                                      | >: Mask Source                   | e for Filter 11 b                     | oit              |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 5-4       |                                      | Source                           |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               | •                                    | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 3-2       |                                      | : Mask Source                    | for Filter 9 bit                      |                  |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | istore contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 1-0       |                                      | : Mask Source                    |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         | ed; do not use                   |                                       |                  |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      |                                  | · · · · · · · · · · · · · · · · · · · |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

NOTES:

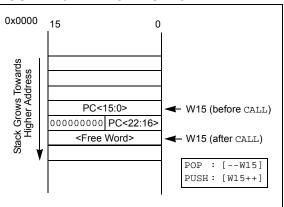

### 22.2 On-Chip Voltage Regulator

All of the dsPIC33FJXXXGPX06A/X08A/X10A devices power their core digital logic at a nominal 2.5V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJXXXGPX06A/X08A/X10A family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. The regulator requires that a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) be connected to the VCAP pin (Figure 22-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 25-13 of **Section 25.0** "**Electrical Characteristics**".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 22-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

### 22.3 BOR: Brown-out Reset

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

### 25.1 DC Characteristics

| TABLE 25-1: | <b>OPERATING MIPS VS. VOLTAGE</b> |

|-------------|-----------------------------------|

|             |                                   |

| Characteristic | VDD Range                | Temp Range      | Max MIPS                     |

|----------------|--------------------------|-----------------|------------------------------|

| Characteristic | (in Volts)               | (in °C)         | dsPIC33FJXXXGPX06A/X08A/X10A |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                           |

| _              | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 25-11 for the minimum and maximum BOR values.

### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                    | Symbol | Min | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| dsPIC33FJXXXGPX06A/X08A/X10A                                                                              |        |     |             |      |      |

| Operating Junction Temperature Range                                                                      | TJ     | -40 | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                                       | TA     | -40 | —           | +85  | °C   |

| Extended Temperature Devices                                                                              |        |     |             |      |      |

| Operating Junction Temperature Range                                                                      | TJ     | -40 | —           | +150 | °C   |

| Operating Ambient Temperature Range                                                                       | TA     | -40 | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ PDPINT + PI/O |        | )   | W           |      |      |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)                   |        |     |             |      |      |

| Maximum Allowed Power Dissipation                                                                         | Pdmax  | (   | TJ - TA)/θJ | A    | W    |

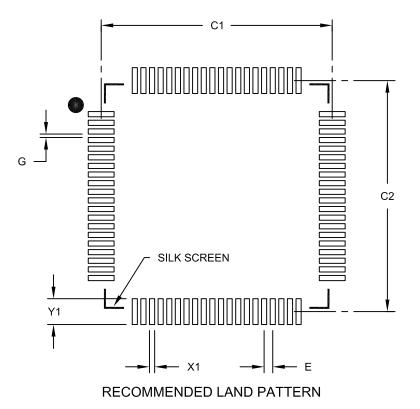

### TABLE 25-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        |     | Тур | Max | Unit | Notes |

|-------------------------------------------------------|-----|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θја | 40  | —   | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1 mm)  | θја | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θja | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

### TABLE 25-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS              |                           |     | $\label{eq:standard operating Conditions: 3.0V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |        |          |  |

|---------------------------------|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|------------|--------|----------|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup>    | Max | Units                                                                                                                      | Conditions |        |          |  |

| Operating Cur                   | rent (IDD) <sup>(1)</sup> |     |                                                                                                                            |            |        |          |  |

| DC20d                           | 27                        | 30  | mA                                                                                                                         | -40°C      |        |          |  |

| DC20a                           | 27                        | 30  | mA                                                                                                                         | +25°C      | 3.3V   | 10 MIPS  |  |

| DC20b                           | 27                        | 30  | mA                                                                                                                         | +85°C      | 3.3V   | 10 10195 |  |

| DC20c                           | 27                        | 35  | mA                                                                                                                         | +125°C     |        |          |  |

| DC21d                           | 36                        | 40  | mA                                                                                                                         | -40°C      |        | 16 MIDS  |  |

| DC21a                           | 37                        | 40  | mA                                                                                                                         | +25°C      | 3.3V   |          |  |

| DC21b                           | 38                        | 45  | mA                                                                                                                         | +85°C      | 3.3V   | 16 MIPS  |  |

| DC21c                           | 39                        | 45  | mA                                                                                                                         | +125°C     |        |          |  |

| DC22d                           | 43                        | 50  | mA                                                                                                                         | -40°C      |        |          |  |

| DC22a                           | 46                        | 50  | mA                                                                                                                         | +25°C      | 2.21/  | 20 MIPS  |  |

| DC22b                           | 46                        | 55  | mA                                                                                                                         | +85°C      | - 3.3V |          |  |

| DC22c                           | 47                        | 55  | mA                                                                                                                         | +125°C     |        |          |  |

| DC23d                           | 65                        | 70  | mA                                                                                                                         | -40°C      |        |          |  |

| DC23a                           | 65                        | 70  | mA                                                                                                                         | +25°C      | 2.21/  |          |  |

| DC23b                           | 65                        | 70  | mA                                                                                                                         | +85°C      | - 3.3V | 30 MIPS  |  |

| DC23c                           | 65                        | 70  | mA                                                                                                                         | +125°C     | 7      |          |  |

| DC24d                           | 84                        | 90  | mA                                                                                                                         | -40°C      |        |          |  |

| DC24a                           | 84                        | 90  | mA                                                                                                                         | +25°C      | 2.21/  |          |  |

| DC24b                           | 84                        | 90  | mA                                                                                                                         | +85°C      | - 3.3V | 40 MIPS  |  |

| DC24c                           | 84                        | 90  | mA                                                                                                                         | +125°C     | 7      |          |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while(1) statement

- · JTAG is disabled

- **2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: These parameters are characterized but not tested in manufacturing.

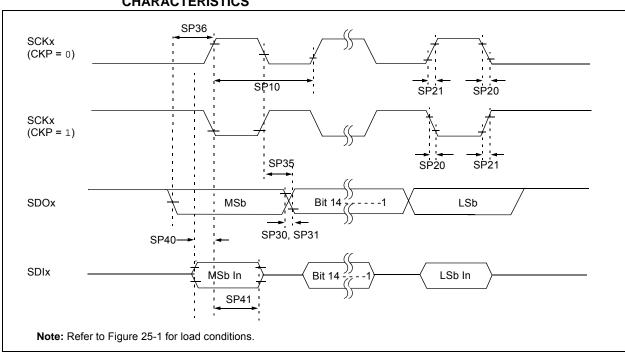

### FIGURE 25-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

### TABLE 25-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | (unless c | Operatin<br>otherwise<br>g temperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|-----------------------------------------------|-----------|-------------------------------------|----------------------------|-----------|-----------------------------------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min       | Тур <sup>(2)</sup>                  | Max                        | Units     | Conditions                                                      |

| SP10               | TscP                  | Maximum SCK Frequency                         | —         | _                                   | 10                         | MHz       | See Note 3                                                      |

| SP20               | TscF                  | SCKx Output Fall Time                         | —         | —                                   | _                          | ns        | See parameter DO32 and <b>Note 4</b>                            |

| SP21               | TscR                  | SCKx Output Rise Time                         | —         | —                                   | _                          | ns        | See parameter DO31 and <b>Note 4</b>                            |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | —         | —                                   | _                          | ns        | See parameter DO32 and <b>Note 4</b>                            |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | —         | —                                   | _                          | ns        | See parameter DO31 and <b>Note 4</b>                            |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —         | 6                                   | 20                         | ns        | —                                                               |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30        | —                                   |                            | ns        | _                                                               |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30        | _                                   |                            | ns        | _                                                               |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30        | —                                   | -                          | ns        | —                                                               |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

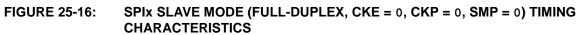

### TABLE 25-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extend} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                | Тур <sup>(2)</sup> | Max | Units | Conditions                           |