Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp310a-e-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

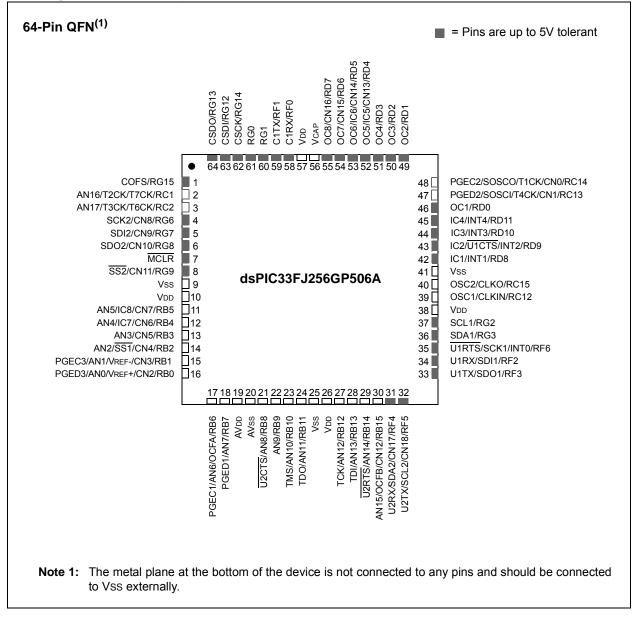

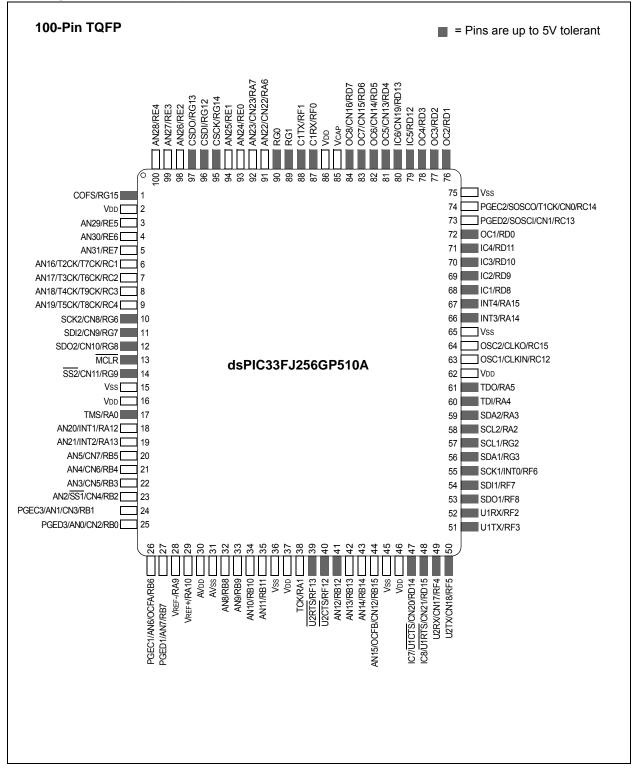

#### Pin Diagrams (Continued)

#### Pin Diagrams (Continued)

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206A

- dsPIC33FJ64GP306A

- dsPIC33FJ64GP310A

- dsPIC33FJ64GP706A

- dsPIC33FJ64GP708A

- dsPIC33FJ64GP710A

- dsPIC33FJ128GP206A

- dsPIC33FJ128GP306A

- dsPIC33FJ128GP310A

- dsPIC33FJ128GP706A

- dsPIC33FJ128GP708A

- dsPIC33FJ128GP710A

- dsPIC33FJ256GP506A

- dsPIC33FJ256GP510A

- dsPIC33FJ256GP710A

The dsPIC33FJXXXGPX06A/X08A/X10A General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes).

This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXGPX06A/X08A/X10A device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06A/X08A/X10A Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXGPX06A/X08A/X10A devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06A/X08A/X10A devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXGPX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXGPX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXGPX06A/X08A/X10A is a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- · Conventional or convergent rounding (RND)

- Automatic saturation on/off for AccA (SATA)

- Automatic saturation on/off for AccB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

Table 3-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | A = A + x2              | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

NOTES:

#### TABLE 4-9: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                                                | Bit 8                 | Bit 7            | Bit 6 | Bit 5   | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|------------------------------------------------------|-----------------------|------------------|-------|---------|----------|-------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       |        | —       | —      |        | _      | _                                                    |                       | Receive Register |       |         |          |       | 0000  |       |       |               |

| I2C1TRN  | 0202        | —       |        | _       | _      | _      | _      | _                                                    | — — Transmit Register |                  |       |         |          |       | OOFF  |       |       |               |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | Baud Rate Generator Register                         |                       |                  |       |         | 0000     |       |       |       |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |                       |                  |       |         | 1000     |       |       |       |       |               |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                                               | ADD10                 | IWCOL            | I2COV | D_A     | Р        | S     | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |                                                      |                       |                  |       | Address | Register |       |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | _      | Address Mask Register                                |                       |                  |       |         | 0000     |       |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                        | Bit 7 | Bit 6 | Bit 5   | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------|-------|-------|---------|----------|-------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | —      |         | —      | _      | -      | _      | – – Receive Register         |       |       |         |          |       | 0000  |       |       |               |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | - — Transmit Register        |       |       |         |          |       | OOFF  |       |       |               |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      | Baud Rate Generator Register |       |       |         |          | 0000  |       |       |       |               |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                         | GCEN  | STREN | ACKDT   | ACKEN    | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                        | IWCOL | I2COV | D_A     | Р        | S     | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | —       | —      | _       | _      | _      |        |        |                              |       |       | Address | Register |       |       |       |       | 0000          |

| I2C2MSK  | 021C        | -       | —      |         | —      | _      |        |        | Address Mask Register        |       |       |         |          |       | 0000  |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **REGISTER 5-2:** NVMKEY: NON-VOLATILE MEMORY KEY REGISTER U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_ — \_\_\_\_ bit 15 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 NVMKEY<7:0> bit 7 Legend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

bit 8

bit 0

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |

|------------------|--------------------------------------|-------------------|-------------------|------------------------------------|

| 54               | 46                                   | 0x000070          | 0x000170          | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072          | 0x000172          | T6 – Timer6                        |

| 56               | 48                                   | 0x000074          | 0x000174          | T7 – Timer7                        |

| 57               | 49                                   | 0x000076          | 0x000176          | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078          | 0x000178          | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A          | 0x00017A          | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C          | 0x00017C          | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E          | 0x00017E          | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080          | 0x000180          | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082          | 0x000182          | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084          | 0x000184          | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086          | 0x000186          | Reserved                           |

| 66               | 58                                   | 0x000088          | 0x000188          | Reserved                           |

| 67               | 59                                   | 0x00008A          | 0x00018A          | DCIE – DCI Error                   |

| 68               | 60                                   | 0x00008C          | 0x00018C          | DCID – DCI Transfer Done           |

| 69               | 61                                   | 0x00008E          | 0x00018E          | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090          | 0x000190          | Reserved                           |

| 71               | 63                                   | 0x000092          | 0x000192          | Reserved                           |

| 72               | 64                                   | 0x000094          | 0x000194          | Reserved                           |

| 73               | 65                                   | 0x000096          | 0x000196          | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098          | 0x000198          | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A          | 0x00019A          | Reserved                           |

| 76               | 68                                   | 0x00009C          | 0x00019C          | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E          | 0x00019E          | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0          | 0x0001A0          | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2          | 0x0001A2          | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-0x0000FE | 0x0001A4-0x0001FE | Reserved                           |

#### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| R/W-0         | R/W-0          | U-0                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|----------------|---------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IF          | DMA4IF         |                                 | OC8IF            | OC7IF            | OC6IF            | OC5IF           | IC6IF   |

| bit 15        |                |                                 |                  |                  | •                |                 | bit     |

|               |                |                                 |                  |                  |                  |                 |         |

| R/W-0         | R/W-0          | R/W-0                           | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                           | DMA3IF           | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |

| bit 7         |                |                                 |                  |                  |                  |                 | bit     |

| Legend:       |                |                                 |                  |                  |                  |                 |         |

| R = Readable  | e bit          | W = Writable                    | bit              | U = Unimplei     | mented bit, read | as '0'          |         |

| -n = Value at | POR            | '1' = Bit is set                |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                |                                 |                  |                  |                  |                 |         |

| bit 15        |                | Interrupt Flag                  |                  |                  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 11        | •              | equest has no                   |                  | amplata Intorr   | unt Flog Status  | hit.            |         |

| bit 14        |                | equest has oc                   |                  |                  | upt Flag Status  | DIL             |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 13        | Unimplemen     | ted: Read as '                  | 0'               |                  |                  |                 |         |

| bit 12        | OC8IF: Outpu   | ut Compare Ch                   | annel 8 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 11        | •              | equest has no                   |                  | unt Flag Otation | - h:+            |                 |         |

| bit 11        | •              | request has oc                  |                  | upt Flag Status  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 10        | OC6IF: Outpu   | ut Compare Ch                   | annel 6 Interr   | upt Flag Status  | s bit            |                 |         |

|               | •              | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

| bit 9         | •              | •                               |                  | upt Flag Status  | s bit            |                 |         |

|               | -              | equest has oc                   |                  | apt i lag olalat |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 8         | -              | Capture Chann                   | -                | -lag Status bit  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 7         | •              | equest has no<br>Capture Chann  |                  | -lag Status hit  |                  |                 |         |

|               |                | equest has oc                   |                  | lay Status bit   |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 6         | IC4IF: Input C | Capture Chann                   | el 4 Interrupt F | Flag Status bit  |                  |                 |         |

|               | •              | equest has oc                   |                  |                  |                  |                 |         |

| L:1 F         | -              | equest has no                   |                  | The Otative hit  |                  |                 |         |

| bit 5         |                | Capture Chann<br>request has oc | -                | -lag Status bit  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 4         | DMA3IF: DM     | A Channel 3 D                   | ata Transfer C   | Complete Interr  | upt Flag Status  | bit             |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 0         | -              | equest has no                   |                  | L :4             |                  |                 |         |

| bit 3         |                | Event Interrup                  | -                | JIC              |                  |                 |         |

|               |                | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0           | U-0        | U-0                               | U-0            | U-0              | U-0             | U-0             | U-0   |

|---------------|------------|-----------------------------------|----------------|------------------|-----------------|-----------------|-------|

|               | —          | —                                 | _              | —                | —               | —               | —     |

| bit 15        |            |                                   |                |                  |                 |                 | bit 8 |

|               |            |                                   |                |                  |                 |                 |       |

| R/W-0         | R/W-0      | R/W-0                             | R/W-0          | U-0              | R/W-0           | R/W-0           | U-0   |

| C2TXIE        | C1TXIE     | DMA7IE                            | DMA6IE         | _                | U2EIE           | U1EIE           |       |

| bit 7         |            |                                   |                |                  |                 |                 | bit C |

|               |            |                                   |                |                  |                 |                 |       |

| Legend:       |            |                                   |                |                  |                 |                 |       |

| R = Readabl   |            | W = Writable                      |                | -                | mented bit, rea | ad as '0'       |       |

| -n = Value at | t POR      | '1' = Bit is set                  | :              | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

|               |            |                                   |                |                  |                 |                 |       |

| bit 15-8      | •          | nted: Read as '                   |                |                  |                 |                 |       |

| bit 7         |            | AN2 Transmit D                    | •              | Interrupt Enab   | le bit          |                 |       |

|               |            | request enable                    |                |                  |                 |                 |       |

|               | •          | request not ena                   |                |                  |                 |                 |       |

| bit 6         |            | AN1 Transmit D                    | •              | Interrupt Enab   | le bit          |                 |       |

|               |            | request enable request not enable |                |                  |                 |                 |       |

| bit 5         | •          | IA Channel 7 D                    |                | Complete Enal    | ble Status bit  |                 |       |

| bit o         |            | request enable                    |                |                  |                 |                 |       |

|               |            | request not ena                   |                |                  |                 |                 |       |

| bit 4         | DMA6IE: DM | A Channel 6 D                     | ata Transfer C | Complete Enal    | ble Status bit  |                 |       |

|               |            | request enable                    |                |                  |                 |                 |       |

|               | •          | request not ena                   |                |                  |                 |                 |       |

| bit 3         | Unimpleme  | nted: Read as '                   | 0'             |                  |                 |                 |       |

| bit 2         |            | T2 Error Interru                  | •              |                  |                 |                 |       |

|               |            | request enable                    |                |                  |                 |                 |       |

|               | •          | request not ena                   |                |                  |                 |                 |       |

| bit 1         |            | T1 Error Interru                  | •              |                  |                 |                 |       |

|               |            | request enable<br>request not ena |                |                  |                 |                 |       |

|               |            | request not en                    | abieu          |                  |                 |                 |       |

bit 0 Unimplemented: Read as '0'

| R-0 HSC          | R-0 HSC                                                      | U-0                                                                                | U-0                                                             | U-0                                      | R/C-0 HS                                       | R-0 HSC              | R-0 HSC         |

|------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------|------------------------------------------------|----------------------|-----------------|

| ACKSTAT          | TRSTAT                                                       | _                                                                                  | _                                                               | _                                        | BCL                                            | GCSTAT               | ADD10           |

| bit 15           |                                                              |                                                                                    |                                                                 |                                          |                                                |                      | bit 8           |

|                  |                                                              |                                                                                    |                                                                 |                                          |                                                |                      |                 |

| R/C-0 HS         | R/C-0 HS                                                     | R-0 HSC                                                                            | R/C-0 HSC                                                       | R/C-0 HSC                                | R-0 HSC                                        | R-0 HSC              | R-0 HSC         |

| IWCOL            | I2COV                                                        | D_A                                                                                | Р                                                               | S                                        | R_W                                            | RBF                  | TBF             |

| oit 7            |                                                              |                                                                                    |                                                                 |                                          |                                                |                      | bit (           |

| Legend:          |                                                              | U = Unimpler                                                                       | nented bit, rea                                                 | ad as '0'                                |                                                | C = Clear onl        | y bit           |

| R = Readable     | bit                                                          | W = Writable                                                                       | bit                                                             | HS = Set in h                            | ardware                                        | HSC = Hardwa         | are set/cleared |

| n = Value at I   | POR                                                          | '1' = Bit is set                                                                   | t                                                               | '0' = Bit is cle                         | ared                                           | x = Bit is unkn      | own             |

| bit 15<br>bit 14 | 1 = NACK rec<br>0 = ACK rece<br>Hardware set<br>TRSTAT: Trar | ng as I <sup>2</sup> C mas<br>eived from slav<br>ived from slav<br>or clear at end | iter, applicable<br>ive<br>e<br>d of slave Ack<br>t (when opera | nowledge.<br>ting as I <sup>2</sup> C ma | nsmit operation<br>ster, applicable            | )<br>to master trans | mit operation   |

|                  | 0 = Master tra                                               | ansmit is not in                                                                   | progress                                                        |                                          | ware clear at e                                | nd of slave Ack      | nowledge.       |

| oit 13-11        | Unimplemen                                                   | ted: Read as                                                                       | 0'                                                              |                                          |                                                |                      |                 |

| bit 10           |                                                              | on                                                                                 | n detected dur                                                  | ing a master o                           | peration                                       |                      |                 |

| bit 9            | GCSTAT: Ger                                                  | neral Call Statu                                                                   | us bit                                                          |                                          |                                                |                      |                 |

|                  | 0 = General c                                                | all address wa<br>all address wa<br>when address                                   | as not received                                                 |                                          | ss. Hardware c                                 | lear at Stop det     | ection.         |

| bit 8            | 1 = 10-bit add<br>0 = 10-bit add                             | it Address Sta<br>Iress was mate<br>Iress was not i<br>at match of 2i              | ched<br>matched                                                 | ched 10-bit ad                           | dress. Hardwa                                  | re clear at Stop     | detection.      |

| bit 7            | IWCOL: Write                                                 |                                                                                    |                                                                 |                                          | 0                                              |                      |                 |

|                  | 0 = No collisio                                              | on                                                                                 | -                                                               |                                          | use the I <sup>2</sup> C mo<br>usy (cleared by | -                    |                 |

| bit 6            | I2COV: Recei                                                 | ve Overflow F                                                                      | lag bit                                                         |                                          |                                                |                      |                 |

|                  | 0 = No overflo                                               | ow.                                                                                |                                                                 | -                                        | till holding the<br>V (cleared by s            | -                    |                 |

| bit 5            |                                                              | Idress bit (whe                                                                    |                                                                 | _                                        | , ,                                            | ,                    |                 |

|                  | 0 = Indicates                                                |                                                                                    | /te received w                                                  | as device add                            | ress<br>by reception of                        | slave byte.          |                 |

| bit 4            | P: Stop bit                                                  |                                                                                    |                                                                 |                                          |                                                |                      |                 |

|                  | 1 = Indicates                                                | that a Stop bit                                                                    | has been dete                                                   | ected last                               |                                                |                      |                 |

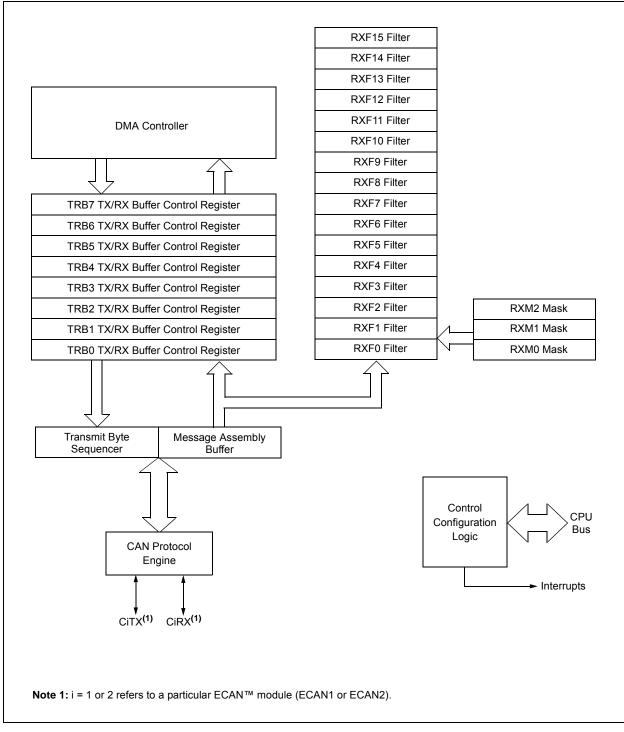

#### FIGURE 19-1: ECAN™ MODULE BLOCK DIAGRAM

#### REGISTER 19-11: CIFEN1: ECAN™ ACCEPTANCE FILTER ENABLE REGISTER

| R/W-1        | R/W-1   | R/W-1        | R/W-1   | R/W-1                              | R/W-1   | R/W-1  | R/W-1  |  |

|--------------|---------|--------------|---------|------------------------------------|---------|--------|--------|--|

| FLTEN15      | FLTEN14 | FLTEN13      | FLTEN12 | FLTEN11                            | FLTEN10 | FLTEN9 | FLTEN8 |  |

| bit 15       |         | -<br>-       |         |                                    |         |        | bit 8  |  |

|              |         |              |         |                                    |         |        |        |  |

| R/W-1        | R/W-1   | R/W-1        | R/W-1   | R/W-1                              | R/W-1   | R/W-1  | R/W-1  |  |

| FLTEN7       | FLTEN6  | FLTEN5       | FLTEN4  | FLTEN3                             | FLTEN2  | FLTEN1 | FLTEN0 |  |

| bit 7        |         |              |         |                                    |         |        | bit 0  |  |

|              |         |              |         |                                    |         |        |        |  |

| Legend:      |         |              |         |                                    |         |        |        |  |

| R = Readable | bit     | W = Writable | hit     | LI - Unimplemented bit read as '0' |         |        |        |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 15-0 **FLTENn:** Enable Filter n to Accept Messages bits

1 = Enable Filter n

0 = Disable Filter n

#### REGISTER 19-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|         |         |         |         |         |         |        |        |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

bit 7

**RXOVF15:RXOVF0:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                             |                    |

|-------------------|--------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 RXOVF31:RXOVF16: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

bit 0

#### TABLE 23-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc             | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD   | f               | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG          | WREG = $f + WREG + (C)$                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1              | None                     |

|                    |                      | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1              | None                     |

| 6 BF               | BRA                  | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GE, Expr        | Branch if greater than or equal          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GEU, Expr       | Branch if unsigned greater than or equal | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GT,Expr         | Branch if greater than                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GTU, Expr       | Branch if unsigned greater than          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LE,Expr         | Branch if less than or equal             | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LEU, Expr       | Branch if unsigned less than or equal    | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LT, Expr        | Branch if less than                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LTU, Expr       | Branch if unsigned less than             | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | N, Expr         | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NC, Expr        | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NN, Expr        | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NOV, Expr       | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OA, Expr        | Branch if Accumulator A overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OB, Expr        | Branch if Accumulator B overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | SA, Expr        | Branch if Accumulator A saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | SB, Expr        | Branch if Accumulator B saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA   |                 | Branch Unconditionally                   | 1             | 2              | None                     |

|                    |                      | BRA   | Expr<br>Z,Expr  | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | Z, Expr<br>Wn   | Computed Branch                          | 1             | 2              | None                     |

| 7                  | BSET                 |       |                 | Bit Set f                                | 1             | 1              | None                     |

| ı                  | DOFI                 | BSET  | f,#bit4         | Bit Set Ws                               | 1             | 1              | None                     |

| 8                  | DCW                  | BSET  | Ws,#bit4        |                                          |               | 1              |                          |

| ر<br>ر             | BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             |                | None                     |

|                    |                      | BSW.Z | Ws,Wb           | Write Z bit to Ws <wb></wb>              | 1             | 1              | None<br>None             |

| 9                  | BTG                  | BTG   | f,#bit4         | Bit Toggle f                             | 1             | 1              |                          |

| АС СНА       | RACTERI | STICS                    |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                             |  |  |

|--------------|---------|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|--|--|

| Param<br>No. | Symbol  | Charact                  | eristic                   | Min                                                                                                                                                                                                                                                                                     | Max  | Units | Conditions                                  |  |  |

| IS10         | TLO:SCL | Clock Low Time           | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |  |

|              |         |                          | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 10 MHz  |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                     | —    | μS    | —                                           |  |  |

| IS11         | THI:SCL | Clock High Time          | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |  |

|              |         |                          | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 10 MHz  |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                     | _    | μS    |                                             |  |  |

| IS20         | TF:SCL  | SDAx and SCLx            | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 300  | ns    | CB is specified to be from                  |  |  |

|              |         | Fall Time                | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | 10 to 400 pF                                |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                       | 100  | ns    |                                             |  |  |

| IS21         | TR:SCL  | SDAx and SCLx            | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns    | CB is specified to be from                  |  |  |

|              |         | Rise Time                | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | 10 to 400 pF                                |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> |                                                                                                                                                                                                                                                                                         | 300  | ns    |                                             |  |  |

| IS25 TSU:D   | TSU:DAT | Data Input<br>Setup Time | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                     |      | ns    |                                             |  |  |

|              |         |                          | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                     |      | ns    |                                             |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                                                                                     |      | ns    |                                             |  |  |

| IS26         | THD:DAT | Data Input               | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       |      | μS    |                                             |  |  |

|              |         | Hold Time                | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 0.9  | μS    | -                                           |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                       | 0.3  | μS    |                                             |  |  |

| IS30         | TSU:STA | Start Condition          | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     |      | μS    | Only relevant for Repeated                  |  |  |

|              |         | Setup Time               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                     |      | μS    | Start condition                             |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                    |      | μS    |                                             |  |  |

| IS31         | THD:STA | Start Condition          | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                     |      | μS    | After this period, the first                |  |  |

|              |         | Hold Time                | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                     |      | μS    | clock pulse is generated                    |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                    |      | μS    |                                             |  |  |

| IS33         | Tsu:sto | Stop Condition           | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     |      | μS    |                                             |  |  |

|              |         | Setup Time               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                     |      | μS    |                                             |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                                                                                                                                     |      | μS    |                                             |  |  |

| IS34         | THD:STO | Stop Condition           | 100 kHz mode              | 4000                                                                                                                                                                                                                                                                                    |      | ns    |                                             |  |  |

|              |         | Hold Time                | 400 kHz mode              | 600                                                                                                                                                                                                                                                                                     |      | ns    |                                             |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 250                                                                                                                                                                                                                                                                                     |      | ns    | -                                           |  |  |

| IS40         | TAA:SCL | Output Valid             | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 3500 | ns    | _                                           |  |  |

|              |         | From Clock               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 1000 | ns    | 1                                           |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                       | 350  | ns    | 1                                           |  |  |

| IS45         | TBF:SDA | Bus Free Time            | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     |      | μS    | Time the bus must be free                   |  |  |

|              |         |                          | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     |      | μS    | before a new transmission                   |  |  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                     |      | μS    | can start                                   |  |  |

| IS50         | Св      | Bus Capacitive Lo        |                           |                                                                                                                                                                                                                                                                                         | 400  | pF    |                                             |  |  |

#### TABLE 25-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

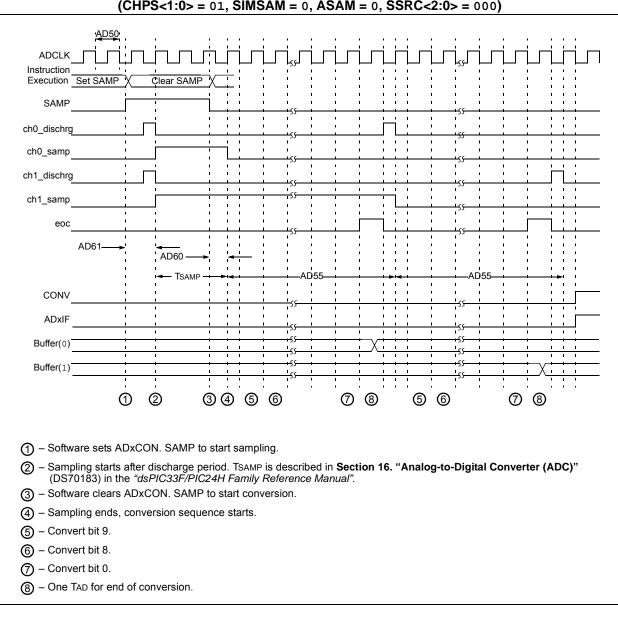

#### FIGURE 25-25: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)

# APPENDIX A: MIGRATING FROM dsPIC33FJXXXGPX06/X08/X10 DEVICES TO dsPIC33FJXXXGPX06A/X08A/X10A DEVICES

dsPIC33FJXXXGPX06A/X08A/X10A devices were designed to enhance the dsPIC33FJXXXGPX06/X08/ X10 families of devices.

In general, the dsPIC33FJXXXGPX06A/X08A/X10A devices backward-compatible are with dsPIC33FJXXXGPX06/X08/X10 devices; however, manufacturing differences may cause dsPIC33FJXXXGPX06A/X08A/X10A devices to behave differently from dsPIC33FJXXXGPX06/X08/ X10 devices. Therefore, complete system test and recommended characterization is if dsPIC33FJXXXGPX06A/X08A/X10A devices are used to replace dsPIC33FJXXXGPX06/X08/X10 devices.

The following enhancements were introduced:

- Extended temperature support of up to +125°C

- Enhanced Flash module with higher endurance and retention

- New PLL Lock Enable configuration bit

- Added Timer5 trigger for ADC1 and Timer3 trigger for ADC2