Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp310a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

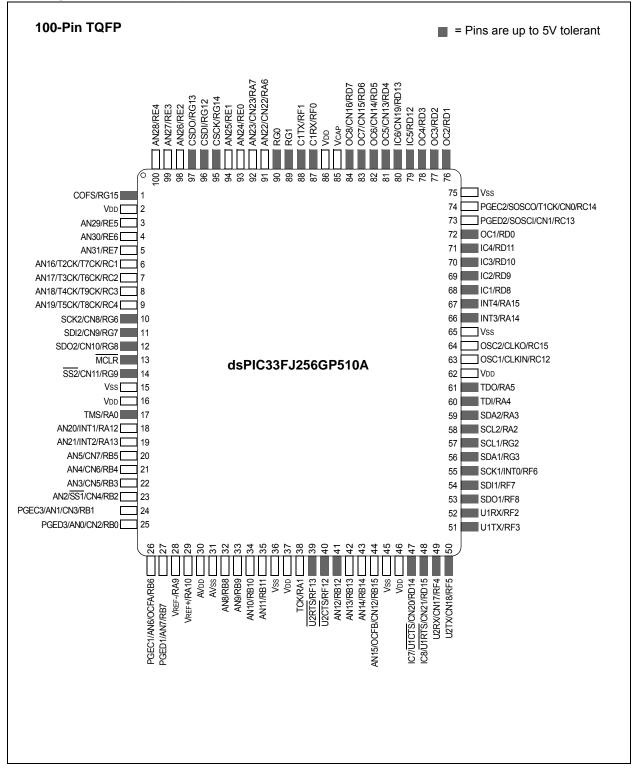

## Pin Diagrams (Continued)

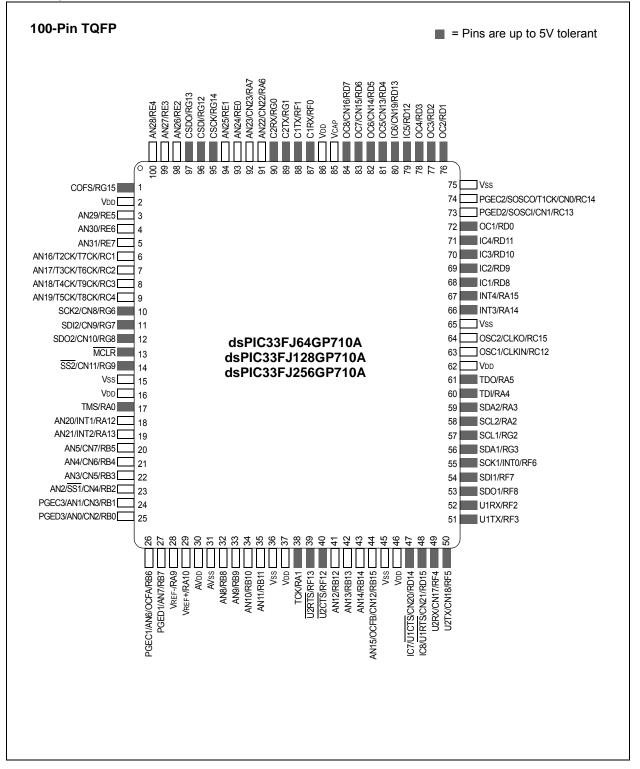

## **Pin Diagrams (Continued)**

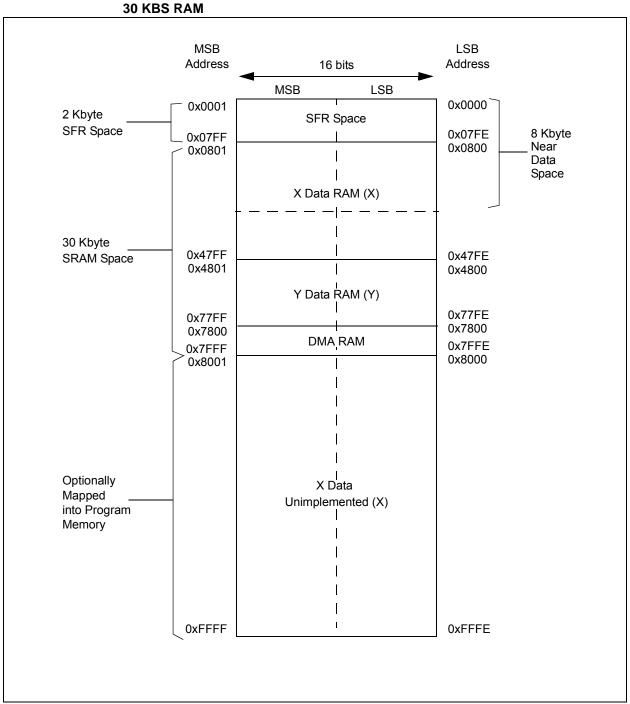

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 30 KBS RAM

### TABLE 4-9: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|-----------------------|-------|-------|-------|---------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       |        | —       | —      |        | _      | _                     |       |       |       |         | Receive  | Register |       |       |       | 0000          |

| I2C1TRN  | 0202        | —       |        | _       | _      | _      | _      | — — Transmit Register |       |       |       |         |          |          | OOFF  |       |       |               |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      |                       |       |       |       |         |          |          | 0000  |       |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN  | GCEN  | STREN | ACKDT   | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                | ADD10 | IWCOL | I2COV | D_A     | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |                       |       |       |       | Address | Register |          |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | _      | Address Mask Register |       |       |       |         |          |          | 0000  |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-10: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | —      |         | —      | _      | -      | _      |       |       |       |            | Receive      | Register   |       |       |       | 0000          |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | _     |       |       |            | Transmit     | t Register |       |       |       | OOFF          |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      |       |       |       | Baud Rat   | e Generato   | r Register |       |       |       | 0000          |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | —       | —      | _       | _      | _      |        |        |       |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C2MSK  | 021C        | -       | —      |         | —      | _      |        |        |       |       |       | Address Ma | ask Register | r          |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: DCI REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7     | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0  | Reset State         |

|-------------|-------|--------|--------|---------|--------|--------|--------|------------|-------------|-----------|--------|-------|-------|-------|-------|---------|--------|---------------------|

| DCICON1     | 0280  | DCIEN  | —      | DCISIDL | _      | DLOOP  | CSCKD  | CSCKE      | COFSD       | UNFM      | CSDOM  | DJST  |       |       | —     | COFSM1  | COFSM0 | 0000 0000 0000 0000 |

| DCICON2     | 0282  | _      | _      | _       | _      | BLEN1  | BLEN0  | _          |             | COFSO     | G<3:0> |       | -     |       | V     | VS<3:0> |        | 0000 0000 0000 0000 |

| DCICON3     | 0284  | _      | _      | _       | _      |        |        |            |             |           | BCG<1  | 1:0>  |       |       |       |         |        | 0000 0000 0000 0000 |

| DCISTAT     | 0286  | _      | _      | _       | _      | SLOT3  | SLOT2  | SLOT1      | SLOT0       |           | _      | -     | -     | ROV   | RFUL  | TUNF    | TMPTY  | 0000 0000 0000 0000 |

| TSCON       | 0288  | TSE15  | TSE14  | TSE13   | TSE12  | TSE11  | TSE10  | TSE9       | TSE8        | TSE7      | TSE6   | TSE5  | TSE4  | TSE3  | TSE2  | TSE1    | TSE0   | 0000 0000 0000 0000 |

| RSCON       | 028C  | RSE15  | RSE14  | RSE13   | RSE12  | RSE11  | RSE10  | RSE9       | RSE8        | RSE7      | RSE6   | RSE5  | RSE4  | RSE3  | RSE2  | RSE1    | RSE0   | 0000 0000 0000 0000 |

| RXBUF0      | 0290  |        |        |         |        |        |        | Receive E  | Buffer #0 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF1      | 0292  |        |        |         |        |        |        | Receive E  | Buffer #1 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF2      | 0294  |        |        |         |        |        |        | Receive E  | Buffer #2 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF3      | 0296  |        |        |         |        |        |        | Receive E  | Buffer #3 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF0      | 0298  |        |        |         |        |        |        | Transmit I | Buffer #0 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF1      | 029A  |        |        |         |        |        |        | Transmit I | Buffer #1 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF2      | 029C  |        |        |         |        |        |        | Transmit I | Buffer #2 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF3      | 029E  |        |        |         |        |        |        | Transmit I | Buffer #3 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend:

— = unimplemented, read as '0'. Refer to the *"dsPIC33F/PIC24H Family Reference Manual"* for descriptions of register bit fields. Note 1:

## TABLE 4-25: PORTA REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA               | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | _      | TRISA10 | TRISA9 |       | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA               | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA                | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA <sup>(2)</sup> | 06C0 | ODCA15  | ODCA14  | _       | _       | _      | _       | _      |       | _      |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices. Legend:

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-26: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | XXXX          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

1 = Interrupt request has occurred0 = Interrupt request has not occurred

© 2009-2012 Microchip Technology Inc.

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

## REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

|                 |                   | T2IP<2:0>                               |                  | —                |                 | OC2IP<2:0>           |       |

|-----------------|-------------------|-----------------------------------------|------------------|------------------|-----------------|----------------------|-------|

| bit 15          |                   |                                         |                  |                  |                 |                      | bit   |

|                 |                   | DAMO                                    |                  | 11.0             |                 | DAALO                |       |

| U-0             | R/W-1             | R/W-0<br>IC2IP<2:0>                     | R/W-0            | U-0              | R/W-1           | R/W-0<br>DMA0IP<2:0> | R/W-0 |

| bit 7           |                   | 10211 42.05                             |                  |                  |                 | Division 42.05       | bit   |

|                 |                   |                                         |                  |                  |                 |                      |       |

| Legend:         |                   |                                         |                  |                  |                 |                      |       |

| R = Readable    |                   | W = Writable k                          | Dit              | •                | mented bit, rea |                      |       |

| -n = Value at F | POR               | '1' = Bit is set                        |                  | '0' = Bit is cle | eared           | x = Bit is unkn      | iown  |

| bit 15          | Unimplemer        | nted: Read as '0                        | )'               |                  |                 |                      |       |

| bit 14-12       | T2IP<2:0>: 7      | Timer2 Interrupt                        | Priority bits    |                  |                 |                      |       |

|                 | 111 = Interru     | ıpt is priority 7 (h                    | nighest priority | y interrupt)     |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 | 001 = Interru     | pt is priority 1                        |                  |                  |                 |                      |       |

|                 | 000 = Interru     | pt source is disa                       | abled            |                  |                 |                      |       |

| bit 11          | Unimplemer        | nted: Read as '0                        | )'               |                  |                 |                      |       |

| bit 10-8        |                   | : Output Compa                          |                  | =                | ity bits        |                      |       |

|                 | 111 = Interru     | ipt is priority 7 (h                    | nighest priority | y interrupt)     |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 |                   | ipt is priority 1<br>ipt source is disa | abled            |                  |                 |                      |       |

| bit 7           |                   | nted: Read as '0                        |                  |                  |                 |                      |       |

| bit 6-4         | -                 | Input Capture C                         |                  | rrupt Priority b | its             |                      |       |

|                 |                   | ipt is priority 7 (h                    |                  |                  |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 |                   | pt is priority 1<br>pt source is disa   | abled            |                  |                 |                      |       |

| bit 3           |                   | nted: Read as '0                        |                  |                  |                 |                      |       |

| bit 2-0         | -                 | >: DMA Channe                           |                  | sfer Complete    | Interrupt Prio  | rity bits            |       |

| 511 2 0         |                   | ipt is priority 7 (h                    |                  | -                |                 |                      |       |

|                 | •                 |                                         | 5                | ,,               |                 |                      |       |

|                 | •                 |                                         |                  |                  |                 |                      |       |

|                 | •<br>001 = Intern | pt is priority 1                        |                  |                  |                 |                      |       |

|                 |                   | ipt source is disa                      | abled            |                  |                 |                      |       |

| U-0          | R/W-1                                    | R/W-0                                                                         | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|------------------------------------------|-------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| —            |                                          | T6IP<2:0>                                                                     |                 | _                |                 | DMA4IP<2:0>     |       |

| bit 15       |                                          |                                                                               |                 |                  |                 |                 | bit 8 |

| U-0          | U-0                                      | U-0                                                                           | U-0             | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _            | _                                        | _                                                                             |                 | _                |                 | OC8IP<2:0>      |       |

| bit 7        |                                          |                                                                               |                 | +                | •               |                 | bit 0 |

| Legend:      |                                          |                                                                               |                 |                  |                 |                 |       |

| R = Readab   | le bit                                   | W = Writable b                                                                | oit             | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR                                    | '1' = Bit is set                                                              |                 | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

| pit 11       | 000 = Interru                            | upt is priority 1<br>upt source is disa<br>n <b>ted:</b> Read as '0           |                 |                  |                 |                 |       |

| bit 10-8     | 111 = Interru<br>•<br>•<br>001 = Interru | DMA Channe<br>upt is priority 7 (h<br>upt is priority 1<br>upt source is disa | nighest priorit |                  | Interrupt Prior | ity bits        |       |

| bit 7-3      | Unimplemer                               | nted: Read as 'o                                                              | )'              |                  |                 |                 |       |

| bit 2-0      |                                          | : Output Compa<br>ıpt is priority 7 (h                                        |                 |                  | ity bits        |                 |       |

|              |                                          | upt is priority 1<br>upt source is disa                                       |                 |                  |                 |                 |       |

| R/W-0      | R/W-0        | R/W-0                               | R/W-0                 | U-0               | U-0            | U-0            | U-0                  |

|------------|--------------|-------------------------------------|-----------------------|-------------------|----------------|----------------|----------------------|

| T9MD       | T8MD         | T7MD                                | T6MD                  |                   |                |                |                      |

| bit 15     | TOMD         | TTND                                | TOND                  |                   | _              | —              | bit                  |

| DIL 15     |              |                                     |                       |                   |                |                | DI                   |

| U-0        | U-0          | U-0                                 | U-0                   | U-0               | U-0            | R/W-0          | R/W-0                |

| _          | _            | _                                   | —                     | _                 | —              | I2C2MD         | AD2MD <sup>(1)</sup> |

| bit 7      |              | •                                   |                       |                   |                |                | bit                  |

|            |              |                                     |                       |                   |                |                |                      |

| Legend:    |              |                                     |                       |                   |                |                |                      |

| R = Reada  | ble bit      | W = Writable                        | bit                   | U = Unimplem      | ented bit, rea | id as '0'      |                      |

| -n = Value | at POR       | '1' = Bit is set                    |                       | '0' = Bit is clea | ired           | x = Bit is unk | nown                 |

|            |              |                                     |                       |                   |                |                |                      |

| bit 15     | T9MD: Timer  | 9 Module Disat                      | ole bit               |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            | 0 = Timer9 m | odule is enable                     | d                     |                   |                |                |                      |

| bit 14     | T8MD: Timer  | 8 Module Disab                      | ole bit               |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            |              | odule is enable                     | -                     |                   |                |                |                      |

| bit 13     |              | 7 Module Disat                      |                       |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            |              | odule is enable                     | -                     |                   |                |                |                      |

| bit 12     |              | 6 Module Disat                      |                       |                   |                |                |                      |

|            |              | odule is disable<br>odule is enable |                       |                   |                |                |                      |

| bit 11-2   |              | ited: Read as '                     |                       |                   |                |                |                      |

| bit 1      | -            | 2 Module Disat                      |                       |                   |                |                |                      |

|            |              | z woodle Disat                      | DIE DIL               |                   |                |                |                      |

|            |              | dule is enabled                     |                       |                   |                |                |                      |

| bit 0      |              | 2 Module Disab                      | le bit <sup>(1)</sup> |                   |                |                |                      |

|            |              | ule is disabled                     |                       |                   |                |                |                      |

|            |              | ule is enabled                      |                       |                   |                |                |                      |

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

## 16.3 SPI Control Registers

## REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                             | U-0                                                                                           | U-0                                     | U-0              | U-0                        | U-0           |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|------------------|----------------------------|---------------|--|--|--|--|

| SPIEN                                 | —                                                                                                                                                                                                                                                                                                              | SPISIDL                                                                                                           | —                                                                                             | —                                       | _                | _                          | _             |  |  |  |  |

| bit 15                                |                                                                                                                                                                                                                                                                                                                |                                                                                                                   |                                                                                               |                                         |                  |                            | bit 8         |  |  |  |  |

|                                       | R/C-0                                                                                                                                                                                                                                                                                                          |                                                                                                                   |                                                                                               |                                         |                  |                            | <b>D</b> 0    |  |  |  |  |

| U-0                                   | SPIROV                                                                                                                                                                                                                                                                                                         | U-0                                                                                                               | U-0                                                                                           | U-0                                     | U-0              | R-0<br>SPITBF              | R-0<br>SPIRBF |  |  |  |  |

| <br>bit 7                             | SPIRUV                                                                                                                                                                                                                                                                                                         | —                                                                                                                 | _                                                                                             | _                                       | —                | SPILBE                     | bit (         |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                                                                                |                                                                                                                   |                                                                                               |                                         |                  |                            |               |  |  |  |  |

| Legend:                               |                                                                                                                                                                                                                                                                                                                | C = Clearable                                                                                                     | bit                                                                                           |                                         |                  |                            |               |  |  |  |  |

| R = Readabl                           | le bit                                                                                                                                                                                                                                                                                                         | W = Writable I                                                                                                    | bit                                                                                           | U = Unimpler                            | mented bit, read | d as '0'                   |               |  |  |  |  |

| -n = Value at                         | t POR                                                                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                  |                                                                                               | '0' = Bit is cle                        | ared             | x = Bit is unkr            | nown          |  |  |  |  |

| bit 14<br>bit 13<br>bit 12-7<br>bit 6 | 0 = Disables<br>Unimplemen<br>SPISIDL: Sto<br>1 = Discontin<br>0 = Continue<br>Unimplemen<br>SPIROV: Rec<br>1 = A new by<br>previous                                                                                                                                                                           | ted: Read as '(<br>p in Idle Mode l<br>ue module operati<br>module operati<br>ted: Read as '(<br>ceive Overflow I | bit<br>ration when de<br>on in Idle mod<br>)'<br>Flag bit<br>pletely receive<br>xBUF register | evice enters Id<br>de<br>ed and discard | lle mode         | oftware has not            | read the      |  |  |  |  |

| bit 5-2                               |                                                                                                                                                                                                                                                                                                                | ted: Read as '(                                                                                                   |                                                                                               |                                         |                  |                            |               |  |  |  |  |

| bit 1                                 | •                                                                                                                                                                                                                                                                                                              | x Transmit Buffe                                                                                                  |                                                                                               | bit                                     |                  |                            |               |  |  |  |  |

|                                       | <ul> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty</li> <li>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.</li> <li>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |                                                                                                                   |                                                                                               |                                         |                  |                            |               |  |  |  |  |

| bit 0                                 | SPIRBF: SPI                                                                                                                                                                                                                                                                                                    | x Receive Buffe                                                                                                   | er Full Status b                                                                              | oit                                     |                  |                            |               |  |  |  |  |

|                                       | 0 = Receive is<br>Automatically                                                                                                                                                                                                                                                                                | complete, SPIxF<br>s not complete,<br>set in hardward<br>cleared in hard                                          | SPIxRXB is e<br>e when SPIx t                                                                 | ransfers data                           |                  | SPIxRXB.<br>reading SPIxRX | ά.            |  |  |  |  |

| R/W-0              | U-0                  | R/W-0                                                                                                   | U-0           | R/W-0            | R/W-0              | R/W-0           | R/W-0       |  |  |  |  |

|--------------------|----------------------|---------------------------------------------------------------------------------------------------------|---------------|------------------|--------------------|-----------------|-------------|--|--|--|--|

| DCIEN              |                      | DCISIDL                                                                                                 |               | DLOOP            | CSCKD              | CSCKE           | COFSD       |  |  |  |  |

| bit 15             |                      |                                                                                                         |               |                  |                    | -               | bit 8       |  |  |  |  |

|                    |                      |                                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| R/W-0              | R/W-0                | R/W-0                                                                                                   | U-0           | U-0              | U-0                | R/W-0           | R/W-0       |  |  |  |  |

| UNFM               | CSDOM                | DJST                                                                                                    |               | _                |                    | COFS            | M<1:0>      |  |  |  |  |

| bit 7              |                      |                                                                                                         |               |                  |                    |                 | bit 0       |  |  |  |  |

| Legend:            |                      |                                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| R = Readable       | e hit                | W = Writable                                                                                            | hit           | LI = LInimpler   | mented bit, read   | 1 as '0'        |             |  |  |  |  |

| -n = Value at      |                      | '1' = Bit is set                                                                                        |               | '0' = Bit is cle |                    | x = Bit is unkr | nown        |  |  |  |  |

| n value at         |                      |                                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| bit 15             | DCIEN: DCI           | Module Enable                                                                                           | bit           |                  |                    |                 |             |  |  |  |  |

|                    | 1 = Module is        | s enabled                                                                                               |               |                  |                    |                 |             |  |  |  |  |

|                    | 0 = Module is        |                                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| bit 14             | -                    | nted: Read as '                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| bit 13             |                      | CI Stop in Idle C                                                                                       |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | vill halt in CPU I<br>vill continue to c                                                                |               | U Idle mode      |                    |                 |             |  |  |  |  |

| bit 12             |                      | nted: Read as '                                                                                         | -             |                  |                    |                 |             |  |  |  |  |

| bit 11             | •                    | ital Loopback M                                                                                         |               | bit              |                    |                 |             |  |  |  |  |

|                    |                      | 1 = Digital Loopback mode is enabled. CSDI and CSDO pins internally connected                           |               |                  |                    |                 |             |  |  |  |  |

|                    | •                    | 0 = Digital Loopback mode is disabled                                                                   |               |                  |                    |                 |             |  |  |  |  |

| bit 10             |                      | <b>CSCKD:</b> Sample Clock Direction Control bit<br>1 = CSCK pin is an input when DCI module is enabled |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | n is an input wh<br>n is an output w                                                                    |               |                  |                    |                 |             |  |  |  |  |

| bit 9              |                      | nple Clock Edge                                                                                         |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | nges on serial o                                                                                        |               | dge, sampled c   | on serial clock ri | ising edge      |             |  |  |  |  |

|                    |                      | nges on serial o                                                                                        | -             | -                | n serial clock fa  | Illing edge     |             |  |  |  |  |

| bit 8              |                      | me Synchroniza                                                                                          |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | n is an input wh<br>n is an output w                                                                    |               |                  |                    |                 |             |  |  |  |  |

| bit 7              | -                    | erflow Mode bit                                                                                         |               |                  |                    |                 |             |  |  |  |  |

| bit i              | •••••••••            | last value writte                                                                                       | n to the tran | smit registers o | n a transmit un    | derflow         |             |  |  |  |  |

|                    |                      | ʻ0 <b>'s on a trans</b> n                                                                               |               |                  |                    |                 |             |  |  |  |  |

| bit 6              |                      | rial Data Output                                                                                        |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | n will be tri-state<br>n drives '0's dur                                                                |               |                  |                    |                 |             |  |  |  |  |

| bit 5              | -                    | ata Justification                                                                                       | -             |                  |                    |                 |             |  |  |  |  |

|                    | 1 = Data trai        | 1 = Data transmission/reception is begun during the same serial clock cycle as the frame                |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | nization pulse                                                                                          | tion in heavy |                  |                    |                 | ation nules |  |  |  |  |

| bit 4-2            |                      | nsmission/recep<br>nted: Read as 'o                                                                     | -             | TONE SENALCIO    | ok cycle alter fra | ame synchroniz  | auon puise  |  |  |  |  |

| bit 4-2<br>bit 1-0 | -                    | >: Frame Sync                                                                                           |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | C-Link mode                                                                                             |               |                  |                    |                 |             |  |  |  |  |

|                    | 10 <b>= 16-bit A</b> | C-Link mode                                                                                             |               |                  |                    |                 |             |  |  |  |  |

|                    |                      | me Sync mode                                                                                            |               |                  |                    |                 |             |  |  |  |  |

|                    | 00 = Multi-Ch        | nannel Frame S                                                                                          | ync mode      |                  |                    |                 |             |  |  |  |  |

## REGISTER 20-1: DCICON1: DCI CONTROL REGISTER 1

| TABLE 22-2: | 22-2: CONFIGURATION BITS DESCRIPTION |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------|--------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field   | Register                             | RTSP<br>Effect | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| BWRP        | FBS                                  | Immediate      | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| BSS<2:0>    | FBS                                  | Immediate      | <ul> <li>Boot Segment Program Flash Code Protection Size</li> <li>X11 = No Boot program Flash segment</li> <li>Boot space is 1K IW less VS</li> <li>110 = Standard security; boot program Flash segment starts at End of VS, ends at 0007FEh</li> <li>010 = High security; boot program Flash segment starts at End of VS, ends at 0007FEh</li> <li>Boot space is 4K IW less VS</li> <li>101 = Standard security; boot program Flash segment starts at End of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 001FFEh</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 001FFEh</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 003FFEh</li> <li>000 = High security; boot program Flash segment starts at End of VS, ends at 003FFEh</li> </ul> |  |  |  |  |

| RBS<1:0>    | FBS                                  | Immediate      | Boot Segment RAM Code Protection<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 Bytes<br>01 = Boot RAM is 256 Bytes<br>00 = Boot RAM is 1024 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SWRP        | FSS                                  | Immediate      | Secure Segment Program Flash Write Protection<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

### TABLE 22-2: CONFIGURATION BITS DESCRIPTION

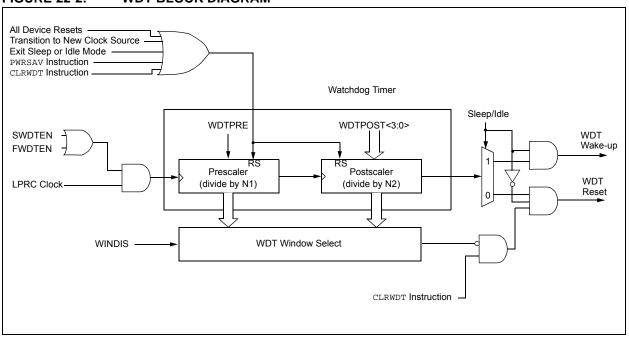

## 22.4 Watchdog Timer (WDT)

For dsPIC33FJXXXGPX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler and then can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

## FIGURE 22-2: WDT BLOCK DIAGRAM

## 24.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 24.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| TABLE 25-4: | DC TEMPERATURE AND VOLTAGE SPECIFICATIONS |

|-------------|-------------------------------------------|

|-------------|-------------------------------------------|

| DC CHARACTERISTICS                 |           |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                |

|------------------------------------|-----------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|----------------|

| Param<br>No. Symbol Characteristic |           |                                                                     | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(1)</sup> | Max | Units | Conditions     |

| Operati                            | ng Voltag | 9                                                                   |                                                                                                                                                                                                                                                                                         |                    |     |       |                |

| DC10                               | Supply V  | oltage                                                              |                                                                                                                                                                                                                                                                                         |                    |     |       |                |

|                                    | Vdd       |                                                                     | 3.0                                                                                                                                                                                                                                                                                     | _                  | 3.6 | V     | —              |

| DC12                               | Vdr       | RAM Data Retention Voltage <sup>(2)</sup>                           | 1.8                                                                                                                                                                                                                                                                                     | _                  |     | V     | —              |

| DC16                               | VPOR      | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                                                                                                                                                                                                                                                       | _                  | Vss | V     | _              |

| DC17                               | Svdd      | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.03                                                                                                                                                                                                                                                                                    | _                  | —   | V/ms  | 0-3.0V in 0.1s |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

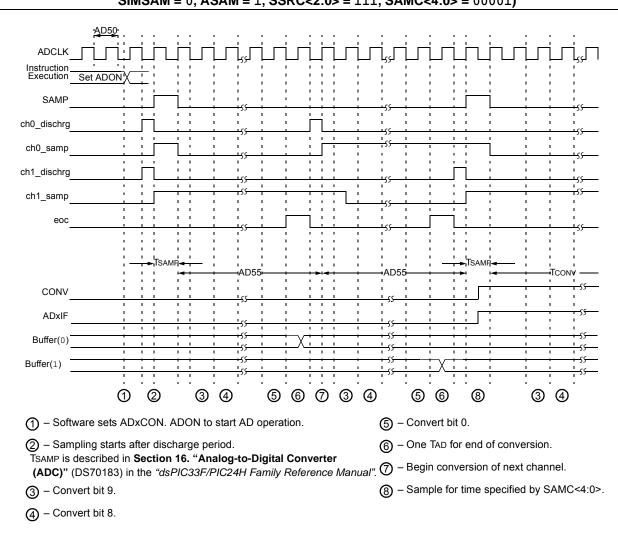

## FIGURE 25-26:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

| AC CH        | AC CHARACTERISTICS |                                                                           |           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |                                                           |  |  |

|--------------|--------------------|---------------------------------------------------------------------------|-----------|-------------------------------------------------------|---------|-------|-----------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                                            | Min.      | Typ <sup>(1)</sup>                                    | Max.    | Units | Conditions                                                |  |  |

|              | -                  | Cloc                                                                      | k Parame  | ters                                                  |         |       | ·                                                         |  |  |

| AD50b        | TAD                | ADC Clock Period                                                          | 76        |                                                       | _       | ns    | —                                                         |  |  |

| AD51b        | TRC                | ADC Internal RC Oscillator Period                                         | _         | 250                                                   | _       | ns    | —                                                         |  |  |

|              |                    | Con                                                                       | version F | late                                                  |         |       |                                                           |  |  |

| AD55b        | TCONV              | Conversion Time                                                           | —         | 12 Tad                                                | _       | _     | —                                                         |  |  |

| AD56b        | FCNV               | Throughput Rate                                                           | —         |                                                       | 1.1     | Msps  | —                                                         |  |  |

| AD57b        | TSAMP              | Sample Time                                                               | 2 Tad     | _                                                     | _       | _     | —                                                         |  |  |

|              |                    | Timir                                                                     | ng Paramo | eters                                                 |         |       |                                                           |  |  |

| AD60b        | TPCS               | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                    | 2.0 TAD   | —                                                     | 3.0 Tad | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111) not<br>selected |  |  |

| AD61b        | TPSS               | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>             | 2.0 Tad   | —                                                     | 3.0 Tad |       | _                                                         |  |  |

| AD62b        | Tcss               | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>        | _         | 0.5 Tad                                               | _       |       | _                                                         |  |  |

| AD63b        | Tdpu               | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup> | _         | —                                                     | 20      | μS    | _                                                         |  |  |

#### TABLE 25-45: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** TDPU is the time required for the ADC module to stabilize when it is turned on (AD1CON1<ADON> = 1). During this time, the ADC result is indeterminate.

### TABLE 25-46: DMA READ/WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS             |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |            |    |                                                                                                    |  |  |

|--------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|----|----------------------------------------------------------------------------------------------------|--|--|

| Param Characteristic           |                           | Min.                                                                                                                                                                                                                                                                                    | Тур | Max. Units |    | Conditions                                                                                         |  |  |

| DM1a                           | DMA Read/Write Cycle Time | —                                                                                                                                                                                                                                                                                       | _   | 2 Tcy      | ns | This characteristic applies to dsPIC33FJ256GPX06A/X08A/X10A devices only.                          |  |  |

| DM1b DMA Read/Write Cycle Time |                           | —                                                                                                                                                                                                                                                                                       | _   | 1 Тсү      | ns | This characteristic applies to all devices with the exception of the dsPIC33FJ256GPX06A/X08A/X10A. |  |  |

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |  |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|

| Param<br>No. Symbol   |                       | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | _   | 35  | ns    | _          |  |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  | —   | —   | ns    | _          |  |  |