Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K × 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 32x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp310at-i-pf |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

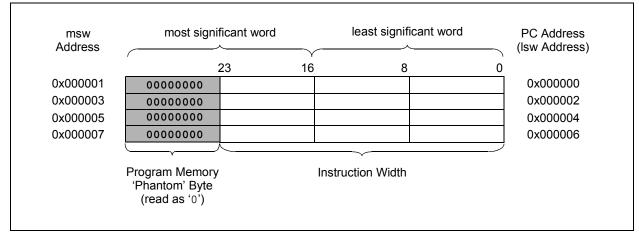

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXGPX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXGPX06A/X08A/X10A devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| TABLE 4-5: | INTERRUPT CONTROLLER REGISTER MAP |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Name A<br>INTCON1 0 | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13     |         |         |        |            |        |          |              |             |         |           |             |            |               |               |

|---------------------|-------------|--------|--------|------------|---------|---------|--------|------------|--------|----------|--------------|-------------|---------|-----------|-------------|------------|---------------|---------------|

|                     |             |        |        | 61113      | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8  | Bit 7    | Bit 6        | Bit 5       | Bit 4   | Bit 3     | Bit 2       | Bit 1      | Bit 0         | All<br>Resets |

| INTCON2 0           | 0080        | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE  | SFTACERR | DIV0ERR      | DMACERR     | MATHERR | ADDRERR   | STKERR      | OSCFAIL    | _             | 0000          |

|                     | 0082        | ALTIVT | DISI   | —          | _       | _       | _      | _          | _      | _        | _            | _           | INT4EP  | INT3EP    | INT2EP      | INT1EP     | INT0EP        | 0000          |

| IFS0 C              | 0084        | —      | DMA1IF | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF   | T2IF     | OC2IF        | IC2IF       | DMA0IF  | T1IF      | OC1IF       | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1 C              | 0086        | U2TXIF | U2RXIF | INT2IF     | T5IF    | T4IF    | OC4IF  | OC3IF      | DMA2IF | IC8IF    | IC7IF        | AD2IF       | INT1IF  | CNIF      | —           | MI2C1IF    | SI2C1IF       | 0000          |

| IFS2 C              | 8800        | T6IF   | DMA4IF | —          | OC8IF   | OC7IF   | OC6IF  | OC5IF      | IC6IF  | IC5IF    | IC4IF        | IC3IF       | DMA3IF  | C1IF      | C1RXIF      | SPI2IF     | SPI2EIF       | 0000          |

| IFS3 0              | 008A        | _      | _      | DMA5IF     | DCIIF   | DCIEIF  |        | _          | C2IF   | C2RXIF   | INT4IF       | INT3IF      | T9IF    | T8IF      | MI2C2IF     | SI2C2IF    | T7IF          | 0000          |

| IFS4 0              | 008C        | _      | _      | _          | _       | -       |        | _          | _      | C2TXIF   | C1TXIF       | DMA7IF      | DMA6IF  | _         | U2EIF       | U1EIF      | _             | 0000          |

| IEC0 C              | 0094        | _      | DMA1IE | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE   | T2IE     | OC2IE        | IC2IE       | DMA0IE  | T1IE      | OC1IE       | IC1IE      | INT0IE        | 0000          |

| IEC1 C              | 0096        | U2TXIE | U2RXIE | INT2IE     | T5IE    | T4IE    | OC4IE  | OC3IE      | DMA2IE | IC8IE    | IC7IE        | AD2IE       | INT1IE  | CNIE      | _           | MI2C1IE    | SI2C1IE       | 0000          |

| IEC2 C              | 0098        | T6IE   | DMA4IE | _          | OC8IE   | OC7IE   | OC6IE  | OC5IE      | IC6IE  | IC5IE    | IC4IE        | IC3IE       | DMA3IE  | C1IE      | C1RXIE      | SPI2IE     | SPI2EIE       | 0000          |

| IEC3 0              | 009A        | _      | _      | DMA5IE     | DCIIE   | DCIEIE  |        | _          | C2IE   | C2RXIE   | INT4IE       | INT3IE      | T9IE    | T8IE      | MI2C2IE     | SI2C2IE    | T7IE          | 0000          |

| IEC4 0              | 009C        | —      | —      | _          | —       | _       | _      | -          |        | C2TXIE   | C1TXIE       | DMA7IE      | DMA6IE  | —         | U2EIE       | U1EIE      |               | 0000          |

| IPC0 0              | 00A4        | —      |        | T1IP<2:0>  | •       | _       | (      | OC1IP<2:0  | )>     | —        |              | IC1IP<2:0>  |         | —         | 11          | NT0IP<2:0> |               | 4444          |

| IPC1 0              | 00A6        | —      |        | T2IP<2:0>  | •       | _       | (      | OC2IP<2:0  | )>     | —        |              | IC2IP<2:0>  |         | —         | DMA0IP<2:0> |            | 4444          |               |

| IPC2 0              | 00A8        | —      | L      | J1RXIP<2:( | )>      | _       | S      | SPI1IP<2:0 | )>     | —        | SPI1EIP<2:0> |             | —       | T3IP<2:0> |             |            | 4444          |               |

| IPC3 0              | 00AA        | —      | —      | _          | —       | _       | D      | MA1IP<2:   | 0>     | —        |              | AD1IP<2:0>  | •       | —         | U           | 1TXIP<2:0> | >             | 0444          |

| IPC4 0              | 00AC        | —      |        | CNIP<2:0>  | >       | —       | -      |            |        | —        | I            | MI2C1IP<2:0 | )>      | _         | SI          | 2C1IP<2:0  | >             | 4044          |

| IPC5 0              | 00AE        | —      |        | IC8IP<2:0> | >       | —       |        | IC7IP<2:0  | >      | —        |              | AD2IP<2:0>  | •       | _         | 11          | VT1IP<2:0> |               | 4444          |

| IPC6 0              | 00B0        | —      |        | T4IP<2:0>  | •       | —       | (      | C4IP<2:0   | )>     | —        |              | OC3IP<2:0>  | >       | _         | DI          | MA2IP<2:0  | >             | 4444          |

| IPC7 0              | 00B2        | _      | ι      | J2TXIP<2:0 | )>      | -       | U      | I2RXIP<2:  | 0>     | _        |              | INT2IP<2:0  | >       | _         |             | T5IP<2:0>  |               | 4444          |

| IPC8 0              | 00B4        | —      |        | C1IP<2:0>  | >       | —       | С      | 1RXIP<2:   | 0>     | —        |              | SPI2IP<2:0  | >       | _         | SF          | PI2EIP<2:0 | >             | 4444          |

| IPC9 0              | 00B6        | —      |        | IC5IP<2:0> | >       | —       |        | IC4IP<2:0  | >      | —        |              | IC3IP<2:0>  |         | _         | DI          | MA3IP<2:0  | >             | 4444          |

| IPC10 0             | 00B8        | —      | (      | OC7IP<2:0  | >       | —       | (      | C6IP<2:0   | )>     | —        |              | OC5IP<2:0>  | >       | _         | I           | C6IP<2:0>  |               | 4444          |

| IPC11 0             | 00BA        | —      |        | T6IP<2:0>  | •       | —       | D      | MA4IP<2:   | 0>     | —        | —            |             |         | _         | C           | 0C8IP<2:0> |               | 4404          |

| IPC12 0             | 00BC        | _      |        | T8IP<2:0>  | •       | -       | Μ      | II2C2IP<2: | 0>     | _        |              | SI2C2IP<2:0 | >       | _         |             | T7IP<2:0>  |               | 4444          |

| IPC13 0             | 00BE        | _      | C      | 2RXIP<2:0  | )>      | _       | I      | NT4IP<2:0  | )>     | -        |              | INT3IP<2:0  | >       | _         |             | T9IP<2:0>  |               | 4444          |

| IPC14 0             | 00C0        | _      | 0      | DCIEIP<2:0 | )>      | _       | _      | —          | —      | —        | —            | —           | —       | —         | (           | C2IP<2:0>  |               | 4004          |

| IPC15 0             | 00C2        | _      | —      | _          | —       | _       | _      | —          | _      | —        |              | DMA5IP<2:0  | >       | _         | [           | OCIIP<2:0> |               | 0044          |

| IPC16 0             | 00C4        | _      | —      | _          | —       | _       | l      | J2EIP<2:0  | >      | —        |              | U1EIP<2:0>  | •       | _         |             | —          | —             | 0440          |

| IPC17 0             | 00C6        | _      |        | C2TXIP<2:0 | )>      | _       | C      | 1TXIP<2:   | 0>     | _        |              | DMA7IP<2:0  | >       | _         | DMA6IP<2:0> |            | >             | 4444          |

| INTTREG 0           | 00E0        | _      | —      | —          | —       |         | ILR<   | 3:0>       |        | _        |              |             | VE      | CNUM<6:0> |             |            |               | 0000          |

© 2009-2012 Microchip Technology Inc.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: ADC1 REGISTER MAP

| File Name   | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7  | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0   | All<br>Resets |

|-------------|------|--------|-------------------|--------|---------|--------|-----------|---------|---------|--------|-----------|--------|--------|--------|-----------|-----------|---------|---------------|

| ADC1BUF0    | 0300 |        | ADC Data Buffer 0 |        |         |        |           |         |         |        | xxxx      |        |        |        |           |           |         |               |

| AD1CON1     | 0320 | ADON   | _                 | ADSIDL | ADDMABM | _      | AD12B     | FOR     | И<1:0>  | :      | SSRC<2:0> |        | _      | SIMSAM | ASAM      | SAMP      | DONE    | 0000          |

| AD1CON2     | 0322 | ١      | /CFG<2:0>         | >      | _       | _      | CSCNA     | CHP     | S<1:0>  | BUFS   | _         |        | SMPI   | <3:0>  |           | BUFM      | ALTS    | 0000          |

| AD1CON3     | 0324 | ADRC   |                   | —      |         | S      | AMC<4:0>  |         |         |        |           |        | ADCS   | 6<7:0> |           |           |         | 0000          |

| AD1CHS123   | 0326 | _      |                   | —      | _       |        | CH123N    | NB<1:0> | CH123SB |        |           |        | —      | —      | CH123N    | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0     | 0328 | CH0NB  |                   | —      |         | CI     | H0SB<4:0> | >       |         | CH0NA  |           |        |        | (      | CH0SA<4:( | )>        |         | 0000          |

| AD1PCFGH(1) | 032A | PCFG31 | PCFG30            | PCFG29 | PCFG28  | PCFG27 | PCFG26    | PCFG25  | PCFG24  | PCFG23 | PCFG22    | PCFG21 | PCFG20 | PCFG19 | PCFG18    | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL    | 032C | PCFG15 | PCFG14            | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7  | PCFG6     | PCFG5  | PCFG4  | PCFG3  | PCFG2     | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)  | 032E | CSS31  | CSS30             | CSS29  | CSS28   | CSS27  | CSS26     | CSS25   | CSS24   | CSS23  | CSS22     | CSS21  | CSS20  | CSS19  | CSS18     | CSS17     | CSS16   | 0000          |

| AD1CSSL     | 0330 | CSS15  | CSS14             | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7   | CSS6      | CSS5   | CSS4   | CSS3   | CSS2      | CSS1      | CSS0    | 0000          |

| AD1CON4     | 0332 | _      | _                 | _      | —       | _      | _         | _       | _       | _      | _         | _      | _      | _      | [         | DMABL<2:( | )>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3        | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|--------|----------|---------|---------|----------|----------|-------|-------|--------------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        | ADC Data  |        |         |        |          |         |         | Buffer 0 |          |       |       |              |        |          | xxxx    |               |

| AD2CON1   | 0360 | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B    | FORI    | M<1:0>  | Ş        | SSRC<2:0 | >     | _     | SIMSAM       | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 | Ň      | VCFG<2:0> | >      | _       | _      | CSCNA    | CHP     | S<1:0>  | BUFS     | _        |       | SMPI  | <3:0>        |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | S      | AMC<4:0> |         |         |          |          |       | ADC   | S<7:0>       |        |          |         | 0000          |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _      | CH123N   | IB<1:0> | CH123SB | _        | _        | _     | _     | _            | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |        | CH0S     | B<3:0>  |         | CH0NA    | _        | _     | _     | — CH0SA<3:0> |        |          |         | 0000          |

| Reserved  | 036A | _      | _         | _      | _       | _      | _        | _       | _       | _        | _        | _     | _     | _            | _      | _        | _       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10   | PCFG9   | PCFG8   | PCFG7    | PCFG6    | PCFG5 | PCFG4 | PCFG3        | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E | _      | _         | _      | _       | _      | _        | _       | _       | _        | _        | _     | _     | _            | _      | _        | _       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8    | CSS7     | CSS6     | CSS5  | CSS4  | CSS3         | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       |        | _        | _       | _       | _        | _        | _     | _     | _            |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | See Notes        |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        | _                     |               | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | Tstartup + Trst        | TOST + TLOCK          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | Trst                   | _                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | —             | 3                |

| Software        | Any Clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | —             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay (10 μs nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- **3:** TRST = Internal state Reset time (20 μs nominal).

- **4:** Tos⊤ = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL lock time (20 μs nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

<sup>© 2009-2012</sup> Microchip Technology Inc.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | <ol> <li>Stack error trap has occurred</li> </ol>  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|---------------|-------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| —             |                   | T1IP<2:0>                                |                |                   |                 | OC1IP<2:0>      |       |

| bit 15        |                   |                                          |                |                   |                 |                 | bi    |

|               |                   |                                          |                |                   |                 |                 |       |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _             |                   | IC1IP<2:0>                               |                |                   |                 | INT0IP<2:0>     |       |

| bit 7         |                   |                                          |                |                   |                 |                 | bi    |

| Legend:       |                   |                                          |                |                   |                 |                 |       |

| R = Readabl   | e bit             | W = Writable I                           | bit            | U = Unimple       | mented bit, rea | id as '0'       |       |

| -n = Value at | POR               | '1' = Bit is set                         |                | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|               |                   |                                          |                |                   |                 |                 |       |

| bit 15        | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 14-12     | T1IP<2:0>:        | Timer1 Interrupt                         | Priority bits  |                   |                 |                 |       |

|               | 111 = Interr      | rupt is priority 7 (ł                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1<br>upt source is dis   | abled          |                   |                 |                 |       |

| bit 11        |                   | ented: Read as '                         |                |                   |                 |                 |       |

| bit 10-8      | -                 | >: Output Compa                          |                | 1 Interrupt Prior | ritv bits       |                 |       |

|               |                   | upt is priority 7 (I                     |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | 001 = Interr      | upt is priority 1                        |                |                   |                 |                 |       |

|               |                   | upt source is dis                        | abled          |                   |                 |                 |       |

| bit 7         | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 6-4       |                   | : Input Capture C                        |                |                   | oits            |                 |       |

|               | 111 = Interr      | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1                        | ablad          |                   |                 |                 |       |

| bit 3         |                   | upt source is disa<br>ented: Read as 'o  |                |                   |                 |                 |       |

| bit 2-0       | -                 |                                          |                | , bite            |                 |                 |       |

| DIL 2-0       |                   | External Interr<br>upt is priority 7 (I) |                |                   |                 |                 |       |

|               | •                 |                                          | gricot priori  | , monuply         |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •<br>001 - Interr | upt is priority 1                        |                |                   |                 |                 |       |

|               |                   |                                          |                |                   |                 |                 |       |

| REGISTER      | 7-21: IPC6       |                                           | PRIORITY       | CONTROL R        | EGISTER 6        |                 |         |

|---------------|------------------|-------------------------------------------|----------------|------------------|------------------|-----------------|---------|

| U-0           | R/W-1            | R/W-0                                     | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0   |

|               |                  | T4IP<2:0>                                 |                | —                |                  | OC4IP<2:0>      |         |

| bit 15        |                  |                                           |                |                  |                  |                 | bit     |

| U-0           | R/W-1            | R/W-0                                     | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0   |

| 0-0           | 10,00-1          | OC3IP<2:0>                                | 10.00-0        | 0-0              |                  | DMA2IP<2:0>     | 10.00-0 |

| bit 7         |                  | 00011 \2.02                               |                |                  |                  |                 | bit     |

|               |                  |                                           |                |                  |                  |                 |         |

| Legend:       |                  |                                           |                |                  |                  |                 |         |

| R = Readabl   |                  | W = Writable I                            | oit            |                  | mented bit, re   |                 |         |

| -n = Value at | POR              | '1' = Bit is set                          |                | '0' = Bit is cl  | eared            | x = Bit is unkn | own     |

| bit 15        | Unimpleme        | ented: Read as '0                         | )'             |                  |                  |                 |         |

| bit 14-12     | T4IP<2:0>:       | Timer4 Interrupt                          | Priority bits  |                  |                  |                 |         |

|               |                  | rupt is priority 7 (h                     |                | ty interrupt)    |                  |                 |         |

|               | •                |                                           | •              |                  |                  |                 |         |

|               | •                |                                           |                |                  |                  |                 |         |

|               | •<br>001 - Inter | rupt is priority 1                        |                |                  |                  |                 |         |

|               |                  | rupt source is disa                       | abled          |                  |                  |                 |         |

| bit 11        |                  | ented: Read as 'd                         |                |                  |                  |                 |         |

| bit 10-8      | OC4IP<2:0        | >: Output Compa                           | re Channel 4   | 4 Interrupt Prio | rity bits        |                 |         |

|               | 111 = Inter      | rupt is priority 7 (ł                     | nighest priori | ty interrupt)    |                  |                 |         |

|               | •                |                                           |                |                  |                  |                 |         |

|               | •                |                                           |                |                  |                  |                 |         |

|               | •<br>001 = Inter | rupt is priority 1                        |                |                  |                  |                 |         |

|               |                  | rupt source is disa                       | abled          |                  |                  |                 |         |

| bit 7         |                  | ented: Read as '0                         |                |                  |                  |                 |         |

| bit 6-4       | -                | >: Output Compa                           |                | 3 Interrupt Prio | rity bits        |                 |         |

|               |                  | rupt is priority 7 (h                     |                | •                |                  |                 |         |

|               | •                |                                           | •              |                  |                  |                 |         |

|               | •                |                                           |                |                  |                  |                 |         |

|               | •<br>001 = Inter | rupt is priority 1                        |                |                  |                  |                 |         |

|               |                  | rupt source is disa                       | abled          |                  |                  |                 |         |

| bit 3         |                  | ented: Read as 'd                         |                |                  |                  |                 |         |

| bit 2-0       | -                | :0>: DMA Channe                           |                | nsfer Complete   | e Interrupt Pric | prity bits      |         |

|               |                  | rupt is priority 7 (h                     |                |                  |                  |                 |         |

|               | •                | · · · · · · · · · · · · · · · · · · ·     |                | ·) ·······       |                  |                 |         |

|               | •                |                                           |                |                  |                  |                 |         |

|               | •<br>001 - Inter | rupt in priority 4                        |                |                  |                  |                 |         |

|               |                  | rupt is priority 1<br>rupt source is disa | abled          |                  |                  |                 |         |

|               |                  |                                           |                |                  |                  |                 |         |

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXGPX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INT0               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| DCI                | 60         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte sized data transfers

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral

- Indirect Addressing of DMA RAM locations with or without automatic post-increment

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral

- One-Shot Block Transfers Terminating DMA transfer after one block transfer

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately

- Automatic or manual initiation of block transfers

- Each channel can select from 20 possible sources of data sources or destinations

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

| U-0          | U-0                                                                                                         | U-0                                                              | U-0   | U-0              | U-0             | U-0                | R/W-0 <sup>(1)</sup> |  |

|--------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------------------|-----------------|--------------------|----------------------|--|

|              | _                                                                                                           |                                                                  | _     | _                | _               | _                  | PLLDIV<8>            |  |

| bit 15       | ·                                                                                                           | ·                                                                | ·     | •                | •               | •                  | bit 8                |  |

| R/W-0        | R/W-0                                                                                                       | R/W-1                                                            | R/W-1 | R/W-0            | R/W-0           | R/W-0              | R/W-0                |  |

| R/W-U        | R/W-0                                                                                                       | R/ W- I                                                          |       | IV<7:0>          | R/W-0           | R/ W-U             | R/W-0                |  |

| bit 7        |                                                                                                             |                                                                  | FLLD  | 10~7.02          |                 |                    | bit 0                |  |

|              |                                                                                                             |                                                                  |       |                  |                 |                    | DILU                 |  |

| Legend:      |                                                                                                             |                                                                  |       |                  |                 |                    |                      |  |

| R = Readab   | le bit                                                                                                      | W = Writable                                                     | bit   | U = Unimple      | mented bit, rea | d as '0'           |                      |  |

|              |                                                                                                             |                                                                  |       |                  |                 | x = Bit is unknown |                      |  |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | ared            | x = Bit is unl     | known                |  |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | eared           | x = Bit is unl     | known                |  |

| -n = Value a |                                                                                                             | '1' = Bit is set                                                 | -     | ʻ0' = Bit is cle | ared            | x = Bit is unl     | known                |  |

|              | Unimpleme                                                                                                   |                                                                  | ʻ0'   |                  |                 |                    | known                |  |

| bit 15-9     | Unimpleme                                                                                                   | nted: Read as '                                                  | ʻ0'   |                  |                 |                    | known                |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                    | known                |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                    | (nown                |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                    | (nown                |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as '                                                  | ʻ0'   |                  |                 |                    | (nown                |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                    | <u>known</u>         |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                    | <u>known</u>         |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                    | <u>Known</u>         |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)        | ʻ0'   |                  |                 |                    | <u>Known</u>         |  |

| bit 15-9     | Unimplemen<br>PLLDIV<8:0<br>111111111<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)<br>= 4 | ʻ0'   |                  |                 |                    | <u>Known</u>         |  |

Note 1: This is register is reset only on a Power-on Reset (POR).

### 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU stops executing instructions

- · The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

## 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLK-DIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLK-DIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLK-DIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

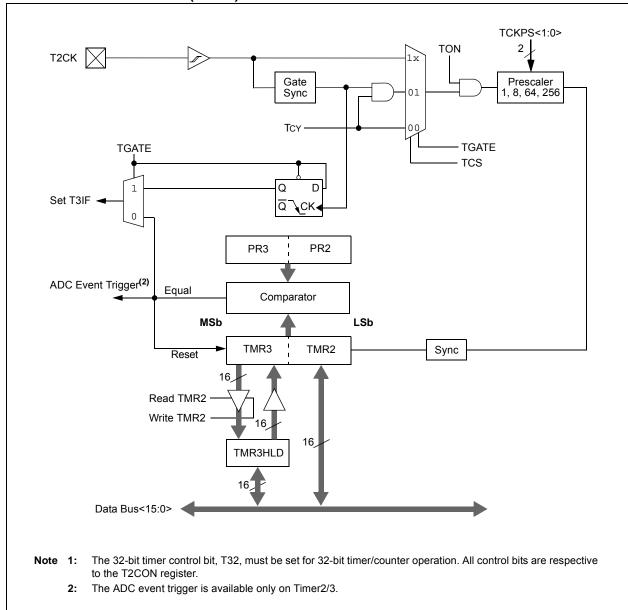

## FIGURE 13-1: TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup>

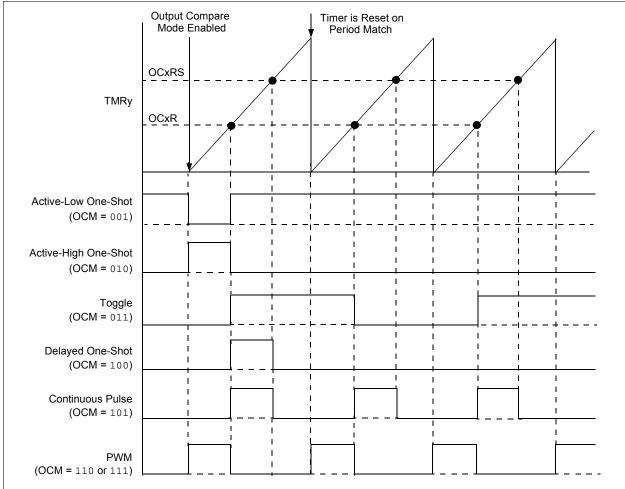

## 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"      |

|-------|---------------------------------------|

|       | (DS70209) in the "dsPIC33F/PIC24H     |

|       | Family Reference Manual" for OCxR and |

|       | OCxRS register restrictions.          |

| OCM<2:0> | Mode                         | OCx Pin Initial State                            | OCx Interrupt Generation         |

|----------|------------------------------|--------------------------------------------------|----------------------------------|

| 000      | Module Disabled              | Controlled by GPIO register                      | _                                |

| 001      | Active-Low One-Shot          | 0                                                | OCx rising edge                  |

| 010      | Active-High One-Shot         | 1                                                | OCx falling edge                 |

| 011      | Toggle                       | Current output is maintained                     | OCx rising and falling edge      |

| 100      | Delayed One-Shot             | 0                                                | OCx falling edge                 |

| 101      | Continuous Pulse             | 0                                                | OCx falling edge                 |

| 110      | PWM without Fault Protection | ʻ0', if OCxR is zero<br>ʻ1', if OCxR is non-zero | No interrupt                     |

| 111      | PWM with Fault Protection    | ʻ0', if OCxR is zero<br>ʻ1', if OCxR is non-zero | OCFA falling edge for OC1 to OC4 |

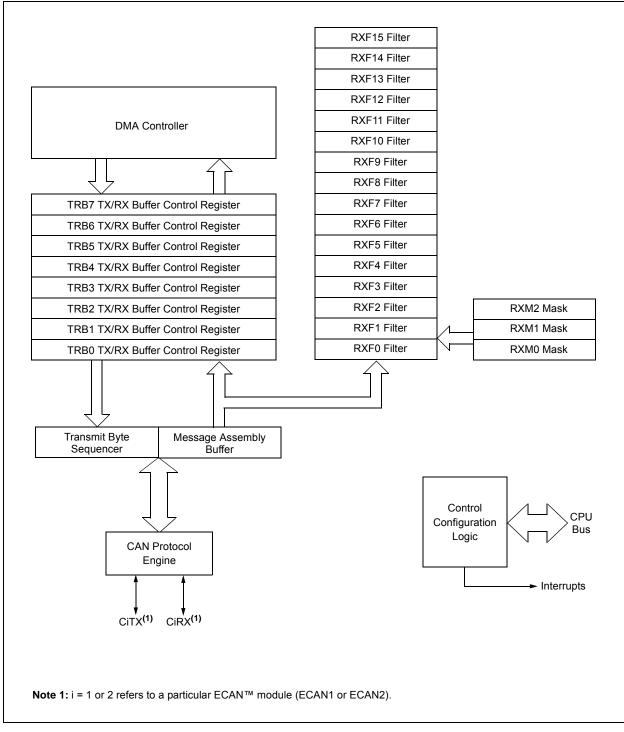

## FIGURE 19-1: ECAN™ MODULE BLOCK DIAGRAM

## **19.3 Modes of Operation**

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

## 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

## 19.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

## 19.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

## 19.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

## 19.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

### REGISTER 19-2: CiCTRL2: ECAN™ CONTROL REGISTER 2

| U-0          | U-0                 | U-0                       | U-0             | U-0                                | U-0        | U-0                | U-0   |  |  |  |

|--------------|---------------------|---------------------------|-----------------|------------------------------------|------------|--------------------|-------|--|--|--|

| _            | —                   | —                         | _               | —                                  | —          | —                  | _     |  |  |  |

| bit 15       |                     |                           |                 |                                    |            |                    | bit 8 |  |  |  |

|              |                     |                           |                 |                                    |            |                    |       |  |  |  |

| U-0          | U-0                 | U-0                       | R-0             | R-0                                | R-0        | R-0                | R-0   |  |  |  |

| —            | —                   | _                         |                 |                                    | DNCNT<4:0> |                    |       |  |  |  |

| bit 7        |                     |                           |                 |                                    |            |                    | bit 0 |  |  |  |

|              |                     |                           |                 |                                    |            |                    |       |  |  |  |

| Legend:      |                     |                           |                 |                                    |            |                    |       |  |  |  |

| R = Readat   | ole bit             | W = Writable              | bit             | U = Unimplemented bit, read as '0' |            |                    |       |  |  |  |

| -n = Value a | at POR              | '1' = Bit is set          |                 | '0' = Bit is cle                   | ared       | x = Bit is unknown |       |  |  |  |

|              |                     |                           |                 |                                    |            |                    |       |  |  |  |

| bit 15-5     | Unimplemen          | ted: Read as '            | 0'              |                                    |            |                    |       |  |  |  |

| bit 4-0      | DNCNT<4:0>          | <b>-:</b> DeviceNet™      | Filter Bit Num  | iber bits                          |            |                    |       |  |  |  |

|              | 11111 = Inv         | alid selection            |                 |                                    |            |                    |       |  |  |  |

|              | •                   |                           |                 |                                    |            |                    |       |  |  |  |

|              | •                   |                           |                 |                                    |            |                    |       |  |  |  |

|              | •                   |                           |                 |                                    |            |                    |       |  |  |  |

|              | 10010 <b>= Inva</b> | 10010 = Invalid selection |                 |                                    |            |                    |       |  |  |  |

|              | 10001 = Con         | npare up to dat           | a byte 3, bit 6 | with EID<17>                       |            |                    |       |  |  |  |

|              | •                   |                           |                 |                                    |            |                    |       |  |  |  |

|              | •                   |                           |                 |                                    |            |                    |       |  |  |  |

|              | 00001 = Con         | npare up to dat           | a bvte 1. bit 7 | with EID<0>                        |            |                    |       |  |  |  |

|              |                     |                           |                 |                                    |            |                    |       |  |  |  |

00000 = Do not compare data bytes

| REGISTER 19-7: CiINTE: ECAN™ INTERRUPT ENABLE REGISTER |                               |                                                                                      |                |                  |                  |                 |                |  |  |  |  |

|--------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|----------------|--|--|--|--|

| U-0                                                    | U-0                           | U-0                                                                                  | U-0            | U-0              | U-0              | U-0             | U-0            |  |  |  |  |

|                                                        |                               |                                                                                      | _              |                  |                  |                 |                |  |  |  |  |

| bit 15                                                 |                               |                                                                                      |                |                  |                  |                 | bit            |  |  |  |  |

| <b>D</b> 444 0                                         | 5444.0                        | <b>D</b> 444 0                                                                       |                | <b>D</b> 444 0   | Dates            | Dates           | <b>D N N O</b> |  |  |  |  |

| R/W-0                                                  | R/W-0                         | R/W-0                                                                                | U-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |

| IVRIE<br>bit 7                                         | WAKIE                         | ERRIE                                                                                | —              | FIFOIE           | RBOVIE           | RBIE            | TBIE           |  |  |  |  |

|                                                        |                               |                                                                                      |                |                  |                  |                 | DI             |  |  |  |  |

| Legend:                                                |                               |                                                                                      |                |                  |                  |                 |                |  |  |  |  |

| R = Readabl                                            | e bit                         | W = Writable                                                                         | bit            | U = Unimpler     | mented bit, read | l as '0'        |                |  |  |  |  |

| -n = Value at                                          | POR                           | '1' = Bit is set                                                                     |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown           |  |  |  |  |

| hit 15 0                                               | Unimplomor                    | ted. Dood oo f                                                                       | o,'            |                  |                  |                 |                |  |  |  |  |

| bit 15-8                                               | -                             | nted: Read as '                                                                      |                |                  |                  |                 |                |  |  |  |  |

| bit 7                                                  |                               | d Message Inter                                                                      | •              | bit              |                  |                 |                |  |  |  |  |

|                                                        |                               | <ol> <li>Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol> |                |                  |                  |                 |                |  |  |  |  |

|                                                        |                               | •                                                                                    |                |                  |                  |                 |                |  |  |  |  |

| bit 6                                                  |                               | Wake-up Activi                                                                       |                | nable bit        |                  |                 |                |  |  |  |  |

|                                                        |                               | request enable                                                                       |                |                  |                  |                 |                |  |  |  |  |

|                                                        | -                             | request not ena                                                                      |                |                  |                  |                 |                |  |  |  |  |

| bit 5                                                  |                               | Interrupt Enab                                                                       |                |                  |                  |                 |                |  |  |  |  |

|                                                        |                               | request enable                                                                       |                |                  |                  |                 |                |  |  |  |  |

|                                                        | 0 = Interrupt                 | request not ena                                                                      | abled          |                  |                  |                 |                |  |  |  |  |

| bit 4                                                  | Unimplemen                    | nted: Read as '                                                                      | 0'             |                  |                  |                 |                |  |  |  |  |

| bit 3                                                  | FIFOIE: FIFO                  | O Almost Full In                                                                     | terrupt Enabl  | e bit            |                  |                 |                |  |  |  |  |

|                                                        | 1 = Interrupt request enabled |                                                                                      |                |                  |                  |                 |                |  |  |  |  |

|                                                        | 0 = Interrupt                 | request not ena                                                                      | abled          |                  |                  |                 |                |  |  |  |  |

| bit 2                                                  | RBOVIE: RX                    | Buffer Overflow                                                                      | v Interrupt Er | nable bit        |                  |                 |                |  |  |  |  |

|                                                        | 1 = Interrupt request enabled |                                                                                      |                |                  |                  |                 |                |  |  |  |  |

|                                                        | 0 = Interrupt                 | request not ena                                                                      | abled          |                  |                  |                 |                |  |  |  |  |

| bit 1                                                  |                               | iffer Interrupt Er                                                                   |                |                  |                  |                 |                |  |  |  |  |

|                                                        |                               | request enable                                                                       |                |                  |                  |                 |                |  |  |  |  |

|                                                        | 0 = Interrupt                 | request not ena                                                                      | abled          |                  |                  |                 |                |  |  |  |  |

| bit 0                                                  |                               | ffer Interrupt En                                                                    |                |                  |                  |                 |                |  |  |  |  |

|                                                        |                               | request enable                                                                       |                |                  |                  |                 |                |  |  |  |  |

|                                                        | 0 = Interrupt                 | request not ena                                                                      | abled          |                  |                  |                 |                |  |  |  |  |

## REGISTER 19-7: CIINTE: ECAN™ INTERRUPT ENABLE REGISTER

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                               |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size                                                                                                                                                                                                         |

|           |          |                | (FOR 128K and 256K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                                                      |

|           |          |                | Secure space is 8K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                             |

|           |          |                | Secure space is 16K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>001 = High security; secure program Flash segment starts at End of BS,                                                |

|           |          |                | ends at 0x007FFE                                                                                                                                                                                                                                          |

|           |          |                | Secure space is 32K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x00FFFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x00FFFE                            |

|           |          |                | (FOR 64K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                                                                |

|           |          |                | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x001FFE                             |

|           |          |                | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                             |

|           |          |                | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 007FFEh<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE                             |