Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

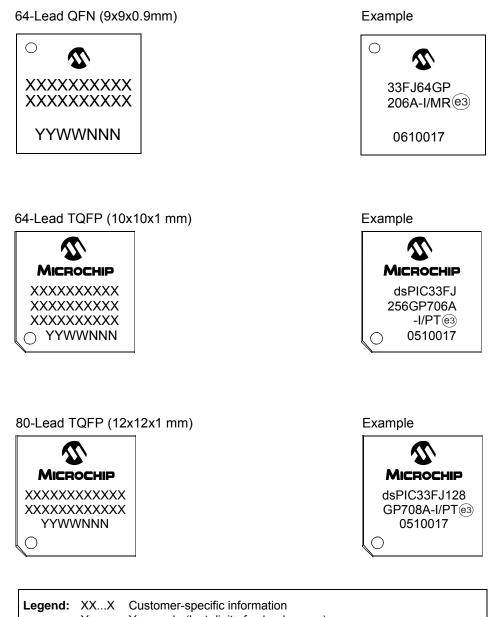

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp708a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.4 CPU Control Registers

CPU control registers include:

- SR: CPU Status Register

- CORCON: Core Control Register

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                  | R-0                     | R/C-0                                  | R/C-0             | R-0              | R/C-0              | R -0            | R/W-0      |

|----------------------|-------------------------|----------------------------------------|-------------------|------------------|--------------------|-----------------|------------|

| OA                   | OB                      | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB              | SAB                | DA              | DC         |

| bit 15               |                         |                                        |                   |                  |                    |                 | bit 8      |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup>                   |                   | DAALO            |                    |                 |            |

| R/W-0-/              | IPL<2:0> <sup>(2)</sup> | R/W-0(**                               | R-0<br>RA         | R/W-0            | R/W-0<br>OV        | R/W-0<br>Z      | R/W-0<br>C |

| bit 7                | IFL~2.0× 7              |                                        | Γ.A               | IN               | 00                 | 2               | bit (      |

|                      |                         |                                        |                   |                  |                    |                 | Dit        |

| Legend:              |                         |                                        |                   |                  |                    |                 |            |

| C = Clear only       | bit                     | R = Readable                           | bit               | U = Unimpler     | mented bit, read   | as '0'          |            |

| S = Set only bi      | t                       | W = Writable                           | bit               | -n = Value at    | POR                |                 |            |

| '1' = Bit is set     |                         | '0' = Bit is clea                      | ared              | x = Bit is unk   | nown               |                 |            |

|                      |                         |                                        |                   |                  |                    |                 |            |

| bit 15               |                         | ator A Overflov                        |                   |                  |                    |                 |            |

|                      |                         | ator A overflowe<br>ator A has not o   |                   |                  |                    |                 |            |

| bit 14               |                         | ator B Overflov                        |                   |                  |                    |                 |            |

|                      | 1 = Accumula            | ator B overflowe                       | ed                |                  |                    |                 |            |

|                      |                         | ator B has not c                       |                   |                  |                    |                 |            |

| bit 13               |                         | ator A Saturatio                       |                   |                  |                    |                 |            |

|                      |                         | ator A is saturat<br>ator A is not sat |                   | en saturated at  | some time          |                 |            |

| bit 12               |                         | ator B Saturatio                       |                   | tus bit(1)       |                    |                 |            |

| Sit 12               |                         | ator B is saturat                      | -                 |                  | some time          |                 |            |

|                      | 0 = Accumula            | ator B is not sat                      | urated            |                  |                    |                 |            |

| bit 11               | <b>OAB:</b> OA    C     | B Combined A                           | ccumulator C      | verflow Status   | bit                |                 |            |

|                      |                         | ators A or B have                      |                   |                  |                    |                 |            |

| bit 10               |                         | ccumulators A<br>B Combined Ac         |                   |                  |                    |                 |            |

|                      |                         |                                        |                   | -                | urated at some     | time in the pas | t          |

|                      |                         | ccumulator A o                         |                   |                  |                    |                 | •          |

|                      | Note: T                 | his bit may be r                       | ead or cleare     | d (not set). Cle | aring this bit wil | I clear SA and  | SB.        |

| bit 9                | DA: DO Loop             | Active bit                             |                   |                  |                    |                 |            |

|                      | 1 = DO <b>loop</b> ir   | n progress<br>ot in progress           |                   |                  |                    |                 |            |

|                      |                         |                                        |                   |                  |                    |                 |            |

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

| TABLE 4   | I-17: | DMA    | REGIS  | TER M  | AP (CO | NTINUE | D)     |        |        |           |        |        |        |           |        |        |        |              |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|--------------|

| File Name | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Reset |

| DMA5CNT   | 03C6  | _      | _      | _      | _      | _      | _      |        |        |           |        | CN1    | <9:0>  |           |        |        |        | 0000         |

| DMA6CON   | 03C8  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _      | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000         |

| DMA6REQ   | 03CA  | FORCE  | _      | _      | _      | _      | —      | —      | _      | _         |        |        |        | RQSEL<6:0 | >      |        |        | 0000         |

| DMA6STA   | 03CC  |        |        |        |        |        |        |        | S      | TA<15:0>  |        |        |        |           |        |        |        | 0000         |

| DMA6STB   | 03CE  |        |        |        |        |        |        |        |        |           |        |        | 0000   |           |        |        |        |              |

| DMA6PAD   | 03D0  |        |        |        |        |        |        |        |        |           |        |        |        |           | 0000   |        |        |              |

| DMA6CNT   | 03D2  | _      | _      | _      | _      | _      | _      |        |        |           |        | CN1    | <9:0>  |           |        |        |        | 0000         |

| DMA7CON   | 03D4  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |        | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000         |

| DMA7REQ   | 03D6  | FORCE  | —      | _      | _      | _      | _      |        | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000         |

| DMA7STA   | 03D8  |        | •      | •      | •      |        |        |        | S      | TA<15:0>  | •      |        |        |           |        |        |        | 0000         |

| DMA7STB   | 03DA  |        |        |        |        |        |        |        | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000         |

| DMA7PAD   | 03DC  |        |        |        |        |        |        |        | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000         |

| DMA7CNT   | 03DE  | _      | _      | _      | _      | _      | —      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000         |

| DMACS0    | 03E0  | PWCOL7 | PWCOL6 | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000         |

| DMACS1    | 03E2  | —      | _      | _      | _      |        | LSTCH  | 1<3:0> |        | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000         |

| DSADR     | 03E4  |        |        |        |        | •      |        |        | DS     | ADR<15:0> |        | 1      | 1      | 1         |        | 1      | 1      | 0000         |

| امعمماه   |       |        |        |        |        |        |        |        |        |           |        |        |        |           |        |        |        |              |

### \_\_\_\_\_

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

dsPIC33FJXXXGPX06A/X08A/X10A

| File Name  | Addr          | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                         | Bit 8                         | Bit 7                 | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|------------------------|--------|--------|--------|--------|-------------------------------|-------------------------------|-----------------------|----------|--------|--------|--------|-------|--------|--------|---------------|

|            | 0400-<br>041E |        |                        |        |        |        |        |                               | See definit                   | ion when V            | /IN = x  |        |        |        |       |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BP                   | <3:0>  |        |        | F2BF   | ><3:0>                        |                               |                       | F1BP     | <3:0>  |        |        | F0BP  | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BP                   | <3:0>  |        |        | F6BF   | ><3:0>                        |                               |                       | F5BP     | <3:0>  |        |        | F4BP  | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11BF                  | ><3:0> |        |        | F10B   | P<3:0>                        |                               |                       | F9BP     | <3:0>  |        |        | F8BP  | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15BF                  | P<3:0> |        |        | F14B   | P<3:0>                        |                               |                       | F13B     | P<3:0> |        |        | F12BF | °<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | MIDE   | _     | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   | •     |        |        | xxxx          |

| C1RXM1SID  | 0434          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | MIDE   | —     | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   | •     |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | MIDE   | _     | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       | •      |        | xxxx          |

| C1RXF0SID  | 0440          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | _      | EXIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        | SID<10:3><br>EID<15:8> |        |        |        |        |                               | EID<7:0>                      |                       |          |        |        |        |       | xxxx   |        |               |

| C1RXF1SID  | 0444          |        | SID<10:3>              |        |        |        |        |                               |                               | SID<2:0>              |          | _      | EXIDE  | _      | EID<  | 17:16> | xxxx   |               |

| C1RXF1EID  | 0446          |        | EID<10:3>              |        |        |        |        |                               |                               |                       |          | EID<   | 7:0>   |        |       |        | xxxx   |               |

| C1RXF2SID  | 0448          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | EXIDE  |       | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |                        |        | EID<   | :15:8> |        |                               |                               | EID<7:0>              |          |        |        |        |       |        | xxxx   |               |

| C1RXF3SID  | 044C          |        |                        |        | SID<   | :10:3> |        |                               |                               | SID<2:0> — EXIDE — EI |          |        |        |        | EID<  | 17:16> | xxxx   |               |

| C1RXF3EID  | 044E          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF4SID  | 0450          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | _      | EXIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF5SID  | 0454          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | EXIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | EXIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | EXIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF8SID  | 0460          |        | SID<10:3>              |        |        |        |        |                               | SID<2:0> — EXIDE — EID<17:16> |                       |          |        |        | 17:16> | xxxx  |        |        |               |

| C1RXF8EID  | 0462          |        | EID<15:8>              |        |        |        |        |                               | EID<7:0>                      |                       |          |        |        |        |       | xxxx   |        |               |

| C1RXF9SID  | 0464          |        |                        |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |                               |                       |          |        | 17:16> | xxxx   |       |        |        |               |

| C1RXF9EID  | 0466          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

| C1RXF10SID | 0468          |        |                        |        | SID<   | :10:3> |        |                               |                               |                       | SID<2:0> |        | —      | EXIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |                        |        | EID<   | :15:8> |        |                               |                               |                       |          |        | EID<   | 7:0>   |       |        |        | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name  | Addr | Bit 15       | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7                        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------------|-----------|--------|--------|--------|--------|-------|----------|------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C2RXF10EID | 056A |              |           |        | EID<   | 15:8>  |        |       |          |                              |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF11SID | 056C |              |           |        | SID<   | 10:3>  |        |       |          |                              | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF11EID | 056E |              | EID<15:8> |        |        |        |        |       |          | EID<7:0>                     |          |       |       |       |       | xxxx  |       |               |

| C2RXF12SID | 0570 |              | SID<10:3> |        |        |        |        |       |          | SID<2:0> — EXIDE — EID<17:16 |          |       |       |       |       | 7:16> | xxxx  |               |

| C2RXF12EID | 0572 |              |           |        | EID<   | 15:8>  |        |       |          | EID<7:0>                     |          |       |       |       |       |       | xxxx  |               |

| C2RXF13SID | 0574 |              |           |        | SID<   | 10:3>  |        |       |          | SID<2:0> — EXIDE — EID<17:1  |          |       |       |       |       | 7:16> | xxxx  |               |

| C2RXF13EID | 0576 |              |           |        | EID<   | 15:8>  |        |       |          |                              |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF14SID | 0578 |              |           |        | SID<   | 10:3>  |        |       |          |                              | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF14EID | 057A |              |           |        | EID<   | 15:8>  |        |       |          |                              |          |       | EID<  | <7:0> |       |       |       | xxxx          |

| C2RXF15SID | 057C |              | SID<10:3> |        |        |        |        |       |          |                              | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C2RXF15EID | 057E | 7E EID<15:8> |           |        |        |        |        |       | EID<7:0> |                              |          |       |       |       | xxxx  |       |       |               |

#### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR dsPIC33FJXXXGP706A/708A/710A DEVICES ONLY (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

SR: CPU STATUS REGISTER<sup>(1)</sup>

| R-0                  | R-0                  | R/C-0                | R/C-0 | R-0           | R/C-0            | R -0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|---------------|------------------|--------|-------|

| OA                   | OB                   | SA                   | SB    | OAB           | SAB              | DA     | DC    |

| bit 15               |                      | ÷                    |       |               |                  |        | bit 8 |

|                      |                      |                      |       |               |                  |        |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0         | R/W-0            | R/W-0  | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N             | OV               | Z      | С     |

| bit 7                |                      |                      |       |               |                  |        | bit 0 |

|                      |                      |                      |       |               |                  |        |       |

| Legend:              |                      |                      |       |               |                  |        |       |

| C = Clear only       | bit                  | R = Readable         | bit   | U = Unimple   | mented bit, read | as '0' |       |

| S = Set only bi      | t                    | W = Writable         | bit   | -n = Value at | POR              |        |       |

|                      |                      |                      |       |               |                  |        |       |

x = Bit is unknown

bit 7-5

1' = Bit is set

**REGISTER 7-1:**

### IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

'0' = Bit is cleared

- 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0          | U-0                | R/W-0            | R/W-0                | R-0             | R-0              | R-0   |

|------------------|--------------|--------------------|------------------|----------------------|-----------------|------------------|-------|

|                  |              |                    | US               | EDT                  |                 | DL<2:0>          |       |

| bit 15           |              |                    |                  |                      |                 |                  | bit 8 |

|                  |              |                    |                  |                      |                 |                  |       |

| R/W-0            | R/W-0        | R/W-1              | R/W-0            | R/C-0                | R/W-0           | R/W-0            | R/W-0 |

| SATA             | SATB         | SATDW              | ACCSAT           | IPL3 <sup>(2)</sup>  | PSV             | RND              | IF    |

| bit 7            |              |                    |                  |                      |                 |                  | bit 0 |

| Legend:          |              | C = Clear onl      | y bit            |                      |                 |                  |       |

| R = Readable     | bit          | W = Writable       | bit              | -n = Value at        | POR             | '1' = Bit is set |       |

| 0' = Bit is clea | ired         | 'x = Bit is unk    | nown             | U = Unimpler         | mented bit, rea | id as '0'        |       |

|                  |              |                    |                  |                      |                 |                  |       |

| bit 3            | IPL3: CPU Ir | terrupt Priority   | Level Status I   | bit 3 <sup>(2)</sup> |                 |                  |       |

|                  | 1 = CPU inte | rrupt priority lev | /el is greater t | han 7                |                 |                  |       |

|                  | 0 = CPU inte | rrupt priority lev | el is 7 or less  | ;                    |                 |                  |       |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| R/W-0         | R/W-0          | U-0                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|----------------|---------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IF          | DMA4IF         |                                 | OC8IF            | OC7IF            | OC6IF            | OC5IF           | IC6IF   |

| bit 15        |                |                                 |                  |                  | •                |                 | bit     |

|               |                |                                 |                  |                  |                  |                 |         |

| R/W-0         | R/W-0          | R/W-0                           | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                           | DMA3IF           | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |

| bit 7         |                |                                 |                  |                  |                  |                 | bit     |

| Legend:       |                |                                 |                  |                  |                  |                 |         |

| R = Readable  | e bit          | W = Writable                    | bit              | U = Unimplei     | mented bit, read | as '0'          |         |

| -n = Value at | POR            | '1' = Bit is set                |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                |                                 |                  |                  |                  |                 |         |

| bit 15        |                | Interrupt Flag                  |                  |                  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 11        | •              | equest has no                   |                  | amplata Intorr   | unt Flog Status  | h:t             |         |

| bit 14        |                | equest has oc                   |                  |                  | upt Flag Status  | DIL             |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 13        | Unimplemen     | ted: Read as '                  | 0'               |                  |                  |                 |         |

| bit 12        | OC8IF: Outpu   | ut Compare Ch                   | annel 8 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 11        | •              | equest has no                   |                  | unt Elea Otativa | - h:+            |                 |         |

| bit 11        | •              | request has oc                  |                  | upt Flag Status  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 10        | OC6IF: Outpu   | ut Compare Ch                   | annel 6 Interr   | upt Flag Status  | s bit            |                 |         |

|               | •              | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

| bit 9         | •              | •                               |                  | upt Flag Status  | s bit            |                 |         |

|               | -              | equest has oc                   |                  | apt i lag olalat |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 8         | -              | Capture Chann                   | -                | -lag Status bit  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 7         | •              | equest has no<br>Capture Chann  |                  | -lag Status hit  |                  |                 |         |

|               |                | equest has oc                   |                  | lay Status bit   |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 6         | IC4IF: Input C | Capture Chann                   | el 4 Interrupt F | Flag Status bit  |                  |                 |         |

|               | •              | equest has oc                   |                  |                  |                  |                 |         |

| L:1 F         | -              | equest has no                   |                  | The Otative hit  |                  |                 |         |

| bit 5         |                | Capture Chann<br>request has oc | -                | -lag Status bit  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 4         | DMA3IF: DM     | A Channel 3 D                   | ata Transfer C   | Complete Interr  | upt Flag Status  | bit             |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 0         | -              | equest has no                   |                  | L :4             |                  |                 |         |

| bit 3         |                | Event Interrup                  | -                | JIC              |                  |                 |         |

|               |                | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0          | R/W-1                                    | R/W-0                                                                         | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|------------------------------------------|-------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| —            |                                          | T6IP<2:0>                                                                     |                 | —                |                 | DMA4IP<2:0>     |       |

| bit 15       |                                          |                                                                               |                 |                  |                 |                 | bit 8 |

| U-0          | U-0                                      | U-0                                                                           | U-0             | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _            | _                                        | _                                                                             |                 | _                |                 | OC8IP<2:0>      |       |

| bit 7        |                                          |                                                                               |                 | +                | •               |                 | bit 0 |

| Legend:      |                                          |                                                                               |                 |                  |                 |                 |       |

| R = Readab   | le bit                                   | W = Writable b                                                                | oit             | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR                                    | '1' = Bit is set                                                              |                 | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

| pit 11       | 000 = Interru                            | upt is priority 1<br>upt source is disa<br>n <b>ted:</b> Read as '0           |                 |                  |                 |                 |       |

| bit 10-8     | 111 = Interru<br>•<br>•<br>001 = Interru | DMA Channe<br>upt is priority 7 (h<br>upt is priority 1<br>upt source is disa | nighest priorit |                  | Interrupt Prior | ity bits        |       |

| bit 7-3      | Unimplemer                               | nted: Read as 'o                                                              | )'              |                  |                 |                 |       |

| bit 2-0      |                                          | : Output Compa<br>ıpt is priority 7 (h                                        |                 |                  | ity bits        |                 |       |

|              |                                          | upt is priority 1<br>upt source is disa                                       |                 |                  |                 |                 |       |

| U-0           | R/W-1         | R/W-0                              | R/W-0           | U-0             | R/W-1            | R/W-0           | R/W-0 |

|---------------|---------------|------------------------------------|-----------------|-----------------|------------------|-----------------|-------|

| _             |               | C2TXIP<2:0>                        |                 | —               |                  | C1TXIP<2:0>     |       |

| bit 15        |               |                                    |                 |                 |                  |                 | bit   |

|               |               | 5444.6                             |                 |                 |                  |                 | -     |

| U-0           | R/W-1         | R/W-0                              | R/W-0           | U-0             | R/W-1            | R/W-0           | R/W-0 |

| <br>bit 7     |               | DMA7IP<2:0>                        |                 | _               |                  | DMA6IP<2:0>     | hit   |

|               |               |                                    |                 |                 |                  |                 | bit   |

| Legend:       |               |                                    |                 |                 |                  |                 |       |

| R = Readable  | e bit         | W = Writable I                     | oit             | U = Unimple     | mented bit, rea  | ad as '0'       |       |

| -n = Value at | POR           | '1' = Bit is set                   |                 | '0' = Bit is cl | eared            | x = Bit is unkn | own   |

|               |               |                                    |                 |                 |                  |                 |       |

| bit 15        | Unimplemer    | nted: Read as 'o                   | )'              |                 |                  |                 |       |

| bit 14-12     | C2TXIP<2:0:   | ECAN2 Trans                        | smit Data Re    | quest Interrupt | Priority bits    |                 |       |

|               | 111 = Interru | ipt is priority 7 (h               | nighest priori  | ty interrupt)   |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               |               | pt is priority 1                   |                 |                 |                  |                 |       |

|               |               | pt source is disa                  |                 |                 |                  |                 |       |

| bit 11        | -             | nted: Read as 'o                   |                 |                 |                  |                 |       |

| bit 10-8      |               | >: ECAN1 Trans                     |                 |                 | Priority bits    |                 |       |

|               | 111 = Interru | ipt is priority 7 (ł               | nighest priori  | ty interrupt)   |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               |               | pt is priority 1                   |                 |                 |                  |                 |       |

| L:4 7         |               | pt source is disa                  |                 |                 |                  |                 |       |

| bit 7         | -             | nted: Read as '(                   |                 |                 |                  |                 |       |

| bit 6-4       |               | >: DMA Channe                      |                 | -               | e Interrupt Prio | rity dits       |       |

|               | •             | pt is priority 7 (h                | lignest priori  | ty interrupt)   |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               |               | pt is priority 1 pt source is disa | abled           |                 |                  |                 |       |

| bit 3         |               | nted: Read as '(                   |                 |                 |                  |                 |       |

| bit 2-0       | -             | >: DMA Channe                      |                 | nsfer Complet   | a Interrunt Prio | rity hite       |       |

|               |               | pt is priority 7 (h                |                 | -               |                  |                 |       |

|               | •             |                                    | ingricot priori | ty memupt)      |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               | •             |                                    |                 |                 |                  |                 |       |

|               | 001 - Interru | pt is priority 1                   |                 |                 |                  |                 |       |

| REGISTER '    | <u>10-2:</u> PMD2 | 2: PERIPHER                        |                  | DISABLE C         | ONTROL RE        | GISTER 2        |       |

|---------------|-------------------|------------------------------------|------------------|-------------------|------------------|-----------------|-------|

| R/W-0         | R/W-0             | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| IC8MD         | IC7MD             | IC6MD                              | IC5MD            | IC4MD             | IC3MD            | IC2MD           | IC1MD |

| bit 15        |                   |                                    |                  |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0             | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| OC8MD         | OC7MD             | OC6MD                              | OC5MD            | OC4MD             | OC3MD            | OC2MD           | OC1MD |

| bit 7         |                   |                                    |                  |                   |                  |                 | bit 0 |

| Legend:       |                   |                                    |                  |                   |                  |                 |       |

| R = Readable  | e bit             | W = Writable                       | bit              | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR               | '1' = Bit is set                   |                  | '0' = Bit is clea | ared             | x = Bit is unkr | lown  |

| bit 15        | IC8MD: Input      | Capture 8 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 8 module i<br>ture 8 module i |                  |                   |                  |                 |       |

| bit 14        | IC7MD: Input      | Capture 7 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 7 module i<br>ture 7 module i |                  |                   |                  |                 |       |

| bit 13        |                   | Capture 6 Mod                      |                  | ŀ                 |                  |                 |       |

|               | 1 = Input Cap     | ture 6 module i<br>ture 6 module i | s disabled       |                   |                  |                 |       |

| bit 12        |                   | Capture 5 Mod                      |                  | t                 |                  |                 |       |

|               |                   | ture 5 module i<br>ture 5 module i |                  |                   |                  |                 |       |

| bit 11        | IC4MD: Input      | Capture 4 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 4 module i<br>ture 4 module i |                  |                   |                  |                 |       |

| bit 10        | •                 | Capture 3 Mod                      |                  | t                 |                  |                 |       |

|               |                   | ture 3 module i<br>ture 3 module i |                  |                   |                  |                 |       |

| bit 9         | IC2MD: Input      | Capture 2 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 2 module i<br>ture 2 module i |                  |                   |                  |                 |       |

| bit 8         | IC1MD: Input      | Capture 1 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 1 module i<br>ture 1 module i |                  |                   |                  |                 |       |

| bit 7         | OC8MD: Out        | put Compare 8                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 8 modu<br>ompare 8 modu     |                  |                   |                  |                 |       |

| bit 6         | OC7MD: Out        | put Compare 4                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 7 modu<br>ompare 7 modu     |                  |                   |                  |                 |       |

| bit 5         | -                 | put Compare 6                      |                  | e bit             |                  |                 |       |

|               | •                 | ompare 6 modu<br>ompare 6 modu     |                  |                   |                  |                 |       |

| bit 4         | OC5MD: Out        | put Compare 5                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 5 modu<br>ompare 5 modu     |                  |                   |                  |                 |       |

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

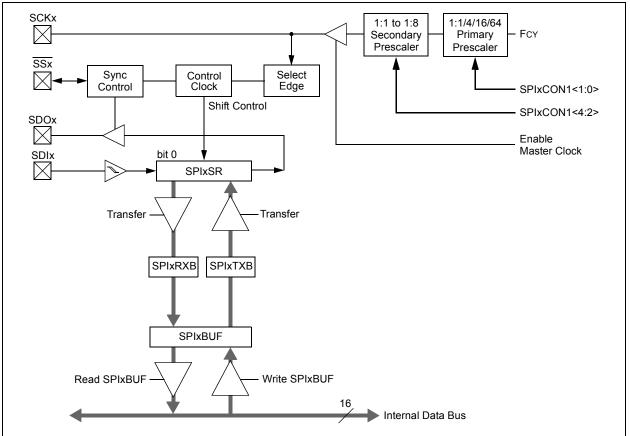

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

### **REGISTER 19-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

|               |                    |                                      | 11.0         |                  |                  |                 | 11.0    |

|---------------|--------------------|--------------------------------------|--------------|------------------|------------------|-----------------|---------|

| U-0           | U-0                | U-0                                  | U-0          | U-0              | U-0              | U-0             | U-0     |

|               | —                  | —                                    | —            |                  | —                | —               |         |

| bit 15        |                    |                                      |              |                  |                  |                 | bit 8   |

| 5444          | 5444.0             |                                      | <b>DM/</b> 0 | <b>D</b> 444 A   | 5444.0           | 5444.0          | D M M A |

| R/W-0         | R/W-0              | R/W-0                                | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|               | N<1:0>             |                                      |              | BRI              | P<5:0>           |                 |         |

| bit 7         |                    |                                      |              |                  |                  |                 | bit 0   |

|               |                    |                                      |              |                  |                  |                 |         |

| Legend:       |                    |                                      |              |                  |                  |                 |         |

| R = Readabl   | e bit              | W = Writable                         | bit          | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | t POR              | '1' = Bit is set                     |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                    |                                      |              |                  |                  |                 |         |

| bit 15-8      | Unimplemer         | nted: Read as '                      | 0'           |                  |                  |                 |         |

| bit 7-6       | SJW<1:0>: S        | Synchronization                      | Jump Width I | bits             |                  |                 |         |

|               | 11 = Length        | is 4 x Tq                            |              |                  |                  |                 |         |

|               | 10 = Length        |                                      |              |                  |                  |                 |         |

|               | 01 = Length        |                                      |              |                  |                  |                 |         |

|               | 00 = Length        |                                      |              |                  |                  |                 |         |

| bit 5-0       |                    | Baud Rate Pres                       |              |                  |                  |                 |         |

|               |                    | [q = 2 x 64 x 1/                     | FCAN         |                  |                  |                 |         |

|               | •                  |                                      |              |                  |                  |                 |         |

|               | •                  |                                      |              |                  |                  |                 |         |

|               | •                  |                                      |              |                  |                  |                 |         |

|               |                    | $Q = 2 \times 3 \times 1/F$          |              |                  |                  |                 |         |

|               |                    | 「q = 2 x 2 x 1/F<br>「q = 2 x 1 x 1/F |              |                  |                  |                 |         |

|               | 00 0000 <b>- 1</b> |                                      |              |                  |                  |                 |         |

### REGISTER 19-13: CIBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                   | R/W-0                         | R/W-0                                   | R/W-0          | R/W-0     | R/W-0 |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|-----------------------------------------|----------------|-----------|-------|--|

| F7BP<3:0>     |                                                                                                                                                                   |                                                         | F6BP<3:0>                     |                                         |                |           |       |  |

| bit 15        |                                                                                                                                                                   |                                                         |                               |                                         |                |           | bit   |  |

|               |                                                                                                                                                                   |                                                         |                               |                                         |                |           |       |  |

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                   | R/W-0                         | R/W-0                                   | R/W-0          | R/W-0     | R/W-0 |  |

|               | F5BP                                                                                                                                                              | <3:0>                                                   |                               |                                         | F4B            | P<3:0>    |       |  |

| bit 7         |                                                                                                                                                                   |                                                         |                               |                                         |                |           | bit   |  |

| Legend:       |                                                                                                                                                                   |                                                         |                               |                                         |                |           |       |  |

| R = Readable  | e bit                                                                                                                                                             | W = Writable                                            | bit                           | U = Unimplem                            | ented bit, rea | ad as '0' |       |  |

| -n = Value at | POR                                                                                                                                                               | '1' = Bit is set                                        |                               | '0' = Bit is cleared x = Bit is unknown |                |           |       |  |

| bit 15-12     |                                                                                                                                                                   | RX Buffer Writt                                         |                               |                                         |                |           |       |  |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |                               | -                                       |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |                               |                                         |                |           |       |  |

| bit 11-8      | <b>F6BP&lt;3:0&gt;:</b> RX Buffer Written when Filter 6 Hits bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |                               |                                         |                |           |       |  |

| bit 7-4       | 1111 = Filter<br>1110 = Filter                                                                                                                                    | RX Buffer Writt<br>hits received in<br>hits received in | RX FIFO bu                    | Iffer                                   |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               |                                                                                                                                                                   | hits received ir<br>hits received ir                    |                               |                                         |                |           |       |  |

| bit 3-0       | F4BP<3:0>:<br>1111 = Filter                                                                                                                                       | RX Buffer Writt<br>hits received ir<br>hits received ir | en when Filte<br>n RX FIFO bu | er 4 Hits bits<br>ıffer                 |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | •                                                                                                                                                                 |                                                         |                               |                                         |                |           |       |  |

|               | 0001 = Filter<br>0000 = Filter                                                                                                                                    | hits received ir                                        | n RX Buffer 1                 |                                         |                |           |       |  |

NOTES:

### 25.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJXXXGPX06A/X08A/X10A electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJXXXGPX06A/X08A/X10A family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                |                      |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0V^{(4)}$ | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} < 3.0V^{(4)}$ | 0.3V to 3.6V         |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                   |                      |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                 | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                 |                      |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                 |                      |

| Maximum current sunk by all ports                                             |                      |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 25-2).

- 3: Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

| DC CHARACTERISTICS              |                                                                     |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |      |         |  |  |

|---------------------------------|---------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup>                                              | Max | Units                                                                                                                                                                                                                                                                                   | Conditions |      |         |  |  |

| Idle Current (I                 | Idle Current (IIDLE): Core OFF Clock ON Base Current <sup>(1)</sup> |     |                                                                                                                                                                                                                                                                                         |            |      |         |  |  |

| DC40d                           | 3                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | -40°C      |      |         |  |  |

| DC40a                           | 3                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | +25°C      |      | 10 MIPS |  |  |

| DC40b                           | 3                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V | TO MIPS |  |  |

| DC40c                           | 3                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |         |  |  |

| DC41d                           | 4                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 16 MIPS |  |  |

| DC41a                           | 5                                                                   | 25  | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V |         |  |  |