Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp708a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the dsPIC33FJ256GP710A product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

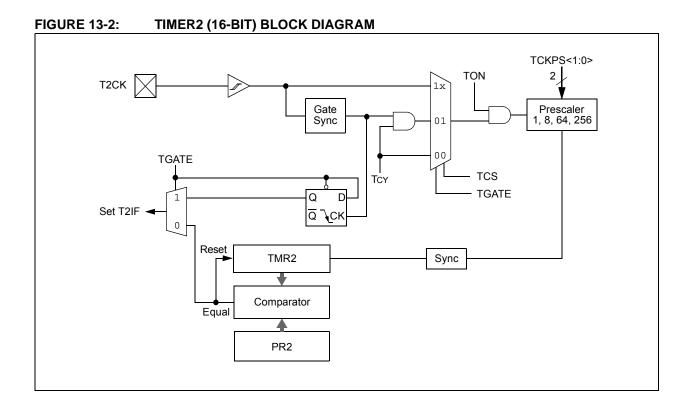

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit<sup>™</sup> (I2C<sup>™</sup>)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

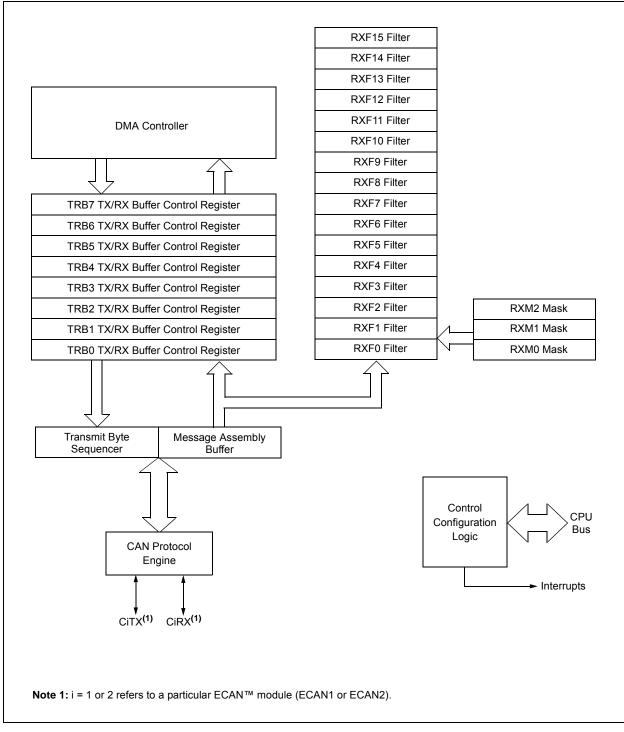

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Section 22. "Direct Memory Access (DMA)" (DS70182)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

NOTES:

| SFR Name | SFR<br>Addr | Bit 15     | Bit 14     | Bit 13      | Bit 12     | Bit 11      | Bit 10     | Bit 9      | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|------------|------------|-------------|------------|-------------|------------|------------|-------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |            |            |             |            |             |            |            | Input 1 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |            |            |             |            |             |            |            | Input 2 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |            |            |             |            |             |            |            | Input 3 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        | _          | _          | ICSIDL      | —          | —           | —          | —          | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |            |            |             |            |             |            |            | Input 4 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC4CON   | 014E        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |            |            |             |            |             |            |            | Input 5 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        |            |            | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |            |            |             |            |             |            |            | Input 6 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        |            |            | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |            |            |             |            |             |            |            | Input 7 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        |            |            | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |            |            |             |            |             |            |            | Input 8 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _          | _          | ICSIDL      | —          | —           | —          | _          | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Legend:  | x = unkno   | wn value c | n Reset, - | – = unimple | emented, r | ead as '0'. | Reset valu | es are sho | wn in hexad | lecimal.     |       |       |       |       |       |          |       |               |

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

### TABLE 4-31: PORTG REGISTER MAP<sup>(1)</sup>

| Fil | le Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----|---------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TF  | RISG    | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PC  | ORTG    | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | -     | _     | RG3    | RG2    | RG1    | RG0    | XXXX          |

| LA  | ΤG      | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | -     | _     | LATG3  | LATG2  | LATG1  | LATG0  | XXXX          |

| O   | DCG     | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | -      |        | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-32: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _         | —      | —      | _      | —         | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE     | BOR     | POR   | xxxxx(1)            |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | _      | 1      | NOSC<2:0  | >     | CLKLOCK | _      | LOCK   | _          | CF    | _        | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | >      | DOZEN  | F      | RCDIV<2:0 | )>    | PLLPOS  | T<1:0> | _      |            | F     | PLLPRE<4 | :0>     |       | 3040                |

| PLLFBD    | 0746 | _      | _      | _         | _      | _      | _      | _         |       |         |        | F      | PLLDIV<8:0 | )>    |          |         |       | 0030                |

| OSCTUN    | 0748 |        | -      | _         | _      | _      | _      | _         | _     | —       | —      |        |            | TUN   | l<5:0>   |         |       | 0000                |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-33: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | -      | —      | _      | -     | _     | -     | ERASE | _     | _     |        | NVMO  | P<3:0> |       | 0000 <b>(1)</b> |

| NVMKEY    | 0766 |        | _      | _      | _      | —      | _      |       | _     |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000            |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-34: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | —      | —     | DCIMD | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | _      | _      | _     | _     | _      | _     | —     | -      | _      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256GPX06A/X08A/X10A devices, this bit is unimplemented and reads back programmed value.

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| REGISTER 7      | '-8: IFS3: I    | INTERRUPT                        | FLAG STAT       | US REGIST        | ER 3             |                 |       |

|-----------------|-----------------|----------------------------------|-----------------|------------------|------------------|-----------------|-------|

| U-0             | U-0             | R/W-0                            | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |

| _               | —               | DMA5IF                           | DCIIF           | DCIEIF           | _                | —               | C2IF  |

| bit 15          |                 |                                  |                 | •                |                  |                 | bit 8 |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIF          | INT4IF          | INT3IF                           | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |

| bit 7           |                 |                                  |                 |                  |                  |                 | bit 0 |

| Legend:         |                 |                                  |                 |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable                     | bit             | U = Unimple      | mented bit, read | as '0'          |       |

| -n = Value at I |                 | '1' = Bit is set                 |                 | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                 |                 |                                  |                 |                  |                  |                 |       |

| bit 15-14       | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 13          | DMA5IF: DM      | A Channel 5 D                    | ata Transfer (  | Complete Inter   | rupt Flag Status | bit             |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 12          | DCIIF: DCI E    | vent Interrupt I                 | -lag Status bit |                  |                  |                 |       |

|                 | 1 = Interrupt   | request has oc                   | curred          |                  |                  |                 |       |

|                 | •               | request has no                   |                 |                  |                  |                 |       |

| bit 11          |                 | Error Interrupt                  | U               | it               |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 10-9        | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 8           | C2IF: ECAN2     | 2 Event Interrup                 | ot Flag Status  | bit              |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 7           | C2RXIF: ECA     | AN2 Receive D                    | ata Ready Int   | errupt Flag Sta  | atus bit         |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 6           | •               | rnal Interrupt 4                 |                 | it               |                  |                 |       |

|                 | 1 = Interrupt i | request has oc<br>request has no | curred          |                  |                  |                 |       |

| bit 5           | INT3IF: Exter   | rnal Interrupt 3                 | Flag Status b   | it               |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 4           | -               | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 | 1 = Interrupt i | request has oc                   | curred          |                  |                  |                 |       |

|                 | 0 = Interrupt   | request has no                   | t occurred      |                  |                  |                 |       |

| bit 3           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

| bit 2           | -               | request has no<br>2 Master Even  |                 | ag Status bit    |                  |                 |       |

| SIL Z           |                 | request has oc                   | •               | ug oluluo bit    |                  |                 |       |

|                 |                 | request has no                   |                 |                  |                  |                 |       |

| bit 1           | SI2C2IF: 12C    | 2 Slave Events                   | Interrupt Flag  | g Status bit     |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

|                 | -               | request has no                   |                 |                  |                  |                 |       |

| bit 0           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

|                 |                 | iequest nas no                   |                 |                  |                  |                 |       |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|---------------|-------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| —             |                   | T1IP<2:0>                                |                |                   |                 | OC1IP<2:0>      |       |

| bit 15        |                   |                                          |                |                   |                 |                 | bi    |

|               |                   |                                          |                |                   |                 |                 |       |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _             |                   | IC1IP<2:0>                               |                |                   |                 | INT0IP<2:0>     |       |

| bit 7         |                   |                                          |                |                   |                 |                 | bi    |

| Legend:       |                   |                                          |                |                   |                 |                 |       |

| R = Readabl   | e bit             | W = Writable I                           | bit            | U = Unimple       | mented bit, rea | id as '0'       |       |

| -n = Value at | POR               | '1' = Bit is set                         |                | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|               |                   |                                          |                |                   |                 |                 |       |

| bit 15        | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 14-12     | T1IP<2:0>:        | Timer1 Interrupt                         | Priority bits  |                   |                 |                 |       |

|               | 111 = Interr      | rupt is priority 7 (ł                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1<br>upt source is dis   | abled          |                   |                 |                 |       |

| bit 11        |                   | ented: Read as '                         |                |                   |                 |                 |       |

| bit 10-8      | -                 | >: Output Compa                          |                | 1 Interrupt Prior | ritv bits       |                 |       |

|               |                   | upt is priority 7 (I                     |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | 001 = Interr      | upt is priority 1                        |                |                   |                 |                 |       |

|               |                   | upt source is dis                        | abled          |                   |                 |                 |       |

| bit 7         | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 6-4       |                   | : Input Capture C                        |                |                   | oits            |                 |       |

|               | 111 = Interr      | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1                        | ablad          |                   |                 |                 |       |

| bit 3         |                   | upt source is disa<br>ented: Read as 'o  |                |                   |                 |                 |       |

| bit 2-0       | -                 |                                          |                | , bite            |                 |                 |       |

| DIL 2-0       |                   | External Interr<br>upt is priority 7 (I) |                |                   |                 |                 |       |

|               | •                 |                                          | gricot priori  | , monuply         |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •<br>001 - Interr | upt is priority 1                        |                |                   |                 |                 |       |

|               |                   |                                          |                |                   |                 |                 |       |

| REGISTER 7-20: IP | PC5: INTERRUPT PRIORITY CONTROL REGISTER 5 |

|-------------------|--------------------------------------------|

|-------------------|--------------------------------------------|

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|-----------------|--------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _               |                    | IC8IP<2:0>                              |                 | —                |                 | IC7IP<2:0>      |       |

| bit 15          |                    |                                         |                 |                  | ·               |                 | bit 8 |

|                 |                    |                                         |                 |                  |                 |                 |       |

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

| —               |                    | AD2IP<2:0>                              |                 | —                |                 | INT1IP<2:0>     |       |

| bit 7           |                    |                                         |                 |                  |                 |                 | bit   |

| Legend:         |                    |                                         |                 |                  |                 |                 |       |

| R = Readable    | bit                | W = Writable t                          | oit             | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at I | POR                | '1' = Bit is set                        |                 | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

| bit 15          | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 14-12       | -                  | Input Capture C                         |                 | rrunt Priority h | nite            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Interr  | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 11          |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 10-8        | -                  | Input Capture C                         |                 | rrupt Priority b | oits            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 = Interru | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 7           | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 6-4         | AD2IP<2:0>         | : ADC2 Convers                          | ion Complete    | e Interrupt Pric | rity bits       |                 |       |

|                 | 111 = Interru      | upt is priority 7 (h                    | nighest priorit | y interrupt)     |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 |                    | upt is priority 1<br>upt source is disa | abled           |                  |                 |                 |       |

| bit 3           |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 2-0         | -                  | : External Interr                       |                 | hits             |                 |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Intern  | int is priority 1                       |                 |                  |                 |                 |       |

|                 | 001 = merrl        | upt is priority 1                       |                 |                  |                 |                 |       |

### **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  | 5444  | 54446            |                 | <b>B</b> 111 A  |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PAI   | 0<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-------|---------------------|

| —      | _   | —   | —   | —   | —   | CNT<  | 9:8> <sup>(2)</sup> |

| bit 15 |     |     |     |     |     |       | bit 8               |

|        |     |     |     |     |     |       |                     |

| R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |

| bit 7                   |       |       |       |       |       |       |       |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

| U-0                 | U-0                                                                                             | U-0                                   | R/W-0                  | R/W-0                                  | R/W-0              | R/W-0              | R/W-0                |  |  |

|---------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|----------------------------------------|--------------------|--------------------|----------------------|--|--|

| —                   |                                                                                                 |                                       | DISSCK                 | DISSDO                                 | MODE16             | SMP                | CKE <sup>(1)</sup>   |  |  |

| bit 15              |                                                                                                 |                                       |                        |                                        |                    |                    | bit                  |  |  |

|                     |                                                                                                 |                                       |                        |                                        |                    |                    |                      |  |  |

| R/W-0               | R/W-0                                                                                           | R/W-0                                 | R/W-0                  | R/W-0                                  | R/W-0              | R/W-0              | R/W-0                |  |  |

| SSEN <sup>(3)</sup> | CKP                                                                                             | MSTEN                                 |                        | SPRE<2:0>(2                            | -)                 | PPRE<              | <1:0> <sup>(2)</sup> |  |  |

| bit 7               |                                                                                                 |                                       |                        |                                        |                    |                    | bit                  |  |  |

| Legend:             |                                                                                                 |                                       |                        |                                        |                    |                    |                      |  |  |

| R = Readab          | le bit                                                                                          | W = Writable                          | bit                    | U = Unimplen                           | nented bit, read   | as '0'             |                      |  |  |

| -n = Value a        | t POR                                                                                           | '1' = Bit is set                      | :                      | '0' = Bit is cle                       | ared               | x = Bit is unkr    | nown                 |  |  |

|                     |                                                                                                 |                                       |                        |                                        |                    |                    |                      |  |  |

| bit 15-13           | Unimplemen                                                                                      | nted: Read as '                       | 0'                     |                                        |                    |                    |                      |  |  |

| bit 12              |                                                                                                 | able SCKx pin                         | -                      |                                        |                    |                    |                      |  |  |

|                     |                                                                                                 | SPI clock is disa<br>SPI clock is ena |                        | ctions as I/O                          |                    |                    |                      |  |  |

| bit 11              |                                                                                                 |                                       |                        |                                        |                    |                    |                      |  |  |

|                     | <b>DISSDO:</b> Disable SDOx pin bit<br>1 = SDOx pin is not used by module; pin functions as I/O |                                       |                        |                                        |                    |                    |                      |  |  |

|                     |                                                                                                 | is controlled b                       |                        |                                        | ,                  |                    |                      |  |  |

| bit 10              | MODE16: Wo                                                                                      | ord/Byte Comm                         | nunication Sel         | ect bit                                |                    |                    |                      |  |  |

|                     |                                                                                                 | ication is word-<br>ication is byte-  |                        |                                        |                    |                    |                      |  |  |

| bit 9               |                                                                                                 | ata Input Sam                         |                        |                                        |                    |                    |                      |  |  |

|                     | Master mode                                                                                     |                                       |                        |                                        |                    |                    |                      |  |  |

|                     |                                                                                                 | a sampled at e                        |                        |                                        |                    |                    |                      |  |  |

|                     | Slave mode:                                                                                     | a sampled at m                        |                        | Sulput lime                            |                    |                    |                      |  |  |

|                     |                                                                                                 | e cleared when                        | SPIx is used           | in Slave mode.                         |                    |                    |                      |  |  |

| bit 8               | CKE: SPIx C                                                                                     | lock Edge Sele                        | ect bit <sup>(1)</sup> |                                        |                    |                    |                      |  |  |

|                     |                                                                                                 |                                       |                        |                                        | clock state to Id  |                    |                      |  |  |

| bit 7               |                                                                                                 | Select Enable                         |                        |                                        | ock state to activ | e clock state (    | see bit 0)           |  |  |

|                     |                                                                                                 | used for Slave                        |                        | ue).                                   |                    |                    |                      |  |  |

|                     |                                                                                                 |                                       |                        | rolled by port fu                      | unction            |                    |                      |  |  |

| bit 6               | CKP: Clock F                                                                                    | Polarity Select                       | oit                    |                                        |                    |                    |                      |  |  |

|                     |                                                                                                 |                                       | •                      | ve state is a lov<br>e state is a higł |                    |                    |                      |  |  |

| bit 5               | MSTEN: Mas                                                                                      | ster Mode Enat                        | ole bit                |                                        |                    |                    |                      |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                    |                                       |                        |                                        |                    |                    |                      |  |  |

|                     | The CKE bit is not                                                                              |                                       | amed SPI mo            | des. The user s                        | should program     | this bit to '0' fo | or the Frame         |  |  |

|                     | SPI modes (FRME                                                                                 | $\pm in = \pm j.$                     |                        |                                        |                    |                    |                      |  |  |

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

### FIGURE 19-1: ECAN™ MODULE BLOCK DIAGRAM

| U-0           | U-0                                       | R-0                                                                                                            | R-0             | R-0              | R-0              | R-0             | R-0   |  |  |  |  |

|---------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|

|               |                                           | ТХВО                                                                                                           | TXBP            | RXBP             | TXWAR            | RXWAR           | EWARN |  |  |  |  |

| bit 15        |                                           |                                                                                                                |                 |                  |                  |                 | bit 8 |  |  |  |  |

| R/C-0         | R/C-0                                     | R/C-0                                                                                                          | U-0             | R/C-0            | R/C-0            | R/C-0           | R/C-0 |  |  |  |  |

| IVRIF         | WAKIF                                     | ERRIF                                                                                                          | 0-0             | FIFOIF           | RBOVIF           | RBIF            | TBIF  |  |  |  |  |

| bit 7         | WAKIF                                     | ERRIF                                                                                                          |                 | FIFUIF           | RBOVIE           | RBIF            | bit   |  |  |  |  |

|               |                                           |                                                                                                                |                 |                  |                  |                 | DIL   |  |  |  |  |

| Legend:       |                                           | C = Clear on                                                                                                   | y bit           |                  |                  |                 |       |  |  |  |  |

| R = Readable  | e bit                                     | W = Writable                                                                                                   | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at | POR                                       | '1' = Bit is set                                                                                               |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 15-14     | Unimplemen                                | nted: Read as '                                                                                                | 0'              |                  |                  |                 |       |  |  |  |  |

| bit 13        | -                                         | smitter in Error                                                                                               |                 | bit              |                  |                 |       |  |  |  |  |

|               |                                           | ter is in Bus Of                                                                                               |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Transmitt                             | ter is not in Bus                                                                                              | Off state       |                  |                  |                 |       |  |  |  |  |

| bit 12        | TXBP: Trans                               | mitter in Error                                                                                                | State Bus Pas   | sive bit         |                  |                 |       |  |  |  |  |

|               |                                           | ter is in Bus Pa<br>ter is not in Bus                                                                          |                 | -                |                  |                 |       |  |  |  |  |

| bit 11        |                                           | iver in Error Sta                                                                                              |                 |                  |                  |                 |       |  |  |  |  |

|               |                                           | is in Bus Pass                                                                                                 |                 | vebil            |                  |                 |       |  |  |  |  |

|               |                                           | is not in Bus P                                                                                                |                 |                  |                  |                 |       |  |  |  |  |

| bit 10        | TXWAR: Trai                               | nsmitter in Erro                                                                                               | r State Warni   | ng bit           |                  |                 |       |  |  |  |  |

|               | 1 = Transmitter is in Error Warning state |                                                                                                                |                 |                  |                  |                 |       |  |  |  |  |

|               | 0 = Transmitt                             | ter is not in Erro                                                                                             | or Warning sta  | ate              |                  |                 |       |  |  |  |  |

| bit 9         |                                           | ceiver in Error                                                                                                | •               | bit              |                  |                 |       |  |  |  |  |

|               |                                           | <ol> <li>1 = Receiver is in Error Warning state</li> <li>0 = Receiver is not in Error Warning state</li> </ol> |                 |                  |                  |                 |       |  |  |  |  |

| L:1 0         |                                           |                                                                                                                |                 |                  | L:4              |                 |       |  |  |  |  |

| bit 8         |                                           | nsmitter or Rec<br>ter or receiver i                                                                           |                 |                  | DIT              |                 |       |  |  |  |  |

|               |                                           | ter or receiver i                                                                                              |                 | •                |                  |                 |       |  |  |  |  |

| bit 7         |                                           | d Message Rec                                                                                                  |                 | •                |                  |                 |       |  |  |  |  |

|               |                                           | request has oc                                                                                                 |                 | 5                |                  |                 |       |  |  |  |  |

|               | 0 = Interrupt                             | request has no                                                                                                 | t occurred      |                  |                  |                 |       |  |  |  |  |

| bit 6         |                                           | Wake-up Activ                                                                                                  |                 | ag bit           |                  |                 |       |  |  |  |  |

|               |                                           | request has oc                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

| 6:4 <i>5</i>  | -                                         | request has no                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

| bit 5         |                                           |                                                                                                                |                 | ources in Clin   | F<13:8> regist   | er)             |       |  |  |  |  |

|               |                                           | request has oc<br>request has no                                                                               |                 |                  |                  |                 |       |  |  |  |  |

| bit 4         | -                                         | nted: Read as '                                                                                                |                 |                  |                  |                 |       |  |  |  |  |

| bit 3         | -                                         | ) Almost Full In                                                                                               |                 | it               |                  |                 |       |  |  |  |  |

|               |                                           | request has oc                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

|               | •                                         | request has no                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

| bit 2         | <b>RBOVIF:</b> RX                         | Buffer Overflo                                                                                                 | w Interrupt Fla | ag bit           |                  |                 |       |  |  |  |  |

|               |                                           | request has oc                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

|               |                                           | request has no                                                                                                 |                 |                  |                  |                 |       |  |  |  |  |

| bit 1         |                                           | Iffer Interrupt Fl                                                                                             | -               |                  |                  |                 |       |  |  |  |  |

|               | •                                         | request has oc<br>request has no                                                                               |                 |                  |                  |                 |       |  |  |  |  |

|               |                                           | i oquest nas nu                                                                                                |                 |                  |                  |                 |       |  |  |  |  |

| hit ()        | TRIF. TY Duf                              | ffor Interrupt El                                                                                              | aa hit          |                  |                  |                 |       |  |  |  |  |

| bit 0         |                                           | ffer Interrupt Fla<br>request has oc                                                                           | -               |                  |                  |                 |       |  |  |  |  |

### REGISTER 19-6: CIINTF: ECAN™ INTERRUPT FLAG REGISTER

### **REGISTER 19-8:** CiEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0                                                                  | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                                                                 | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------|------------------|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      |                  | TERRO                         | CNT<7:0>                                     |                                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      |                  |                               |                                              |                                                                                                                                           |                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                      |                  |                               |                                              |                                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R-0                                                                  | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                                                                 | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                      |                  | RERRO                         | CNT<7:0>                                     |                                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      |                  |                               |                                              |                                                                                                                                           |                                                                                                                                     | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                      |                  |                               |                                              |                                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      |                  |                               |                                              |                                                                                                                                           |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |