Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 69                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10/12b                                                                      |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

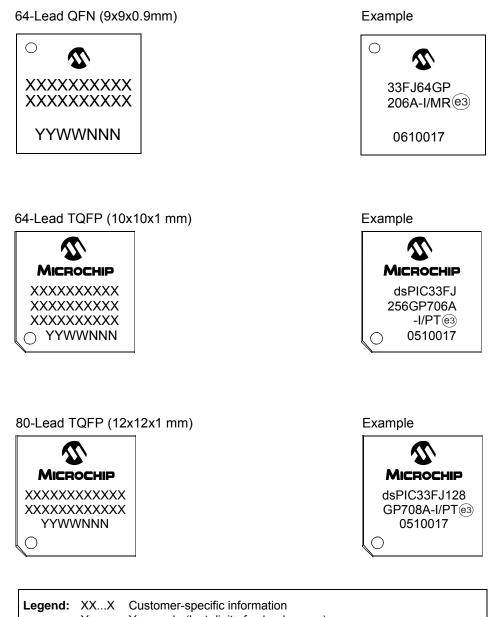

| Package / Case             | 80-TQFP                                                                            |

| Supplier Device Package    | 80-TQFP (12x12)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp708at-i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

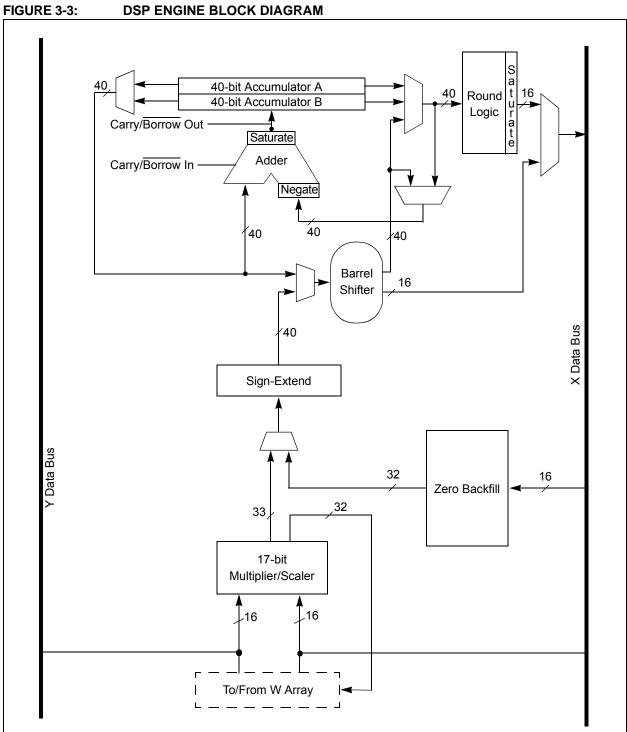

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and, thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes:

• Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF), or maximally negative 9.31 value (0x800000000), into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against errone-ous data or unexpected algorithm problems (e.g., gain calculations).

Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF), or maximally negative 1.31 value (0x008000000), into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

### 3.6.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 3.6.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.2.4 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator write-back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

ister or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

#### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where:

Operand 1 is always a working register (i.e., the addressing mode can only be register direct) which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- Register Indirect

- Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

| Note: | Not all instructions support all the  |

|-------|---------------------------------------|

|       | addressing modes given above.         |

|       | Individual instructions may support   |

|       | different subsets of these addressing |

|       | modes.                                |

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-35: FUNDAMENTAL ADDRESSING MODES SUPPORTED

## 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the Addressing     |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | mode specified in the instruction can differ |  |  |  |  |  |  |

|       | for the source and destination EA.           |  |  |  |  |  |  |

|       | However, the 4-bit Wb (Register Offset)      |  |  |  |  |  |  |

|       | field is shared between both source and      |  |  |  |  |  |  |

|       | destination (but typically only used by      |  |  |  |  |  |  |

|       | one).                                        |  |  |  |  |  |  |

In summary, the following Addressing modes are supported by move and accumulator instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not all instructions support all the                                         |

|-------|------------------------------------------------------------------------------|

|       | Addressing modes given above.                                                |

|       | Individual instructions may support<br>different subsets of these Addressing |

|       | modes.                                                                       |

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and

NOTES:

| U-0          | R/W-1                                    | R/W-0                                                                         | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|------------------------------------------|-------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| —            |                                          | T6IP<2:0>                                                                     |                 | —                |                 | DMA4IP<2:0>     |       |

| bit 15       |                                          |                                                                               |                 |                  |                 |                 | bit 8 |

| U-0          | U-0                                      | U-0                                                                           | U-0             | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _            | _                                        | _                                                                             |                 | _                |                 | OC8IP<2:0>      |       |

| bit 7        |                                          |                                                                               |                 | +                | •               |                 | bit 0 |

| Legend:      |                                          |                                                                               |                 |                  |                 |                 |       |

| R = Readab   | le bit                                   | W = Writable b                                                                | oit             | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR                                    | '1' = Bit is set                                                              |                 | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |

| pit 11       | 000 = Interru                            | upt is priority 1<br>upt source is disa<br>n <b>ted:</b> Read as '0           |                 |                  |                 |                 |       |

| bit 10-8     | 111 = Interru<br>•<br>•<br>001 = Interru | DMA Channe<br>upt is priority 7 (h<br>upt is priority 1<br>upt source is disa | nighest priorit |                  | Interrupt Prior | ity bits        |       |

| bit 7-3      | Unimplemer                               | nted: Read as 'o                                                              | )'              |                  |                 |                 |       |

| bit 2-0      |                                          | : Output Compa<br>ıpt is priority 7 (h                                        |                 |                  | ity bits        |                 |       |

|              |                                          | upt is priority 1<br>upt source is disa                                       |                 |                  |                 |                 |       |

**EQUATION 9-3:**

**XT WITH PLL MODE**

= 40 MIPS

**EXAMPLE**

$FCY = \frac{FOSC}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right)$

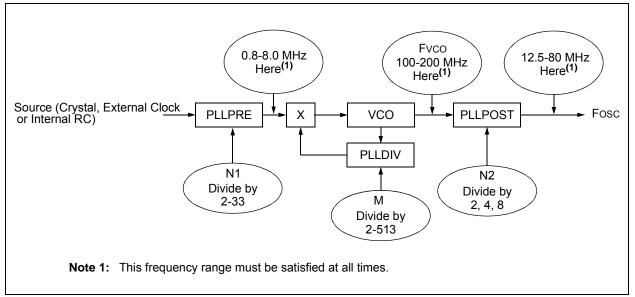

For example, suppose a 10 MHz crystal is being used, with "XT with PLL" being the selected oscillator mode. If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz. If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz range needed.

If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

### FIGURE 9-2: dsPIC33FJXXXGPX06A/X08A/X10A PLL BLOCK DIAGRAM

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|--------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | xx          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | xx          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1        |

| Secondary (Timer1) Oscillator (Sosc)             | Secondary         | XX          | 100        | 1        |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -        |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -        |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | _        |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | xx          | 001        | 1        |

| Fast RC Oscillator (FRC)                         | Internal          | xx          | 000        | 1        |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

### bit 0 OSWEN: Oscillator Switch Enable bit

bit 1

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This is register is reset only on a Power-on Reset (POR).

| R/W-0         | R/W-0                                                                                       | R/W-0                                 | R/W-0   | R/W-0             | U-0              | U-0            | R/W-0                |

|---------------|---------------------------------------------------------------------------------------------|---------------------------------------|---------|-------------------|------------------|----------------|----------------------|

| T5MD          | T4MD                                                                                        | T3MD                                  | T2MD    | T1MD              |                  | _              | DCIMD                |

| bit 15        |                                                                                             |                                       |         |                   |                  |                | bit 8                |

|               |                                                                                             |                                       |         |                   |                  |                |                      |

| R/W-0         | R/W-0                                                                                       | R/W-0                                 | R/W-0   | R/W-0             | R/W-0            | R/W-0          | R/W-0                |

| I2C1MD        | U2MD                                                                                        | U1MD                                  | SPI2MD  | SPI1MD            | C2MD             | C1MD           | AD1MD <sup>(1)</sup> |

| bit 7         |                                                                                             |                                       |         |                   |                  |                | bit                  |

| Legend:       |                                                                                             |                                       |         |                   |                  |                |                      |

| R = Readabl   | e bit                                                                                       | W = Writable                          | bit     | U = Unimplen      | nented bit, read | d as '0'       |                      |

| -n = Value at | POR                                                                                         | '1' = Bit is set                      |         | '0' = Bit is clea |                  | x = Bit is unk | nown                 |

|               |                                                                                             |                                       |         |                   |                  |                |                      |

| bit 15        | T5MD: Timer                                                                                 | 5 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                                                                             | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 14        | T4MD: Timer                                                                                 | 4 Module Disat                        | ole bit |                   |                  |                |                      |

|               | -                                                                                           | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 13        |                                                                                             | 3 Module Disat                        |         |                   |                  |                |                      |

|               | 1 = Timer3 m                                                                                | nodule is disable                     | ed      |                   |                  |                |                      |

|               | 0 = Timer3 m                                                                                | nodule is enable                      | d       |                   |                  |                |                      |

| bit 12        | -                                                                                           | 2 Module Disat                        |         |                   |                  |                |                      |

|               | -                                                                                           | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 11        | T1MD: Timer                                                                                 | 1 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                                                                             | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 10-9      | Unimplemer                                                                                  | ted: Read as '                        | כ'      |                   |                  |                |                      |

| bit 8         | DCIMD: DCI Module Disable bit                                                               |                                       |         |                   |                  |                |                      |

|               |                                                                                             | ule is disabled<br>ule is enabled     |         |                   |                  |                |                      |

| bit 7         | <b>I2C1MD:</b> I <sup>2</sup> C                                                             | 1 Module Disab                        | le bit  |                   |                  |                |                      |

|               |                                                                                             | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

| bit 6         |                                                                                             | T2 Module Disa                        | ble bit |                   |                  |                |                      |

|               | 1 = UART2 module bisable bit<br>0 = UART2 module is disabled<br>0 = UART2 module is enabled |                                       |         |                   |                  |                |                      |

| bit 5         | 0 = OART2 module is enabled<br>U1MD: UART1 Module Disable bit                               |                                       |         |                   |                  |                |                      |

|               | 1 = UART1 module is disabled                                                                |                                       |         |                   |                  |                |                      |

|               | 0 = UART1 n                                                                                 | nodule is enable                      | ed      |                   |                  |                |                      |

| bit 4         | SPI2MD: SP                                                                                  | I2 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                                                                             | dule is disabled                      |         |                   |                  |                |                      |

|               |                                                                                             | dule is enabled                       |         |                   |                  |                |                      |

| bit 3         |                                                                                             | 11 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                                                                             | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

## **19.3 Modes of Operation**

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

## 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

## 19.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

## 19.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

## 19.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

## 19.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

#### REGISTER 19-13: CIBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                         | R/W-0                   | R/W-0          | R/W-0           | R/W-0 |

|---------------|--------------------------------|---------------------------------------------------------|-------------------------------|-------------------------|----------------|-----------------|-------|

| F7BP<3:0>     |                                |                                                         |                               | F6B                     | P<3:0>         |                 |       |

| bit 15        |                                |                                                         |                               |                         |                |                 | bit   |

|               |                                |                                                         |                               |                         |                |                 |       |

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                         | R/W-0                   | R/W-0          | R/W-0           | R/W-0 |

|               | F5BP                           | <3:0>                                                   |                               |                         | F4B            | P<3:0>          |       |

| bit 7         |                                |                                                         |                               |                         |                |                 | bit   |

| Legend:       |                                |                                                         |                               |                         |                |                 |       |

| R = Readable  | e bit                          | W = Writable                                            | bit                           | U = Unimplem            | ented bit, rea | ad as '0'       |       |

| -n = Value at | POR                            | '1' = Bit is set                                        |                               | '0' = Bit is clea       |                | x = Bit is unkı | nown  |

| bit 15-12     |                                | RX Buffer Writt                                         |                               |                         |                |                 |       |

|               |                                | hits received ir hits received ir                       |                               | -                       |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               |                                | hits received ir hits received ir                       |                               |                         |                |                 |       |

| bit 11-8      | 1111 <b>= Filte</b> r          | RX Buffer Writt<br>hits received ir<br>hits received ir | RX FIFO bu                    | uffer                   |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               |                                | hits received ir hits received ir                       |                               |                         |                |                 |       |

| bit 7-4       | 1111 = Filter<br>1110 = Filter | RX Buffer Writt<br>hits received in<br>hits received in | RX FIFO bu                    | uffer                   |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               |                                | hits received ir<br>hits received ir                    |                               |                         |                |                 |       |

| bit 3-0       | F4BP<3:0>:<br>1111 = Filter    | RX Buffer Writt<br>hits received ir<br>hits received ir | en when Filte<br>n RX FIFO bu | er 4 Hits bits<br>uffer |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | •                              |                                                         |                               |                         |                |                 |       |

|               | 0001 = Filter<br>0000 = Filter | hits received ir                                        | n RX Buffer 1                 |                         |                |                 |       |

| R/W-0         | R-0                        | R-0                                                                                                                                                                                         | R-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

|---------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|------------------|-----------------|---------|--|

| TXENn         | TXABTn                     | TXLARBn                                                                                                                                                                                     | TXERRn                        | TXREQn           | RTRENn           | TXnPF           | RI<1:0> |  |

| bit 15        |                            |                                                                                                                                                                                             |                               |                  |                  |                 | bit 8   |  |

|               |                            |                                                                                                                                                                                             |                               |                  | <b>D</b> # 44 A  |                 |         |  |

| R/W-0         | R-0                        | R-0                                                                                                                                                                                         | R-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

| TXENm         | TXABTm <sup>(1)</sup>      | TXLARBm <sup>(1)</sup>                                                                                                                                                                      | TXERRm <sup>(1)</sup>         | TXREQm           | RTRENm           | TXmPF           |         |  |

| bit 7         |                            |                                                                                                                                                                                             |                               |                  |                  |                 | bit     |  |

| Legend:       |                            |                                                                                                                                                                                             |                               |                  |                  |                 |         |  |

| R = Readable  | e bit                      | W = Writable                                                                                                                                                                                | bit                           | U = Unimpler     | mented bit, read | as '0'          |         |  |

| -n = Value at | POR                        | '1' = Bit is set                                                                                                                                                                            |                               | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |

|               |                            |                                                                                                                                                                                             |                               |                  |                  |                 |         |  |

| bit 15-8      | See Definition             | on for Bits 7-0,                                                                                                                                                                            | Controls Buf                  | fer n            |                  |                 |         |  |

| bit 7         |                            | /RX Buffer Sele                                                                                                                                                                             |                               |                  |                  |                 |         |  |

|               |                            | Bn is a transm                                                                                                                                                                              |                               |                  |                  |                 |         |  |

| <b>L</b> H 0  |                            | RBn is a receive                                                                                                                                                                            |                               |                  |                  |                 |         |  |

| bit 6         |                            | essage Aborted                                                                                                                                                                              |                               |                  |                  |                 |         |  |

|               | 1 = Message<br>0 = Message | completed trar                                                                                                                                                                              | smission succ                 | essfully         |                  |                 |         |  |

| bit 5         | TXLARBm:                   | Message Lost                                                                                                                                                                                | Arbitration bit <sup>(1</sup> | )                |                  |                 |         |  |

|               |                            | lost arbitration did not lose ar                                                                                                                                                            |                               |                  |                  |                 |         |  |

| bit 4         | TXERRm: E                  | <b>TXERRm:</b> Error Detected During Transmission bit <sup>(1)</sup>                                                                                                                        |                               |                  |                  |                 |         |  |

|               |                            | or occurred wh<br>or did not occu                                                                                                                                                           | •                             | •                |                  |                 |         |  |

| bit 3         | TXREQm: N                  | lessage Send F                                                                                                                                                                              | Request bit                   |                  |                  |                 |         |  |

|               |                            | Setting this bit to '1' requests sending a message. The bit will automatically clear when the message is successfully sent. Clearing the bit to '0' while set will request a message abort. |                               |                  |                  |                 |         |  |

| bit 2         | RTRENm: Au                 | uto-Remote Tra                                                                                                                                                                              | Insmit Enable                 | oit              |                  |                 |         |  |

|               |                            | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul>                                     |                               |                  |                  |                 |         |  |

| bit 1-0       | TXmPRI<1:0                 | TXmPRI<1:0>: Message Transmission Priority bits                                                                                                                                             |                               |                  |                  |                 |         |  |

|               |                            | message prior                                                                                                                                                                               |                               |                  |                  |                 |         |  |

|               |                            |                                                                                                                                                                                             | oggo priority                 |                  |                  |                 |         |  |

|               | 10 = High integration      | ermediate mes                                                                                                                                                                               |                               |                  |                  |                 |         |  |

### 25.1 DC Characteristics

| TABLE 25-1: | <b>OPERATING MIPS VS. VOLTAGE</b> |

|-------------|-----------------------------------|

|             |                                   |

| Characteristic VDD Range<br>(in Volts) |                          | Temp Range      | Max MIPS                     |

|----------------------------------------|--------------------------|-----------------|------------------------------|

|                                        |                          | (in °C)         | dsPIC33FJXXXGPX06A/X08A/X10A |

|                                        | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                           |

|                                        | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 25-11 for the minimum and maximum BOR values.

#### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min          | Тур         | Max  | Unit |  |

|---------------------------------------------------------------------------------------------|--------|--------------|-------------|------|------|--|

| dsPIC33FJXXXGPX06A/X08A/X10A                                                                |        |              |             |      |      |  |

| Operating Junction Temperature Range                                                        | TJ     | -40          | —           | +125 | °C   |  |

| Operating Ambient Temperature Range                                                         | TA     | TA -40 — +85 |             |      |      |  |

| Extended Temperature Devices                                                                |        |              |             |      |      |  |

| Operating Junction Temperature Range                                                        | TJ     | -40          | —           | +150 | °C   |  |

| Operating Ambient Temperature Range                                                         | TA     | -40          | °C          |      |      |  |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O  |             |      | W    |  |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |              |             |      |      |  |

| Maximum Allowed Power Dissipation                                                           | Pdmax  | (            | TJ - TA)/θJ | A    | W    |  |

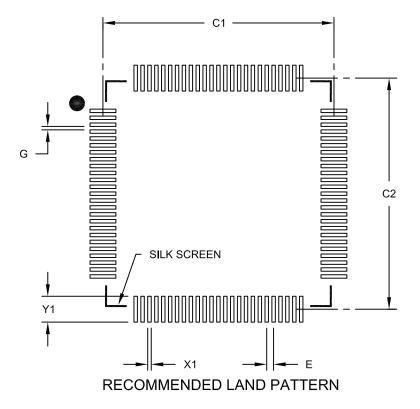

#### TABLE 25-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        | Symbol | Тур | Max | Unit | Notes |

|-------------------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θja    | 40  | —   | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1 mm)  | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θja    | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHA       | RACTER | ISTICS                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                     |       |                                                                                                                                    |

|--------------|--------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                        | Min                                                                                                                                                                                                                                                                                     | Typ <sup>(1)</sup> | Max                 | Units | Conditions                                                                                                                         |

| DI60a        | licl   | Input Low Injection Current                                           | 0                                                                                                                                                                                                                                                                                       |                    | <sub>-5</sub> (5,8) | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, and RB11                                                     |

| DI60b        | ІІСН   | Input High Injection Current                                          | 0                                                                                                                                                                                                                                                                                       | _                  | +5(6,7,8)           | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>             |

| DI60c        | Σ ΙΙΟΤ | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                                                                                                                                                                                                                                                      | _                  | +20 <sup>(9)</sup>  | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |

## TABLE 25-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| АС СНА       | RACTERI    | STICS             |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                             |  |

|--------------|------------|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|--|

| Param<br>No. | Symbol     | Charact           | eristic                   | Min                                                                                                                                                                                                                                                                                   | Max  | Units | Conditions                                  |  |

| IS10         | TLO:SCL    | Clock Low Time    | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|              |            |                   | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                   | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   | —    | μS    | —                                           |  |

| IS11         | THI:SCL    | Clock High Time   | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                   | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|              |            |                   | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                   | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   | _    | μS    |                                             |  |

| IS20         | TF:SCL     | SDAx and SCLx     | 100 kHz mode              | —                                                                                                                                                                                                                                                                                     | 300  | ns    | CB is specified to be from                  |  |

|              |            | Fall Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | 10 to 400 pF                                |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                     | 100  | ns    |                                             |  |

| IS21         | TR:SCL     | SDAx and SCLx     | 100 kHz mode              | —                                                                                                                                                                                                                                                                                     | 1000 | ns    | CB is specified to be from                  |  |

|              |            | Rise Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | 10 to 400 pF                                |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> |                                                                                                                                                                                                                                                                                       | 300  | ns    |                                             |  |

| IS25         | TSU:DAT    | Data Input        | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                   |      | ns    |                                             |  |

|              | Setup Time | 400 kHz mode      | 100                       |                                                                                                                                                                                                                                                                                       | ns   |       |                                             |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                                                                                   |      | ns    |                                             |  |

| IS26         | THD:DAT    | Data Input        | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                     |      | μS    |                                             |  |

|              |            | Hold Time         | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                     | 0.9  | μS    | -                                           |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                     | 0.3  | μS    |                                             |  |

| IS30         | TSU:STA    | Start Condition   | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   |      | μS    | Only relevant for Repeated                  |  |

|              |            | Setup Time        | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                   |      | μS    | Start condition                             |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                  |      | μS    |                                             |  |

| IS31         | THD:STA    | Start Condition   | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                   |      | μS    | After this period, the first                |  |

|              |            | Hold Time         | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                   |      | μS    | clock pulse is generated                    |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                  |      | μS    | -                                           |  |

| IS33         | Tsu:sto    | Stop Condition    | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   |      | μS    |                                             |  |

|              |            | Setup Time        | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                   | _    | μS    |                                             |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                                                                                                                                   |      | μS    | -                                           |  |

| IS34         | THD:STO    | Stop Condition    | 100 kHz mode              | 4000                                                                                                                                                                                                                                                                                  |      | ns    |                                             |  |

|              |            | Hold Time         | 400 kHz mode              | 600                                                                                                                                                                                                                                                                                   |      | ns    |                                             |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 250                                                                                                                                                                                                                                                                                   |      | ns    | -                                           |  |

| IS40         | TAA:SCL    | Output Valid      | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                     | 3500 | ns    | _                                           |  |

|              |            | From Clock        | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                     | 1000 | ns    | 1                                           |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                     | 350  | ns    | 1                                           |  |

| IS45         | TBF:SDA    | Bus Free Time     | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   |      | μS    | Time the bus must be free                   |  |

|              |            |                   | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                   |      | μS    | before a new transmission                   |  |

|              |            |                   | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   |      | μS    | can start                                   |  |

| IS50         | Св         | Bus Capacitive Lo |                           |                                                                                                                                                                                                                                                                                       | 400  | pF    |                                             |  |

#### TABLE 25-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| CHARAG       | AC<br>CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                 |                                             |         |   |    |   |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|---------|---|----|---|--|--|

| Param<br>No. | Symbol                                                                                                                                                                       | Characteristic                  | Characteristic Min Typ Max Units Conditions |         |   |    |   |  |  |

|              | Clock Parameters                                                                                                                                                             |                                 |                                             |         |   |    |   |  |  |

|              | -                                                                                                                                                                            |                                 |                                             |         |   |    |   |  |  |

| HAD50        | TAD                                                                                                                                                                          | ADC Clock Period <sup>(1)</sup> | 147                                         |         | — | ns | — |  |  |

| HAD50        | IAD                                                                                                                                                                          |                                 | 147<br>version R                            | <br>ate |   | ns |   |  |  |

#### TABLE 26-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

### TABLE 26-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                                                           |                                 |                                             |  |     |      | ed) |  |