Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

|                           | • 11                                                                              |

| Product Status            | Active                                                                            |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| Speed                     | 40 MIPs                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals               | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O             | 85                                                                                |

| Program Memory Size       | 128KB (128K x 8)                                                                  |

| Program Memory Type       | FLASH                                                                             |

| EEPROM Size               | -                                                                                 |

| RAM Size                  | 16K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters           | A/D 32x10b/12b                                                                    |

| Oscillator Type           | Internal                                                                          |

| perating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type             | Surface Mount                                                                     |

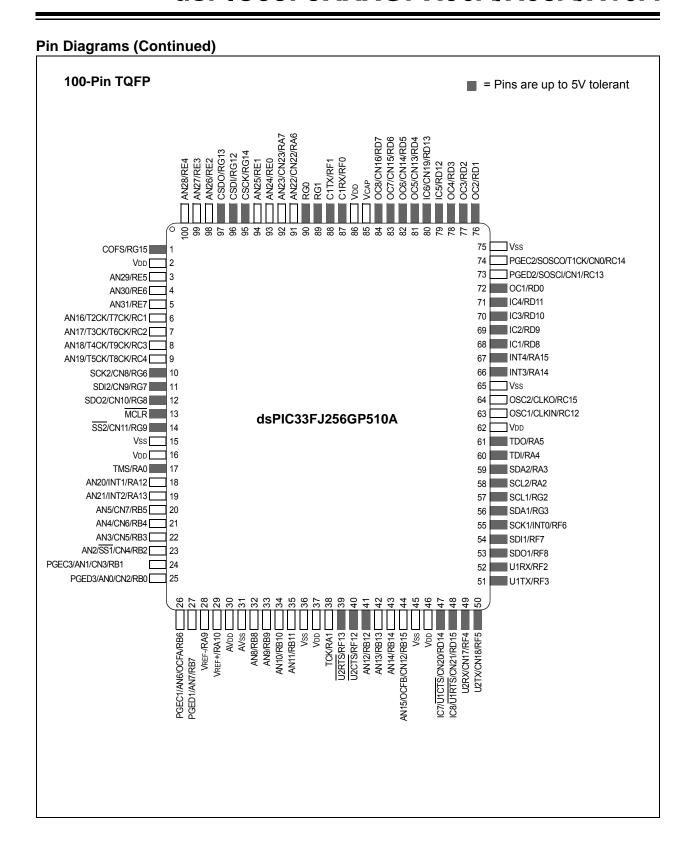

| Package / Case            | 100-TQFP                                                                          |

| Supplier Device Package   | 100-TQFP (12x12)                                                                  |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp710a-h-pt |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IADLE I-I.   | 1 11400     | I I/O DESC     | CRIFTIONS (CONTINUED)                                          |

|--------------|-------------|----------------|----------------------------------------------------------------|

| Pin Name     | Pin<br>Type | Buffer<br>Type | Description                                                    |

| RG0-RG3      | I/O         | ST             | PORTG is a bidirectional I/O port.                             |

| RG6-RG9      | I/O         | ST             | ·                                                              |

| RG12-RG15    | I/O         | ST             |                                                                |

| SCK1         | I/O         | ST             | Synchronous serial clock input/output for SPI1.                |

| SDI1         | I           | ST             | SPI1 data in.                                                  |

| SDO1         | 0           |                | SPI1 data out.                                                 |

| SS1          | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2         | I/O         | ST             | Synchronous serial clock input/output for SPI2.                |

| SDI2         | l           | ST             | SPI2 data in.                                                  |

| SDO2         | 0           | _              | SPI2 data out.                                                 |

| SS2          | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1         | I/O         | ST             | Synchronous serial clock input/output for I2C1.                |

| SDA1         | I/O         | ST             | Synchronous serial data input/output for I2C1.                 |

| SCL2         | I/O         | ST             | Synchronous serial clock input/output for I2C2.                |

| SDA2         | I/O         | ST             | Synchronous serial data input/output for I2C2.                 |

| SOSCI        | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise. |

| SOSCO        | 0           | _              | 32.768 kHz low-power oscillator crystal output.                |

| TMS          | I           | ST             | JTAG Test mode select pin.                                     |

| TCK          | !           | ST             | JTAG test clock input pin.                                     |

| TDI          |             | ST             | JTAG test data input pin.                                      |

| TDO          | 0           | _              | JTAG test data output pin.                                     |

| T1CK         | !           | ST             | Timer1 external clock input.                                   |

| T2CK         | !           | ST             | Timer2 external clock input.                                   |

| T3CK<br>T4CK |             | ST<br>ST       | Timer3 external clock input. Timer4 external clock input.      |

| T5CK         |             | ST             | Timer5 external clock input.  Timer5 external clock input.     |

| T6CK         |             | ST             | Timer6 external clock input.                                   |

| T7CK         | li          | ST             | Timer7 external clock input.                                   |

| T8CK         | i           | ST             | Timer8 external clock input.                                   |

| T9CK         | i           | ST             | Timer9 external clock input.                                   |

| U1CTS        | ı           | ST             | UART1 clear to send.                                           |

| U1RTS        | Ö           | _              | UART1 ready to send.                                           |

| U1RX         | Ī           | ST             | UART1 receive.                                                 |

| U1TX         | Ö           | _              | UART1 transmit.                                                |

| U2CTS        | Ī           | ST             | UART2 clear to send.                                           |

| U2RTS        | 0           | _              | UART2 ready to send.                                           |

| U2RX         | I           | ST             | UART2 receive.                                                 |

| U2TX         | 0           | _              | UART2 transmit.                                                |

| VDD          | Р           | _              | Positive supply for peripheral logic and I/O pins.             |

| VCAP         | Р           | _              | CPU logic flter capacitor connection.                          |

| Vss          | Р           | _              | Ground reference for logic and I/O pins.                       |

| VREF+        | I           | Analog         | Analog voltage reference (high) input.                         |

| VREF-        | I           | Analog         | Analog voltage reference (low) input.                          |

|              |             |                |                                                                |

**Legend:** CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Analog = Analog input;

P = Power

els; O = Output;

I = Input

### TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7             | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------|---------|-------------------|-----------|---------|-------|-------|--------|--------|--------|---------------|

| XBREV    | 0050        | BREN   |        |        |        |        |        |       | 2       | <b<14:0></b<14:0> |           |         |       |       |        |        |        | xxxx          |

| DISICNT  | 0052        | _      | _      |        |        |        |        |       | Disable | Interrupts        | Counter R | egister |       |       |        |        |        | xxxx          |

| BSRAM    | 0750        | _      | _      | _      | _      | _      | _      | _     | _       | _                 | _         | _       | _     | _     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM    | 0752        | _      | _      | _      | _      | _      | _      | _     | _       | _                 | _         | _       | _     | _     | IW_SSR | IR_SSR | RL_SSR | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR dsPIC33FJXXXGP506A/510A/706A/708A/710A DEVICES ONLY

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11   | Bit 10                        | Bit 9 | Bit 8 | Bit 7              | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|----------|-------------------------------|-------|-------|--------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11SID | 046C |           | SID<10:3> |        |        |          | SID<2:0> — EXIDE — EID<17:16> |       |       |                    |          |       | 7:16> | xxxx  |       |       |       |               |

| C1RXF11EID | 046E | EID<15:8> |           |        |        | EID<7:0> |                               |       |       |                    |          |       | xxxx  |       |       |       |       |               |

| C1RXF12SID | 0470 |           |           |        | SID<   | 10:3>    |                               |       |       |                    | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472 | EID<15:8> |           |        |        | EID<7:0> |                               |       |       |                    |          |       | xxxx  |       |       |       |       |               |

| C1RXF13SID | 0474 |           |           |        | SID<   | 10:3>    |                               |       |       | SID<2:0> — EXIDE — |          |       |       | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXF13EID | 0476 |           |           |        | EID<   | 15:8>    |                               |       |       | EID<7:0>           |          |       |       |       |       |       | xxxx  |               |

| C1RXF14SID | 0478 |           |           |        | SID<   | 10:3>    |                               |       |       |                    | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A | EID<15:8> |           |        |        |          | EID<7:0>                      |       |       |                    |          |       | xxxx  |       |       |       |       |               |

| C1RXF15SID | 047C | SID<10:3> |           |        |        |          | SID<2:0>                      |       | _     | EXIDE              | _        | EID<1 | 7:16> | xxxx  |       |       |       |               |

| C1RXF15EID | 047E | EID<15:8> |           |        |        | EID<7:0> |                               |       |       |                    |          | xxxx  |       |       |       |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

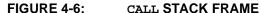

### 4.2.7 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-35 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

dsPlC33FJXXXGPX06A/X08A/X10A

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file reg-

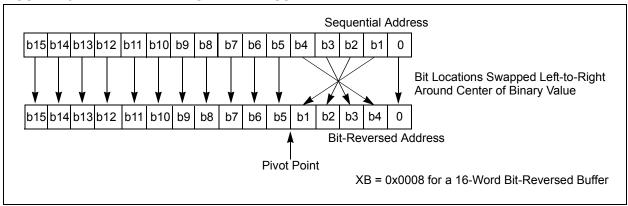

FIGURE 4-8: BIT-REVERSED ADDRESS EXAMPLE

TABLE 4-36: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | s       |    |    | Bit-Rev    | ersed Ad | dress   |

|----|----|-------|-----------|---------|----|----|------------|----------|---------|

| А3 | A2 | A1    | A0        | Decimal | А3 | A2 | <b>A</b> 1 | Α0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0          | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0          | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0          | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0          | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1          | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1          | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1          | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1          | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0          | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0          | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0          | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0          | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1          | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1          | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1          | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1          | 1        | 15      |

### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0     | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|-----------|-------|-----|-------|------------|-------|

| _      |       | T1IP<2:0> |       | _   |       | OC1IP<2:0> |       |

| bit 15 |       |           |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|-------|-------|------------|-------|-----|-------|-------------|-------|

| _     |       | IC1IP<2:0> |       | _   |       | INT0IP<2:0> |       |

| bit 7 |       |            |       |     |       |             | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 T1IP<2:0>: Timer1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 **INT0IP<2:0>:** External Interrupt 0 Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

of - interrupt is priority i

000 = Interrupt source is disabled

### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0    | R/W-1 | R/W-0     | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|-----------|-------|-----|-------|------------|-------|

| _      |       | T4IP<2:0> |       | _   |       | OC4IP<2:0> |       |

| bit 15 |       |           |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|-------|-------|------------|-------|-----|-------|-------------|-------|

| _     |       | OC3IP<2:0> |       | _   |       | DMA2IP<2:0> |       |

| bit 7 |       |            |       |     |       |             | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **T4IP<2:0>:** Timer4 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 OC3IP<2:0>: Output Compare Channel 3 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 DMA2IP<2:0>: DMA Channel 2 Data Transfer Complete Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

| USPIC33FJXXXGPXU0A/XU0A/XIUA |  |  |                |                       |                       |  |  |  |  |

|------------------------------|--|--|----------------|-----------------------|-----------------------|--|--|--|--|

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  |                |                       |                       |  |  |  |  |

|                              |  |  | JAAAGPAUOA/AUO | JAKAGP KUGA/KUGA/K TU | JAKAGPAUGA/AUGA/A TUA |  |  |  |  |

### REGISTER 15-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| _      | _   | OCSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|-------|-----|-----|---------|--------|-------|----------|-------|

| _     | _   | _   | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7 |     |     |         |        |       |          | bit 0 |

Legend:HC = Hardware Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 OCSIDL: Stop Output Compare in Idle Mode Control bit

1 = Output Compare x halts in CPU Idle mode

0 = Output Compare x continues to operate in CPU Idle mode

bit 12-5 Unimplemented: Read as '0'

bit 4 OCFLT: PWM Fault Condition Status bit

1 = PWM Fault condition has occurred (cleared in hardware only)

0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111)

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for Compare x

0 = Timer2 is the clock source for Compare x

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx, Fault pin enabled

110 = PWM mode on OCx, Fault pin disabled

101 = Initialize OCx pin low, generate continuous output pulses on OCx pin

100 = Initialize OCx pin low, generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high, compare event forces OCx pin low

001 = Initialize OCx pin low, compare event forces OCx pin high

000 = Output compare channel is disabled

### REGISTER 19-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

**Legend:** C = Clear only bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 RXOVF15:RXOVF0: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

### REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

**Legend:** C = Clear only bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 RXOVF31:RXOVF16: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

TABLE 25-28: SPIX MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | AC CHARACTERISTICS                       |                                             |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extende |     |     |  |  |  |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE                                                                                                                                                                                                                                              | СКР | SMP |  |  |  |

| 15 MHz               | Table 25-29                              | _                                           |                                            | 0,1                                                                                                                                                                                                                                              | 0,1 | 0,1 |  |  |  |

| 10 MHz               | _                                        | Table 25-30                                 |                                            | 1                                                                                                                                                                                                                                                | 0,1 | 1   |  |  |  |

| 10 MHz               | _                                        | Table 25-31                                 |                                            | 0                                                                                                                                                                                                                                                | 0,1 | 1   |  |  |  |

| 15 MHz               | _                                        | _                                           | Table 25-32                                | 1                                                                                                                                                                                                                                                | 0   | 0   |  |  |  |

| 11 MHz               | <u> </u>                                 | _                                           | Table 25-33                                | 1                                                                                                                                                                                                                                                | 1   | 0   |  |  |  |

| 15 MHz               | <u> </u>                                 | _                                           | Table 25-34                                | 0                                                                                                                                                                                                                                                | 1   | 0   |  |  |  |

| 11 MHz               | _                                        | _                                           | Table 25-35                                | 0                                                                                                                                                                                                                                                | 0   | 0   |  |  |  |

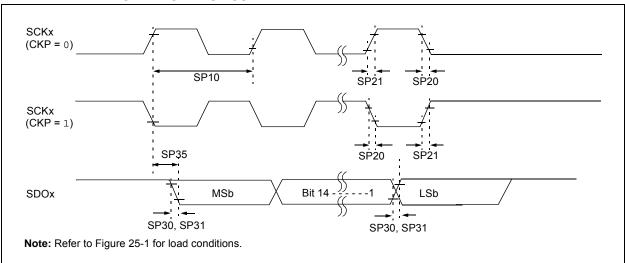

FIGURE 25-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

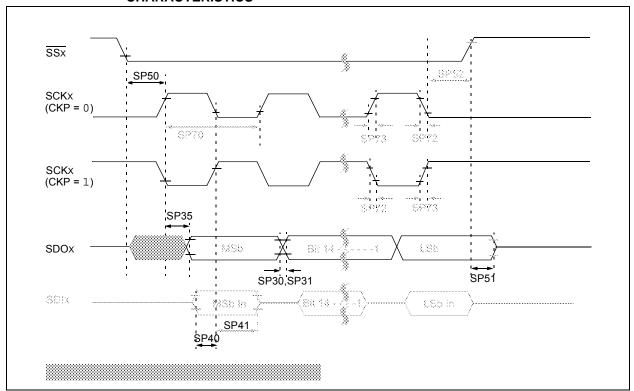

FIGURE 25-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

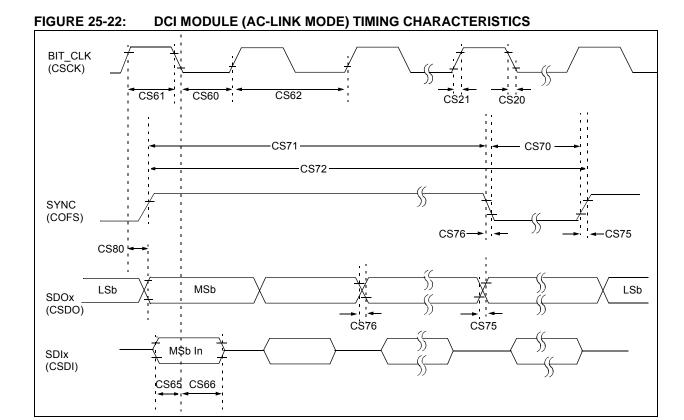

TABLE 25-39: DCI MODULE (AC-LINK MODE) TIMING REQUIREMENTS

| AC CHA       | RACTERIS | STICS                                          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} -40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extermination of the conditions of the con |      |    |    | Ta ≤ +85°C              |

|--------------|----------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|----|-------------------------|

| Param<br>No. | Symbol   | Characteristic <sup>(1,2)</sup>                | Min Typ <sup>(3)</sup> Max Units Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |    |    | Conditions              |

| CS60         | TBCLKL   | BIT_CLK Low Time                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40.7 | 45 | ns | _                       |

| CS61         | TBCLKH   | BIT_CLK High Time                              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40.7 | 45 | ns | _                       |

| CS62         | TBCLK    | BIT_CLK Period                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81.4 | _  | ns | Bit clock is input      |

| CS65         | TSACL    | Input Setup Time to Falling Edge of BIT_CLK    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 10 | ns | _                       |

| CS66         | THACL    | Input Hold Time from Falling Edge of BIT_CLK   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 10 | ns | _                       |

| CS70         | TSYNCLO  | SYNC Data Output Low Time                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19.5 | _  | μS | Note 1                  |

| CS71         | Tsynchi  | SYNC Data Output High Time                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.3  | _  | μS | Note 1                  |

| CS72         | TSYNC    | SYNC Data Output Period                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20.8 | _  | μS | Note 1                  |

| CS75         | TRACL    | Rise Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10   | 25 | ns | CLOAD = 50 pF, VDD = 5V |

| CS76         | TFACL    | Fall Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10   | 25 | ns | CLOAD = 50 pF, VDD = 5V |

| CS77         | TRACL    | Rise Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 30 | ns | CLOAD = 50 pF, VDD = 3V |

| CS78         | TFACL    | Fall Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 30 | ns | CLOAD = 50 pF, VDD = 3V |

| CS80         | TOVDACL  | Output Valid Delay from Rising Edge of BIT_CLK | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 15 | ns | _                       |

Note 1: These parameters are characterized but not tested in manufacturing.

- 2: These values assume BIT\_CLK frequency is 12.288 MHz.

- **3:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters for high temperature devices. However, all AC timing specifications in this section are the same as those in Section 25.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter OS53 in **Section 25.2 "AC Characteristics and Timing Parameters"** is the Industrial and Extended temperature equivalent of HOS53.

TABLE 26-7: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                                                                                           |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature Operating voltage VDD range as described in Table 26-1. |

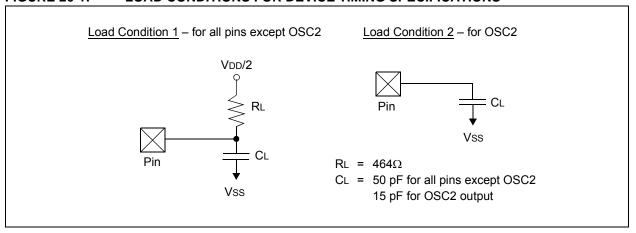

### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 26-8: PLL CLOCK TIMING SPECIFICATIONS

| _            | C<br>TERISTICS |                                        | andard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) perating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +150^{\circ}\text{C}$ for High Temperature |     |   |   |                             |  |  |

|--------------|----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|---|-----------------------------|--|--|

| Param<br>No. | Symbol         | Characteristic                         | Characteristic Min Typ Max Units Conditions                                                                                                                                |     |   |   |                             |  |  |

| HOS53        | DCLK           | CLKO Stability (Jitter) <sup>(1)</sup> | -5                                                                                                                                                                         | 0.5 | 5 | % | Measured over 100 ms period |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

| USPIC33FJXXXGPXU0A/XU0A/XIUA |  |  |  |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|--|--|--|

| NOTES:                       |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

NOTES:

| USPIC33FJXXXGPXU0A/XU0A/XIUA |  |  |  |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|--|--|--|

| NOTES:                       |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |  |  |