Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                            |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp710a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

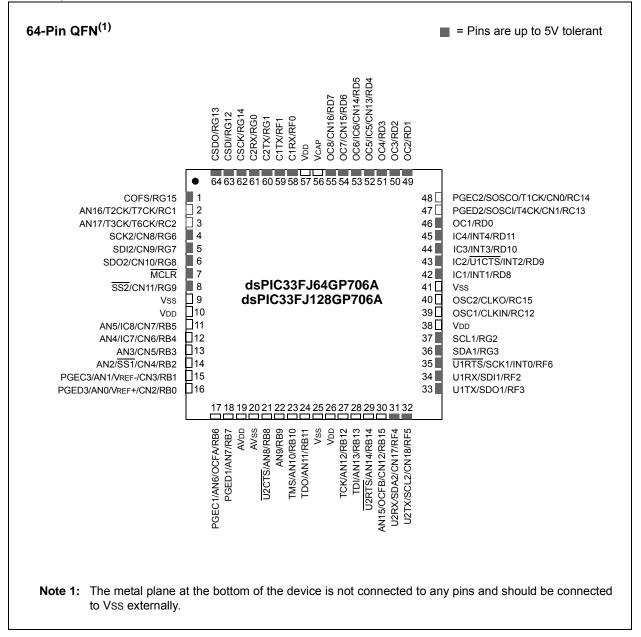

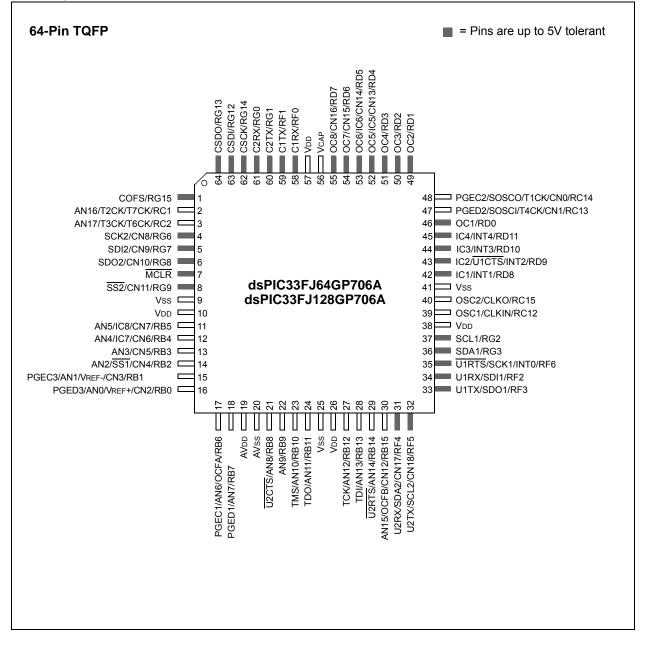

#### **Pin Diagrams (Continued)**

#### **Pin Diagrams (Continued)**

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/ PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

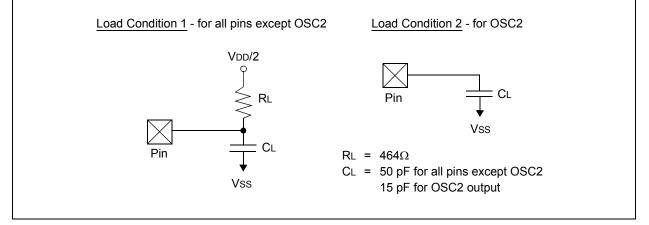

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXGPX06A/ X08A/X10A family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| bit 8  |    | DC: MCU ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | <ul> <li>1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data)<br/>of the result occurred</li> </ul>                                                                                                                                                                                                                                                                             |

|        |    | <ul> <li>0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                |

| bit 7- | 5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|        |    | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4  |    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |    | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3  |    | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |    | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2  |    | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |    | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                |

| bit 1  |    | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |    | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                               |

| bit 0  |    | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |    | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

| Note   | 1: | This bit may be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                  |

|        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and, thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes:

• Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF), or maximally negative 9.31 value (0x800000000), into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against errone-ous data or unexpected algorithm problems (e.g., gain calculations).

Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF), or maximally negative 1.31 value (0x008000000), into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

#### 3.6.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 3.6.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.2.4 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator write-back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

|                 | R/W-0 <sup>(1)</sup>                                                                                     | R/W-0 <sup>(1)</sup>               | U-0           | U-0                             | U-0                  | U-0                  | U-0                  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------|------------------------------------|---------------|---------------------------------|----------------------|----------------------|----------------------|--|--|--|

| WR              | WREN                                                                                                     | WRERR                              | —             |                                 |                      |                      | _                    |  |  |  |

| bit 15          |                                                                                                          |                                    |               |                                 |                      |                      | bit                  |  |  |  |

| U-0             | R/W-0 <sup>(1)</sup>                                                                                     | U-0                                | U-0           | R/W-0 <sup>(1)</sup>            | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |  |  |  |

| 0-0             | ERASE                                                                                                    | 0-0                                | 0-0           | N/W-0.7                         | -                    | ><3:0>(2)            | N/ VV-U * 7          |  |  |  |

| <br>bit 7       | LINAGE                                                                                                   | _                                  |               |                                 |                      | <3.0×7               | bit (                |  |  |  |

|                 |                                                                                                          |                                    |               |                                 |                      |                      |                      |  |  |  |

| Legend:         |                                                                                                          | SO = Settable                      | e only bit    |                                 |                      |                      |                      |  |  |  |

| R = Readable    | bit                                                                                                      | W = Writable                       | bit           | U = Unimpler                    | nented bit, read     | l as '0'             |                      |  |  |  |

| -n = Value at F | POR                                                                                                      | '1' = Bit is set                   |               | '0' = Bit is cle                | ared                 | x = Bit is unkr      | nown                 |  |  |  |

| bit 15          | WR: Write Co                                                                                             | ntral hit                          |               |                                 |                      |                      |                      |  |  |  |

| DIL 15          |                                                                                                          |                                    | w program o   | r erase operatio                | n The operation      | on is self-timed     | and the hit i        |  |  |  |

|                 |                                                                                                          | by hardware on                     |               |                                 |                      |                      |                      |  |  |  |

|                 |                                                                                                          |                                    |               | lete and inactive               | 9                    |                      |                      |  |  |  |

| bit 14          | •                                                                                                        | -                                  | ·             |                                 |                      |                      |                      |  |  |  |

|                 | WREN: Write Enable bit<br>1 = Enable Flash program/erase operations                                      |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 |                                                                                                          | ash program/er                     |               |                                 |                      |                      |                      |  |  |  |

| bit 13          | WRERR: Wri                                                                                               | te Sequence E                      | rror Flag bit |                                 |                      |                      |                      |  |  |  |

|                 | 1 = An improper program or erase sequence attempt or termination has occurred (bit is set                |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 |                                                                                                          |                                    | -             | npleted normally                | 1                    |                      |                      |  |  |  |

| bit 12-7        | Unimplemen                                                                                               | ted: Read as '                     | 0'            |                                 |                      |                      |                      |  |  |  |

| bit 6           | ERASE: Erase/Program Enable bit                                                                          |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 |                                                                                                          |                                    |               | ed by NVMOP<3<br>ified by NVMOF |                      |                      |                      |  |  |  |

| bit 5-4         |                                                                                                          | ited: Read as '                    | -             |                                 |                      |                      |                      |  |  |  |

| bit 3-0         | -                                                                                                        |                                    |               | ts(2)                           |                      |                      |                      |  |  |  |

|                 | NVMOP<3:0>: NVM Operation Select bits <sup>(2)</sup><br>If ERASE = 1:                                    |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1111 = Memory bulk erase operation                                                                       |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1110 = Reserved                                                                                          |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1101 = Erase General Segment                                                                             |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1100 = Erase Secure Segment                                                                              |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1011 = Reserved<br>0011 = No operation                                                                   |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 0011 = No operation<br>0010 = Memory page erase operation                                                |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 0001 = No operation                                                                                      |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 0000 = Erase a single Configuration register byte                                                        |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | If ERASE = 0:                                                                                            |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1111 = No operation                                                                                      |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1110 = Reserved                                                                                          |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1101 = No operation<br>1100 = No operation                                                               |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 1100 = No operation<br>1011 = Reserved                                                                   |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 0011 = Memo                                                                                              | ory word progra                    | am operation  |                                 |                      |                      |                      |  |  |  |

|                 | 0010 = No op                                                                                             |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 | 0001 = Memory row program operation                                                                      |                                    |               |                                 |                      |                      |                      |  |  |  |

|                 |                                                                                                          | ory row prograr<br>ram a single Cc |               |                                 |                      |                      |                      |  |  |  |

| REGISTE    | R 6-1: RCON                                       | I: RESET COI                                                                               | NTROL REC                                   | GISTER <sup>(1)</sup>         |                   |                  |                      |

|------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------|-------------------|------------------|----------------------|

| R/W-0      | R/W-0                                             | U-0                                                                                        | U-0                                         | U-0                           | U-0               | U-0              | R/W-0                |

| TRAPR      | IOPUWR                                            |                                                                                            | _                                           |                               |                   | _                | VREGS <sup>(3)</sup> |

| bit 15     |                                                   |                                                                                            |                                             |                               |                   | •<br>•           | bit 8                |

| R/W-0      | R/W-0                                             | R/W-0                                                                                      | R/W-0                                       | R/W-0                         | R/W-0             | R/W-1            | R/W-1                |

| EXTR       | SWR                                               | SWDTEN <sup>(2)</sup>                                                                      | WDTO                                        | SLEEP                         | IDLE              | BOR              | POR                  |

| bit 7      |                                                   |                                                                                            |                                             |                               |                   |                  | bit (                |

| Legend:    |                                                   |                                                                                            |                                             |                               |                   |                  |                      |

| R = Reada  | ble bit                                           | W = Writable                                                                               | bit                                         | U = Unimpler                  | mented bit, read  | as '0'           |                      |

| -n = Value | at POR                                            | '1' = Bit is set                                                                           |                                             | '0' = Bit is cle              | ared              | x = Bit is unk   | nown                 |

| bit 15     | 1 = A Trap C                                      | o Reset Flag bit<br>onflict Reset ha                                                       | s occurred                                  | d                             |                   |                  |                      |

| bit 14     | IOPUWR: Ille<br>1 = An illega<br>Address          | onflict Reset ha<br>gal Opcode or<br>al opcode deter<br>Pointer caused<br>I opcode or unit | Uninitialized<br>ction, an illeç<br>a Reset | W Access Res<br>gal address m | ode or uninitial  | ized W regist    | er used as a         |

| bit 13-9   | •                                                 | ted: Read as '                                                                             |                                             |                               |                   |                  |                      |

| bit 8      | VREGS: Volt<br>1 = Voltage F                      | age Regulator S<br>Regulator is acti<br>Regulator goes i                                   | Standby Durir<br>ve during Sle              | ep mode                       | еер               |                  |                      |

| bit 7      | EXTR: Extern<br>1 = A Master                      | nal Reset (MCL<br>Clear (pin) Res<br>Clear (pin) Res                                       | R) Pin bit<br>set has occur                 | red                           |                   |                  |                      |

| bit 6      | 1 <b>= A</b> reset                                | are Reset (Instru<br>instruction has<br>instruction has                                    | been execute                                | ed                            |                   |                  |                      |

| bit 5      | <b>SWDTEN:</b> So<br>1 = WDT is e<br>0 = WDT is d |                                                                                            | Disable of W                                | DT bit <sup>(2)</sup>         |                   |                  |                      |

| bit 4      | 1 = WDT time                                      | hdog Timer Tim<br>e-out has occur<br>e-out has not oc                                      | red                                         | t                             |                   |                  |                      |

| bit 3      | <b>SLEEP:</b> Wak<br>1 = Device ha                | e-up from Slee<br>as been in Slee<br>as not been in S                                      | o Flag bit<br>p mode                        |                               |                   |                  |                      |

| bit 2      | IDLE: Wake-<br>1 = Device w                       | up from Idle Fla<br>as in Idle mode<br>as not in Idle m                                    | g bit                                       |                               |                   |                  |                      |

| bit 1      | <b>BOR:</b> Brown-<br>1 = A Brown-                | -out Reset Flag<br>out Reset has o<br>out Reset has r                                      | bit<br>occurred                             |                               |                   |                  |                      |

|            | All of the Reset sta<br>cause a device Re         |                                                                                            | set or cleare                               | d in software. S              | Setting one of th | ese bits in soft | ware does not        |

| 2:         | If the FWDTEN Co                                  | onfiguration bit i                                                                         | s '1' (unprog                               | rammed), the V                | VDT is always e   | nabled, regard   | dless of the         |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

SWDTEN bit setting.

3: For dsPIC33FJ256GPX06A/X08A/X10A devices, this bit is unimplemented and reads back programmed value.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | Request (IRQ) IVT Address AIVT Address |                   | Interrupt Source                   |

|------------------|--------------------------------------|----------------------------------------|-------------------|------------------------------------|

| 54               | 46                                   | 0x000070                               | 0x000170          | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072                               | 0x000172          | T6 – Timer6                        |

| 56               | 48                                   | 0x000074                               | 0x000174          | T7 – Timer7                        |

| 57               | 49                                   | 0x000076                               | 0x000176          | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078                               | 0x000178          | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A                               | 0x00017A          | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C                               | 0x00017C          | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E                               | 0x00017E          | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080                               | 0x000180          | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082                               | 0x000182          | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084                               | 0x000184          | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086                               | 0x000186          | Reserved                           |

| 66               | 58                                   | 0x000088                               | 0x000188          | Reserved                           |

| 67               | 59                                   | 0x00008A                               | 0x00018A          | DCIE – DCI Error                   |

| 68               | 60                                   | 0x00008C                               | 0x00018C          | DCID – DCI Transfer Done           |

| 69               | 61                                   | 0x00008E                               | 0x00018E          | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090                               | 0x000190          | Reserved                           |

| 71               | 63                                   | 0x000092                               | 0x000192          | Reserved                           |

| 72               | 64                                   | 0x000094                               | 0x000194          | Reserved                           |

| 73               | 65                                   | 0x000096                               | 0x000196          | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098                               | 0x000198          | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A                               | 0x00019A          | Reserved                           |

| 76               | 68                                   | 0x00009C                               | 0x00019C          | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E                               | 0x00019E          | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0                               | 0x0001A0          | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2                               | 0x0001A2          | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-0x0000FE                      | 0x0001A4-0x0001FE | Reserved                           |

### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0 0x000004  |              | Reserved           |

| 1             | 1 0x000006  |              | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 7 0x000012  |              | Reserved           |

#### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                                                                | R/W-0          | U-0              | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------|-----------------|-------|--|--|--|--|

| —             |                                                                                                                           | IC5IP<2:0>                                                                                                                                           |                | —                |                | IC4IP<2:0>      |       |  |  |  |  |

| bit 15        |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 | bit 8 |  |  |  |  |

|               |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                                                                | R/W-0          | U-0              | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |

|               |                                                                                                                           | IC3IP<2:0>                                                                                                                                           |                | —                |                | DMA3IP<2:0>     |       |  |  |  |  |

| bit 7         |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 | bit ( |  |  |  |  |

| Legend:       |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

| R = Readable  | e bit                                                                                                                     | W = Writable b                                                                                                                                       | oit            | U = Unimpler     | nented bit, re | ad as '0'       |       |  |  |  |  |

| -n = Value at | POR                                                                                                                       | '1' = Bit is set                                                                                                                                     |                | '0' = Bit is cle | ared           | x = Bit is unkn | own   |  |  |  |  |

| bit 15        | Unimpleme                                                                                                                 | nted: Read as 'o                                                                                                                                     | )'             |                  |                |                 |       |  |  |  |  |

| bit 14-12     | -                                                                                                                         |                                                                                                                                                      |                | rrupt Prioritv b | its            |                 |       |  |  |  |  |

|               |                                                                                                                           | <b>IC5IP&lt;2:0&gt;:</b> Input Capture Channel 5 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)               |                |                  |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | 001 = Interrupt is priority 1                                                                                             |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               |                                                                                                                           | upt source is disa                                                                                                                                   | abled          |                  |                |                 |       |  |  |  |  |

| bit 11        | Unimpleme                                                                                                                 | nted: Read as 'o                                                                                                                                     | )'             |                  |                |                 |       |  |  |  |  |

| bit 10-8      | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits                                                               |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

| bit 7         |                                                                                                                           | nted: Read as '0                                                                                                                                     |                |                  |                |                 |       |  |  |  |  |

| bit 6-4       | -                                                                                                                         |                                                                                                                                                      |                | rrunt Priority b | its            |                 |       |  |  |  |  |

|               | IC3IP<2:0>: Input Capture Channel 3 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      | 5              | ,,               |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | •<br>001 = Interrupt is priority 1                                                                                        |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | 000 = Interrupt source is disabled                                                                                        |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

| bit 3         | Unimpleme                                                                                                                 | nted: Read as '0                                                                                                                                     | )'             |                  |                |                 |       |  |  |  |  |

| bit 2-0       | DMA3IP<2:0                                                                                                                | D>: DMA Channe                                                                                                                                       | el 3 Data Trar | sfer Complete    | Interrupt Pric | rity bits       |       |  |  |  |  |

|               | 111 = Interru                                                                                                             | <b>DMA3IP&lt;2:0&gt;:</b> DMA Channel 3 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                |                  |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

|               | 001 = Interru                                                                                                             | int is priority 1                                                                                                                                    |                |                  |                |                 |       |  |  |  |  |

|               |                                                                                                                           |                                                                                                                                                      |                |                  |                |                 |       |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                                               | R/W-0                                             | R/W-0          | R/W-0                             | U-0            | U-0             | U-0                                                                                  |  |  |  |  |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|-----------------------------------|----------------|-----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| CHEN         | SIZE                                                                                                                                                                                                | DIR                                               | HALF           | NULLW                             | _              | —               |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 15       |                                                                                                                                                                                                     |                                                   |                |                                   |                |                 | bit                                                                                  |  |  |  |  |  |  |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                 | R/W-0                                             | R/W-0          | U-0                               | U-0            | R/W-0           | R/W-0                                                                                |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                     | AMOD                                              | -              | _                                 |                | MODE            |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                                     |                                                   |                |                                   |                |                 | bit                                                                                  |  |  |  |  |  |  |  |  |  |  |

| Legend:      |                                                                                                                                                                                                     |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| R = Readab   | la hit                                                                                                                                                                                              | W = Writable                                      | hit            | II – Unimplon                     | contod hit roa | d aa '0'        |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| -n = Value a |                                                                                                                                                                                                     | '1' = Bit is set                                  |                | U = Unimplen<br>'0' = Bit is clea |                | x = Bit is unkr | 0.000                                                                                |  |  |  |  |  |  |  |  |  |  |

|              | IPOR                                                                                                                                                                                                | I = DILIS SEL                                     |                |                                   | areu           | X - BILIS UTKI  | IOWII                                                                                |  |  |  |  |  |  |  |  |  |  |

| bit 15       | CHEN: Chan                                                                                                                                                                                          | nel Enable bit                                    |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 1 = Channel e                                                                                                                                                                                       | 1 = Channel enabled                               |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 0 = Channel disabled                                                                                                                                                                                |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 14       | SIZE: Data Transfer Size bit                                                                                                                                                                        |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 1 = Byte<br>0 = Word                                                                                                                                                                                |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 13       | DIR: Transfer Direction bit (source/destination bus select)                                                                                                                                         |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                   |                | to peripheral ad<br>o DMA RAM ad  |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 12       | HALF: Early Block Transfer Complete Interrupt Select bit                                                                                                                                            |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Initiate block transfer complete interrupt when half of the data has been moved</li> <li>0 = Initiate block transfer complete interrupt when all of the data has been moved</li> </ul> |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 11       | NULLW: Null                                                                                                                                                                                         | NULLW: Null Data Peripheral Write Mode Select bit |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | <ul> <li>1 = Null data write to peripheral in addition to DMA RAM write (DIR bit must also be clear)</li> <li>0 = Normal operation</li> </ul>                                                       |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 10-6     | Unimplemen                                                                                                                                                                                          | ted: Read as '                                    | 0'             |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 5-4      | AMODE<1:0                                                                                                                                                                                           | >: DMA Chann                                      | el Operating I | Mode Select bit                   | S              |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 11 = Reserved                                                                                                                                                                                       |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 10 = Peripheral Indirect Addressing mode                                                                                                                                                            |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | 01 = Register Indirect without Post-Increment mode<br>00 = Register Indirect with Post-Increment mode                                                                                               |                                                   |                |                                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 3-2      | -                                                                                                                                                                                                   | ted: Read as '                                    |                | it mode                           |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 0 2      | -                                                                                                                                                                                                   |                                                   |                | ode Select bits                   |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                     |                                                   |                |                                   | ansfer from/to | each DMA RAM    | buffer)                                                                              |  |  |  |  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                     | ous, Ping-Pong                                    |                |                                   |                |                 | 201101/                                                                              |  |  |  |  |  |  |  |  |  |  |

|              | 01 = One-Sh                                                                                                                                                                                         | ot, Ping-Pong r                                   | nodes disable  | ed                                |                |                 |                                                                                      |  |  |  |  |  |  |  |  |  |  |

|              | an Oration                                                                                                                                                                                          |                                                   |                |                                   |                |                 | 01 = One-Shot, Ping-Pong modes disabled<br>00 = Continuous, Ping-Pong modes disabled |  |  |  |  |  |  |  |  |  |  |

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0        | R-0                  | R-0                                                                                                                                               | R-0              | U-0                    | R/W-y           | R/W-y            | R/W-y          |  |  |  |  |

|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|-----------------|------------------|----------------|--|--|--|--|

| _          |                      | COSC<2:0>                                                                                                                                         |                  |                        |                 | NOSC<2:0>(2)     |                |  |  |  |  |

| bit 15     |                      |                                                                                                                                                   |                  |                        |                 |                  | bit 8          |  |  |  |  |

|            |                      |                                                                                                                                                   |                  |                        |                 |                  |                |  |  |  |  |

| R/W-0      | U-0                  | R-0                                                                                                                                               | U-0              | R/C-0                  | U-0             | R/W-0            | R/W-0          |  |  |  |  |