## Microchip Technology - DSPIC33FJ128GP710AT-I/PF Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Details                    |                                                                                    |

| Product Status             | Obsolete                                                                           |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 32x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp710at-i-pf |

### 3.6.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly, For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.6.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and between bit positions 0 to 16 for left shifts.

TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR dsPIC33FJXXXGP506A/510A/706A/708A/710A DEVICES ONLY

| F          | _    |           |           |           |        |                           |                               |          |       |          |                    |       |       |       |       |       |       |               |

|------------|------|-----------|-----------|-----------|--------|---------------------------|-------------------------------|----------|-------|----------|--------------------|-------|-------|-------|-------|-------|-------|---------------|

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13    | Bit 12 | Bit 11                    | Bit 10                        | Bit 9    | Bit 8 | Bit 7    | Bit 6              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11SID | 046C |           |           | SID<10:3> |        |                           | SID<2:0> — EXIDE — EID<17:16> |          |       |          |                    |       | 7:16> | xxxx  |       |       |       |               |

| C1RXF11EID | 046E | EID<15:8> |           |           |        |                           |                               | EID<7:0> |       |          |                    |       |       |       | xxxx  |       |       |               |

| C1RXF12SID | 0470 | SID<10:3> |           |           |        |                           | SID<2:0> — EXIDE — EID<17:16> |          |       |          |                    |       | 7:16> | xxxx  |       |       |       |               |

| C1RXF12EID | 0472 |           | EID<15:8> |           |        |                           |                               | EID<7:0> |       |          |                    |       |       |       | xxxx  |       |       |               |

| C1RXF13SID | 0474 |           |           |           | SID<   | 10:3>                     |                               |          |       |          | SID<2:0>           |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476 |           |           |           | EID<   | 15:8>                     |                               |          |       | EID<7:0> |                    |       |       |       |       | xxxx  |       |               |

| C1RXF14SID | 0478 |           |           |           | SID<   | 10:3>                     |                               |          |       |          | SID<2:0> — EXIDE — |       |       |       |       | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A |           |           |           | EID<   | 15:8>                     |                               |          |       | EID<7:0> |                    |       |       |       | xxxx  |       |       |               |

| C1RXF15SID | 047C | SID<10:3> |           |           |        | SID<2:0> — EXIDE — EID<17 |                               |          | 7:16> | xxxx     |                    |       |       |       |       |       |       |               |

| C1RXF15EID | 047E | EID<15:8> |           |           |        |                           | EID<7:0>                      |          |       |          |                    |       | xxxx  |       |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2009-2012 Microchip Technology Inc.

ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR dsPIC33FJXXXGP706A/708A/710A DEVICES ONLY **TABLE 4-23**:

| File Name  | Addr      | Bit 15    | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10                                                   | Bit 9    | Bit 8        | Bit 7                      | Bit 6      | Bit 5  | Bit 4 | Bit 3              | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|-----------|-----------|-----------------------|--------|--------|--------|----------------------------------------------------------|----------|--------------|----------------------------|------------|--------|-------|--------------------|--------|--------|--------|---------------|

|            | 0500      |           |                       |        |        |        |                                                          | Se       | e definition | when WIN                   | I = x      |        |       |                    |        |        |        |               |

|            | -<br>051E |           |                       |        |        |        |                                                          |          |              |                            |            |        |       |                    |        |        |        |               |

| C2BUFPNT1  | 0520      |           | F3BF                  | P<3:0> |        |        | F2BP                                                     | <3:0>    |              |                            | F1BF       | <3:0>  |       |                    | F0BF   | P<3:0> |        | 0000          |

| C2BUFPNT2  | 0522      |           | F7BF                  | P<3:0> |        |        | F6BP                                                     | <3:0>    |              | F5BP<3:0> F4BP<3:0>        |            |        |       |                    |        | 0000   |        |               |

| C2BUFPNT3  | 0524      |           | F11BP<3:0> F10BP<3:0> |        |        |        |                                                          |          | F9BF         | <3:0>                      |            |        | F8BF  | P<3:0>             |        | 0000   |        |               |

| C2BUFPNT4  | 0526      |           | F15BP<3:0> F14BP<3:0> |        |        |        |                                                          |          |              | F13BF                      | P<3:0>     |        |       | F12B               | P<3:0> |        | 0000   |               |

| C2RXM0SID  | 0530      |           | SID<10:3>             |        |        |        |                                                          |          | SID<2:0>     |                            | _          | MIDE   | _     | EID<               | 17:16> | xxxx   |        |               |

| C2RXM0EID  | 0532      |           | EID<15:8>             |        |        |        |                                                          |          |              |                            |            |        | EID<  | <7:0>              |        |        |        | xxxx          |

| C2RXM1SID  | 0534      |           | SID<10:3>             |        |        |        |                                                          |          |              | SID<2:0>                   |            | _      | MIDE  | _                  | EID<   | 17:16> | xxxx   |               |

| C2RXM1EID  | 0536      |           | EID<15:8>             |        |        |        |                                                          |          |              |                            |            | EID<   | <7:0> |                    |        |        | xxxx   |               |

| C2RXM2SID  | 0538      |           | SID<10:3>             |        |        |        |                                                          |          | SID<2:0>     |                            | _          | MIDE   | _     | EID<               | 17:16> | xxxx   |        |               |

| C2RXM2EID  | 053A      |           |                       |        | EID<   | 15:8>  | 3>                                                       |          |              |                            |            |        | EID<  | <7:0>              |        |        |        | xxxx          |

| C2RXF0SID  | 0540      |           |                       |        | SID<   | 10:3>  | 3>                                                       |          |              |                            | SID<2:0> — |        |       | EXIDE — EID<17:16> |        |        | 17:16> | xxxx          |

| C2RXF0EID  | 0542      |           | EID<15:8>             |        |        |        |                                                          |          |              |                            | EID<       | <7:0>  |       |                    |        | xxxx   |        |               |

| C2RXF1SID  | 0544      | SID<10:3> |                       |        |        |        |                                                          | SID<2:0> |              | _                          | EXIDE      | _      | EID<  | 17:16>             | xxxx   |        |        |               |

| C2RXF1EID  | 0546      |           |                       |        | EID<   | 15:8>  |                                                          |          |              |                            |            |        | EID<  | <7:0>              |        |        |        | xxxx          |

| C2RXF2SID  | 0548      |           |                       |        | SID<   | 10:3>  |                                                          |          |              |                            | SID<2:0>   |        | _     | EXIDE              | _      | EID<   | 17:16> | xxxx          |

| C2RXF2EID  | 054A      |           |                       |        | EID<   | 15:8>  |                                                          |          |              | EID<7:0>                   |            |        |       |                    |        |        | xxxx   |               |

| C2RXF3SID  | 054C      |           |                       |        | SID<   | 10:3>  |                                                          |          |              | SID<2:0> — EXIDE — EID<17: |            |        |       |                    | 17:16> | xxxx   |        |               |

| C2RXF3EID  | 054E      |           |                       |        | EID<   | 15:8>  |                                                          |          |              | EID<7:0>                   |            |        |       |                    |        | xxxx   |        |               |

| C2RXF4SID  | 0550      |           |                       |        | SID<   | 10:3>  |                                                          |          |              | SID<2:0> — EXIDE —         |            |        |       | EID<               | 17:16> | xxxx   |        |               |

| C2RXF4EID  | 0552      |           |                       |        | EID<   | 15:8>  |                                                          |          |              | EID<7:0>                   |            |        |       |                    |        |        | xxxx   |               |

| C2RXF5SID  | 0554      |           |                       |        | SID<   | 10:3>  |                                                          |          |              |                            | SID<2:0>   |        | _     | EXIDE              | _      | EID<   | 17:16> | xxxx          |

| C2RXF5EID  | 0556      |           |                       |        | EID<   | 15:8>  |                                                          |          |              |                            |            |        | EID<  | <7:0>              | 1      |        |        | xxxx          |

| C2RXF6SID  | 0558      |           |                       |        | SID<   | 10:3>  |                                                          |          |              |                            | SID<2:0>   |        | _     | EXIDE              | _      | EID<   | 17:16> | xxxx          |

| C2RXF6EID  | 055A      |           |                       |        | EID<   | 15:8>  |                                                          |          |              |                            |            |        | EID<  | <7:0>              | 1      |        |        | xxxx          |

| C2RXF7SID  | 055C      |           |                       |        | SID<   | 10:3>  |                                                          |          |              |                            | SID<2:0>   |        | _     | EXIDE              | _      | EID<   | 17:16> | xxxx          |

| C2RXF7EID  | 055E      |           |                       |        | EID<   |        |                                                          |          |              |                            |            |        | EID<  | <7:0>              |        |        |        | xxxx          |

| C2RXF8SID  | 0560      | SID<10:3> |                       |        |        |        | SID         —         EXIDE         —         EID<17:16> |          |              |                            |            | 17:16> | xxxx  |                    |        |        |        |               |

| C2RXF8EID  | 0562      | EID<15:8> |                       |        |        |        | EID<7:0>                                                 |          |              |                            |            |        | xxxx  |                    |        |        |        |               |

| C2RXF9SID  | 0564      | SID<10:3> |                       |        |        |        | SID<2:0> — EXIDE — EID<17:16>                            |          |              |                            |            | xxxx   |       |                    |        |        |        |               |

| C2RXF9EID  | 0566      |           |                       |        | EID<   |        |                                                          |          |              | EID<7:0>                   |            |        |       |                    |        | xxxx   |        |               |

| C2RXF10SID | 0568      |           |                       |        | SID<   | 10:3>  |                                                          |          |              |                            | SID<2:0>   |        | _     | EXIDE              | _      | EID<   | 17:16> | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 5-2: NVMKEY: NON-VOLATILE MEMORY KEY REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 | W-0   |  |  |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|--|

| NVMKEY<7:0> |     |     |     |     |     |     |       |  |  |  |  |

| bit 7       |     |     |     |     |     |     | bit 0 |  |  |  |  |

**Legend:** SO = Settable only bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (Write Only) bits

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0  | R-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|------|-----|-----|-----|-----|-----|-------|

| ALTIVT | DISI | _   | _   | _   | _   | _   | _     |

| bit 15 |      |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| _     | _   | _   | INT4EP | INT3EP | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ALTIVT: Enable Alternate Interrupt Vector Table bit

1 = Use alternate vector table

0 = Use standard (default) vector table

bit 14 DISI Instruction Status bit

1 = DISI instruction is active 0 = DISI instruction is not active

bit 13-5 **Unimplemented:** Read as '0'

bit 4 INT4EP: External Interrupt 4 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 3 INT3EP: External Interrupt 3 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INTOEP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0    | U-0 | R/W-0  | R/W-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|--------|-----|--------|-------|--------|-----|-----|-------|

| _      | _   | DMA5IE | DCIIE | DCIEIE | _   | _   | C2IE  |

| bit 15 |     |        |       |        |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 |

|--------|--------|--------|-------|-------|---------|---------|-------|

| C2RXIE | INT4IE | INT3IE | T9IE  | T8IE  | MI2C2IE | SI2C2IE | T7IE  |

| bit 7  | •      | •      | •     | •     | •       | •       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 DMA5IE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 12 DCIIE: DCI Event Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 11 DCIEIE: DCI Error Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 10-9 **Unimplemented:** Read as '0'

bit 8 **C2IE:** ECAN2 Event Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 7 C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 6 INT4IE: External Interrupt 4 Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 5 INT3IE: External Interrupt 3 Enable bit

1 = Interrupt request enabled 0 = Interrupt request not enabled **T9IE:** Timer9 Interrupt Enable bit

bit 4 **T9IE:** Timer9 Interrupt Enable bit 1 = Interrupt request enabled

0 = Interrupt request not enabled

TRIE. Timer? Interrupt Enable bit

bit 3 T8IE: Timer8 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 2 MI2C2IE: I2C2 Master Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 1 SI2C2IE: I2C2 Slave Events Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 0 T7IE: Timer7 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

#### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|-------|-------|-------------|-------|-----|-------|------------|-------|

| _     |       | DMA5IP<2:0> |       | _   |       | DCIIP<2:0> |       |

| bit 7 |       |             |       |     |       |            | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-4 DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 **DCIIP<2:0>:** DCI Event Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | _   | _   | _   | _   | _   | _   | _     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0                  | R/W-0                                                                | R/W-0 | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|------------------------|------------------------|----------------------------------------------------------------------|-------|------------------------|------------------------|------------------------|

| _     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> IRQSEL3 <sup>(2)</sup> IRQSEL2 <sup>(2)</sup> |       | IRQSEL2 <sup>(2)</sup> | IRQSEL1 <sup>(2)</sup> | IRQSEL0 <sup>(2)</sup> |

| bit 7 |                        |                        |                                                                      |       |                        |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **FORCE**: Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup>

1111111 = DMAIRQ127 selected to be Channel DMAREQ

•

•

0000000 = DMAIRQ0 selected to be Channel DMAREQ

**Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| PAD<15:8> |       |       |       |       |       |       |       |

| bit 15    |       |       |       | bit 8 |       |       |       |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|

|       | PAD<7:0> |       |       |       |       |       |       |  |  |

| bit 7 | bit 7    |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-------|---------------------|

| _      | _   | _   | _   | _   | _   | CNT<  | 9:8> <sup>(2)</sup> |

| bit 15 |     |     |     |     |     |       | bit 8               |

| R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                   |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits(2)

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

#### REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0    | U-0 | U-0 | U-0 | R-1 | R-1  | R-1    | R-1   |

|--------|-----|-----|-----|-----|------|--------|-------|

| _      | _   | _   | _   |     | LSTC | H<3:0> |       |

| bit 15 |     |     |     |     |      |        | bit 8 |

| R-0   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PPST7 | PPST6 | PPST5 | PPST4 | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 LSTCH<3:0>: Last DMA Channel Active bits

1111 = No DMA transfer has occurred since system Reset

1110-1000 = Reserved

0111 = Last data transfer was by DMA Channel 7

0110 = Last data transfer was by DMA Channel 6

0101 = Last data transfer was by DMA Channel 5

0100 = Last data transfer was by DMA Channel 4

0011 = Last data transfer was by DMA Channel 3 0010 = Last data transfer was by DMA Channel 2

0001 = Last data transfer was by DMA Channel 1

0000 = Last data transfer was by DMA Channel 0

bit 7 PPST7: Channel 7 Ping-Pong Mode Status Flag bit

1 = DMA7STB register selected

0 = DMA7STA register selected

bit 6 PPST6: Channel 6 Ping-Pong Mode Status Flag bit

1 = DMA6STB register selected

0 = DMA6STA register selected

bit 5 PPST5: Channel 5 Ping-Pong Mode Status Flag bit

1 = DMA5STB register selected

0 = DMA5STA register selected

bit 4 PPST4: Channel 4 Ping-Pong Mode Status Flag bit

1 = DMA4STB register selected

0 = DMA4STA register selected

bit 3 **PPST3:** Channel 3 Ping-Pong Mode Status Flag bit

1 = DMA3STB register selected

0 = DMA3STA register selected

bit 2 PPST2: Channel 2 Ping-Pong Mode Status Flag bit

1 = DMA2STB register selected

0 = DMA2STA register selected

bit 1 PPST1: Channel 1 Ping-Pong Mode Status Flag bit

1 = DMA1STB register selected

0 = DMA1STA register selected

bit 0 PPST0: Channel 0 Ping-Pong Mode Status Flag bit

1 = DMA0STB register selected

0 = DMA0STA register selected

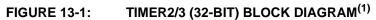

- Note 1: The 32-bit timer control bit, T32, must be set for 32-bit timer/counter operation. All control bits are respective to the T2CON register.

- 2: The ADC event trigger is available only on Timer2/3.

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0                | R/W-0 |

|---------------------|-------|-------|-------|-------------|-------|----------------------|-------|

| SSEN <sup>(3)</sup> | CKP   | MSTEN |       | SPRE<2:0>(2 | PPRE< | <1:0> <sup>(2)</sup> |       |

| bit 7               |       |       |       |             |       |                      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12 **DISSCK:** Disable SCKx pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled, pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 DISSDO: Disable SDOx pin bit

1 = SDOx pin is not used by module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)<sup>(3)</sup>

$1 = \overline{SSx}$  pin used for Slave mode

$0 = \overline{SSx}$  pin not used by module. Pin controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

bit 3 S: Start bit

1 = Indicates that a Start (or Repeated Start) bit has been detected last

0 = Start bit was not detected last

bit 2  $R_W$ : Read/Write Information bit (when operating as  $I^2C$  slave)

1 = Read - indicates data transfer is output from slave0 = Write - indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

bit 1 RBF: Receive Buffer Full Status bit

1 = Receive complete, I2CxRCV is full0 = Receive not complete, I2CxRCV is empty

Hardware set when I2CxRCV is written with received byte. Hardware clear when software

reads I2CxRCV.

bit 0 TBF: Transmit Buffer Full Status bit

1 = Transmit in progress, I2CxTRN is full 0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

#### 22.5 JTAG Interface

dsPIC33FJXXXGPX06A/X08A/X10A devices implement a JTAG interface, which supports boundary scan device testing, as well as in-circuit programming. Detailed information on the interface will be provided in future revisions of the document.

# 22.6 Code Protection and CodeGuard™ Security

The dsPIC33F product families offer the advanced implementation of CodeGuard™ Security. CodeGuard™ Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property in collaborative system designs.

When coupled with software encryption libraries, CodeGuard Security can be used to securely update Flash even when multiple IP are resident on the single chip. The code protection features vary depending on the actual dsPIC33F implemented. The following sections provide an overview of these features.

The code protection features are controlled by the Configuration registers: FBS, FSS and FGS.

Note:

Refer to **Section 23. "CodeGuard™ Security"** (DS70199) in the "dsPIC33F/PIC24H Family Reference Manual" for further information on usage, configuration and operation of CodeGuard™ Security.

### 22.7 In-Circuit Serial Programming

dsPIC33FJXXXGPX06A/X08A/X10A family digital signal controllers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming sequence. This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware, to be programmed. Please refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) document for details about ICSP.

Any one out of three pairs of programming clock/data pins may be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

### 22.8 In-Circuit Debugger

When MPLAB® ICD 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any one out of three pairs of debugging clock/data pins may be used:

- · PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss and the PGEDx/PGECx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

### **TABLE 25-11: ELECTRICAL CHARACTERISTICS: BOR**

| DC CHARACTERISTICS        |      |                                         | Standard Opera<br>(unless otherwise<br>Operating temperating temperating temperating temperating temperature) | se state<br>erature | <b>d)</b><br>-40°C ≤ | TA ≤ +8 | 35°C for   | Industrial<br>Extended |

|---------------------------|------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------|------------|------------------------|

| Param. Symbol Characteris |      | stic <sup>(1)</sup>                     | Min <sup>(1)</sup>                                                                                            | Тур                 | Max <sup>(1)</sup>   | Units   | Conditions |                        |

| BO10                      | VBOR | BOR Event on VDD transition high-to-low |                                                                                                               | 2.40                | _                    | 2.55    | V          | VDD                    |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

#### TABLE 25-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHA | RACTER | ISTICS                               | (unless |                            | ise state | <b>d)</b><br>-40°C : | s: 3.0V to 3.6V<br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |

|--------|--------|--------------------------------------|---------|----------------------------|-----------|----------------------|------------------------------------------------------------------------------|

| Param. | Symbol | Characteristic <sup>(3)</sup>        | Min     | Min Typ <sup>(1)</sup> Max |           | Units                | Conditions                                                                   |

|        |        | Program Flash Memory                 |         |                            |           |                      |                                                                              |

| D130   | EP     | Cell Endurance                       | 10,000  | _                          | _         | E/W                  |                                                                              |

| D131   | VPR    | VDD for Read                         | VMIN    | _                          | 3.6       | V                    | VMIN = Minimum operating voltage                                             |

| D132b  | VPEW   | VDD for Self-Timed Write             | VMIN    | _                          | 3.6       | V                    | VMIN = Minimum operating voltage                                             |

| D134   | TRETD  | Characteristic Retention             | 20      | _                          |           | Year                 | Provided no other specifications are violated                                |

| D135   | IDDP   | Supply Current during<br>Programming | _       | 10                         |           | mA                   |                                                                              |

| D136a  | Trw    | Row Write Time                       | 1.32    | _                          | 1.74      | ms                   | TRW = 11064 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>                     |

| D136b  | Trw    | Row Write Time                       | 1.28    | _                          | 1.79      | ms                   | TRW = 11064 FRC cycles,<br>TA = +150°C, See <b>Note 2</b>                    |

| D137a  | TPE    | Page Erase Time                      | 20.1    | _                          | 26.5      | ms                   | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>                    |

| D137b  | TPE    | Page Erase Time                      | 19.5    | _                          | 27.3      | ms                   | TPE = 168517 FRC cycles,<br>TA = +150°C, See <b>Note 2</b>                   |

| D138a  | Tww    | Word Write Cycle Time                | 42.3    | _                          | 55.9      | μs                   | Tww = 355 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>                       |

| D138b  | Tww    | Word Write Cycle Time                | 41.1    | _                          | 57.6      | μs                   | Tww = 355 FRC cycles,<br>TA = +150°C, See <b>Note 2</b>                      |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

- 3: These parameters are assured by design, but are not characterized or tested in manufacturing.

### **TABLE 25-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**

| IADLL                                                                 | ABLE 25-15. INTERNAL VOLTAGE REGULATOR OF EGIT TOATIONS                                                                                                                    |                 |     |     |     |       |          |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|-------|----------|--|--|--|

| Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |                                                                                                                                                                            |                 |     |     |     |       |          |  |  |  |

| Operation                                                             | Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                 |     |     |     |       |          |  |  |  |

| Param.                                                                | Symbol                                                                                                                                                                     | Characteristics | Min | Тур | Max | Units | Comments |  |  |  |

| _                                                                     | <ul> <li>CEFC External Filter Capacitor Value<sup>(1)</sup></li> <li>4.7</li> <li>10</li> <li>μF Capacitor must be low series resistance (&lt; 5 ohms)</li> </ul>          |                 |     |     |     |       |          |  |  |  |

**Note 1:** Typical VCORE voltage = 2.5V when VDD ≥ VDDMIN.

# 25.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters.

### TABLE 25-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial               |  |  |  |  |

|                    | -40°C ≤ TA ≤ +125°C for Extended                                      |  |  |  |  |

|                    | Operating voltage VDD range as described in Table 25-1.               |  |  |  |  |

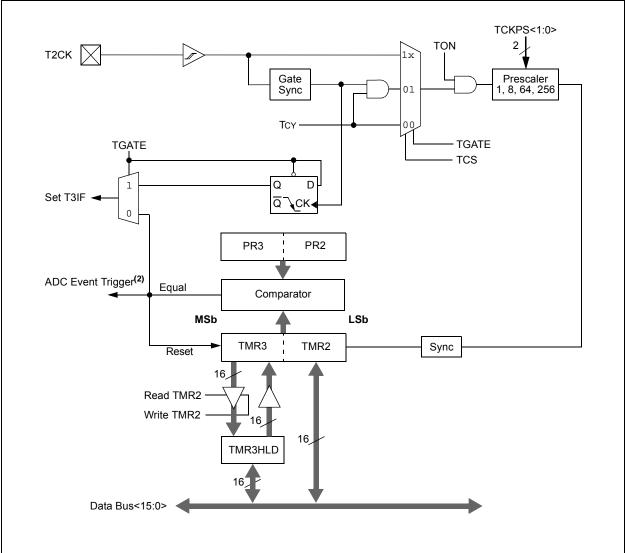

### FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 25-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                   |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | _   | 15  | pF    | In XT and HS modes when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O pins and OSC2 | _   | _   | 50  | pF    | EC mode                                                      |

| DO58         | Св     | SCLx, SDAx            | _   |     | 400 | pF    | In I <sup>2</sup> C™ mode                                    |

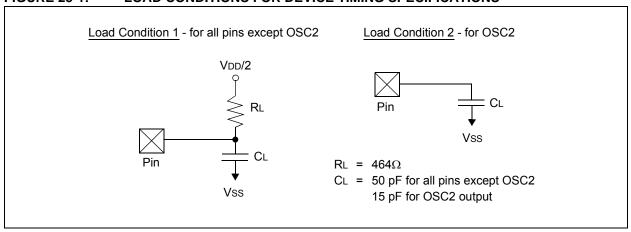

### FIGURE 25-23: CAN MODULE I/O TIMING CHARACTERISTICS

### TABLE 25-40: ECAN™ MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |     |       |                    |  |

|--------------------|--------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                               | Тур | Max | Units | Conditions         |  |

| CA10               | TioF   | Port Output Fall Time                        | _                                                                                                                                                                                                                                 | _   | _   | ns    | See parameter D032 |  |

| CA11               | TioR   | Port Output Rise Time                        | _                                                                                                                                                                                                                                 | _   | _   | ns    | See parameter D031 |  |

| CA20               | Tcwf   | Pulse Width to Trigger<br>CAN Wake-up Filter | 120                                                                                                                                                                                                                               | _   | _   | ns    | _                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

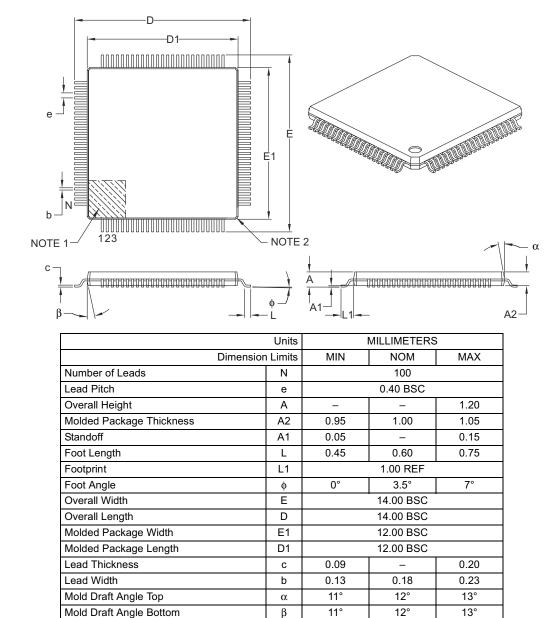

### 100-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

| DMAxPAD                                              | 136      | Instruction Set                                    |     |

|------------------------------------------------------|----------|----------------------------------------------------|-----|

| DMAxREQ                                              |          | Overview                                           | 262 |

| DMAxSTA                                              |          | Summary                                            |     |

| DMAxSTB                                              |          | Instruction-Based Power-Saving Modes               |     |

| DSP Engine                                           |          | ldle                                               |     |

| Multiplier                                           |          | Sleep                                              |     |

| _                                                    |          | Internal RC Oscillator                             |     |

| E                                                    |          | Use with WDT                                       | 257 |

| ECAN Module                                          |          | Internet Address                                   |     |

| CiFMSKSEL2 register                                  | 221      | Interrupt Control and Status Registers             |     |

| ECAN1 Register Map (C1CTRL1.WIN = 0                  |          | IECx                                               |     |

| ECAN1 Register Map (C1CTRL1.WIN = 0)                 | 58       | IFSx                                               |     |

| ECAN1 Register Map (C1CTRL1.WIN = 1)                 | 59       | INTCON1                                            | 93  |

| ECAN2 Register Map (C2CTRL1.WIN = 0 c                | or 1)61  | INTCON2                                            | 93  |

| ECAN2 Register Map (C2CTRL1.WIN = 0)                 | 61, 62   | IPCx                                               | 93  |

| Frame Types                                          | 201      | Interrupt Setup Procedures                         | 133 |

| Modes of Operation                                   | 203      | Initialization                                     | 133 |

| Overview                                             | 201      | Interrupt Disable                                  | 133 |

| ECAN Registers                                       |          | Interrupt Service Routine                          | 133 |

| Filter 15-8 Mask Selection Register                  |          | Trap Service Routine                               | 133 |

| (CiFMSKSEL2)                                         |          | Interrupt Vector Table (IVT)                       | 89  |

| Electrical Characteristics                           |          | Interrupts Coincident with Power Save Instructions | 156 |

| AC                                                   | ,        | J                                                  |     |

| Enhanced CAN Module                                  | 201      | •                                                  |     |

| Equations                                            |          | JTAG Boundary Scan Interface                       | 251 |

| Device Operating Frequency                           |          | M                                                  |     |

| Errata                                               | 16       |                                                    | 0.0 |

| F                                                    |          | Memory Organization                                |     |

| •                                                    | 77       | Microchip Internet Web Site                        | 357 |

| Flash Program Memory                                 |          | Modes of Operation                                 | 202 |

| Control Registers                                    |          | Disable                                            |     |

| Operations                                           |          | Initialization                                     |     |

| Programming Algorithm RTSP Operation                 |          | Listen All Messages                                |     |

| Table Instructions                                   |          | Listen Only                                        |     |

| Flexible Configuration                               |          | Loopback<br>Normal Operation                       |     |

| FSCM                                                 | 201      | Modulo Addressing                                  |     |

| Delay for Crystal and PLL Clock Sources              | 97       | Applicability                                      |     |

| Device Resets                                        |          | Operation Example                                  |     |

| Device resolution                                    |          | Start and End Address                              |     |

| Н                                                    |          | W Address Register Selection                       |     |

| High Temperature Electrical Characteristics          | 321      | MPLAB ASM30 Assembler, Linker, Librarian           |     |

|                                                      |          | MPLAB Integrated Development                       |     |

| 1                                                    |          | Environment Software                               | 267 |

| I/O Ports                                            | 163      | MPLAB PM3 Device Programmer                        |     |

| Parallel I/O (PIO)                                   | 163      | MPLAB REAL ICE In-Circuit Emulator System          |     |

| Write/Read Timing                                    | 164      | MPLINK Object Linker/MPLIB Object Librarian        |     |

| l <sup>2</sup> C                                     |          |                                                    |     |

| Operating Modes                                      | 187      | N                                                  |     |

| Registers                                            | 187      | NVM Module                                         |     |

| I <sup>2</sup> C Module                              |          | Register Map                                       | 66  |

| I2C1 Register Map                                    |          | 0                                                  |     |

| I2C2 Register Map                                    | 53       | 0                                                  |     |

| In-Circuit Debugger                                  |          | Open-Drain Configuration                           |     |

| In-Circuit Emulation                                 |          | Output Compare                                     | 177 |

| In-Circuit Serial Programming (ICSP)                 | 251, 258 | Р                                                  |     |

| Input Capture                                        | 4===     |                                                    | 005 |

| Registers                                            |          | Packaging                                          |     |

| Input Change Notification Module                     |          | Details                                            |     |

| Instruction Addressing Modes                         |          | Marking                                            |     |

| File Register Instructions                           |          | Peripheral Module Disable (PMD)                    |     |

| Fundamental Modes Supported                          |          | Pinout I/O Descriptions (table)                    | 21  |

| MAC Instructions                                     |          | PMD Module Register Map                            | 66  |

| MCU Instructions                                     |          | POR and Long Oscillator Start-up Times             |     |

| Move and Accumulator Instructions Other Instructions |          | Tork and Long Osomator Start-up Times              | 01  |

|                                                      |          |                                                    |     |