Welcome to E-XFL.COM

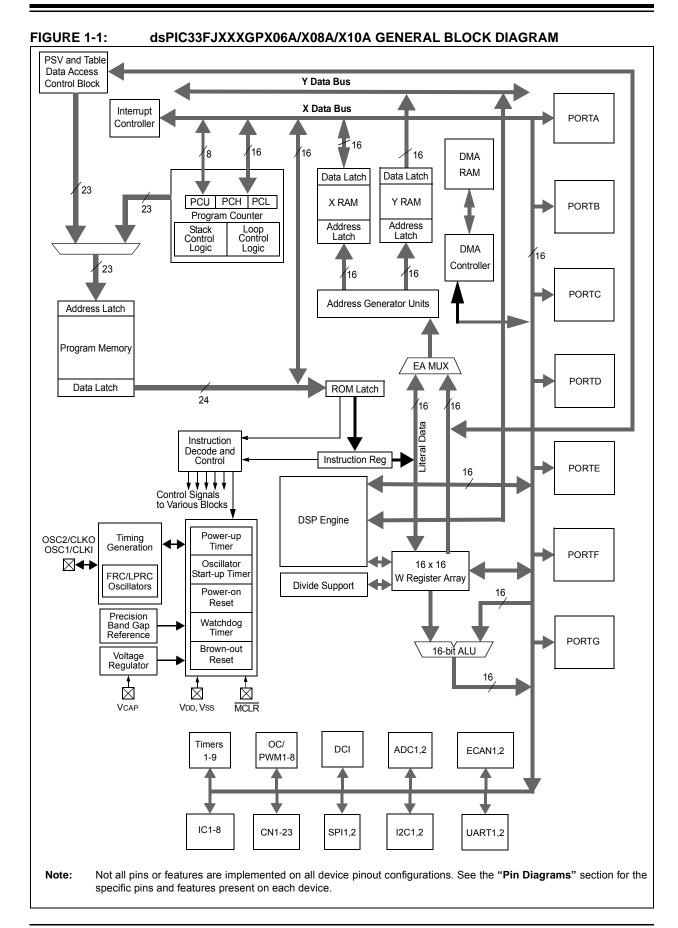

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 53                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 18x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | 64-VQFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp506at-i-mr |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| bit 8  |    | DC: MCU ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | <ul> <li>1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data)<br/>of the result occurred</li> </ul>                                                                                                                                                                                                                                                                             |

|        |    | <ul> <li>0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                |

| bit 7- | 5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|        |    | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4  |    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |    | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3  |    | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |    | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2  |    | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |    | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                |

| bit 1  |    | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |    | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                               |

| bit 0  |    | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |    | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

| Note   | 1: | This bit may be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                  |

|        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

#### REGISTER 7-29: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

| U-0           | R/W-1              | R/W-0                | R/W-0           | U-0                                     | U-0             | U-0       | U-0   |  |  |

|---------------|--------------------|----------------------|-----------------|-----------------------------------------|-----------------|-----------|-------|--|--|

| —             |                    | DCIEIP<2:0>          |                 | _                                       |                 | —         | —     |  |  |

| bit 15        |                    |                      |                 |                                         |                 |           | bit 8 |  |  |

|               |                    |                      |                 |                                         |                 |           |       |  |  |

| U-0           | U-0                | U-0                  | U-0             | U-0                                     | R/W-1           | R/W-0     | R/W-0 |  |  |

| _             | _                  | —                    | _               | —                                       |                 | C2IP<2:0> |       |  |  |

| bit 7         |                    |                      |                 |                                         |                 |           | bit C |  |  |

|               |                    |                      |                 |                                         |                 |           |       |  |  |

| Legend:       |                    |                      |                 |                                         |                 |           |       |  |  |

| R = Readabl   | le bit             | W = Writable b       | oit             | U = Unimpler                            | nented bit, rea | d as '0'  |       |  |  |

| -n = Value at | t POR              | '1' = Bit is set     |                 | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |  |

|               |                    |                      |                 |                                         |                 |           |       |  |  |

| bit 15        | Unimplemer         | nted: Read as 'o     | )'              |                                         |                 |           |       |  |  |

| bit 14-12     | DCIEIP<2:0>        | . DCI Error Inte     | rrupt Priority  | bits                                    |                 |           |       |  |  |

|               | 111 = Interru      | pt is priority 7 (h  | nighest priorit | ty interrupt)                           |                 |           |       |  |  |

|               | •                  |                      |                 |                                         |                 |           |       |  |  |

|               | •                  |                      |                 |                                         |                 |           |       |  |  |

|               | 001 = Interru      | pt is priority 1     |                 |                                         |                 |           |       |  |  |

|               |                    | pt source is disa    | abled           |                                         |                 |           |       |  |  |

| bit 11-3      | Unimplemer         | ted: Read as '0      | )'              |                                         |                 |           |       |  |  |

| bit 2-0       | C2IP<2:0>: [       | ECAN2 Event In       | terrupt Priori  | tv bits                                 |                 |           |       |  |  |

|               |                    | ipt is priority 7 (h | •               |                                         |                 |           |       |  |  |

|               | •                  | , , ,                | 0               |                                         |                 |           |       |  |  |

|               | •                  |                      |                 |                                         |                 |           |       |  |  |

|               | •<br>001 - Interry | unt in priority 1    |                 |                                         |                 |           |       |  |  |

|               |                    | pt is priority 1     | ahlad           |                                         |                 |           |       |  |  |

000 = Interrupt source is disabled

| R/W-0        | R/W-0                       | R/W-1                              | R/W-1        | R/W-0                | R/W-0          | R/W-0               | R/W-0      |  |  |

|--------------|-----------------------------|------------------------------------|--------------|----------------------|----------------|---------------------|------------|--|--|

| ROI          |                             | DOZE<2:0>                          |              | DOZEN <sup>(1)</sup> |                | FRCDIV<2:0>         |            |  |  |

| bit 15       | ·                           |                                    |              |                      |                |                     | bit        |  |  |

|              |                             |                                    |              |                      |                |                     |            |  |  |

| R/W-0        | R/W-1                       | U-0                                | R/W-0        | R/W-0                | R/W-0          | R/W-0               | R/W-0      |  |  |

|              | OST<1:0>                    | _                                  |              | PLLPRE<4:0>          |                |                     |            |  |  |

| bit 7        |                             |                                    |              |                      |                |                     | bit (      |  |  |

| Legend:      |                             | v = Value set                      | from Configu | ration bits on P     | OR             |                     |            |  |  |

| R = Readab   | le bit                      | W = Writable                       | -            | U = Unimplen         |                | id as '0'           |            |  |  |

| -n = Value a | t POR                       | '1' = Bit is set                   |              | '0' = Bit is clea    |                | x = Bit is unkn     | own        |  |  |

|              |                             |                                    |              |                      |                |                     |            |  |  |

| bit 15       | ROI: Recove                 | r on Interrupt bi                  | t            |                      |                |                     |            |  |  |

|              |                             |                                    |              |                      | r clock/periph | eral clock ratio is | set to 1:1 |  |  |

| hit 11 10    | •                           | s have no effect<br>Processor Cloc |              |                      |                |                     |            |  |  |

| bit 14-12    | 111 = Fcy/12                |                                    | Reduction    | Select bits          |                |                     |            |  |  |

|              | 110 = Fcy/64                |                                    |              |                      |                |                     |            |  |  |

|              | 101 = Fcy/32                |                                    |              |                      |                |                     |            |  |  |

|              | 100 = Fcy/16<br>011 = Fcy/8 |                                    |              |                      |                |                     |            |  |  |

|              | 010 = FCY/4                 | (deladit)                          |              |                      |                |                     |            |  |  |

|              | 001 = Fcy/2                 |                                    |              |                      |                |                     |            |  |  |

|              | 000 = Fcy/1                 |                                    | (1)          |                      |                |                     |            |  |  |

| bit 11       |                             | ZE Mode Enabl                      |              | atwaan the neri      | nharal alaaka  | and the process     | ar ala aka |  |  |

|              |                             | or clock/periphe                   |              |                      | prierai ciocks | and the processo    | DI CIUCKS  |  |  |

| bit 10-8     |                             |                                    |              | or Postscaler bits   | 3              |                     |            |  |  |

|              | 111 <b>= FRC d</b>          |                                    |              |                      |                |                     |            |  |  |

|              | 110 = FRC d                 |                                    |              |                      |                |                     |            |  |  |

|              | 101 = FRC d<br>100 = FRC d  |                                    |              |                      |                |                     |            |  |  |

|              | 011 = FRC d                 |                                    |              |                      |                |                     |            |  |  |

|              | 010 = FRC d                 |                                    |              |                      |                |                     |            |  |  |

|              | 001 = FRC d                 | ivide by 2<br>ivide by 1 (defa     | ult)         |                      |                |                     |            |  |  |

| bit 7-6      |                             |                                    | -            | er Select bits (al   | so denoted as  | s 'N2', PLL postso  | aler)      |  |  |

|              | 11 = Output/8               |                                    |              |                      |                | , 112, 1 22 poolo   |            |  |  |

|              | 10 = Reserve                | ed                                 |              |                      |                |                     |            |  |  |

|              | 01 = Output/4               | · /                                |              |                      |                |                     |            |  |  |

| bit 5        | 00 = Output/2               | <b>ted:</b> Read as '              | ۰ <b>،</b>   |                      |                |                     |            |  |  |

| bit 4-0      | -                           |                                    |              | ıt Divider bits (al  | so denoted a   | s 'N1', PLL presc   | alor)      |  |  |

|              | 11111 = Inpu                |                                    |              | מושועכו שונס (מ      |                | s in , i LL pieso   |            |  |  |

|              | •                           |                                    |              |                      |                |                     |            |  |  |

|              | •                           |                                    |              |                      |                |                     |            |  |  |

|              | •                           |                                    |              |                      |                |                     |            |  |  |

|              | 00001 = Inpu                |                                    |              |                      |                |                     |            |  |  |

|              | 00000 <b>= Inp</b> i        |                                    |              |                      |                |                     |            |  |  |

#### Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

2: This is register is reset only on a Power-on Reset (POR).

### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SSx}$ .

| Note: | This   | insures    | that  | the        | first | fra | ame |

|-------|--------|------------|-------|------------|-------|-----|-----|

|       | transr | nission a  | after | initializa | ation | is  | not |

|       | shifte | d or corru | pted. |            |       |     |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

### 16.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en546064              |

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                            | R/W-x                                                                   | U-0                                                                                 | U-0                                  | U-0               | R/W-x            | R/W-x           | R/W-x |

|--------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|-------------------|------------------|-----------------|-------|

|                                | WAKFIL                                                                  |                                                                                     | _                                    |                   |                  | SEG2PH<2:0>     |       |

| bit 15                         |                                                                         | ·                                                                                   |                                      | · · · ·           |                  |                 | bit 8 |

| R/W-x                          | R/W-x                                                                   | R/W-x                                                                               | R/W-x                                | R/W-x             | R/W-x            | R/W-x           | R/W-x |

| SEG2PHTS                       | SAM                                                                     |                                                                                     | SEG1PH<2:0>                          | >                 |                  | PRSEG<2:0>      |       |

| bit 7                          |                                                                         |                                                                                     |                                      |                   |                  |                 | bit ( |

| Legend:                        |                                                                         |                                                                                     |                                      |                   |                  |                 |       |

| R = Readable                   | bit                                                                     | W = Writable                                                                        | bit                                  | U = Unimplen      | nented bit, read | as '0'          |       |

| -n = Value at P                | OR                                                                      | '1' = Bit is set                                                                    | :                                    | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 13-11<br>bit 10-8<br>bit 7 | 0 = CAN bus<br>Unimplemen<br>SEG2PH<2:(<br>111 = Length<br>000 = Length |                                                                                     | used for wake<br>o'<br>fer Segment 2 | bits              |                  |                 |       |

| bit 6                          | SAM: Samp<br>1 = Bus line i                                             | ogrammable<br>n of SEG1PH b<br>le of the CAN b<br>is sampled thre<br>is sampled onc | ous Line bit<br>e times at the       | sample point      | Time (IPT), wh   | ichever is grea | ter   |

| bit 5-3                        |                                                                         | <b>0&gt;:</b> Phase Buff<br>n is 8 x TQ                                             |                                      | •                 |                  |                 |       |

| bit 2-0                        | PRSEG<2:0:<br>111 = Length<br>000 = Length                              |                                                                                     | Time Segmer                          | nt bits           |                  |                 |       |

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------------|----------------------------------|---------------------------------------|------------------|------------------|-----------------|--------|

| F15M          | SK<1:0>                              | F14MS                            | <<1:0>                                | F13M             | SK<1:0>          | F12MSI          | K<1:0> |

| bit 15        |                                      | ł                                |                                       |                  |                  | ł               | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| F11M          | SK<1:0>                              | F10MS                            | <<1:0>                                | F9MS             | SK<1:0>          | F8MSK           | (<1:0> |

| bit 7         |                                      |                                  |                                       |                  |                  |                 | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| Legend:       |                                      |                                  |                                       |                  |                  |                 |        |

| R = Readable  |                                      | W = Writable I                   | bit                                   | -                | mented bit, read |                 |        |

| -n = Value at | POR                                  | '1' = Bit is set                 |                                       | '0' = Bit is cle | eared            | x = Bit is unkn | own    |

|               |                                      |                                  |                                       | ,                |                  |                 |        |

| bit 15-14     |                                      | >: Mask Source                   | e for Filter 15                       | DIT              |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 13-12     | F14MSK<1:0                           | >: Mask Source                   | e for Filter 14                       | bit              |                  |                 |        |

|               | 11 = Reserve                         | -,                               |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 11-10     | -                                    | >: Mask Source                   |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | -                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 9-8       | <b>F12MSK&lt;1:0</b><br>11 = Reserve | >: Mask Source                   | e for Filter 12                       | bit              |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | •                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 7-6       |                                      | >: Mask Source                   | e for Filter 11 b                     | oit              |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 5-4       |                                      | Source                           |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               | •                                    | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 3-2       |                                      | : Mask Source                    | for Filter 9 bit                      |                  |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | istore contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 1-0       |                                      | : Mask Source                    |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         | ed; do not use                   |                                       |                  |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      |                                  | · · · · · · · · · · · · · · · · · · · |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| R/W-x                             | R/W-x                                                                                                                                | R/W-x                                                        | R/W-x          | R/W-x                              | R/W-x              | R/W-x              | R/W-x            |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------|------------------------------------|--------------------|--------------------|------------------|--|--|

|                                   |                                                                                                                                      |                                                              | SID            | <10:3>                             |                    |                    |                  |  |  |

| bit 15                            |                                                                                                                                      |                                                              |                |                                    |                    |                    | bit 8            |  |  |

|                                   |                                                                                                                                      |                                                              |                |                                    |                    |                    |                  |  |  |

| R/W-x                             | R/W-x                                                                                                                                | R/W-x                                                        | U-0            | R/W-x                              | U-0                | R/W-x              | R/W-x            |  |  |

|                                   | SID<2:0>                                                                                                                             |                                                              |                | MIDE                               |                    | EID<1              | 7:16>            |  |  |

| bit 7                             |                                                                                                                                      |                                                              |                |                                    |                    |                    | bit C            |  |  |

| Legend:                           |                                                                                                                                      |                                                              |                |                                    |                    |                    |                  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                      |                                                              |                | U = Unimplemented bit, read as '0' |                    |                    |                  |  |  |

| -n = Value at                     | POR                                                                                                                                  | '1' = Bit is set                                             |                | '0' = Bit is cleared               |                    | x = Bit is unknown |                  |  |  |

|                                   |                                                                                                                                      |                                                              |                |                                    |                    |                    |                  |  |  |

| bit 15-5                          | SID<10:0>:                                                                                                                           | Standard Identif                                             | ier bits       |                                    |                    |                    |                  |  |  |

|                                   | 1 = Include                                                                                                                          | bit SIDx in filter c                                         | omparison      |                                    |                    |                    |                  |  |  |

|                                   | 0 = Bit SIDx                                                                                                                         | is don't care in fi                                          | ilter comparis | son                                |                    |                    |                  |  |  |

| bit 4                             | Unimpleme                                                                                                                            | nted: Read as '0                                             | )'             |                                    |                    |                    |                  |  |  |

| bit 3                             | MIDE: Iden                                                                                                                           | tifier Receive Mo                                            | de bit         |                                    |                    |                    |                  |  |  |

|                                   | 0 = Match e                                                                                                                          | only message typ<br>either standard or<br>(Filter SID) = (Me | extended a     | ddress messag                      | e if filters match | י.<br>ו            | DE bit in filter |  |  |

| bit 2                             | Unimpleme                                                                                                                            | nted: Read as 'o                                             | )'             |                                    |                    |                    |                  |  |  |

| bit 1-0                           | EID<17:16>                                                                                                                           | : Extended Ident                                             | ifier bits     |                                    |                    |                    |                  |  |  |

|                                   | EID<17:16>: Extended Identifier bits<br>1 = Include bit EIDx in filter comparison<br>0 = Bit EIDx is don't care in filter comparison |                                                              |                |                                    |                    |                    |                  |  |  |

### REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | EID   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | EID   | )<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable b  | oit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

#### REGISTER 21-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | U-0        | U-0   |

|--------|-----|-----|-----|-----|-------|------------|-------|

| —      | —   | —   | —   | —   | —     | —          |       |

| bit 15 |     |     |     |     |       |            | bit 8 |

|        |     |     |     |     |       |            |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0      | R/W-0 |

| _      | _   | —   | —   | _   |       | DMABL<2:0> |       |

bit 0

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 7

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

| TABLE 25-11: | ELECTRICAL CHARACTERISTICS: BOR |

|--------------|---------------------------------|

|--------------|---------------------------------|

| DC CHARACTERISTICS (unless otherw |           | ating Conditions: 3.0V to 3.6V<br>ise stated)<br>erature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                  |                    |        |                    |       |            |

|-----------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------|--------------------|-------|------------|

| Param.                            | Symbol    | Characteristic <sup>(1)</sup>                                                                                                                                          |                  | Min <sup>(1)</sup> | Тур    | Max <sup>(1)</sup> | Units | Conditions |

| BO10                              | VBOR      | BOR Event on VDD transition high-to-low                                                                                                                                |                  | 2.40               | _      | 2.55               | V     | Vdd        |

| Noto 1                            | Doromotor | aro for dosign quidanco                                                                                                                                                | only and are not | tostod in          | monufo | oturina            |       |            |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

#### TABLE 25-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHA | RACTER | ISTICS                               | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |      |       | ≤ TA ≤ +85°C for Industrial                                |

|--------|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------------------------------------------------------------|

| Param. | Symbol | Characteristic <sup>(3)</sup>        | Min                                                                                                                                                                                                  | Typ <sup>(1)</sup> | Max  | Units | Conditions                                                 |

|        |        | Program Flash Memory                 |                                                                                                                                                                                                      |                    |      |       |                                                            |

| D130   | Eр     | Cell Endurance                       | 10,000                                                                                                                                                                                               | —                  | _    | E/W   |                                                            |

| D131   | Vpr    | VDD for Read                         | VMIN                                                                                                                                                                                                 | —                  | 3.6  | V     | Vмın = Minimum operating<br>voltage                        |

| D132b  | VPEW   | VDD for Self-Timed Write             | VMIN                                                                                                                                                                                                 | —                  | 3.6  | V     | Vмın = Minimum operating<br>voltage                        |

| D134   | TRETD  | Characteristic Retention             | 20                                                                                                                                                                                                   | —                  | —    | Year  | Provided no other specifications are violated              |

| D135   | IDDP   | Supply Current during<br>Programming | —                                                                                                                                                                                                    | 10                 | —    | mA    |                                                            |

| D136a  | Trw    | Row Write Time                       | 1.32                                                                                                                                                                                                 | —                  | 1.74 | ms    | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |

| D136b  | Trw    | Row Write Time                       | 1.28                                                                                                                                                                                                 | —                  | 1.79 | ms    | Trw = 11064 FRC cycles,<br>Ta = +150°C, See <b>Note 2</b>  |

| D137a  | TPE    | Page Erase Time                      | 20.1                                                                                                                                                                                                 | —                  | 26.5 | ms    | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |

| D137b  | TPE    | Page Erase Time                      | 19.5                                                                                                                                                                                                 | —                  | 27.3 | ms    | TPE = 168517 FRC cycles,<br>TA = +150°C, See <b>Note 2</b> |

| D138a  | Tww    | Word Write Cycle Time                | 42.3                                                                                                                                                                                                 | —                  | 55.9 | μs    | Tww = 355 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>     |

| D138b  | Tww    | Word Write Cycle Time                | 41.1                                                                                                                                                                                                 | —                  | 57.6 | μs    | Tww = 355 FRC cycles,<br>Ta = +150°C, See <b>Note 2</b>    |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b '011111 (for Min), TUN<5:0> = b '100000 (for Max). This parameter depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

3: These parameters are assured by design, but are not characterized or tested in manufacturing.

#### TABLE 25-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |        |                                                |     |     |     |       |                                                    |  |

|--------------------------------------------------------------------------|--------|------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------|--|

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |        |                                                |     |     |     |       |                                                    |  |

| Param.                                                                   | Symbol | Characteristics                                | Min | Тур | Max | Units | Comments                                           |  |

| _                                                                        | Cefc   | External Filter Capacitor Value <sup>(1)</sup> | 4.7 | 10  | —   | μF    | Capacitor must be low series resistance (< 5 ohms) |  |

**Note 1:** Typical VCORE voltage = 2.5V when VDD  $\ge$  VDDMIN.

| TABLE 25-38: | DCI MODULE | MULTI-CHANNEL. | I <sup>2</sup> S MODES | TIMING REQUIREMENTS |

|--------------|------------|----------------|------------------------|---------------------|

|              | DOLINODOLL |                |                        |                     |

|              |        |                                                                                   |            |                    | <b>ated)</b><br>re -40°C : | ≤ Ta ≤ +8 | <b>3.6V</b><br>35°C for Industrial<br>25°C for Extended |

|--------------|--------|-----------------------------------------------------------------------------------|------------|--------------------|----------------------------|-----------|---------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                                     | Min        | Тур <sup>(2)</sup> | Max                        | Units     | Conditions                                              |

| CS10         | TCSCKL | CSCK Input Low Time<br>(CSCK pin is an input)                                     | Tcy/2 + 20 | _                  |                            | ns        | —                                                       |

|              |        | CSCK Output Low Time <sup>(3)</sup><br>(CSCK pin is an output)                    | 30         |                    |                            | ns        | _                                                       |

| CS11         | Тсѕскн | CSCK Input High Time<br>(CSCK pin is an input)                                    | Tcy/2 + 20 |                    |                            | ns        | —                                                       |

|              |        | CSCK Output High Time <sup>(3)</sup><br>(CSCK pin is an output)                   | 30         | _                  | _                          | ns        | —                                                       |

| CS20         | TCSCKF | CSCK Output Fall Time <sup>(4)</sup><br>(CSCK pin is an output)                   | —          | 10                 | 25                         | ns        | —                                                       |

| CS21         | TCSCKR | CSCK Output Rise Time <sup>(4)</sup><br>(CSCK pin is an output)                   | —          | 10                 | 25                         | ns        | —                                                       |

| CS30         | TCSDOF | CSDO Data Output Fall Time <sup>(4)</sup>                                         | —          | 10                 | 25                         | ns        | —                                                       |

| CS31         | TCSDOR | CSDO Data Output Rise Time <sup>(4)</sup>                                         | —          | 10                 | 25                         | ns        | —                                                       |

| CS35         | TDV    | Clock Edge to CSDO Data Valid                                                     | —          | —                  | 10                         | ns        | —                                                       |

| CS36         | TDIV   | Clock Edge to CSDO Tri-Stated                                                     | 10         | _                  | 20                         | ns        | —                                                       |

| CS40         | TCSDI  | Setup Time of CSDI Data Input<br>to<br>CSCK Edge (CSCK pin is input<br>or output) | 20         |                    | _                          | ns        | _                                                       |

| CS41         | THCSDI | Hold Time of CSDI Data Input to<br>CSCK Edge (CSCK pin is input<br>or output)     | 20         |                    | _                          | ns        | _                                                       |

| CS50         | TCOFSF | COFS Fall Time<br>(COFS pin is output)                                            | _          | 10                 | 25                         | ns        | Note 1                                                  |

| CS51         | TCOFSR | COFS Rise Time<br>(COFS pin is output)                                            | _          | 10                 | 25                         | ns        | Note 1                                                  |

| CS55         | TSCOFS | Setup Time of COFS Data Input<br>to CSCK Edge (COFS pin is<br>input)              | 20         | _                  | _                          | ns        | —                                                       |

| CS56         | THCOFS | Hold Time of COFS Data Input to CSCK Edge (COFS pin is input)                     | 20         |                    | —                          | ns        | —                                                       |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for CSCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all DCI pins.

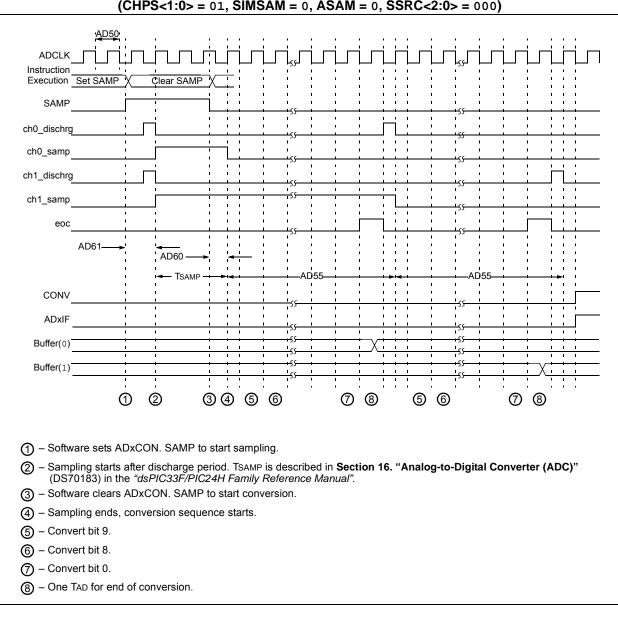

#### FIGURE 25-25: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)

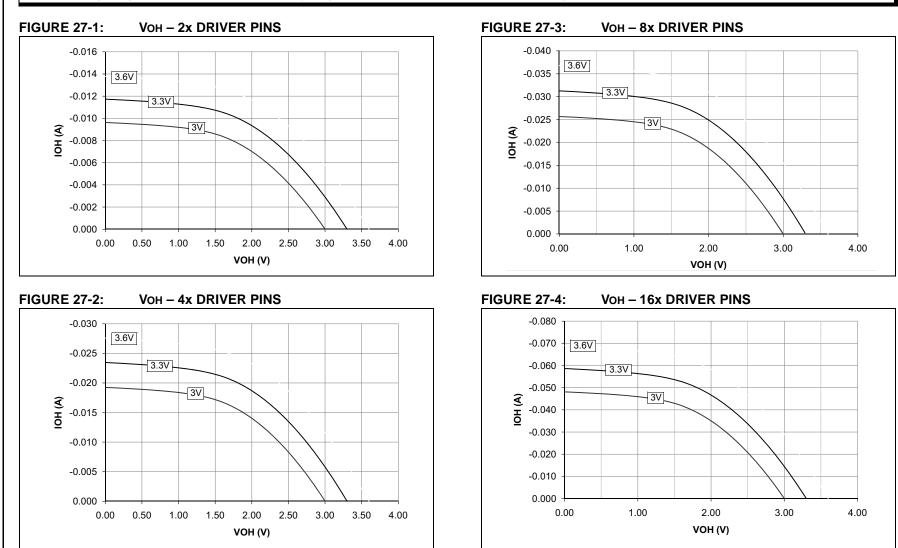

### 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

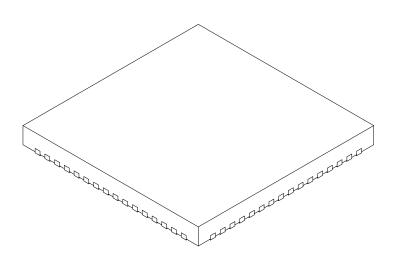

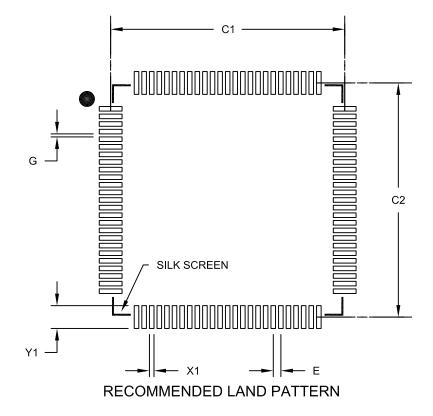

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | Ν        | S        |      |

|------------------------|----------|----------|----------|------|

| Dimensio               | n Limits | MIN      | NOM      | MAX  |

| Number of Pins         | Ν        |          | 64       |      |

| Pitch                  | е        |          | 0.50 BSC |      |

| Overall Height         | Α        | 0.80     | 0.90     | 1.00 |

| Standoff               | A1       | 0.00     | 0.02     | 0.05 |

| Contact Thickness      | A3       | 0.20 REF |          |      |

| Overall Width          | Е        | 9.00 BSC |          |      |

| Exposed Pad Width      | E2       | 5.30     | 5.40     | 5.50 |

| Overall Length         | D        | 9.00 BSC |          |      |

| Exposed Pad Length     | D2       | 5.30     | 5.40     | 5.50 |

| Contact Width          | b        | 0.20     | 0.25     | 0.30 |

| Contact Length         | L        | 0.30     | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K        | 0.20     | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

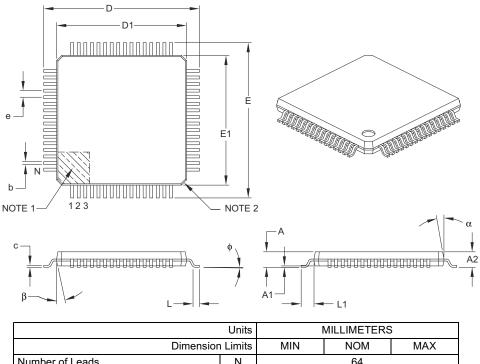

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Dimension Limits MIN NC |           |          | MAX  |

|--------------------------|-------------------------|-----------|----------|------|

| Number of Leads          | N                       | 64        |          |      |

| Lead Pitch               | е                       |           | 0.50 BSC |      |

| Overall Height           | А                       | _         | -        | 1.20 |

| Molded Package Thickness | A2                      | 0.95      | 1.00     | 1.05 |

| Standoff                 | A1                      | 0.05      | -        | 0.15 |

| Foot Length              | L                       | 0.45      | 0.60     | 0.75 |

| Footprint                | L1                      | 1.00 REF  |          |      |

| Foot Angle               | φ                       | 0°        | 3.5°     | 7°   |

| Overall Width            | E                       | 12.00 BSC |          |      |

| Overall Length           | D                       | 12.00 BSC |          |      |

| Molded Package Width     | E1                      | 10.00 BSC |          |      |

| Molded Package Length    | D1                      | 10.00 BSC |          |      |

| Lead Thickness           | С                       | 0.09      | -        | 0.20 |

| Lead Width               | b                       | 0.17      | 0.22     | 0.27 |

| Mold Draft Angle Top     | α                       | 11°       | 12°      | 13°  |

| Mold Draft Angle Bottom  | β                       | 11°       | 12°      | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

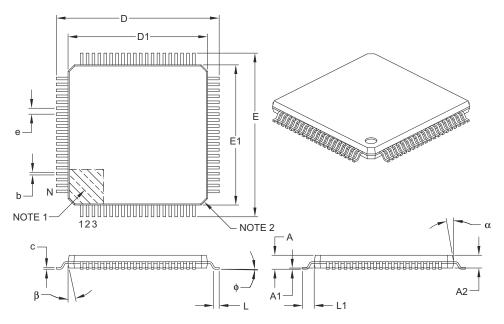

### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |

|--------------------------|------------------|-------------|----------|------|

| ]                        | Dimension Limits |             |          | MAX  |

| Number of Leads          | N                |             | 80       |      |

| Lead Pitch               | е                |             | 0.50 BSC |      |

| Overall Height           | А                | -           | -        | 1.20 |

| Molded Package Thickness | A2               | 0.95        | 1.00     | 1.05 |

| Standoff                 | A1               | 0.05        | -        | 0.15 |

| Foot Length              | L                | 0.45        | 0.60     | 0.75 |

| Footprint                | L1               | 1.00 REF    |          |      |

| Foot Angle               | ¢                | 0° 3.5° 7°  |          |      |

| Overall Width            | E                | 14.00 BSC   |          |      |

| Overall Length           | D                | 14.00 BSC   |          |      |

| Molded Package Width     | E1               | 12.00 BSC   |          |      |

| Molded Package Length    | D1               | 12.00 BSC   |          |      |

| Lead Thickness           | С                | 0.09        | -        | 0.20 |

| Lead Width               | b                | 0.17        | 0.22     | 0.27 |

| Mold Draft Angle Top     | α                | 11°         | 12°      | 13°  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°      | 13°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

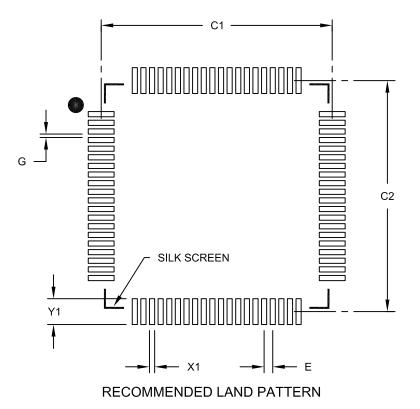

80-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| [                        |                  |          |       | -    |

|--------------------------|------------------|----------|-------|------|

|                          | Units            |          |       | S    |

| Dimensi                  | Dimension Limits |          | NOM   | MAX  |

| Contact Pitch            | E                | 0.50 BSC |       |      |

| Contact Pad Spacing      | C1               |          | 13.40 |      |

| Contact Pad Spacing      | C2               |          | 13.40 |      |

| Contact Pad Width (X80)  | X1               |          |       | 0.30 |

| Contact Pad Length (X80) | Y1               |          |       | 1.50 |

| Distance Between Pads    | G                | 0.20     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B

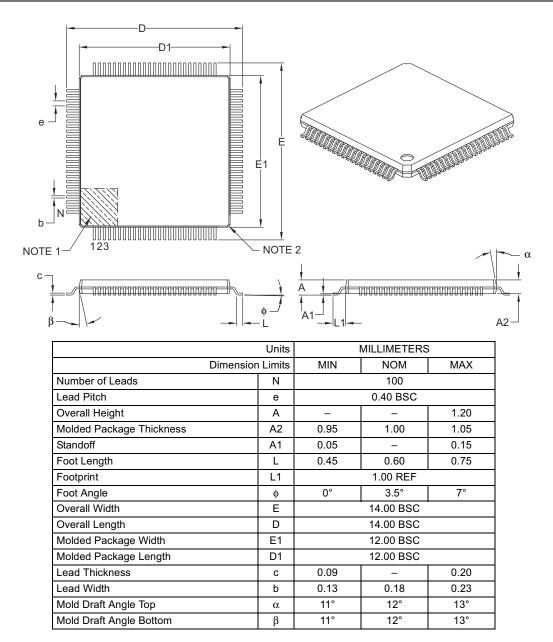

### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units            | Ν    | S        |      |

|---------------------------|------------------|------|----------|------|

| Dimensior                 | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch             | E                |      | 0.50 BSC |      |

| Contact Pad Spacing       | C1               |      | 15.40    |      |

| Contact Pad Spacing       | C2               |      | 15.40    |      |

| Contact Pad Width (X100)  | X1               |      |          | 0.30 |

| Contact Pad Length (X100) | Y1               |      |          | 1.50 |

| Distance Between Pads     | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

NOTES: