Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

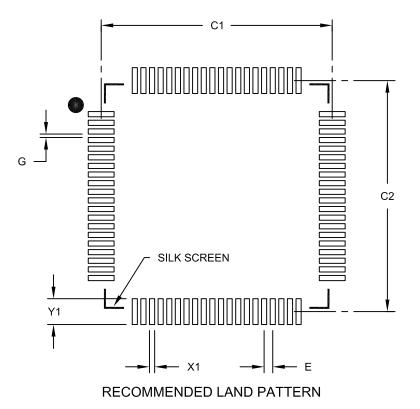

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp510a-e-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

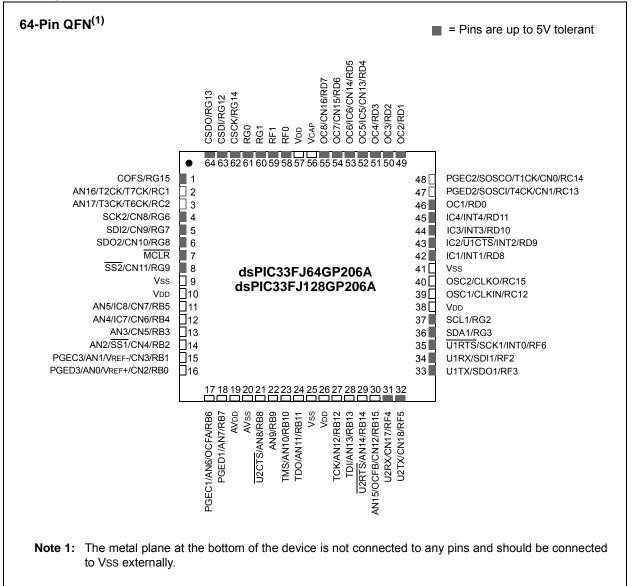

### Pin Diagrams

### 3.6.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly, For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

### 3.6.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and between bit positions 0 to 16 for left shifts.

### TABLE 4-17: DMA REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|---------------|

| DMA0CON   | 0380 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        |       | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA0REQ   | 0382 | FORCE  | _      | _      | _      | _      | _      | _     | _     | _        |       |       |        | RQSEL<6:0 | >     | -     | -     | 0000          |

| DMA0STA   | 0384 | I      |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0STB   | 0386 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0PAD   | 0388 |        |        |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0CNT   | 038A | _      | —      | _      | —      | _      | _      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA1CON   | 038C | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | —     | _        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA1REQ   | 038E | FORCE  | _      | _      | —      | _      | _      | _     | _     | _        |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA1STA   | 0390 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1STB   | 0392 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1PAD   | 0394 |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1CNT   | 0396 | —      | —      |        | —      | —      | _      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA2CON   | 0398 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | _     | —     |          | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA2REQ   | 039A | FORCE  | —      |        |        | _      | —      | _     | —     |          |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA2STA   | 039C |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2STB   | 039E |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2PAD   | 03A0 |        |        |        | -      |        |        | -     | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2CNT   | 03A2 | —      | _      | —      | —      | _      | _      |       | -     |          |       | CN    | <9:0>  | _         | -     | -     |       | 0000          |

| DMA3CON   | 03A4 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | _        | —     | AMOD  | E<1:0> | -         | —     | MODE  | <1:0> | 0000          |

| DMA3REQ   | 03A6 | FORCE  | _      | _      | —      | —      | _      | —     | —     | _        |       |       |        | RQSEL<6:0 | >     |       |       | 0000          |

| DMA3STA   | 03A8 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3STB   | 03AA |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3PAD   | 03AC |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3CNT   | 03AE | —      | —      | —      | —      | —      | —      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA4CON   | 03B0 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA4REQ   | 03B2 | FORCE  | —      | —      | —      | —      | —      | —     | —     | —        |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA4STA   | 03B4 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4STB   | 03B6 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4PAD   | 03B8 |        |        |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4CNT   | 03BA | —      | —      | —      | —      | —      | —      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA5CON   | 03BC | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | _        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA5REQ   | 03BE | FORCE  | —      | —      | —      | —      |        | —     | —     | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000          |

| DMA5STA   | 03C0 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA5STB   | 03C2 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA5PAD   | 03C4 |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

© 2009-2012 Microchip Technology Inc.

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70593D-page 56

| File Name  | Addr             | Bit 15                                | Bit 14                          | Bit 13    | Bit 12 | Bit 11   | Bit 10 | Bit 9                         | Bit 8       | Bit 7                       | Bit 6    | Bit 5  | Bit 4           | Bit 3      | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|------------|------------------|---------------------------------------|---------------------------------|-----------|--------|----------|--------|-------------------------------|-------------|-----------------------------|----------|--------|-----------------|------------|--------|-------|--------|---------------|

|            | 0400-<br>041E    |                                       |                                 |           |        |          |        |                               | See definit | ion when V                  | /IN = x  |        |                 |            |        |       |        |               |

| C1BUFPNT1  | 0420             |                                       | F3BP                            | <3:0>     |        |          | F2BF   | ><3:0>                        |             |                             | F1BP     | <3:0>  |                 |            | F0BP   | <3:0> |        | 0000          |

| C1BUFPNT2  | 0422             |                                       | F7BP                            | <3:0>     |        |          | F6BF   | ><3:0>                        |             |                             | F5BP     | <3:0>  |                 |            | F4BP   | <3:0> |        | 0000          |

| C1BUFPNT3  | 0424             |                                       | F11BF                           | ><3:0>    |        |          | F10B   | P<3:0>                        |             |                             | F9BP     | <3:0>  |                 | F8BP<3:0>  |        |       |        | 0000          |

| C1BUFPNT4  | 0426             |                                       | F15BF                           | P<3:0>    |        |          | F14B   | P<3:0>                        |             |                             | F13B     | P<3:0> |                 | F12BP<3:0> |        |       |        | 0000          |

| C1RXM0SID  | 0430             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | MIDE       | _      | EID<  | 17:16> | xxxx          |

| C1RXM0EID  | 0432             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       | •      |       |        | xxxx          |

| C1RXM1SID  | 0434             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | MIDE       | —      | EID<  | 17:16> | xxxx          |

| C1RXM1EID  | 0436             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       | •      |       |        | xxxx          |

| C1RXM2SID  | 0438             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | MIDE EID<17:16> |            |        |       |        | xxxx          |

| C1RXM2EID  | 043A             |                                       | EID<15:8><br>SID<10:3> SID<2:0> |           |        |          |        |                               |             | EID<                        | 7:0>     |        | •               |            | xxxx   |       |        |               |

| C1RXF0SID  | 0440             | SID<10:3><br>EID<15:8>                |                                 |           |        |          |        | SID<2:0> — EXIDE — EID<17:16> |             |                             |          |        |                 |            | 17:16> | xxxx  |        |               |

| C1RXF0EID  | 0442             |                                       | EID<15:8>                       |           |        |          |        |                               |             | EID<7:0>                    |          |        |                 |            |        |       | xxxx   |               |

| C1RXF1SID  | 0444             |                                       |                                 | SID<10:3> |        |          |        |                               |             |                             | SID<2:0> |        | _               | EXIDE      | _      | EID<  | 17:16> | xxxx          |

| C1RXF1EID  | 0446             |                                       | EID<15:8>                       |           |        |          |        |                               |             |                             |          | EID<   | 7:0>            |            |        |       | xxxx   |               |

| C1RXF2SID  | 0448             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | EXIDE      |        | EID<  | 17:16> | xxxx          |

| C1RXF2EID  | 044A             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF3SID  | 044C             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             | SID<2:0> — EXIDE — EID<17:1 |          |        |                 |            | 17:16> | xxxx  |        |               |

| C1RXF3EID  | 044E             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             | EID<7:0>                    |          |        |                 |            |        |       | xxxx   |               |

| C1RXF4SID  | 0450             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | _               | EXIDE      | —      | EID<  | 17:16> | xxxx          |

| C1RXF4EID  | 0452             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF5SID  | 0454             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | EXIDE      | _      | EID<  | 17:16> | xxxx          |

| C1RXF5EID  | 0456             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF6SID  | 0458             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | EXIDE      | —      | EID<  | 17:16> | xxxx          |

| C1RXF6EID  | 045A             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF7SID  | 045C             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | EXIDE      | —      | EID<  | 17:16> | xxxx          |

| C1RXF7EID  | 045E             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF8SID  | 0460             | 0 SID<10:3> SID<2:0> — EXIDE — EID<17 |                                 |           |        |          | 17:16> | xxxx                          |             |                             |          |        |                 |            |        |       |        |               |

| C1RXF8EID  | 0462             |                                       |                                 |           | EID<   | :15:8>   |        | EID<7:0>                      |             |                             |          |        |                 | xxxx       |        |       |        |               |

| C1RXF9SID  | 0464             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | _               | EXIDE      | _      | EID<  | 17:16> | xxxx          |

| C1RXF9EID  | 0466             |                                       |                                 |           | EID<   | :15:8>   |        |                               |             |                             |          |        | EID<            | 7:0>       |        |       |        | xxxx          |

| C1RXF10SID | 0468             |                                       |                                 |           | SID<   | :10:3>   |        |                               |             |                             | SID<2:0> |        | —               | EXIDE      | —      | EID<  | 17:16> | xxxx          |

| C1RXF10EID | D 046A EID<15:8> |                                       |                                 |           |        | EID<7:0> |        |                               |             |                             |          |        | xxxx            |            |        |       |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR dsPIC33FJXXXGP506A/510A/706A/708A/710A DEVICES ONLY

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                        | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|-----------|--------|--------|--------|--------|-------|------------------------------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11SID | 046C |        |           |        | SID<   | :10:3> |        |       |                              |                               | SID<2:0> |       | _     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF11EID | 046E |        |           |        | EID<   | :15:8> |        |       |                              |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF12SID | 0470 |        |           |        | SID<   | :10:3> |        |       |                              | SID<2:0> — EXIDE — EID<17:16> |          |       |       |       |       |       | 7:16> | xxxx          |

| C1RXF12EID | 0472 |        | EID<15:8> |        |        |        |        |       |                              |                               |          | EID<  | 7:0>  |       |       |       | xxxx  |               |

| C1RXF13SID | 0474 |        | SID<10:3> |        |        |        |        |       | SID<2:0>                     |                               | _        | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |               |

| C1RXF13EID | 0476 |        |           |        | EID<   | :15:8> |        |       |                              |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF14SID | 0478 |        |           |        | SID<   | :10:3> |        |       |                              |                               | SID<2:0> |       | _     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A |        | EID<15:8> |        |        |        |        |       |                              |                               | EID<     | 7:0>  |       |       |       | xxxx  |       |               |

| C1RXF15SID | 047C |        | SID<10:3> |        |        |        |        |       | SID<2:0> — EXIDE — EID<17:16 |                               |          |       |       | 7:16> | xxxx  |       |       |               |

| C1RXF15EID | 047E |        | EID<15:8> |        |        |        |        |       | EID<7:0>                     |                               |          |       |       |       |       | xxxx  |       |               |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

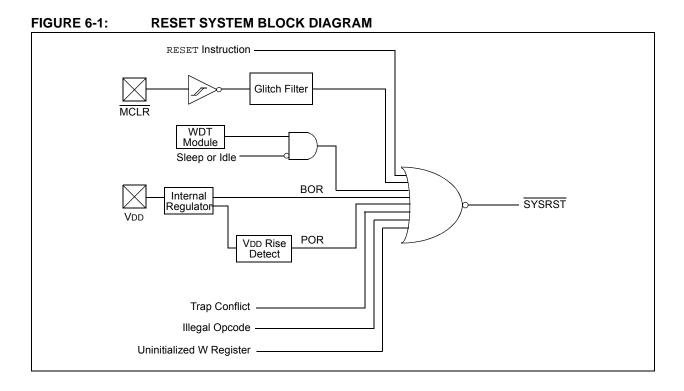

### 6.0 RESET

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section

8. "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the POR bit (RCON<0>), that are set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

| R/W-0       R/W-0 <th< th=""><th>REGISTER</th><th>7-5: IFS0:</th><th>INTERRUPT</th><th>FLAG STAT</th><th>US REGIST</th><th>ER 0</th><th></th><th></th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REGISTER | 7-5: IFS0:   | INTERRUPT        | FLAG STAT        | US REGIST       | ER 0              |          |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|------------------|------------------|-----------------|-------------------|----------|-------|

| bit 15 bit 2 bit 3 bit 4                                                                                                | U-0      | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0             | R/W-0    | R/W-0 |

| RW-0       RW no is is is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _        | DMA1IF       | AD1IF            | U1TXIF           | U1RXIF          | SPI1IF            | SPI1EIF  | T3IF  |

| T2IF     OC2IF     IC2IF     DMA01IF     T1IF     OC1IF     IC1IF     INTOIF       bit 7     bit 7     bit 0     bit 0     bit 0       Legend:     R = Readable bit     W = Writable bit     U = Unimplemented bit, read as '0'     bit 0       n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15     Unimplemented: Read as '0'     '0' = Bit is cleared     x = Bit is unknown       bit 14     DMA1F: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit     1 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has not occurred     0 = Interrupt request has not occurred     0 = Interrupt request has not occurred       0 = Interrupt request has occurred     0 = Interrupt request has occurred     0 = Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15   |              |                  |                  |                 |                   |          | bit 8 |

| T2IF     OC2IF     IC2IF     DMA01IF     T1IF     OC1IF     IC1IF     INTOIF       bit 7     bit 7     bit 0     bit 0       Legend:     R = Readable bit     W = Writable bit     U = Unimplemented bit, read as '0'       n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15     Unimplemented: Read as '0'     '0' = Bit is cleared     x = Bit is unknown       bit 14     DMA1F: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit     1 = Interrupt request has not occurred     0 = Interrupt request has not occurred       bit 13     AD1F: ADC1 Conversion Complete Interrupt Flag Status bit     1 = Interrupt request has not occurred       bit 12     U1TXF: UART1 Transmitter Interrupt Flag Status bit     1 = Interrupt request has not occurred       bit 12     U1TXF: UART1 Receiver Interrupt Flag Status bit     1 = Interrupt request has not occurred       bit 11     U1RXF: UART1 Receiver Interrupt Flag Status bit     1 = Interrupt request has not occurred       bit 10     SPI1E: SPI1 Event Interrupt Flag Status bit     1 = Interrupt request has occurred       bit 19     SPI1E: SPI1 Faut Interrupt Flag Status bit     1 = Interrupt request has occurred       bit 10     SPI1E: SPI1 Faut Interrupt Flag Status bit     1 = Interrupt request has occurred       bit 8     T3F: Timer2 Interrupt Flag Status bit     1 = Interrupt request has occu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W/-0   | R/M_0        | R/M-0            | R/\/_0           | R/\/_0          | R/M-0             | R/M-0    | R/M-0 |

| bit 7 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 7 bit 0 bit 15 bit 14 bit 12 bit 13 bit 13 bit 14 bit                                                                                                 |          |              | -                | -                | -               | -                 |          |       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'          bit 14       DMA1IF: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit       1 = Interrupt request has occurred         0 = Interrupt request has not occurred       0 = Interrupt request has not occurred         bit 13       AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred       0 = Interrupt request has not occurred         bit 12       U1TXIF: UART1 Transmitter Interrupt Flag Status bit         1 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has not occurred       0 = Interrupt request has not occurred         bit 10       SPI1EE: SPI1 Fault Interrupt Flag Status bit       1 = Interrupt request has not occurred         bit 3       Interrupt request has not occurred       0 = Interrupt request has no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 0021         | 10211            | DIVIAUTI         | 1111            | 00111             | 10111    | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'          bit 14       DMA1IF: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit       1 = Interrupt request has occurred         0       Interrupt request has not occurred       0         bit 13       AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit       1 = Interrupt request has not occurred         0       Interrupt request has not occurred       0         bit 12       U1TXIF: UART1 Transmitter Interrupt Flag Status bit       1 = Interrupt request has not occurred         0       Interrupt request has occurred       0       Interrupt request has not occurred         bit 11       U1RXIF: UART1 Receiver Interrupt Flag Status bit       1 = Interrupt request has occurred         0       Interrupt request has occurred       0       Interrupt request has occurred         bit 10       SP11FE: SP11 Fault Interrupt Flag Status bit       1 = Interrupt request has not occurred         bit 3       Interrupt request has not occurred       0       Interrupt request has not occurred         bit 4       DMCLIP: Tenge Status bit       1 = Interrupt request has not occurred       0 = Interrupt request has not occurred </td <td>Logondu</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Logondu  |              |                  |                  |                 |                   |          |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'          bit 14       DMA1F: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit       1 = Interrupt request has occurred         0 = Interrupt request has not occurred       0 = Interrupt request has not occurred       0 = Interrupt request has not occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred       0 = Interrupt request has occurred         0 = Interrupt request has occurred       0 = Interrupt request has occurred       0 = Interrupt request has occurred         bit 10       SPHEIF: SPH 5 Event Interrupt Flag Status bit       1 = Interrupt request has occurred       0 = Interrupt request has occurred         bit 8       T3F: Timer3 Interrupt Flag Status bit       1 = Interrupt request has not occurred       0 = Interrupt request has not occurred         bit 7       T2F: Timer2 Interrupt Flag Status bit       1 = Interrupt request has not occurred       0 = Interrupt request has not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | - hit        | VV - Writabla    | bit              | II – Unimplo    | montod bit roa    | d as '0' |       |

| bit 15 Unimplemented: Read as '0'<br>bit 14 DMA1IF: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit<br>1 = Interrupt request has not occurred<br>0 = Interrupt request has not occurred<br>10 = Interrupt request has not occurred<br>bit 13 AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit<br>1 = Interrupt request has not occurred<br>bit 12 U1TXIF: UART1 Transmitter Interrupt Flag Status bit<br>1 = Interrupt request has not occurred<br>0 = Interrupt request has not occurred<br>bit 12 U1TXIF: UART1 Transmitter Interrupt Flag Status bit<br>1 = Interrupt request has not occurred<br>0 = Interrupt request has not occurred<br>bit 10 URXIF: UART1 Receiver Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred<br>bit 10 SPH1F: SPH1 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has occurred<br>0 = Interrupt request has occurred<br>bit 9 SPH1EFI: SPH1 Event Interrupt Flag Status bit<br>1 = Interrupt request has not occurred<br>0 = Interrupt request has occurred<br>0 = Interrupt request has not occurred<br>0 = |          |              |                  |                  | •               |                   |          | 0.00  |

| bit 14       DMA IF: DMA Channel 1 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 13       AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 12       UTXIF: UART1 Transmitter Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 10       SPI1IF: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 6       C2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | PUR          | I = DILIS SE     |                  |                 | eareu             |          | OWI   |

| <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 13 AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 12 U1TXIF: UART1 Transmitter Interrupt Flag Status bit</li> <li>1 = Interrupt request has not occurred</li> <li>bit 12 U1TXIF: UART1 Receiver Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 11 U1RXIF: UART1 Receiver Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>0 = Interrupt request has occurred</li> <li>0 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>0 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>0 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred<td>bit 15</td><td>Unimplemer</td><td>nted: Read as</td><td>0'</td><td></td><td></td><td></td><td></td></li></ul>                                                                                                                                              | bit 15   | Unimplemer   | nted: Read as    | 0'               |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 13       AD1F: ADC1 Conversion Complete Interrupt Flag Status bit         1 = Interrupt request has occurred         o = Interrupt request has occurred         bit 12       U1TXIF: UART1 Transmitter Interrupt Flag Status bit         1 = Interrupt request has occurred         o = Interrupt request has occurred         bit 11       U1RXIF: UART1 Receiver Interrupt Flag Status bit         1 = Interrupt request has occurred         o = Interrupt request has occ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 14   | DMA1IF: DM   | 1A Channel 1 D   | ata Transfer C   | Complete Inter  | rupt Flag Status  | s bit    |       |

| <ul> <li>i = Interrupt request has occurred</li> <li>i Interrupt request has not occurred</li> <li>i = Interrupt request has not occurred</li> <li>i = Interrupt request has not occurred</li> <li>i = Interrupt request has not occurred</li> <li>i = Interrupt request has not occurred</li> <li>i = Interrupt request has occurred</li> <li< td=""><td></td><td></td><td>•</td><td></td><td></td><td></td><td></td><td></td></li<></ul>                                                                                                                                                                                |          |              | •                |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 12       U1TXIF: UART1 Transmitter Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 11       UIRXIF: UART1 Receiver Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 10       SPI1IF: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has not occurred         0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has not occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 13   | AD1IF: ADC   | 1 Conversion C   | Complete Interr  | rupt Flag Statu | ıs bit            |          |       |

| 1 = Interrupt request has not occurred         bit 11       U1RXIF: UART1 Receiver Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 10       SPI1EF: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 10       SPI1EF: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 7       T2IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 4       DMAO1IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |              |                  |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 11       U1RXIF: UART1 Receiver Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 10       SPI1F: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 12   | U1TXIF: UA   | RT1 Transmitte   | r Interrupt Flag | g Status bit    |                   |          |       |

| 1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 10       SPI1E: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 9       SPI1E: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |              |                  |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 10       SPI1IF: SPI1 Event Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 11   | U1RXIF: UA   | RT1 Receiver I   | nterrupt Flag S  | Status bit      |                   |          |       |

| 1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |              | •                |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 9       SPI1EIF: SPI1 Fault Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 10   | SPI1IF: SPI1 | I Event Interrup | ot Flag Status b | pit             |                   |          |       |

| 1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       Interrupt request has occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |              |                  |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 8       T3IF: Timer3 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 9    | SPI1EIF: SP  | 11 Fault Interru | pt Flag Status   | bit             |                   |          |       |

| 1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         0 = Interrupt request has occurred         0 = Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |              |                  |                  |                 |                   |          |       |

| 0 = Interrupt request has not occurred         bit 7       T2IF: Timer2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 6       OC2IF: Output Compare Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has occurred         0 = Interrupt request has not occurred         bit 5       IC2IF: Input Capture Channel 2 Interrupt Flag Status bit         1 = Interrupt request has occurred         0 = Interrupt request has occurred         bit 4       DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit         1 = Interrupt request has occurred         bit 3       T1IF: Timer1 Interrupt Flag Status bit         1 = Interrupt request has not occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 8    | T3IF: Timer3 | Interrupt Flag   | Status bit       |                 |                   |          |       |

| <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 6 OC2IF: Output Compare Channel 2 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 5 IC2IF: Input Capture Channel 2 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 4 DMA01IF: DMA Channel 0 Data Transfer Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>bit 3 T1IF: Timer1 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |              |                  |                  |                 |                   |          |       |