Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

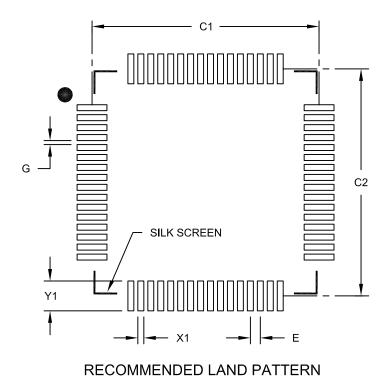

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp510a-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

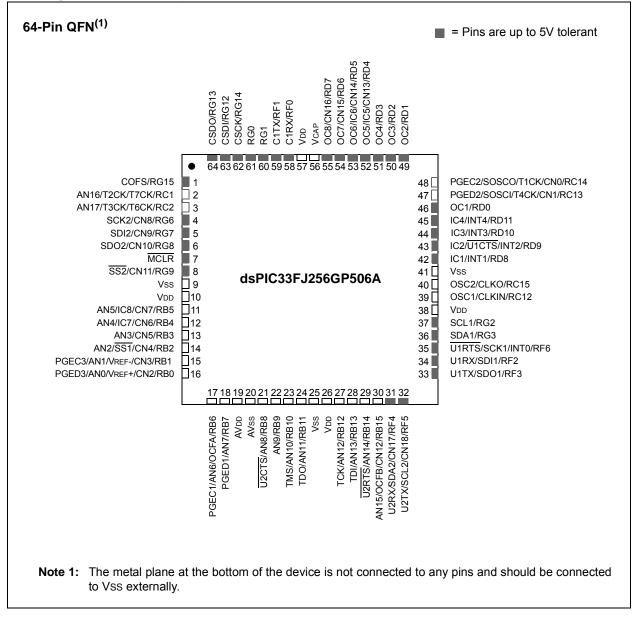

#### Pin Diagrams (Continued)

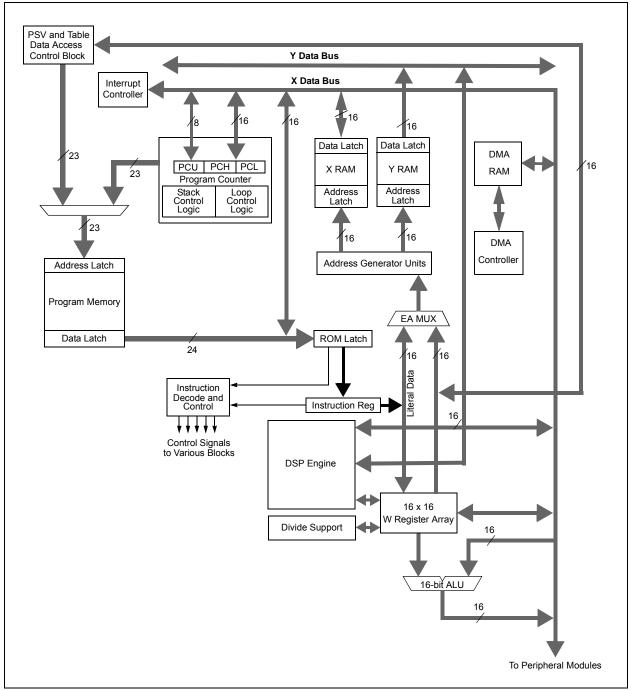

#### FIGURE 3-1: dsPIC33FJXXXGPX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

#### TABLE 4-15: ADC1 REGISTER MAP

| File Name   | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7    | Bit 6     | Bit 5  | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | All<br>Resets |

|-------------|------|--------|-----------|--------|---------|--------|-----------|---------|----------|----------|-----------|--------|-----------|--------|-----------|-----------|---------|---------------|

| ADC1BUF0    | 0300 |        |           |        |         |        |           |         | ADC Data | Buffer 0 |           |        |           |        |           |           |         | xxxx          |

| AD1CON1     | 0320 | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B     | FOR     | И<1:0>   | :        | SSRC<2:0> |        | _         | SIMSAM | ASAM      | SAMP      | DONE    | 0000          |

| AD1CON2     | 0322 | ١      | /CFG<2:0> | >      | _       | _      | CSCNA     | CHP     | S<1:0>   | BUFS     | _         |        | SMPI      | <3:0>  |           | BUFM      | ALTS    | 0000          |

| AD1CON3     | 0324 | ADRC   |           | —      |         | S      | SAMC<4:0> |         |          |          |           |        | ADCS<7:0> |        |           |           |         |               |

| AD1CHS123   | 0326 | _      |           | —      | _       |        | CH123N    | NB<1:0> | CH123SB  |          |           |        | —         | —      | CH123N    | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0     | 0328 | CH0NB  |           | —      |         | C      | H0SB<4:0> | >       |          | CH0NA    |           |        |           | (      | CH0SA<4:( | )>        |         | 0000          |

| AD1PCFGH(1) | 032A | PCFG31 | PCFG30    | PCFG29 | PCFG28  | PCFG27 | PCFG26    | PCFG25  | PCFG24   | PCFG23   | PCFG22    | PCFG21 | PCFG20    | PCFG19 | PCFG18    | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL    | 032C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8    | PCFG7    | PCFG6     | PCFG5  | PCFG4     | PCFG3  | PCFG2     | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)  | 032E | CSS31  | CSS30     | CSS29  | CSS28   | CSS27  | CSS26     | CSS25   | CSS24    | CSS23    | CSS22     | CSS21  | CSS20     | CSS19  | CSS18     | CSS17     | CSS16   | 0000          |

| AD1CSSL     | 0330 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8     | CSS7     | CSS6      | CSS5   | CSS4      | CSS3   | CSS2      | CSS1      | CSS0    | 0000          |

| AD1CON4     | 0332 | _      | _         | _      | —       | _      | _         | _       | _        | _        | _         | _      | _         | _      | [         | DMABL<2:( | )>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

#### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8    | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|--------|----------|---------|----------|----------|----------|-------|-------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         |        |          |         | ADC Data | Buffer 0 |          |       |       |        |        |          |         | xxxx          |

| AD2CON1   | 0360 | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B    | FORI    | M<1:0>   | Ş        | SSRC<2:0 | >     | _     | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 | Ň      | VCFG<2:0> | >      | _       | _      | CSCNA    | CHP     | S<1:0>   | BUFS     | _        |       | SMPI  | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | S      | AMC<4:0> |         |          |          |          |       | ADC   | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _      | CH123N   | IB<1:0> | CH123SB  | _        | _        | _     | _     | _      | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |        | CH0S     | B<3:0>  |          | CH0NA    | _        | _     | _     |        | CH0S   | A<3:0>   |         | 0000          |

| Reserved  | 036A | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _      | _        | _       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10   | PCFG9   | PCFG8    | PCFG7    | PCFG6    | PCFG5 | PCFG4 | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _      | _        | _       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8     | CSS7     | CSS6     | CSS5  | CSS4  | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       |        | _        | _       | _        | _        | _        | _     | _     | _      |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-27: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 |        | _      |       |       | _     | —     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 |       | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | _      | _     | -     | _     | _     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  |        |        | _     |       | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-28: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-29: PORTE REGISTER MAP<sup>(1)</sup>

|           | -    | -      |        |        |        |        |        |       |       |        |        |        |        |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | —      | —      | —      | —      | _      | _     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | OOFF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-30: PORTF REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF     | 02DE | _      | _      | TRISF13 | TRISF12 | —      | -      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF     | 02E0 | _      | _      | RF13    | RF12    | _      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF      | 02E2 | _      | _      | LATF13  | LATF12  | _      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF      | 06DE | _      | _      | ODCF13  | ODCF12  | _      | _      | _     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | See Notes        |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        | _                     |               | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | Tstartup + Trst        | TOST + TLOCK          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | Trst                   | _                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | —             | 3                |

| Software        | Any Clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | —             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay (10 μs nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- **3:** TRST = Internal state Reset time (20 μs nominal).

- **4:** Tos⊤ = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- 5: TLOCK = PLL lock time (20 μs nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

#### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

<sup>© 2009-2012</sup> Microchip Technology Inc.

| 1                                 | Reset – GOTO Instruction       | 0x000000  |                                                        |

|-----------------------------------|--------------------------------|-----------|--------------------------------------------------------|

|                                   | Reset – GOTO Address           | 0x000002  |                                                        |

|                                   | Reserved                       | 0x000004  |                                                        |

|                                   | Oscillator Fail Trap Vector    |           |                                                        |

|                                   | Address Error Trap Vector      | _         |                                                        |

|                                   | Stack Error Trap Vector        | _         |                                                        |

|                                   | Math Error Trap Vector         | -         |                                                        |

|                                   | DMA Error Trap Vector          | _         |                                                        |

|                                   | Reserved                       | _         |                                                        |

|                                   |                                | _         |                                                        |

|                                   | Reserved<br>Interrupt Vector 0 | 0x000014  |                                                        |

|                                   |                                | 0x000014  |                                                        |

|                                   | Interrupt Vector 1             | -         |                                                        |

|                                   | ~                              | _         |                                                        |

|                                   | ~                              | _         |                                                        |

|                                   | ~                              |           |                                                        |

|                                   | Interrupt Vector 52            | 0x00007C  | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53            | 0x00007E  |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 54            | 0x000080  |                                                        |

| Pric                              | ~                              |           |                                                        |

| ц<br>2                            | ~                              |           |                                                        |

| rde                               | ~                              |           |                                                        |

| 0                                 | Interrupt Vector 116           | 0x0000FC  |                                                        |

| ıra                               | Interrupt Vector 117           | 0x0000FE  |                                                        |

| atı                               | Reserved                       | 0x000100  |                                                        |

| Z                                 | Reserved                       | 0x000102  |                                                        |

| sinç                              | Reserved                       |           |                                                        |

| sas                               | Oscillator Fail Trap Vector    |           |                                                        |

| CCE                               | Address Error Trap Vector      |           |                                                        |

| De                                | Stack Error Trap Vector        |           |                                                        |

|                                   | Math Error Trap Vector         |           |                                                        |

|                                   | DMA Error Trap Vector          |           |                                                        |

|                                   | Reserved                       |           |                                                        |

|                                   | Reserved                       |           |                                                        |

|                                   | Interrupt Vector 0             | 0x000114  |                                                        |

|                                   | Interrupt Vector 1             |           |                                                        |

|                                   | ~                              | -         |                                                        |

|                                   | ~                              | -         |                                                        |

|                                   | ~                              | -         | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52            | 0x00017C  |                                                        |

|                                   | Interrupt Vector 53            | 0x00017E  |                                                        |

|                                   | Interrupt Vector 54            | 0x000180  |                                                        |

|                                   |                                | 0,000,000 |                                                        |

|                                   | ~                              | -         |                                                        |

|                                   | ~                              | -         |                                                        |

|                                   | Interrupt Vector 116           |           | l                                                      |

|                                   | Interrupt Vector 117           | 0x0001FE  |                                                        |

| ▼                                 | Start of Code                  | 0x0001FE  |                                                        |

|                                   |                                |           |                                                        |

|                                   |                                |           |                                                        |

|                                   |                                |           |                                                        |

|                                   |                                |           |                                                        |

| R/W-0            | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0          | R/W-0          |

|------------------|-----------------|----------------------------------|-----------------|------------------|------------------|----------------|----------------|

| U2TXIF<br>bit 15 | U2RXIF          | INT2IF                           | T5IF            | T4IF             | OC4IF            | OC3IF          | DMA21IF<br>bit |

|                  |                 |                                  |                 |                  |                  |                | DIL            |

| R/W-0            | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | U-0              | R/W-0          | R/W-0          |

| IC8IF            | IC7IF           | AD2IF                            | INT1IF          | CNIF             | _                | MI2C1IF        | SI2C1IF        |

| bit 7            |                 | !                                |                 | · · ·            |                  | ·              | bit            |

| Legend:          |                 |                                  |                 |                  |                  |                |                |

| R = Readable     | e bit           | W = Writable                     | bit             | U = Unimplen     | nented bit, read | d as '0'       |                |

| -n = Value at    | POR             | '1' = Bit is set                 | :               | '0' = Bit is cle | ared             | x = Bit is unk | nown           |

| bit 15           | U2TXIF: UAF     | T2 Transmitte                    | r Interrupt Fla | g Status bit     |                  |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 14           | U2RXIF: UAF     | RT2 Receiver I                   | nterrupt Flag   | Status bit       |                  |                |                |

|                  |                 | request has oc<br>request has no |                 |                  |                  |                |                |

| bit 13           | INT2IF: Exter   | nal Interrupt 2                  | Flag Status b   | it               |                  |                |                |

|                  | •               | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 12           | T5IF: Timer5    | Interrupt Flag                   | Status bit      |                  |                  |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 11           | T4IF: Timer4    | Interrupt Flag                   | Status bit      |                  |                  |                |                |

|                  | •               | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 10           | OC4IF: Outpu    | ut Compare Ch                    | annel 4 Interr  | upt Flag Status  | bit              |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 9            | •               | •                                |                 | upt Flag Status  | hit              |                |                |

| bit 5            | 1 = Interrupt i | equest has oc                    | curred          | upt i lag otatus | bit              |                |                |

| L:1 0            | •               | request has no                   |                 |                  |                  | - h'i          |                |

| bit 8            |                 | request has oc                   |                 | Complete Inter   | rupt Flag Statu  | IS DIL         |                |

|                  |                 | equest has no                    |                 |                  |                  |                |                |

| bit 7            | IC8IF: Input C  | Capture Chann                    | el 8 Interrupt  | Flag Status bit  |                  |                |                |

|                  |                 | equest has oc                    |                 |                  |                  |                |                |

| hit C            | -               | equest has no                    |                 | Flag Status hit  |                  |                |                |

| bit 6            | 1 = Interrupt i | equest has oc                    | curred          | Flag Status bit  |                  |                |                |

| bit 5            |                 | equest has no                    |                 | rupt Elag Statu  | - hit            |                |                |

| DIL U            |                 | equest has oc                    | -               | rupt Flag Status |                  |                |                |

|                  | •               | equest has no                    |                 |                  |                  |                |                |

|                  | INT1IF. Exter   | nal Interrunt 1                  | Flag Status b   | it               |                  |                |                |

| bit 4            |                 | nai interrupt i                  | i lug oluluo b  |                  |                  |                |                |

| REGISTER 7      | -13: IEC3:      | INTERRUPT                         |                | ONTROL RE        | GISTER 3         |                 |       |

|-----------------|-----------------|-----------------------------------|----------------|------------------|------------------|-----------------|-------|

| U-0             | U-0             | R/W-0                             | R/W-0          | R/W-0            | U-0              | U-0             | R/W-0 |

| —               | _               | DMA5IE                            | DCIIE          | DCIEIE           | —                | —               | C2IE  |

| bit 15          |                 |                                   | 1              | 1                |                  |                 | bit 8 |

| R/W-0           | R/W-0           | R/W-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIE          | INT4IE          | INT3IE                            | T9IE           | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |

| bit 7           |                 |                                   |                |                  |                  |                 | bit 0 |

| Legend:         |                 |                                   |                |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable                      | bit            | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at F |                 | '1' = Bit is set                  |                | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

|                 |                 |                                   |                |                  |                  |                 |       |

| bit 15-14       | Unimplemen      | ted: Read as '                    | 0'             |                  |                  |                 |       |

| bit 13          | DMA5IE: DM      | A Channel 5 D                     | ata Transfer ( | Complete Interi  | rupt Enable bit  |                 |       |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |

| bit 12          | DCIIE: DCI E    | vent Interrupt E                  | Enable bit     |                  |                  |                 |       |

|                 |                 | request enable                    |                |                  |                  |                 |       |

|                 | -               | request not ena                   |                |                  |                  |                 |       |

| bit 11          |                 | Error Interrupt                   |                |                  |                  |                 |       |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |

| bit 10-9        | Unimplemen      | ted: Read as '                    | 0'             |                  |                  |                 |       |

| bit 8           | C2IE: ECAN2     | 2 Event Interrup                  | ot Enable bit  |                  |                  |                 |       |

|                 | •               | request enable<br>request not ena |                |                  |                  |                 |       |

| bit 7           | C2RXIE: ECA     | AN2 Receive D                     | ata Ready Int  | errupt Enable I  | bit              |                 |       |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |

| bit 6           | •               | rnal Interrupt 4                  |                |                  |                  |                 |       |

| bit o           | 1 = Interrupt r | request enable<br>request not ena | d              |                  |                  |                 |       |

| bit 5           | •               | nal Interrupt 3                   |                |                  |                  |                 |       |

|                 | 1 = Interrupt r | request enable<br>request not ena | d              |                  |                  |                 |       |

| bit 4           | -               | Interrupt Enab                    |                |                  |                  |                 |       |

|                 | 1 = Interrupt r | request enable                    | d              |                  |                  |                 |       |

| bit 3           | -               | request not ena                   |                |                  |                  |                 |       |

| DIL 3           | 1 = Interrupt r | Interrupt Enab                    | d              |                  |                  |                 |       |

| bit 2           |                 | request not ena<br>2 Master Even  |                | nahla hit        |                  |                 |       |

|                 |                 | request enable                    |                |                  |                  |                 |       |

|                 |                 | request not ena                   |                |                  |                  |                 |       |

| bit 1           | -               | 2 Slave Events                    |                | able bit         |                  |                 |       |

|                 |                 | request enable                    |                |                  |                  |                 |       |

|                 | -               | request not ena                   |                |                  |                  |                 |       |

| bit 0           |                 | Interrupt Enab                    |                |                  |                  |                 |       |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |

| REGISTER 7-20: IP | PC5: INTERRUPT PRIORITY CONTROL REGISTER 5 |

|-------------------|--------------------------------------------|

|-------------------|--------------------------------------------|

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|-----------------|--------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _               |                    | IC8IP<2:0>                              |                 | —                |                 | IC7IP<2:0>      |       |

| bit 15          |                    |                                         |                 |                  |                 |                 | bit 8 |

|                 |                    |                                         |                 |                  |                 |                 |       |

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

| —               |                    | AD2IP<2:0>                              |                 | —                |                 | INT1IP<2:0>     |       |

| bit 7           |                    |                                         |                 |                  |                 |                 | bit   |

| Legend:         |                    |                                         |                 |                  |                 |                 |       |

| R = Readable    | bit                | W = Writable t                          | oit             | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at I | POR                | '1' = Bit is set                        |                 | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

| bit 15          | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 14-12       | -                  | Input Capture C                         |                 | rrunt Priority h | nite            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Interr  | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 11          |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 10-8        | -                  | Input Capture C                         |                 | rrupt Priority b | oits            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 = Interru | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 7           | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 6-4         | AD2IP<2:0>         | : ADC2 Convers                          | ion Complete    | e Interrupt Pric | rity bits       |                 |       |

|                 | 111 = Interru      | upt is priority 7 (h                    | nighest priorit | y interrupt)     |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 |                    | upt is priority 1<br>upt source is disa | abled           |                  |                 |                 |       |

| bit 3           |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 2-0         | -                  | : External Interr                       |                 | hits             |                 |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Intern  | int is priority 1                       |                 |                  |                 |                 |       |

|                 | 001 = merrl        | upt is priority 1                       |                 |                  |                 |                 |       |

| REGISTER '    | <u>10-2:</u> PMD2 | 2: PERIPHER                        |                  | DISABLE C         | ONTROL RE        | GISTER 2        |       |

|---------------|-------------------|------------------------------------|------------------|-------------------|------------------|-----------------|-------|

| R/W-0         | R/W-0             | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| IC8MD         | IC7MD             | IC6MD                              | IC5MD            | IC4MD             | IC3MD            | IC2MD           | IC1MD |

| bit 15        |                   |                                    |                  |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0             | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| OC8MD         | OC7MD             | OC6MD                              | OC5MD            | OC4MD             | OC3MD            | OC2MD           | OC1MD |

| bit 7         |                   |                                    |                  |                   |                  |                 | bit 0 |

| Legend:       |                   |                                    |                  |                   |                  |                 |       |

| R = Readable  | e bit             | W = Writable                       | bit              | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR               | '1' = Bit is set                   |                  | '0' = Bit is clea | ared             | x = Bit is unkr | lown  |

| bit 15        | IC8MD: Input      | Capture 8 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 8 module i<br>ture 8 module i |                  |                   |                  |                 |       |

| bit 14        | IC7MD: Input      | Capture 7 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 7 module i<br>ture 7 module i |                  |                   |                  |                 |       |

| bit 13        |                   | Capture 6 Mod                      |                  | ŀ                 |                  |                 |       |

|               | 1 = Input Cap     | ture 6 module i<br>ture 6 module i | s disabled       |                   |                  |                 |       |

| bit 12        |                   | Capture 5 Mod                      |                  | t                 |                  |                 |       |

|               |                   | ture 5 module i<br>ture 5 module i |                  |                   |                  |                 |       |

| bit 11        | IC4MD: Input      | Capture 4 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 4 module i<br>ture 4 module i |                  |                   |                  |                 |       |

| bit 10        | •                 | Capture 3 Mod                      |                  | t                 |                  |                 |       |

|               |                   | ture 3 module i<br>ture 3 module i |                  |                   |                  |                 |       |

| bit 9         | IC2MD: Input      | Capture 2 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 2 module i<br>ture 2 module i |                  |                   |                  |                 |       |

| bit 8         | IC1MD: Input      | Capture 1 Mod                      | lule Disable bit | t                 |                  |                 |       |

|               |                   | ture 1 module i<br>ture 1 module i |                  |                   |                  |                 |       |

| bit 7         | OC8MD: Out        | put Compare 8                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 8 modu<br>ompare 8 modu     |                  |                   |                  |                 |       |

| bit 6         | OC7MD: Out        | put Compare 4                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 7 modu<br>ompare 7 modu     |                  |                   |                  |                 |       |

| bit 5         | -                 | put Compare 6                      |                  | e bit             |                  |                 |       |

|               | •                 | ompare 6 modu<br>ompare 6 modu     |                  |                   |                  |                 |       |

| bit 4         | OC5MD: Out        | put Compare 5                      | Module Disabl    | e bit             |                  |                 |       |

|               |                   | ompare 5 modu<br>ompare 5 modu     |                  |                   |                  |                 |       |

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| R/W-0                 | U-0                           | R/W-0                             | U-0            | U-0              | U-0            | U-0                | U-0   |  |  |

|-----------------------|-------------------------------|-----------------------------------|----------------|------------------|----------------|--------------------|-------|--|--|

| TON                   |                               | TSIDL                             |                |                  |                |                    |       |  |  |

| bit 15                |                               | TOIDE                             |                |                  |                |                    | bit   |  |  |

|                       |                               |                                   |                |                  |                |                    |       |  |  |

| U-0                   | R/W-0                         | R/W-0                             | R/W-0          | R/W-0            | U-0            | R/W-0              | U-0   |  |  |

| _                     | TGATE                         | TCKP                              | S<1:0>         | T32              | _              | TCS <sup>(1)</sup> | _     |  |  |

| bit 7                 |                               |                                   |                |                  |                |                    | bit   |  |  |

|                       |                               |                                   |                |                  |                |                    |       |  |  |

| Legend:<br>R = Readab | le hit                        | W = Writable                      | hit            | U = Unimplen     | nented hit rea | d as '0'           |       |  |  |

| -n = Value a          |                               | '1' = Bit is set                  |                | 0' = Bit is cle  |                | x = Bit is unkn    | 0.000 |  |  |

|                       |                               |                                   |                |                  | arcu           |                    | OWIT  |  |  |

| bit 15                | TON: Timerx                   | On bit                            |                |                  |                |                    |       |  |  |

|                       | When T32 =                    | 1:                                |                |                  |                |                    |       |  |  |

|                       | 1 = Starts 32                 |                                   |                |                  |                |                    |       |  |  |

|                       | 0 = Stops 32                  | •                                 |                |                  |                |                    |       |  |  |

|                       | When T32 =<br>1 = Starts 16   |                                   |                |                  |                |                    |       |  |  |

|                       | 1 = Starts 16<br>0 = Stops 16 |                                   |                |                  |                |                    |       |  |  |

| bit 14                | Unimplemented: Read as '0'    |                                   |                |                  |                |                    |       |  |  |

| bit 13                | TSIDL: Stop                   | TSIDL: Stop in Idle Mode bit      |                |                  |                |                    |       |  |  |

|                       |                               |                                   |                | device enters Id | le mode        |                    |       |  |  |

|                       | 0 = Continue                  | module operat                     | ion in Idle mo | ode              |                |                    |       |  |  |

| bit 12-7              | Unimplemer                    | nted: Read as '                   | 0'             |                  |                |                    |       |  |  |

| bit 6                 | TGATE: Time                   | erx Gated Time                    | Accumulatio    | n Enable bit     |                |                    |       |  |  |

|                       | When TCS =<br>This bit is ign |                                   |                |                  |                |                    |       |  |  |

|                       | When TCS =                    |                                   |                |                  |                |                    |       |  |  |

|                       | 1 = Gated tin                 | ne accumulatio                    |                |                  |                |                    |       |  |  |

|                       |                               | ne accumulatio                    |                |                  |                |                    |       |  |  |

| bit 5-4               |                               | Timerx Input                      | Clock Presca   | ale Select bits  |                |                    |       |  |  |

|                       | 11 = 1:256                    |                                   |                |                  |                |                    |       |  |  |

|                       | 10 = 1:64<br>01 = 1:8         |                                   |                |                  |                |                    |       |  |  |

|                       | 00 = 1:1                      |                                   |                |                  |                |                    |       |  |  |

| bit 3                 | T32: 32-bit T                 | imer Mode Sele                    | ect bit        |                  |                |                    |       |  |  |

|                       |                               | nd Timery form<br>nd Timery act a |                |                  |                |                    |       |  |  |

| bit 2                 | Unimplemer                    | nted: Read as '                   | 0'             |                  |                |                    |       |  |  |

| bit 1                 | -                             | Clock Source S                    |                |                  |                |                    |       |  |  |

|                       |                               | clock from pin <sup>-</sup>       |                | rising edge)     |                |                    |       |  |  |

|                       | Unimplemer                    | -                                 |                |                  |                |                    |       |  |  |

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

#### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SSx}$ .

| Note: | This   | insures    | that  | the        | first | fra | ame |

|-------|--------|------------|-------|------------|-------|-----|-----|

|       | transr | nission a  | after | initializa | ation | is  | not |

|       | shifte | d or corru | pted. |            |       |     |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

#### 16.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en546064              |

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                            | R/W-x                                                                   | U-0                                                                                 | U-0                                  | U-0               | R/W-x            | R/W-x           | R/W-x |  |

|--------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|-------------------|------------------|-----------------|-------|--|

|                                | WAKFIL                                                                  |                                                                                     | _                                    |                   |                  | SEG2PH<2:0>     |       |  |

| bit 15                         |                                                                         | ·                                                                                   |                                      | · · · ·           |                  |                 | bit 8 |  |

| R/W-x                          | R/W-x                                                                   | R/W-x                                                                               | R/W-x                                | R/W-x             | R/W-x            | R/W-x           | R/W-x |  |

| SEG2PHTS                       | SAM                                                                     |                                                                                     | SEG1PH<2:0>                          | >                 |                  | PRSEG<2:0>      |       |  |

| bit 7                          |                                                                         |                                                                                     |                                      |                   |                  |                 | bit ( |  |

| Legend:                        |                                                                         |                                                                                     |                                      |                   |                  |                 |       |  |

| R = Readable                   | bit                                                                     | W = Writable                                                                        | bit                                  | U = Unimplen      | nented bit, read | as '0'          |       |  |

| -n = Value at P                | OR                                                                      | '1' = Bit is set                                                                    | :                                    | '0' = Bit is clea |                  |                 |       |  |

| bit 13-11<br>bit 10-8<br>bit 7 | 0 = CAN bus<br>Unimplemen<br>SEG2PH<2:(<br>111 = Length<br>000 = Length |                                                                                     | used for wake<br>o'<br>fer Segment 2 | bits              |                  |                 |       |  |

| bit 6                          | SAM: Samp<br>1 = Bus line i                                             | ogrammable<br>n of SEG1PH b<br>le of the CAN b<br>is sampled thre<br>is sampled onc | ous Line bit<br>e times at the       | sample point      | Time (IPT), wh   | ichever is grea | ter   |  |

| bit 5-3                        |                                                                         | <b>0&gt;:</b> Phase Buff<br>n is 8 x TQ                                             |                                      | •                 |                  |                 |       |  |

| bit 2-0                        | PRSEG<2:0:<br>111 = Length<br>000 = Length                              |                                                                                     | Time Segmer                          | nt bits           |                  |                 |       |  |

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------------|----------------------------------|---------------------------------------|------------------|------------------|-----------------|--------|

| F15M          | SK<1:0>                              | F14MS                            | <<1:0>                                | F13M             | SK<1:0>          | F12MSI          | K<1:0> |

| bit 15        |                                      | ł                                |                                       |                  |                  | ł               | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| R/W-0         | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| F11M          | SK<1:0>                              | F10MS                            | <<1:0>                                | F9MS             | SK<1:0>          | F8MSK           | (<1:0> |

| bit 7         |                                      |                                  |                                       |                  |                  |                 | bi     |

|               |                                      |                                  |                                       |                  |                  |                 |        |

| Legend:       |                                      |                                  |                                       |                  |                  |                 |        |

| R = Readable  |                                      | W = Writable I                   | bit                                   | -                | mented bit, read |                 |        |

| -n = Value at | POR                                  | '1' = Bit is set                 |                                       | '0' = Bit is cle | eared            | x = Bit is unkn | own    |

|               |                                      |                                  |                                       | ,                |                  |                 |        |

| bit 15-14     |                                      | >: Mask Source                   | e for Filter 15                       | DIT              |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 13-12     | F14MSK<1:0                           | >: Mask Source                   | e for Filter 14                       | bit              |                  |                 |        |

|               | 11 = Reserve                         | -,                               |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 11-10     | -                                    | >: Mask Source                   |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | -                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 9-8       | <b>F12MSK&lt;1:0</b><br>11 = Reserve | >: Mask Source                   | e for Filter 12                       | bit              |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               | •                                    | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 7-6       |                                      | >: Mask Source                   | e for Filter 11 b                     | oit              |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

| bit 5-4       |                                      | Source                           |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         |                                  |                                       | 5 TC             |                  |                 |        |

|               |                                      | nce Mask 2 reg                   | isters contain                        | mask             |                  |                 |        |

|               | •                                    | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 3-2       |                                      | : Mask Source                    | for Filter 9 bit                      |                  |                  |                 |        |

|               | 11 = Reserve                         | nce Mask 2 reg                   | istore contain                        | mask             |                  |                 |        |

|               |                                      | nce Mask 1 reg                   |                                       |                  |                  |                 |        |

|               |                                      | nce Mask 0 reg                   |                                       |                  |                  |                 |        |

| bit 1-0       |                                      | : Mask Source                    |                                       |                  |                  |                 |        |

|               | 11 = Reserve                         | ed; do not use                   |                                       |                  |                  |                 |        |

|               | 10 = Accepta                         | nce Mask 2 reg                   |                                       |                  |                  |                 |        |

|               |                                      |                                  | · · · · · · · · · · · · · · · · · · · |                  |                  |                 |        |

|               |                                      | nce Mask 1 reg<br>nce Mask 0 reg |                                       |                  |                  |                 |        |

#### REGISTER 20-5: RSCON: DCI RECEIVE SLOT CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| RSE15  | RSE14 | RSE13 | RSE12 | RSE11 | RSE10 | RSE9  | RSE8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RSE7  | RSE6  | RSE5  | RSE4  | RSE3  | RSE2  | RSE1  | RSE0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 RSE<15:0>: Receive Slot Enable bits

1 = CSDI data is received during the individual time slot n

0 = CSDI data is ignored during the individual time slot n

#### REGISTER 20-6: TSCON: DCI TRANSMIT SLOT CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| TSE15  | TSE14 | TSE13 | TSE12 | TSE11 | TSE10 | TSE9  | TSE8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TSE7  | TSE6  | TSE5  | TSE4  | TSE3  | TSE2  | TSE1  | TSE0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

TSE<15:0>: Transmit Slot Enable Control bits

1 = Transmit buffer contents are sent during the individual time slot n

0 = CSDO pin is tri-stated or driven to logic '0', during the individual time slot, depending on the state of the CSDOM bit

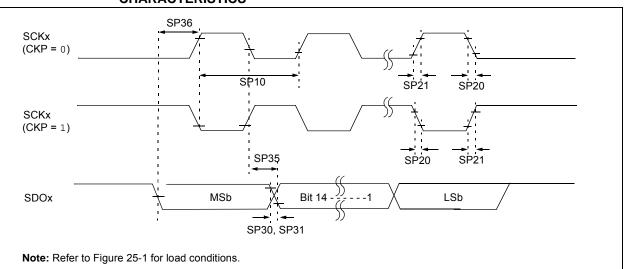

| TABLE 25-29: | : SPIx MASTER MODE (HALF-DUPLEX | (, TRANSMIT ONLY) TIMING REQUIREMENTS |

|--------------|---------------------------------|---------------------------------------|