Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

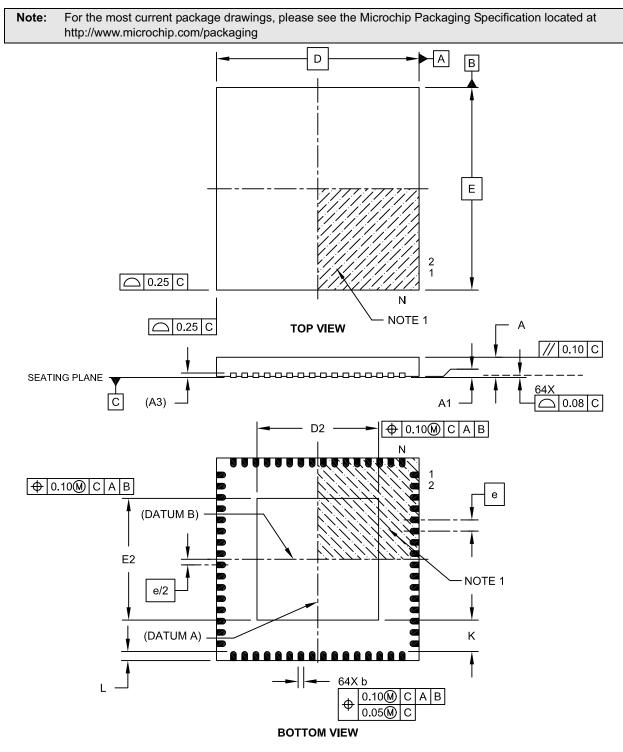

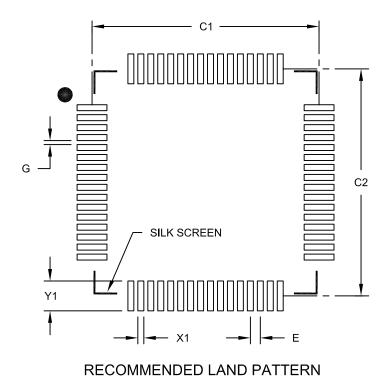

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp510a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                  | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|------------------|----------------------------------------|------------------|-------|-----------------|-------|

|                 |       |                  | PAD                                    | <15:8>           |       |                 |       |

| bit 15          |       |                  |                                        |                  |       |                 | bit 8 |

|                 |       |                  | 5444                                   | 54446            |       | <b>B</b> 111 A  |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                  | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                  | PAI                                    | 0<7:0>           |       |                 |       |

| bit 7           |       |                  |                                        |                  |       |                 | bit 0 |

| Legend:         |       |                  |                                        |                  |       |                 |       |

| R = Readable    | bit   | W = Writable b   | bit U = Unimplemented bit, read as '0' |                  |       |                 |       |

| -n = Value at P | POR   | '1' = Bit is set |                                        | '0' = Bit is cle | ared  | x = Bit is unki | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------------------------|-------|

| —      | _   | —   | —   | —   | —   | CNT<9:8> <sup>(2)</sup> |       |

| bit 15 |     |     |     |     |     |                         | bit 8 |

|        |     |     |     |     |     |                         |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <b>(2)</b> |       |       |       |

| bit 7 |       |       |       |                 |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

#### 10.0 POWER-SAVING FEATURES

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) in "dsPIC33F/PIC24H Familv the Reference Manual", which is available the site from Microchip web (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXGPX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXGPX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXGPX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into SLEEP modePWRSAV#IDLE\_MODE; Put the device into IDLE mode

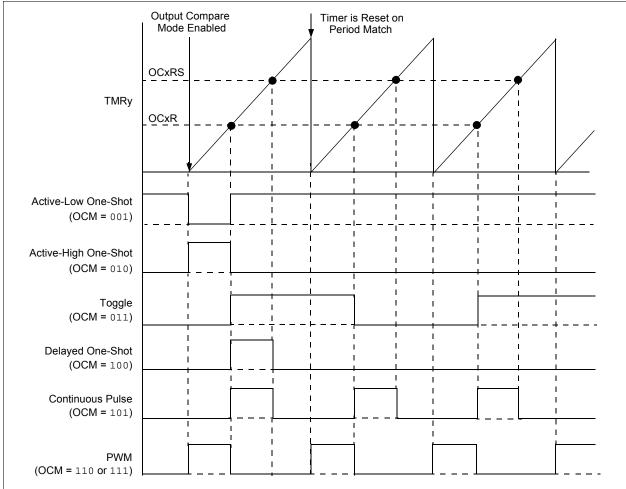

#### 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"      |

|-------|---------------------------------------|

|       | (DS70209) in the "dsPIC33F/PIC24H     |

|       | Family Reference Manual" for OCxR and |

|       | OCxRS register restrictions.          |

| OCM<2:0> | Mode                         | OCx Pin Initial State                            | OCx Interrupt Generation         |  |  |

|----------|------------------------------|--------------------------------------------------|----------------------------------|--|--|

| 000      | Module Disabled              | Controlled by GPIO register                      | _                                |  |  |

| 001      | Active-Low One-Shot          | 0                                                | OCx rising edge                  |  |  |

| 010      | Active-High One-Shot         | 1                                                | OCx falling edge                 |  |  |

| 011      | Toggle                       | Current output is maintained                     | OCx rising and falling edge      |  |  |

| 100      | Delayed One-Shot             | 0                                                | OCx falling edge                 |  |  |

| 101      | Continuous Pulse             | 0                                                | OCx falling edge                 |  |  |

| 110      | PWM without Fault Protection | ʻ0', if OCxR is zero<br>ʻ1', if OCxR is non-zero | No interrupt                     |  |  |

| 111      | PWM with Fault Protection    | ʻ0', if OCxR is zero<br>ʻ1', if OCxR is non-zero | OCFA falling edge for OC1 to OC4 |  |  |

| R/W-0         | U-0                           | R/W-0                                 | R/W-1 HC          | R/W-0            | R/W-0                   | R/W-0              | R/W-0         |

|---------------|-------------------------------|---------------------------------------|-------------------|------------------|-------------------------|--------------------|---------------|

| I2CEN         |                               | I2CSIDL                               | SCLREL            | IPMIEN           | A10M                    | DISSLW             | SMEN          |

| bit 15        |                               |                                       |                   |                  |                         |                    | bit 8         |

|               |                               |                                       |                   |                  |                         |                    |               |

| R/W-0         | R/W-0                         | R/W-0                                 | R/W-0 HC          | R/W-0 HC         | R/W-0 HC                | R/W-0 HC           | R/W-0 HC      |

| GCEN          | STREN                         | ACKDT                                 | ACKEN             | RCEN             | PEN                     | RSEN               | SEN           |

| bit 7         |                               |                                       |                   |                  |                         |                    | bit 0         |

| Legend:       |                               | U = Unimplei                          | nented bit, rea   | d as '0'         |                         |                    |               |

| R = Readable  | e hit                         | W = Writable                          |                   | HS = Set in h    | ardware                 | HC = Cleared       | in hardware   |

| -n = Value at |                               | '1' = Bit is se                       |                   | '0' = Bit is cle |                         | x = Bit is unkr    |               |

|               | TOIN                          |                                       |                   |                  |                         |                    |               |

| bit 15        | <b>12CEN:</b> 12Cx            | Enable bit                            |                   |                  |                         |                    |               |

|               | 1 = Enables t                 | the I2Cx modu                         | le and configur   | es the SDAx a    | and SCLx pins a         | as serial port pir | าร            |

|               |                               |                                       |                   |                  | by port functio         |                    |               |

| bit 14        | Unimplemen                    | ted: Read as                          | ʻ0'               |                  |                         |                    |               |

| bit 13        | I2CSIDL: Sto                  | p in Idle Mode                        | bit               |                  |                         |                    |               |

|               |                               | •                                     | eration when de   |                  | n Idle mode             |                    |               |

|               |                               | -                                     | tion in Idle mod  |                  | 1 <sup>2</sup> 0 1      |                    |               |

| bit 12        |                               |                                       | ontrol bit (when  | operating as     | I <sup>2</sup> C slave) |                    |               |

|               | 1 = Release 3                 | SCLX CIOCK<br>_X Clock low (cl        | ock stretch)      |                  |                         |                    |               |

|               | If STREN = 1                  | •                                     |                   |                  |                         |                    |               |

|               |                               |                                       | y write '0' to in | itiate stretch a | nd write '1' to re      | elease clock). H   | ardware clear |

|               |                               |                                       |                   |                  | d of slave rece         |                    |               |

|               | If STREN = 0                  |                                       |                   |                  |                         |                    |               |

|               | Bit is R/S (i.e transmission. |                                       | y only write '1'  | to release clo   | ck). Hardware c         | lear at beginnin   | g of slave    |

| bit 11        | IPMIEN: Intel                 | lligent Periphe                       | ral Managemer     | nt Interface (IF | MI) Enable bit          |                    |               |

|               | 1 = IPMI mod<br>0 = IPMI mod  |                                       | all addresses A   | cknowledged      |                         |                    |               |

| bit 10        | A10M: 10-bit                  | Slave Address                         | s bit             |                  |                         |                    |               |

|               | 1 = I2CxADD                   | ) is a 10-bit sla                     | ve address        |                  |                         |                    |               |

|               | 0 = I2CxADD                   | ) is a 7-bit slave                    | e address         |                  |                         |                    |               |

| bit 9         |                               | able Slew Rate                        |                   |                  |                         |                    |               |

|               |                               | e control disable<br>e control enable |                   |                  |                         |                    |               |

| bit 8         |                               | us Input Levels                       |                   |                  |                         |                    |               |

|               |                               | -                                     | ds compliant wi   | th SMBus spe     | cification              |                    |               |

|               |                               | SMBus input th                        |                   | ·                |                         |                    |               |

| bit 7         |                               |                                       | e bit (when ope   | •                | ,                       |                    |               |

|               |                               |                                       |                   | ddress is rece   | eived in the I2C        | xRSR               |               |

|               | •                             | is enabled for                        | • •               |                  |                         |                    |               |

| hit C         |                               | call address di                       |                   | han anaratia -   | $a_{12}$                |                    |               |

| bit 6         |                               |                                       | h Enable bit (w   | nen operating    | as I-C slave)           |                    |               |

|               |                               | unction with SC<br>oftware or rece    | VEREL Dit.        | hina             |                         |                    |               |

|               |                               |                                       | eive clock stret  | •                |                         |                    |               |

|               |                               |                                       |                   |                  |                         |                    |               |

| R-0 HSC          | R-0 HSC                                                      | U-0                                                                                | U-0                                                             | U-0                                      | R/C-0 HS                                       | R-0 HSC              | R-0 HSC         |

|------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------|------------------------------------------------|----------------------|-----------------|

| ACKSTAT          | TRSTAT                                                       | _                                                                                  | _                                                               | _                                        | BCL                                            | GCSTAT               | ADD10           |

| bit 15           |                                                              |                                                                                    |                                                                 |                                          |                                                |                      | bit 8           |

|                  |                                                              |                                                                                    |                                                                 |                                          |                                                |                      |                 |

| R/C-0 HS         | R/C-0 HS                                                     | R-0 HSC                                                                            | R/C-0 HSC                                                       | R/C-0 HSC                                | R-0 HSC                                        | R-0 HSC              | R-0 HSC         |

| IWCOL            | I2COV                                                        | D_A                                                                                | Р                                                               | S                                        | R_W                                            | RBF                  | TBF             |

| oit 7            |                                                              |                                                                                    |                                                                 |                                          |                                                |                      | bit (           |

| Legend:          |                                                              | U = Unimpler                                                                       | nented bit, rea                                                 | ad as '0'                                |                                                | C = Clear onl        | y bit           |

| R = Readable     | bit                                                          | W = Writable                                                                       | bit                                                             | HS = Set in h                            | ardware                                        | HSC = Hardwa         | are set/cleared |

| n = Value at I   | POR                                                          | '1' = Bit is set                                                                   | t                                                               | '0' = Bit is cle                         | ared                                           | x = Bit is unkn      | own             |

| bit 15<br>bit 14 | 1 = NACK rec<br>0 = ACK rece<br>Hardware set<br>TRSTAT: Trar | ng as I <sup>2</sup> C mas<br>eived from slav<br>ived from slav<br>or clear at end | iter, applicable<br>ive<br>e<br>d of slave Ack<br>t (when opera | nowledge.<br>ting as I <sup>2</sup> C ma | nsmit operation<br>ster, applicable            | )<br>to master trans | mit operation   |

|                  | 0 = Master tra                                               | ansmit is not in                                                                   | progress                                                        |                                          | ware clear at e                                | nd of slave Ack      | nowledge.       |

| oit 13-11        | Unimplemen                                                   | ted: Read as                                                                       | 0'                                                              |                                          |                                                |                      |                 |

| bit 10           |                                                              | on                                                                                 | n detected dur                                                  | ing a master o                           | peration                                       |                      |                 |

| bit 9            | GCSTAT: Ger                                                  | neral Call Statu                                                                   | us bit                                                          |                                          |                                                |                      |                 |

|                  | 0 = General c                                                | all address wa<br>all address wa<br>when address                                   | as not received                                                 |                                          | ss. Hardware c                                 | lear at Stop det     | ection.         |

| bit 8            | 1 = 10-bit add<br>0 = 10-bit add                             | it Address Sta<br>Iress was mate<br>Iress was not i<br>at match of 2i              | ched<br>matched                                                 | ched 10-bit ad                           | dress. Hardwa                                  | re clear at Stop     | detection.      |

| bit 7            | IWCOL: Write                                                 |                                                                                    |                                                                 |                                          | 0                                              |                      |                 |

|                  | 0 = No collisio                                              | on                                                                                 | -                                                               |                                          | use the I <sup>2</sup> C mo<br>usy (cleared by | -                    |                 |

| bit 6            | I2COV: Recei                                                 | ve Overflow F                                                                      | lag bit                                                         |                                          |                                                |                      |                 |

|                  | 0 = No overflo                                               | ow.                                                                                |                                                                 | -                                        | till holding the<br>V (cleared by s            | -                    |                 |

| bit 5            |                                                              | Idress bit (whe                                                                    |                                                                 | _                                        | , ,                                            | ,                    |                 |

|                  | 0 = Indicates                                                |                                                                                    | /te received w                                                  | as device add                            | ress<br>by reception of                        | slave byte.          |                 |

| bit 4            | P: Stop bit                                                  |                                                                                    |                                                                 |                                          |                                                |                      |                 |

|                  | 1 = Indicates                                                | that a Stop bit                                                                    | has been dete                                                   | ected last                               |                                                |                      |                 |

#### **REGISTER 19-8:** CiEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0 | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                            | R-0                                                                                                                                                                                          |  |

|-----|------------------|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |                  | TERRO                         | CNT<7:0>                                     |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|     |                  |                               |                                              |                                                                                                                                           |                                                                                                | bit 8                                                                                                                                                                                        |  |

|     |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

| R-0 | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                            | R-0                                                                                                                                                                                          |  |

|     |                  | RERRO                         | CNT<7:0>                                     |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|     |                  |                               |                                              |                                                                                                                                           |                                                                                                | bit 0                                                                                                                                                                                        |  |

|     |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|     |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

| bit | W = Writable b   | it                            | U = Unimplement                              | ted bit, rea                                                                                                                              | ad as '0'                                                                                      |                                                                                                                                                                                              |  |

| OR  | '1' = Bit is set |                               | '0' = Bit is cleared x = Bit is unknown      |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|     | R-0              | R-0 R-0<br>bit W = Writable b | R-0 R-0 R-0<br>RERRO<br>bit W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>            bit         W = Writable bit         U = Unimplement | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | R-0         R-0         R-0         R-0         R-0         R-0           Bit         W = Writable bit         U = Unimplemented bit, read as '0'         U = Unimplemented bit, read as '0' |  |

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### **REGISTER 19-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

|               |                    |                                      | 11.0         |                                         |                  |          | 11.0    |

|---------------|--------------------|--------------------------------------|--------------|-----------------------------------------|------------------|----------|---------|

| U-0           | U-0                | U-0                                  | U-0          | U-0                                     | U-0              | U-0      | U-0     |

|               | —                  | —                                    | —            |                                         | —                | —        |         |

| bit 15        |                    |                                      |              |                                         |                  |          | bit 8   |

| 5444          | 5444.0             |                                      | <b>DM/</b> 0 | <b>D</b> 444 A                          | 5444.0           | 5444.0   | D M M A |

| R/W-0         | R/W-0              | R/W-0                                | R/W-0        | R/W-0                                   | R/W-0            | R/W-0    | R/W-0   |

|               | N<1:0>             |                                      |              | BRI                                     | P<5:0>           |          |         |

| bit 7         |                    |                                      |              |                                         |                  |          | bit 0   |

|               |                    |                                      |              |                                         |                  |          |         |

| Legend:       |                    |                                      |              |                                         |                  |          |         |

| R = Readabl   | e bit              | W = Writable                         | bit          | U = Unimpler                            | mented bit, read | l as '0' |         |

| -n = Value at | t POR              | '1' = Bit is set                     |              | '0' = Bit is cleared x = Bit is unknown |                  |          |         |

|               |                    |                                      |              |                                         |                  |          |         |

| bit 15-8      | Unimplemer         | nted: Read as '                      | 0'           |                                         |                  |          |         |

| bit 7-6       | SJW<1:0>: S        | Synchronization                      | Jump Width I | bits                                    |                  |          |         |

|               | 11 = Length        | is 4 x Tq                            |              |                                         |                  |          |         |

|               | 10 = Length        |                                      |              |                                         |                  |          |         |

|               | 01 = Length        |                                      |              |                                         |                  |          |         |

|               | 00 = Length        |                                      |              |                                         |                  |          |         |

| bit 5-0       |                    | Baud Rate Pres                       |              |                                         |                  |          |         |

|               |                    | [q = 2 x 64 x 1/                     | FCAN         |                                         |                  |          |         |

|               | •                  |                                      |              |                                         |                  |          |         |

|               | •                  |                                      |              |                                         |                  |          |         |

|               | •                  |                                      |              |                                         |                  |          |         |

|               |                    | $Q = 2 \times 3 \times 1/F$          |              |                                         |                  |          |         |

|               |                    | 「q = 2 x 2 x 1/F<br>「q = 2 x 1 x 1/F |              |                                         |                  |          |         |

|               | 00 0000 <b>- 1</b> |                                      |              |                                         |                  |          |         |

#### REGISTER 19-12: CiBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0         | R/W-0        | R/W-0                                                         | R/W-0         | R/W-0             | R/W-0            | R/W-0             | R/W-0          |

|---------------|--------------|---------------------------------------------------------------|---------------|-------------------|------------------|-------------------|----------------|

|               | F3BF         | P<3:0>                                                        |               |                   | F2BF             | <b>?&lt;</b> 3:0> |                |

| bit 15        |              |                                                               |               |                   |                  |                   | bit 8          |

|               | 5444.6       |                                                               | 5444          | <b>D</b> 444 A    | 5444.0           | 5444.6            | <b>D</b> 444 A |

| R/W-0         | R/W-0        | R/W-0                                                         | R/W-0         | R/W-0             | R/W-0            | R/W-0             | R/W-0          |

| F1BP<3:0>     |              |                                                               |               |                   | FUBF             | P<3:0>            | bit (          |

|               |              |                                                               |               |                   |                  |                   | Dit t          |

| Legend:       |              |                                                               |               |                   |                  |                   |                |

| R = Readable  | e bit        | W = Writable                                                  | bit           | U = Unimplen      | nented bit, read | d as '0'          |                |

| -n = Value at | POR          | '1' = Bit is set                                              |               | '0' = Bit is clea | ared             | x = Bit is unkn   | iown           |

| bit 15-12     | 1111 = Filte | RX Buffer Writte<br>r hits received in<br>r hits received in  | RX FIFO bu    | ffer              |                  |                   |                |

|               | •            |                                                               |               |                   |                  |                   |                |

|               |              | r hits received in<br>r hits received in                      |               |                   |                  |                   |                |

| bit 11-8      | 1111 = Filte | RX Buffer Writter<br>r hits received in<br>r hits received in | RX FIFO bu    | ffer              |                  |                   |                |

|               | •            |                                                               |               |                   |                  |                   |                |

|               |              | r hits received in<br>r hits received in                      |               |                   |                  |                   |                |

| bit 7-4       | 1111 = Filte | RX Buffer Writter<br>r hits received in<br>r hits received in | RX FIFO bu    | ffer              |                  |                   |                |

|               | •            |                                                               |               |                   |                  |                   |                |

|               |              | r hits received in<br>r hits received in                      |               |                   |                  |                   |                |

| bit 3-0       | F0BP<3:0>:   | RX Buffer Writte                                              | en when Filte | er 0 Hits bits    |                  |                   |                |

|               |              | r hits received in<br>r hits received in                      |               | -                 |                  |                   |                |

|               | •            |                                                               |               |                   |                  |                   |                |

|               | •            |                                                               |               |                   |                  |                   |                |

|               |              | r hits received in<br>r hits received in                      |               |                   |                  |                   |                |

| R/W-0              | U-0                                                                                                                                   | R/W-0                                                                                                      | U-0      | R/W-0            | R/W-0              | R/W-0           | R/W-0      |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------|------------------|--------------------|-----------------|------------|--|--|--|--|

| DCIEN              |                                                                                                                                       | DCISIDL                                                                                                    |          | DLOOP            | CSCKD              | CSCKE           | COFSD      |  |  |  |  |

| bit 15             |                                                                                                                                       |                                                                                                            |          |                  |                    | -               | bit 8      |  |  |  |  |

|                    |                                                                                                                                       |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| R/W-0              | R/W-0                                                                                                                                 | R/W-0                                                                                                      | U-0      | U-0              | U-0                | R/W-0           | R/W-0      |  |  |  |  |

| UNFM               | CSDOM                                                                                                                                 | DJST                                                                                                       |          | _                |                    | COFS            | COFSM<1:0> |  |  |  |  |

| bit 7              |                                                                                                                                       |                                                                                                            |          |                  |                    |                 | bit 0      |  |  |  |  |

| Legend:            |                                                                                                                                       |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| R = Readable       | e hit                                                                                                                                 | W = Writable                                                                                               | hit      | LI = LInimpler   | mented bit, read   | 1 as '0'        |            |  |  |  |  |

| -n = Value at      |                                                                                                                                       | '1' = Bit is set                                                                                           |          | '0' = Bit is cle |                    | x = Bit is unkr | nown       |  |  |  |  |

| n value at         |                                                                                                                                       |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 15             | DCIEN: DCI                                                                                                                            | Module Enable                                                                                              | bit      |                  |                    |                 |            |  |  |  |  |

|                    | 1 = Module is                                                                                                                         | 1 = Module is enabled                                                                                      |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | 0 = Module is disabled                                                                                     |          |                  |                    |                 |            |  |  |  |  |

| bit 14             | -                                                                                                                                     | nted: Read as '                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 13             |                                                                                                                                       | CI Stop in Idle C                                                                                          |          |                  |                    |                 |            |  |  |  |  |

|                    | <ol> <li>Module will halt in CPU Idle mode</li> <li>Module will continue to operate in CPU Idle mode</li> </ol>                       |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 12             | Unimplemented: Read as '0'                                                                                                            |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 11             | <b>DLOOP:</b> Digital Loopback Mode Control bit                                                                                       |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | 1 = Digital Loopback mode is enabled. CSDI and CSDO pins internally connected                              |          |                  |                    |                 |            |  |  |  |  |

|                    | •                                                                                                                                     | 0 = Digital Loopback mode is disabled                                                                      |          |                  |                    |                 |            |  |  |  |  |

| bit 10             |                                                                                                                                       | CSCKD: Sample Clock Direction Control bit                                                                  |          |                  |                    |                 |            |  |  |  |  |

|                    | <ol> <li>1 = CSCK pin is an input when DCI module is enabled</li> <li>0 = CSCK pin is an output when DCI module is enabled</li> </ol> |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 9              | CSCKE: Sample Clock Edge Control bit                                                                                                  |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | 1 = Data changes on serial clock falling edge, sampled on serial clock rising edge                         |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | 0 = Data changes on serial clock rising edge, sampled on serial clock falling edge                         |          |                  |                    |                 |            |  |  |  |  |

| bit 8              |                                                                                                                                       | COFSD: Frame Synchronization Direction Control bit                                                         |          |                  |                    |                 |            |  |  |  |  |

|                    | 1 = COFS pin is an input when DCI module is enabled                                                                                   |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 7              | -                                                                                                                                     | <ul> <li>0 = COFS pin is an output when DCI module is enabled</li> <li>UNFM: Underflow Mode bit</li> </ul> |          |                  |                    |                 |            |  |  |  |  |

| bit i              | •••••••••                                                                                                                             | 1 = Transmit last value written to the transmit registers on a transmit underflow                          |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | ʻ0 <b>'s on a trans</b> n                                                                                  |          |                  |                    |                 |            |  |  |  |  |

| bit 6              | CSDOM: Serial Data Output Mode bit                                                                                                    |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | n will be tri-state<br>n drives '0's dur                                                                   |          |                  |                    |                 |            |  |  |  |  |

| bit 5              | <ul> <li>0 = CSDO pin drives '0's during disabled transmit time slots</li> <li>DJST: DCI Data Justification Control bit</li> </ul>    |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    | 1 = Data transmission/reception is begun during the same serial clock cycle as the frame                                              |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    | synchronization pulse<br>0 = Data transmission/reception is begun one serial clock cycle after frame synchronization pulse            |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

| bit 4-2            |                                                                                                                                       | -                                                                                                          | -        | TONE SENALCIO    | ok cycle alter fra | ame synchroniz  | auon puise |  |  |  |  |

| bit 4-2<br>bit 1-0 | Unimplemented: Read as '0'                                                                                                            |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    | COFSM<1:0>: Frame Sync Mode bits<br>11 = 20-bit AC-Link mode                                                                          |                                                                                                            |          |                  |                    |                 |            |  |  |  |  |

|                    | 10 <b>= 16-bit</b> A                                                                                                                  | C-Link mode                                                                                                |          |                  |                    |                 |            |  |  |  |  |

|                    |                                                                                                                                       | 01 = I <sup>2</sup> S Frame Sync mode<br>00 = Multi-Channel Frame Sync mode                                |          |                  |                    |                 |            |  |  |  |  |

|                    | 00 = Multi-Ch                                                                                                                         | nannel Frame S                                                                                             | ync mode |                  |                    |                 |            |  |  |  |  |

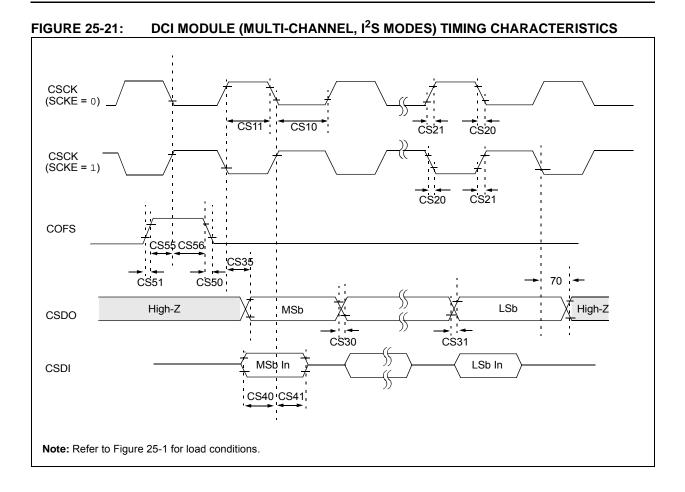

#### REGISTER 20-1: DCICON1: DCI CONTROL REGISTER 1

#### **REGISTER 21-1:** ADxCON1: ADCx CONTROL REGISTER 1 (where x = 1 or 2) (CONTINUED)

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or $1x$ )                                                                                                                                                                                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or     Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                   |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                               |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                     |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software may write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software may write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>      |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>1 = ADC conversion cycle is completed</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when ADC conversion is complete. Software may write '0' to clear</li> <li>DONE status (software not allowed to write '1'). Clearing this bit will NOT affect any operation in progress. Automatically cleared by hardware at start of a new conversion.</li> </ul> |

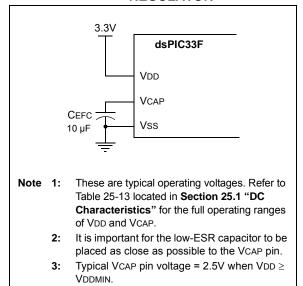

#### 22.2 On-Chip Voltage Regulator

All of the dsPIC33FJXXXGPX06A/X08A/X10A devices power their core digital logic at a nominal 2.5V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJXXXGPX06A/X08A/X10A family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. The regulator requires that a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) be connected to the VCAP pin (Figure 22-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 25-13 of **Section 25.0** "**Electrical Characteristics**".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 22-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 22.3 BOR: Brown-out Reset

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

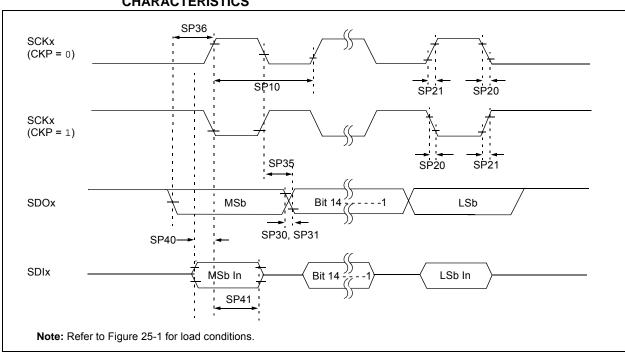

### FIGURE 25-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

### TABLE 25-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP10               | TscP                  | Maximum SCK Frequency                         | —                                                                                                                                                                                                                                                                                       | _                  | 10  | MHz   | See Note 3                           |  |

| SP20               | TscF                  | SCKx Output Fall Time                         | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP21               | TscR                  | SCKx Output Rise Time                         | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —                                                                                                                                                                                                                                                                                       | 6                  | 20  | ns    | —                                    |  |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | —                  |     | ns    | _                                    |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                                                                                                                      | _                  |     | ns    | _                                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | —                  | -   | ns    | —                                    |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

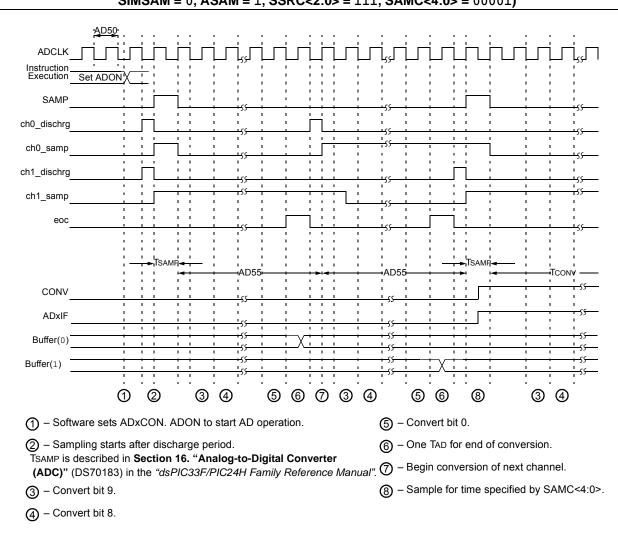

### FIGURE 25-26:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

#### 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters for high temperature devices. However, all AC timing specifications in this section are the same as those in Section 25.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter OS53 in Section 25.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

#### TABLE 26-7: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

|                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$                  |

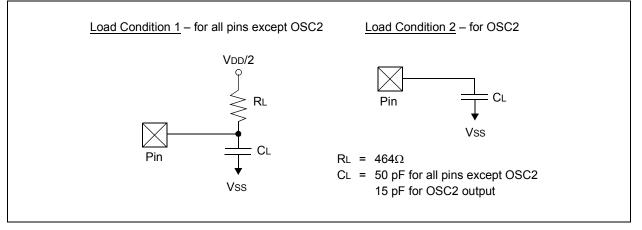

#### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-8: PLL CLOCK TIMING SPECIFICATIONS

| AC<br>CHARACTERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |                             |  |

|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|-----------------------------|--|

| Param<br>No. Symbol   |      | Characteristic                                                                                                                                          | Min | Тур | Max | Units | Conditions                  |  |

| HOS53                 | DCLK | CLKO Stability (Jitter) <sup>(1)</sup>                                                                                                                  | -5  | 0.5 | 5   | %     | Measured over 100 ms period |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

NOTES:

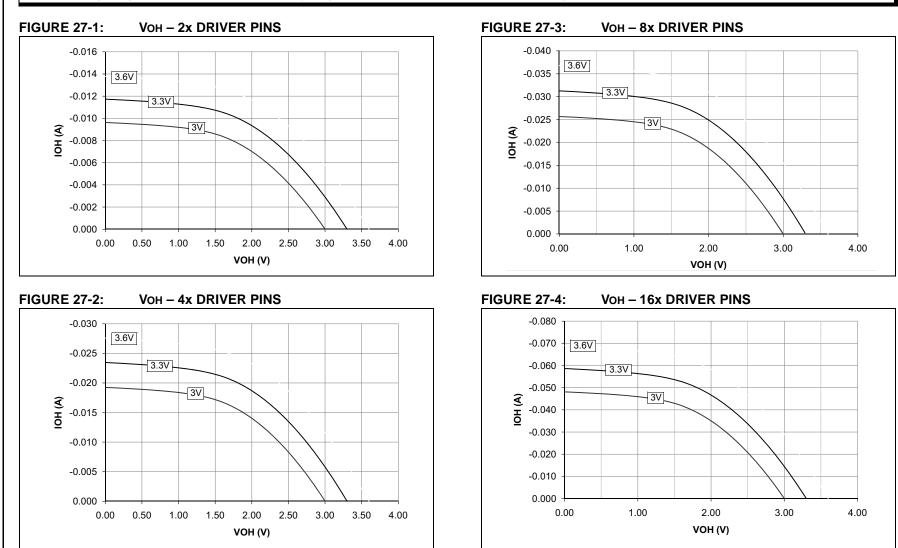

### 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS