Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 30K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp710a-h-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

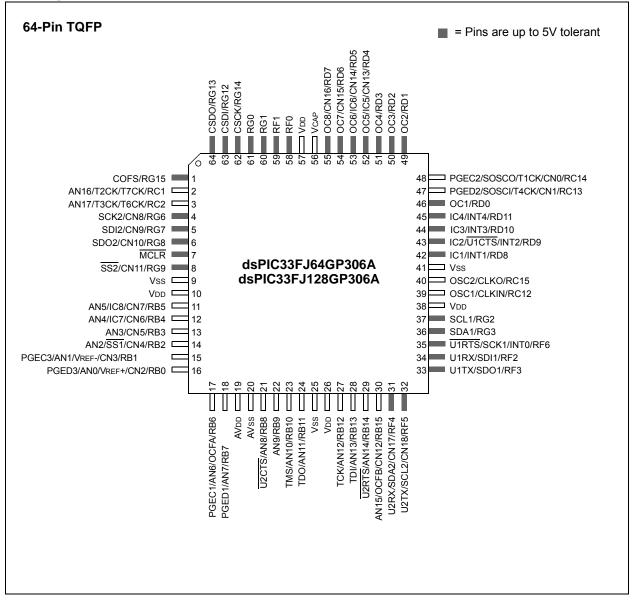

## Pin Diagrams (Continued)

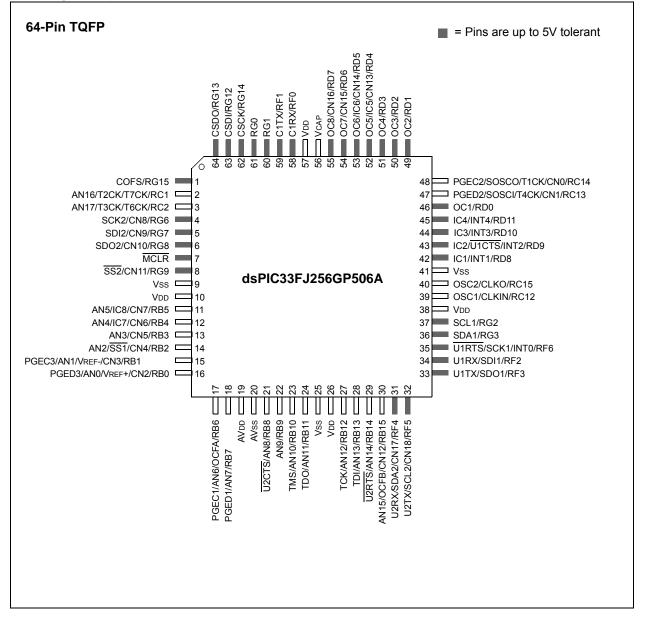

## Pin Diagrams (Continued)

# 5.0 FLASH PROGRAM MEMORY

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and

Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

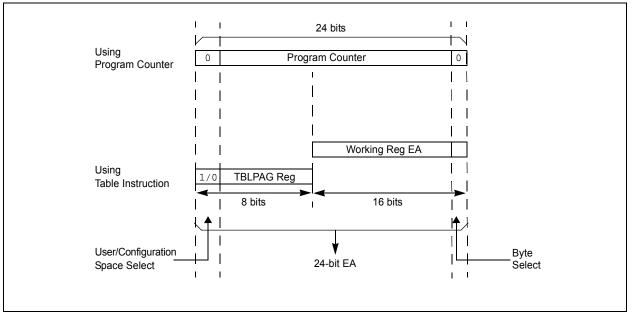

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| R/W-0                  | U-0                    | U-0                    | U-0                    | U-0             | U-0                         | U-0                | U-0        |

|------------------------|------------------------|------------------------|------------------------|-----------------|-----------------------------|--------------------|------------|

| FORCE <sup>(1)</sup>   | —                      | —                      | -                      | —               | —                           | —                  | —          |

| bit 15                 |                        |                        |                        |                 |                             |                    | bit 8      |

|                        |                        |                        |                        |                 |                             |                    |            |

| U-0                    | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0           | R/W-0                       | R/W-0              | R/W-0      |

| —                      | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2)      | IRQSEL2 <sup>(2)</sup>      | IRQSEL1(2)         | IRQSEL0(2) |

| bit 7                  |                        |                        |                        |                 |                             |                    | bit 0      |

|                        |                        |                        |                        |                 |                             |                    |            |

| Legend:                |                        |                        |                        |                 |                             |                    |            |

| R = Readable bit W = V |                        | W = Writable           | / = Writable bit       |                 | U = Unimplemented bit, read |                    |            |

| -n = Value at F        | POR                    | '1' = Bit is set       | et '0' = Bit           |                 | ared                        | x = Bit is unknown |            |

|                        |                        |                        |                        |                 |                             |                    |            |

| bit 15                 | FORCE: Force           | e DMA Transfe          | er bit <sup>(1)</sup>  |                 |                             |                    |            |

|                        |                        | ingle DMA tran         |                        | ,               |                             |                    |            |

|                        |                        | DMA transfer           | -                      | MA request      |                             |                    |            |

| bit 14-7               | Unimplemen             | ted: Read as '         | 0'                     |                 |                             |                    |            |

| bit 6-0                | IRQSEL<6:0>            | DMA Periph             | eral IRQ Numl          | ber Select bits | (2)                         |                    |            |

|                        | 1111111 <b>= D</b>     | MAIRQ127 se            | lected to be C         | hannel DMARI    | EQ                          |                    |            |

|                        | •                      |                        |                        |                 |                             |                    |            |

|                        | •                      |                        |                        |                 |                             |                    |            |

|                        | •                      |                        |                        |                 |                             |                    |            |

|                        | 0000000 = DN           | MAIRQ0 select          | ed to be Chan          | nel DMAREQ      |                             |                    |            |

|                        |                        |                        |                        |                 |                             |                    |            |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

- 2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0                  | R/W-0 |

|-----------------|-------|------------------|-------|------------------------------------|-------|------------------------|-------|

|                 |       |                  | STA   | <15:8>                             |       |                        |       |

| bit 15          |       |                  |       |                                    |       |                        | bit 8 |

|                 |       |                  |       |                                    |       |                        |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0                  | R/W-0 |

|                 |       |                  | ST/   | \<7:0>                             |       |                        |       |

| bit 7           |       |                  |       |                                    |       |                        | bit 0 |

|                 |       |                  |       |                                    |       |                        |       |

| Legend:         |       |                  |       |                                    |       |                        |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplemented bit, read as '0' |       |                        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | red x = Bit is unknown |       |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                 |       |                  | STB   | <15:8>                             |       |                 |       |

| bit 15          |       |                  |       |                                    |       |                 | bit 8 |

|                 |       |                  |       |                                    |       |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>                             |       |                 |       |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |

|                 |       |                  |       |                                    |       |                 |       |

| Legend:         |       |                  |       |                                    |       |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

|                 |       |                  |       |                                    |       |                 |       |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

## REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit |

|-------|----------------------------------------------------|

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

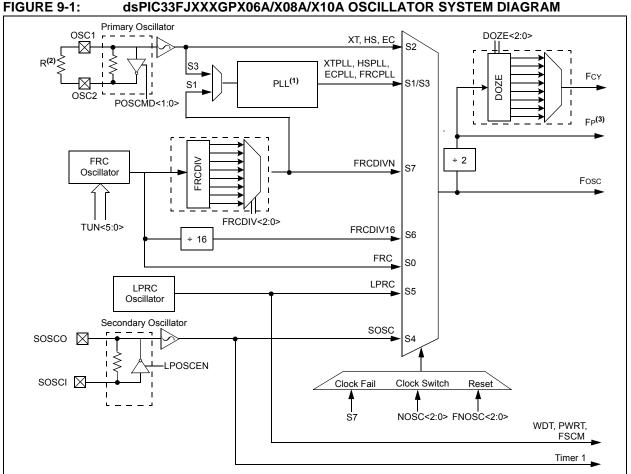

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, not intended to it is be а comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

A simplified diagram of the oscillator system is shown in Figure 9-1.

Note 1: See Figure 9-2 for PLL details.

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 M $\Omega$  must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while Fcy refers to the clock source for the CPU. Throughout this document FP and Fcy are used interchangeably, except in the case of Doze mode. FP and Fcy will be different when Doze mode is used in any ratio other than 1:1, which is the default.

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | U-0              | U-0            | R/W-0                |

|---------------|---------------------------------|---------------------------------------|---------|-------------------|------------------|----------------|----------------------|

| T5MD          | T4MD                            | T3MD                                  | T2MD    | T1MD              |                  | _              | DCIMD                |

| bit 15        |                                 |                                       |         |                   |                  |                | bit 8                |

|               |                                 |                                       |         |                   |                  |                |                      |

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | R/W-0            | R/W-0          | R/W-0                |

| I2C1MD        | U2MD                            | U1MD                                  | SPI2MD  | SPI1MD            | C2MD             | C1MD           | AD1MD <sup>(1)</sup> |

| bit 7         |                                 |                                       |         |                   |                  |                | bit                  |

| Legend:       |                                 |                                       |         |                   |                  |                |                      |

| R = Readabl   | e bit                           | W = Writable                          | bit     | U = Unimplen      | nented bit, read | d as '0'       |                      |

| -n = Value at | POR                             | '1' = Bit is set                      |         | '0' = Bit is clea |                  | x = Bit is unk | nown                 |

|               |                                 |                                       |         |                   |                  |                |                      |

| bit 15        | T5MD: Timer                     | 5 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 14        | T4MD: Timer                     | 4 Module Disat                        | ole bit |                   |                  |                |                      |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 13        |                                 | 3 Module Disat                        |         |                   |                  |                |                      |

|               | 1 = Timer3 m                    | nodule is disable                     | ed      |                   |                  |                |                      |

|               | 0 = Timer3 m                    | nodule is enable                      | d       |                   |                  |                |                      |

| bit 12        | -                               | 2 Module Disat                        |         |                   |                  |                |                      |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 11        | T1MD: Timer                     | 1 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 10-9      | Unimplemer                      | ted: Read as '                        | כ'      |                   |                  |                |                      |

| bit 8         | DCIMD: DCI                      | Module Disable                        | e bit   |                   |                  |                |                      |

|               |                                 | ule is disabled<br>ule is enabled     |         |                   |                  |                |                      |

| bit 7         | <b>I2C1MD:</b> I <sup>2</sup> C | 1 Module Disab                        | le bit  |                   |                  |                |                      |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

| bit 6         |                                 | T2 Module Disa                        | ble bit |                   |                  |                |                      |

|               | -                               | nodule is disabl<br>nodule is enable  |         |                   |                  |                |                      |

| bit 5         |                                 | T1 Module Disa                        |         |                   |                  |                |                      |

|               |                                 | nodule is disabl                      |         |                   |                  |                |                      |

|               | 0 = UART1 n                     | nodule is enable                      | ed      |                   |                  |                |                      |

| bit 4         | SPI2MD: SP                      | I2 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                 | dule is disabled                      |         |                   |                  |                |                      |

|               |                                 | dule is enabled                       |         |                   |                  |                |                      |

| bit 3         |                                 | 11 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

# 11.0 I/O PORTS

- This data sheet summarizes the features Note 1: of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in "dsPIC33F/PIC24H the Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

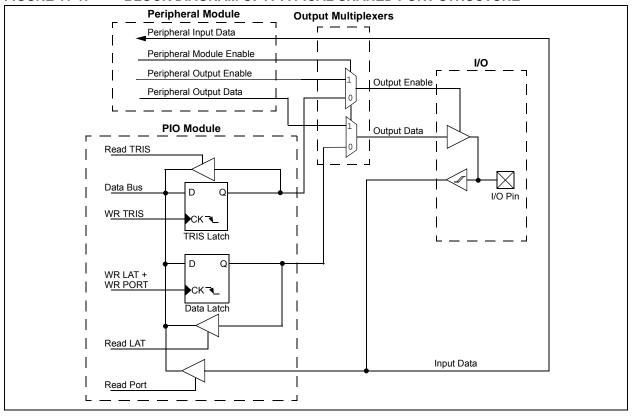

## 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

© 2009-2012 Microchip Technology Inc.

| REGISTER      | 12-1: T1CO                                            | N: TIMER1 C                 | ONTROL R        | EGISTER                 |                  |                 |       |

|---------------|-------------------------------------------------------|-----------------------------|-----------------|-------------------------|------------------|-----------------|-------|

| R/W-0         | U-0                                                   | R/W-0                       | U-0             | U-0                     | U-0              | U-0             | U-0   |

| TON           |                                                       | TSIDL                       | —               | _                       | —                | —               | _     |

| bit 15        |                                                       |                             |                 |                         |                  |                 | bit 8 |

|               |                                                       |                             |                 |                         |                  |                 |       |

| U-0           | R/W-0                                                 | R/W-0                       | R/W-0           | U-0                     | R/W-0            | R/W-0           | U-0   |

|               | TGATE                                                 | TCKP                        | S<1:0>          |                         | TSYNC            | TCS             | _     |

| bit 7         |                                                       |                             |                 |                         |                  |                 | bit 0 |

| <del></del>   |                                                       |                             |                 |                         |                  |                 |       |

| Legend:       |                                                       |                             |                 |                         |                  | 1               |       |

| R = Readabl   |                                                       | W = Writable                |                 |                         | mented bit, read |                 |       |

| -n = Value at | POR                                                   | '1' = Bit is set            |                 | '0' = Bit is cle        | eared            | x = Bit is unkn | own   |

| bit 15        | <b>TON:</b> Timer1<br>1 = Starts 16-<br>0 = Stops 16- | bit Timer1                  |                 |                         |                  |                 |       |

| bit 14        | -                                                     | ited: Read as '             | 0'              |                         |                  |                 |       |

| bit 13        | -                                                     | in Idle Mode bi             |                 |                         |                  |                 |       |

|               | 1 = Discontin                                         |                             | ration when     | device enters lo<br>ode | lle mode         |                 |       |

| bit 12-7      | Unimplemen                                            | ted: Read as '              | 0'              |                         |                  |                 |       |

| bit 6         | TGATE: Time                                           | er1 Gated Time              | Accumulatio     | n Enable bit            |                  |                 |       |

|               | When TCS =                                            |                             |                 |                         |                  |                 |       |

|               | This bit is ign                                       |                             |                 |                         |                  |                 |       |

|               | <u>When TCS =</u><br>1 = Gated times                  | <u>0:</u><br>ne accumulatio | n enabled       |                         |                  |                 |       |

|               |                                                       | ne accumulatio              |                 |                         |                  |                 |       |

| bit 5-4       | TCKPS<1:0>                                            | : Timer1 Input              | Clock Presca    | ale Select bits         |                  |                 |       |

|               | 11 <b>= 1:256</b>                                     |                             |                 |                         |                  |                 |       |

|               | 10 = 1:64                                             |                             |                 |                         |                  |                 |       |

|               | 01 = 1:8<br>00 = 1:1                                  |                             |                 |                         |                  |                 |       |

| bit 3         | Unimplemen                                            | ted: Read as '              | 0'              |                         |                  |                 |       |

| bit 2         | TSYNC: Time                                           | er1 External Cl             | ock Input Syr   | hchronization S         | elect bit        |                 |       |

|               | When TCS =                                            |                             |                 |                         |                  |                 |       |

|               |                                                       | ize external clo            |                 |                         |                  |                 |       |

|               | 0 = Do not sy<br>When TCS =                           | nchronize exte              | ernal clock inp | but                     |                  |                 |       |

|               | This bit is ign                                       |                             |                 |                         |                  |                 |       |

| bit 1         | -                                                     | Clock Source                | Select bit      |                         |                  |                 |       |

|               |                                                       | clock from pin              |                 | rising edge)            |                  |                 |       |

|               | 0 = Internal c                                        |                             |                 |                         |                  |                 |       |

| bit 0         | Unimplemen                                            | ted: Read as '              | 0'              |                         |                  |                 |       |

|               |                                                       |                             |                 |                         |                  |                 |       |

# 14.1 Input Capture Registers

### REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0                  | U-0                                                                                                                                                               | R/W-0                            | U-0              | U-0               | U-0             | U-0              | U-0   |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------|-----------------|------------------|-------|--|--|--|--|

| —                    | —                                                                                                                                                                 | ICSIDL                           | _                | _                 | —               | —                | _     |  |  |  |  |

| bit 15               |                                                                                                                                                                   |                                  |                  |                   |                 |                  | bit 8 |  |  |  |  |

|                      |                                                                                                                                                                   |                                  |                  |                   |                 |                  |       |  |  |  |  |

| R/W-0                | R/W-0                                                                                                                                                             | R/W-0                            | R-0, HC          | R-0, HC           | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |

| ICTMR <sup>(1)</sup> | ICI                                                                                                                                                               | <1:0>                            | ICOV             | ICBNE             |                 | ICM<2:0>         |       |  |  |  |  |

| bit 7                |                                                                                                                                                                   |                                  |                  |                   |                 |                  | bit ( |  |  |  |  |

| Legend:              |                                                                                                                                                                   |                                  |                  |                   |                 |                  |       |  |  |  |  |

| R = Readable         | bit                                                                                                                                                               | W = Writable                     | bit              | U = Unimpler      | mented bit, rea | d as '0'         |       |  |  |  |  |

| -n = Value at F      | POR                                                                                                                                                               | '1' = Bit is set                 |                  | '0' = Bit is cle  | ared            | x = Bit is unkn  | own   |  |  |  |  |

|                      |                                                                                                                                                                   |                                  |                  |                   |                 |                  |       |  |  |  |  |

| bit 15-14            | Unimplemer                                                                                                                                                        | nted: Read as '                  | 0'               |                   |                 |                  |       |  |  |  |  |

| bit 13               | ICSIDL: Inpu                                                                                                                                                      | t Capture Mod                    | ule Stop in Idle | e Control bit     |                 |                  |       |  |  |  |  |

|                      |                                                                                                                                                                   | ture module wi                   |                  |                   |                 |                  |       |  |  |  |  |

|                      |                                                                                                                                                                   | ture module wi                   |                  | operate in CPU    | I Idle mode     |                  |       |  |  |  |  |

| bit 12-8             | -                                                                                                                                                                 | nted: Read as '                  |                  |                   |                 |                  |       |  |  |  |  |

| bit 7                | ICTMR: Input Capture Timer Select bits <sup>(1)</sup><br>1 = TMR2 contents are captured on capture event                                                          |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      |                                                                                                                                                                   | intents are capt                 |                  |                   |                 |                  |       |  |  |  |  |

| oit 6-5              | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                            |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      | 11 = Interrupt on every fourth capture event                                                                                                                      |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      | 10 = Interrupt on every third capture event                                                                                                                       |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      | <ul> <li>01 = Interrupt on every second capture event</li> <li>00 = Interrupt on every capture event</li> </ul>                                                   |                                  |                  |                   |                 |                  |       |  |  |  |  |

| bit 4                | -                                                                                                                                                                 |                                  |                  | i bit (read-only) |                 |                  |       |  |  |  |  |

|                      | ICOV: Input Capture Overflow Status Flag bit (read-only)<br>1 = Input capture overflow occurred                                                                   |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      | 0 = No input capture overflow occurred                                                                                                                            |                                  |                  |                   |                 |                  |       |  |  |  |  |

| bit 3                | •                                                                                                                                                                 | t Capture Buffe                  | 1,2              | . ,               | ,               |                  |       |  |  |  |  |

|                      | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                 |                                  |                  |                   |                 |                  |       |  |  |  |  |

| h ii 0 0             |                                                                                                                                                                   |                                  | . ,              | _                 |                 |                  |       |  |  |  |  |

| bit 2-0              |                                                                                                                                                                   | put Capture M                    |                  |                   | dovice is in SI | oon or Idlo mode | ,     |  |  |  |  |

|                      | 111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br>(Rising edge detect only, all other control bits are not applicable.) |                                  |                  |                   |                 |                  |       |  |  |  |  |

|                      | 110 = Unuse                                                                                                                                                       | d (module disa                   | bled)            |                   |                 | ,                |       |  |  |  |  |

|                      |                                                                                                                                                                   | re mode, every                   |                  |                   |                 |                  |       |  |  |  |  |

|                      | •                                                                                                                                                                 | re mode, every<br>re mode, every |                  | e                 |                 |                  |       |  |  |  |  |

|                      |                                                                                                                                                                   | re mode, every                   |                  |                   |                 |                  |       |  |  |  |  |

|                      | 001 = Captur                                                                                                                                                      | re mode, every                   | edge (rising a   |                   |                 |                  |       |  |  |  |  |

|                      |                                                                                                                                                                   | :0> bits do not                  |                  | pt generation     | for this mode.) |                  |       |  |  |  |  |

|                      | 000 = input c                                                                                                                                                     | capture module                   | turnea oπ        |                   |                 |                  |       |  |  |  |  |

# 18.3 UART Control Registers

### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                          | R/W-0                                             | R/W-0                         | R/W-0                                   | U-0                                                             | R/W-0             | R/W-0           |

|-----------------------|------------------------------|---------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------------------------------|-------------------|-----------------|

| UARTEN <sup>(1)</sup> | _                            | USIDL                                             | IREN <sup>(2)</sup>           | RTSMD                                   | —                                                               | UEN               | <1:0>           |

| bit 15                |                              |                                                   |                               | ·                                       |                                                                 |                   | bit 8           |

|                       |                              |                                                   |                               |                                         |                                                                 |                   |                 |

| R/W-0 HC              | R/W-0                        | R/W-0 HC                                          | R/W-0                         | R/W-0                                   | R/W-0                                                           | R/W-0             | R/W-0           |

| WAKE                  | LPBACK                       | ABAUD                                             | URXINV                        | BRGH                                    | PDSEL                                                           | _<1:0>            | STSEL           |

| bit 7                 |                              |                                                   |                               |                                         |                                                                 |                   | bit 0           |

|                       |                              |                                                   |                               |                                         |                                                                 |                   |                 |

| Legend:               |                              | HC = Hardwa                                       |                               |                                         |                                                                 |                   |                 |

| R = Readable b        |                              | W = Writable                                      | bit                           | -                                       | mented bit, read                                                | as '0'            |                 |

| -n = Value at P       | OR                           | '1' = Bit is set                                  |                               | '0' = Bit is cle                        | ared                                                            | x = Bit is unkr   | nown            |

| bit 15                | 1 = UARTx is                 |                                                   | ARTx pins are                 |                                         | UARTx as defir<br>port latches; U                               |                   |                 |

| bit 14                | Unimplemen                   | ted: Read as '                                    | )'                            |                                         |                                                                 |                   |                 |

| bit 13                | USIDL: Stop i                | n Idle Mode bit                                   |                               |                                         |                                                                 |                   |                 |

|                       |                              | ue module ope<br>module operat                    |                               |                                         | dle mode                                                        |                   |                 |

| bit 12                |                              | Encoder and D                                     |                               | e bit <sup>(2)</sup>                    |                                                                 |                   |                 |

|                       |                              | coder and deco                                    |                               |                                         |                                                                 |                   |                 |

| bit 11                |                              | e Selection for                                   |                               | it                                      |                                                                 |                   |                 |

|                       |                              | in in Simplex m<br>in in Flow Cont                |                               |                                         |                                                                 |                   |                 |

| bit 10                | Unimplemen                   | ted: Read as '                                    | )'                            |                                         |                                                                 |                   |                 |

| bit 9-8               |                              | ARTx Pin Enat                                     |                               |                                         |                                                                 |                   |                 |

|                       | 10 = UxTX, U<br>01 = UxTX, U | xRX, UxCTS a<br>xRX and UxRT<br>d UxRX pins a     | nd UxRTS pir<br>S pins are en | ns are enabled<br>abled an <u>d use</u> | ; UxCTS pin col<br>and used<br>d; UxCTS pin co<br>S and UxRTS/B | ontrolled by po   | rt latches      |

| bit 7                 | WAKE: Wake                   | -up on Start bit                                  | Detect During                 | g Sleep Mode                            | Enable bit                                                      |                   |                 |

|                       |                              | are on following                                  | -                             | RX pin; interru                         | ipt generated or                                                | n falling edge; l | bit cleared     |

| bit 6                 |                              | RTx Loopback                                      | Mode Select                   | hit                                     |                                                                 |                   |                 |

| 2.1.0                 |                              | popback mode                                      |                               |                                         |                                                                 |                   |                 |

|                       |                              | mode is disat                                     | oled                          |                                         |                                                                 |                   |                 |

| bit 5                 | ABAUD: Auto                  | -Baud Enable                                      | bit                           |                                         |                                                                 |                   |                 |

|                       | before ot                    | aud rate meas<br>her data; cleare<br>e measuremen | ed in hardwar                 | e upon comple                           | ter - requires re<br>tion                                       | ception of a S    | ync field (55h) |

| Note 1: Refe          | er to Section 1              |                                                   |                               | -                                       |                                                                 |                   |                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

| R/W-x            | R/W-x        | R/W-x                                                        | R/W-x          | R/W-x                | R/W-x              | R/W-x              | R/W-x            |

|------------------|--------------|--------------------------------------------------------------|----------------|----------------------|--------------------|--------------------|------------------|

|                  |              |                                                              | SID            | <10:3>               |                    |                    |                  |

| bit 15           |              |                                                              |                |                      |                    |                    | bit 8            |

|                  |              |                                                              |                |                      |                    |                    |                  |

| R/W-x            | R/W-x        | R/W-x                                                        | U-0            | R/W-x                | U-0                | R/W-x              | R/W-x            |

|                  | SID<2:0>     |                                                              |                | MIDE                 |                    | EID<1              | 7:16>            |

| bit 7            |              |                                                              |                |                      |                    |                    | bit C            |

| Legend:          |              |                                                              |                |                      |                    |                    |                  |

| R = Readable bit |              | W = Writable t                                               | oit            | U = Unimpler         | mented bit, read   | d as '0'           |                  |

| -n = Value at    | POR          | '1' = Bit is set                                             |                | '0' = Bit is cleared |                    | x = Bit is unknown |                  |

|                  |              |                                                              |                |                      |                    |                    |                  |

| bit 15-5         | SID<10:0>:   | Standard Identif                                             | ier bits       |                      |                    |                    |                  |

|                  | 1 = Include  | bit SIDx in filter c                                         | omparison      |                      |                    |                    |                  |

|                  | 0 = Bit SIDx | is don't care in fi                                          | ilter comparis | son                  |                    |                    |                  |

| bit 4            | Unimpleme    | nted: Read as '0                                             | )'             |                      |                    |                    |                  |

| bit 3            | MIDE: Iden   | tifier Receive Mo                                            | de bit         |                      |                    |                    |                  |

|                  | 0 = Match e  | only message typ<br>either standard or<br>(Filter SID) = (Me | extended a     | ddress messag        | e if filters match | י.<br>ו            | DE bit in filter |

| bit 2            | Unimpleme    | nted: Read as 'o                                             | )'             |                      |                    |                    |                  |

| bit 1-0          | EID<17:16>   | : Extended Ident                                             | ifier bits     |                      |                    |                    |                  |

|                  | 1 = Include  | bit EIDx in filter of                                        | comparison     |                      |                    |                    |                  |

### REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x                              | R/W-x | R/W-x | R/W-x                              | R/W-x  | R/W-x              | R/W-x | R/W-x |

|------------------------------------|-------|-------|------------------------------------|--------|--------------------|-------|-------|

|                                    |       |       | EID                                | <15:8> |                    |       |       |

| bit 15                             |       |       |                                    |        |                    |       | bit 8 |

|                                    |       |       |                                    |        |                    |       |       |

| R/W-x                              | R/W-x | R/W-x | R/W-x                              | R/W-x  | R/W-x              | R/W-x | R/W-x |

|                                    |       |       | EIC                                | )<7:0> |                    |       |       |

| bit 7                              |       |       |                                    |        |                    |       | bit 0 |

|                                    |       |       |                                    |        |                    |       |       |

| Legend:                            |       |       |                                    |        |                    |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0' |        |                    |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea                  | ared   | x = Bit is unknown |       |       |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

### 25.1 DC Characteristics

| TABLE 25-1: | <b>OPERATING MIPS VS. VOLTAGE</b> |

|-------------|-----------------------------------|

|             |                                   |

| Characteristic | VDD Range                | Temp Range      | Max MIPS                     |  |  |

|----------------|--------------------------|-----------------|------------------------------|--|--|

| Characteristic | (in Volts)               | (in °C)         | dsPIC33FJXXXGPX06A/X08A/X10A |  |  |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                           |  |  |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                           |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 25-11 for the minimum and maximum BOR values.

#### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol         | Min | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------|----------------|-----|-------------|------|------|

| dsPIC33FJXXXGPX06A/X08A/X10A                                                                |                |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ             | -40 | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA             | -40 | —           | +85  | °C   |

| Extended Temperature Devices                                                                |                |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ             | -40 | —           | +150 | °C   |

| Operating Ambient Temperature Range                                                         | TA             | -40 | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD PINT + PI/O |     | W           |      |      |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |                |     |             |      |      |

| Maximum Allowed Power Dissipation                                                           | Pdmax          | (   | TJ - TA)/θJ | A    | W    |

#### TABLE 25-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        |     | Тур | Max | Unit | Notes |

|-------------------------------------------------------|-----|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θја | 40  | —   | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1 mm)  | θја | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θja | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

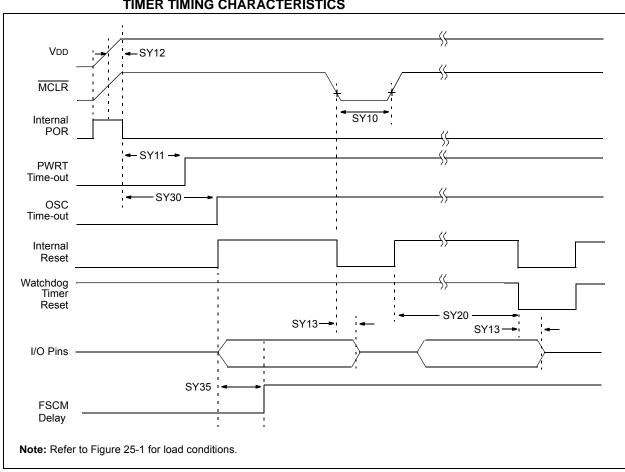

# FIGURE 25-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

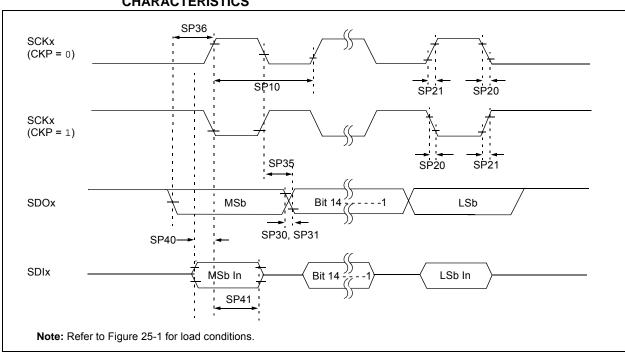

# FIGURE 25-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

# TABLE 25-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Inc<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for E |                       |                                               |                                             |   | +85°C for Industrial |     |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------|---------------------------------------------|---|----------------------|-----|--------------------------------------|

| Param<br>No.                                                                                                                                                                                                        | Symbol                | Characteristic <sup>(1)</sup>                 | Min Typ <sup>(2)</sup> Max Units Conditions |   |                      |     |                                      |

| SP10                                                                                                                                                                                                                | TscP                  | Maximum SCK Frequency                         | —                                           | _ | 10                   | MHz | See Note 3                           |

| SP20                                                                                                                                                                                                                | TscF                  | SCKx Output Fall Time                         | —                                           | — | _                    | ns  | See parameter DO32 and <b>Note 4</b> |

| SP21                                                                                                                                                                                                                | TscR                  | SCKx Output Rise Time                         | —                                           | — | _                    | ns  | See parameter DO31 and <b>Note 4</b> |

| SP30                                                                                                                                                                                                                | TdoF                  | SDOx Data Output Fall Time                    | —                                           | — | _                    | ns  | See parameter DO32 and <b>Note 4</b> |

| SP31                                                                                                                                                                                                                | TdoR                  | SDOx Data Output Rise Time                    | —                                           | — | _                    | ns  | See parameter DO31 and <b>Note 4</b> |

| SP35                                                                                                                                                                                                                | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —                                           | 6 | 20                   | ns  | —                                    |

| SP36                                                                                                                                                                                                                | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                          | — |                      | ns  | _                                    |

| SP40                                                                                                                                                                                                                | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                          | _ |                      | ns  | _                                    |

| SP41                                                                                                                                                                                                                | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                          | — | -                    | ns  | —                                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

#### FIGURE 25-17: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE) ))ī SCLx IM34 IM31\_ IM30 IM33 1 SDAx )) (( Start Stop Condition Condition Note: Refer to Figure 25-1 for load conditions.

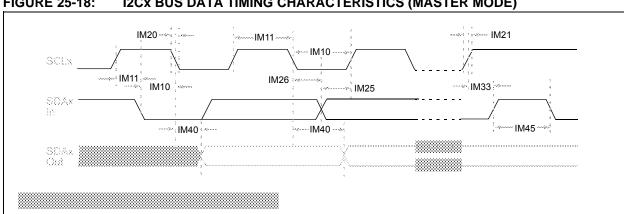

#### FIGURE 25-18: **I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)**

### 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters for high temperature devices. However, all AC timing specifications in this section are the same as those in Section 25.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter OS53 in Section 25.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

### TABLE 26-7: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

|                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$                  |

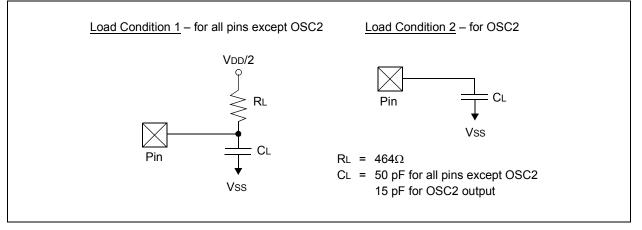

## FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 26-8: PLL CLOCK TIMING SPECIFICATIONS

| AC<br>CHARACTERISTICSStandard Operating Conditions: $3.0V$ to $3.6V$ (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |        |                                        |    |     |   |       |                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|----|-----|---|-------|-----------------------------|

| Param<br>No.                                                                                                                                                                         | Symbol | Characteristic Min Typ Max             |    |     |   | Units | Conditions                  |

| HOS53                                                                                                                                                                                | DCLK   | CLKO Stability (Jitter) <sup>(1)</sup> | -5 | 0.5 | 5 | %     | Measured over 100 ms period |

Note 1: These parameters are characterized, but are not tested in manufacturing.

80-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

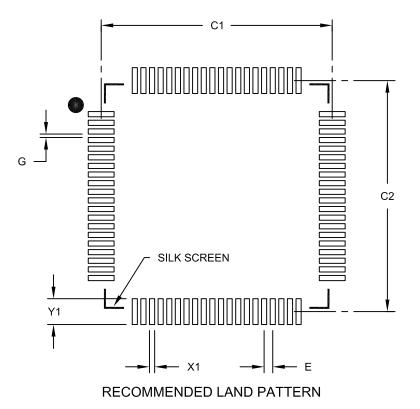

| [                        | Units       |      |          | -    |  |

|--------------------------|-------------|------|----------|------|--|

|                          | MILLIMETERS |      |          |      |  |

| Dimensi                  | MIN         | NOM  | MAX      |      |  |

| Contact Pitch            | E           |      | 0.50 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 13.40    |      |  |

| Contact Pad Spacing      | C2          |      | 13.40    |      |  |

| Contact Pad Width (X80)  | X1          |      |          | 0.30 |  |

| Contact Pad Length (X80) | Y1          |      |          | 1.50 |  |

| Distance Between Pads    | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B