Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp206a-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

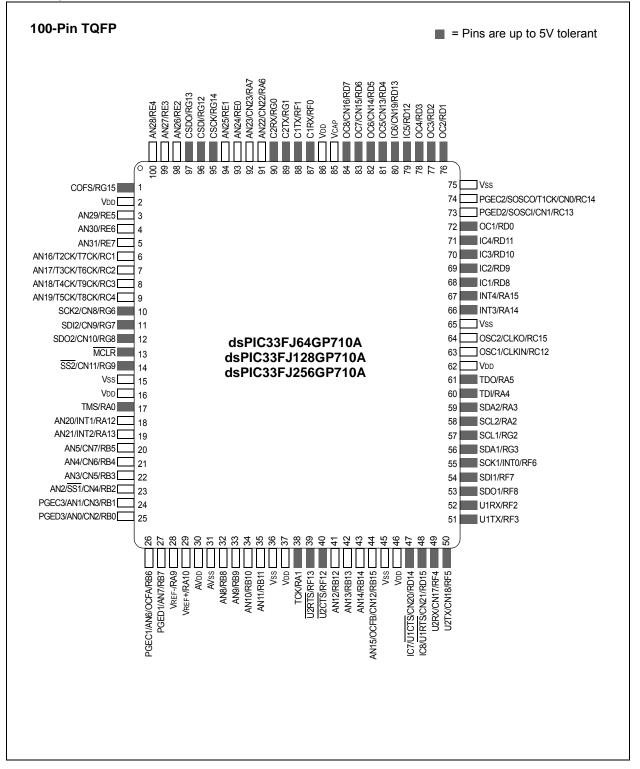

### **Pin Diagrams (Continued)**

| SFR Name | SFR<br>Addr | Bit 15     | Bit 14     | Bit 13      | Bit 12     | Bit 11      | Bit 10     | Bit 9      | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|------------|------------|-------------|------------|-------------|------------|------------|-------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |            |            |             |            |             |            |            | Input 1 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |            |            |             |            |             |            |            | Input 2 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |            |            |             |            |             |            |            | Input 3 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |            |            |             |            |             |            |            | Input 4 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC4CON   | 014E        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |            |            |             |            |             |            |            | Input 5 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        |            |            | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |            |            |             |            |             |            |            | Input 6 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | _          | _          | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |            |            |             |            |             |            |            | Input 7 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | -          | _          | ICSIDL      | _          | _           | —          |            | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |            |            |             |            |             |            |            | Input 8 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _          | —          | ICSIDL      | —          | —           | —          | _          | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Legend:  | x = unkno   | wn value c | n Reset, - | – = unimple | emented, r | ead as '0'. | Reset valu | es are sho | wn in hexad | lecimal.     |       |       |       |       |       |          |       |               |

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

dsPIC33FJXXXGPX06A/X08A/X10A

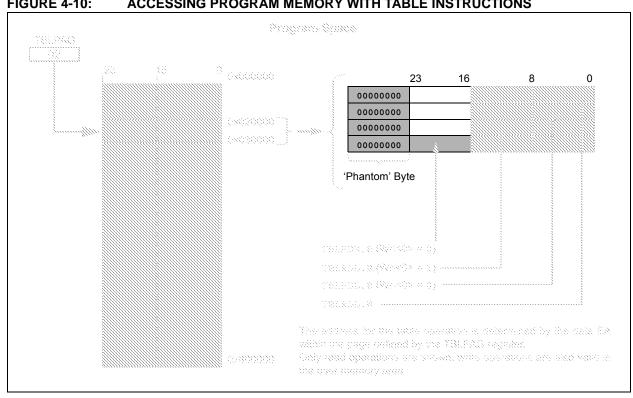

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0           | U-0                                                                                                        | U-0                                    | U-0            | U-0              | U-0              | U-0              | U-0 |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|------------------|------------------|------------------|-----|--|--|--|--|--|

|               |                                                                                                            |                                        | 0-0            |                  |                  |                  |     |  |  |  |  |  |

| <br>bit 15    |                                                                                                            |                                        |                |                  |                  |                  | bit |  |  |  |  |  |

|               |                                                                                                            |                                        |                |                  |                  |                  | Dit |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                      | R/W-0                                  | R/W-0          | U-0              | R/W-0            | R/W-0            | U-0 |  |  |  |  |  |

| C2TXIF        | C1TXIF                                                                                                     | DMA7IF                                 | DMA6IF         |                  | U2EIF            | U1EIF            | _   |  |  |  |  |  |

| bit 7         |                                                                                                            |                                        |                |                  |                  |                  | bit |  |  |  |  |  |

| Legend:       |                                                                                                            |                                        |                |                  |                  |                  |     |  |  |  |  |  |

| R = Readabl   | lo hit                                                                                                     | W = Writable                           | hit            | II – Unimploi    | mented bit, read |                  |     |  |  |  |  |  |

| -n = Value at |                                                                                                            | '1' = Bit is set                       |                | '0' = Bit is cle |                  | x = Bit is unkno | WD  |  |  |  |  |  |

|               | FUR                                                                                                        |                                        |                |                  | areu             |                  | WII |  |  |  |  |  |

| bit 15-8      | Unimalomo                                                                                                  | n <b>ted:</b> Read as '                | 0'             |                  |                  |                  |     |  |  |  |  |  |

| bit 7         | •                                                                                                          |                                        |                | ntorrunt Flog C  | Yatua hit        |                  |     |  |  |  |  |  |

|               |                                                                                                            | AN2 Transmit D                         | -              | nterrupt riag a  | Status Dit       |                  |     |  |  |  |  |  |

|               | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>         |                                        |                |                  |                  |                  |     |  |  |  |  |  |

| bit 6         | •                                                                                                          | •                                      |                | nterrunt Elan S  | status bit       |                  |     |  |  |  |  |  |

| bit 0         | <b>C1TXIF:</b> ECAN1 Transmit Data Request Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                        |                |                  |                  |                  |     |  |  |  |  |  |

|               |                                                                                                            | request has no                         |                |                  |                  |                  |     |  |  |  |  |  |

| bit 5         | DMA7IF: DM                                                                                                 | 1A Channel 7 D                         | ata Transfer C | complete Interr  | upt Flag Status  | bit              |     |  |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                                         |                                        |                |                  |                  |                  |     |  |  |  |  |  |

|               |                                                                                                            | 0 = Interrupt request has not occurred |                |                  |                  |                  |     |  |  |  |  |  |

| bit 4         | DMA6IF: DM                                                                                                 | 1A Channel 6 D                         | ata Transfer C | omplete Interr   | upt Flag Status  | bit              |     |  |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                                         |                                        |                |                  |                  |                  |     |  |  |  |  |  |

|               | 0 = Interrupt                                                                                              | request has no                         | t occurred     |                  |                  |                  |     |  |  |  |  |  |

| bit 3         | Unimpleme                                                                                                  | nted: Read as '                        | 0'             |                  |                  |                  |     |  |  |  |  |  |

| bit 2         | U2EIF: UAR                                                                                                 | T2 Interrupt Fla                       | g Status bit   |                  |                  |                  |     |  |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                                         |                                        |                |                  |                  |                  |     |  |  |  |  |  |

|               | 0 = Interrupt                                                                                              | request has no                         | t occurred     |                  |                  |                  |     |  |  |  |  |  |

| bit 1         | U1EIF: UAR                                                                                                 | T1 Interrupt Fla                       | g Status bit   |                  |                  |                  |     |  |  |  |  |  |

|               |                                                                                                            | request has oc                         |                |                  |                  |                  |     |  |  |  |  |  |

|               | 0 = Interrupt                                                                                              | request has no                         | t occurred     |                  |                  |                  |     |  |  |  |  |  |

| bit 0         | Unimpleme                                                                                                  | nted: Read as '                        | 0'             |                  |                  |                  |     |  |  |  |  |  |

|               |                                                                                                            |                                        |                |                  |                  |                  |     |  |  |  |  |  |

### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit |

|-------|----------------------------------------------------|

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 1 | XWCOL1: Channel 1 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit |

|       | 1 = Write collision detected                       |

|       | 0 = No write collision detected                    |

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

### 11.3 Configuring Analog Port Pins

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXGPX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| btss | PORTB, #13 | i | Next Instruction                |

|      |            |   |                                 |

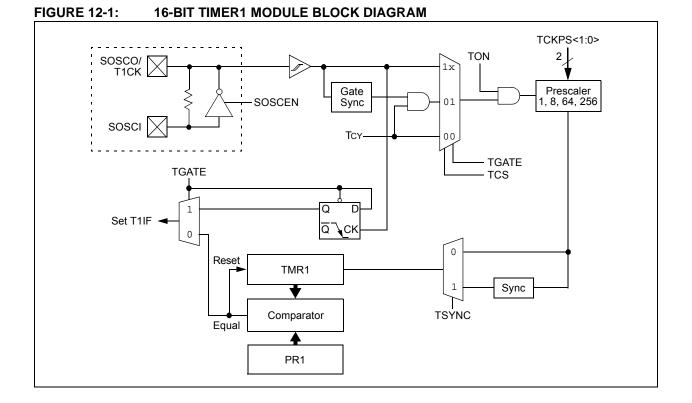

### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

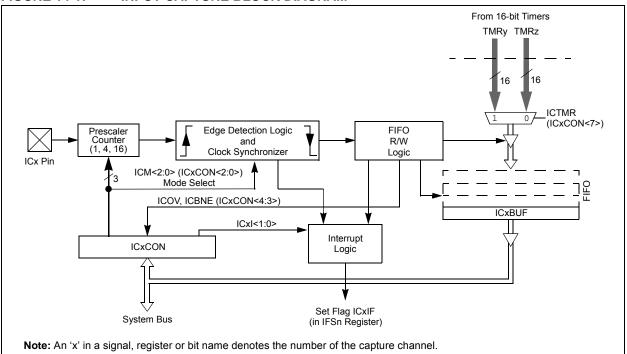

### 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJXXXGPX06A/X08A/X10A devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- · Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to 1 (ICI<1:0> = 00).

FIGURE 14-1: INPUT CAPTURE BLOCK DIAGRAM

### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1 (CONTINUED)

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

| U-0             | U-0                                                                                        | R/W-0                                  | R/W-0         | r-0                          | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------|----------------------------------------|---------------|------------------------------|------------------|-----------------|-------|--|--|--|--|--|

| _               | —                                                                                          | CSIDL                                  | ABAT          | —                            |                  | REQOP<2:0>      |       |  |  |  |  |  |

| bit 15          |                                                                                            |                                        |               |                              |                  |                 | bit   |  |  |  |  |  |

| R-1             | R-0                                                                                        | R-0                                    | U-0           | R/W-0                        | U-0              | U-0             | R/W-0 |  |  |  |  |  |

|                 | OPMODE<2:0                                                                                 |                                        | _             | CANCAP                       | _                | _               | WIN   |  |  |  |  |  |

| bit 7           |                                                                                            |                                        |               |                              |                  |                 | bit   |  |  |  |  |  |

| Legend:         |                                                                                            |                                        |               |                              |                  |                 |       |  |  |  |  |  |

| R = Readable    | hit                                                                                        | W = Writable                           | hit           | II = I Inimplen              | nented bit, read | 1 as 'N'        |       |  |  |  |  |  |

| -n = Value at I |                                                                                            | '1' = Bit is se                        |               | '0' = Bit is clea            |                  | r = Bit is Rese | rved  |  |  |  |  |  |

|                 | Ölt                                                                                        | 1 Dit io oo                            |               |                              |                  |                 |       |  |  |  |  |  |

| bit 15-14       | Unimplemer                                                                                 | nted: Read as                          | '0'           |                              |                  |                 |       |  |  |  |  |  |

| bit 13          | CSIDL: Stop                                                                                | o in Idle Mode I                       | oit           |                              |                  |                 |       |  |  |  |  |  |

|                 |                                                                                            |                                        |               | levice enters Idl            | e mode           |                 |       |  |  |  |  |  |

|                 |                                                                                            | module opera                           |               |                              |                  |                 |       |  |  |  |  |  |

| bit 12          |                                                                                            | All Pending Tr                         |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 0                                                                                          | l transmit buffe<br>vill clear this bi |               | nsmission<br>smissions are a | borted           |                 |       |  |  |  |  |  |

| bit 11          | Reserved: D                                                                                |                                        |               |                              |                  |                 |       |  |  |  |  |  |

| bit 10-8        |                                                                                            |                                        | peration Mode | bits                         |                  |                 |       |  |  |  |  |  |

|                 | <b>REQOP&lt;2:0&gt;:</b> Request Operation Mode bits<br>111 = Set Listen All Messages mode |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 110 = Reserved - do not use                                                                |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 101 = Reserved - do not use                                                                |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 |                                                                                            | onfiguration mo<br>sten Only Mode      |               |                              |                  |                 |       |  |  |  |  |  |

|                 |                                                                                            | opback mode                            | 5             |                              |                  |                 |       |  |  |  |  |  |

|                 | 001 = Set Disable mode                                                                     |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 000 <b>= Set N</b> o                                                                       | ormal Operatio                         | n mode        |                              |                  |                 |       |  |  |  |  |  |

| bit 7-5         |                                                                                            | :0>: Operation                         |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 111 = Module is in Listen All Messages mode                                                |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 110 = Reserved<br>101 = Reserved                                                           |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 100 = Module is in Configuration mode                                                      |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 011 = Module is in Listen Only mode                                                        |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 010 = Module is in Loopback mode                                                           |                                        |               |                              |                  |                 |       |  |  |  |  |  |

|                 |                                                                                            | e is in Disable<br>e is in Normal      |               | de                           |                  |                 |       |  |  |  |  |  |

| bit 4           |                                                                                            | nted: Read as                          | -             |                              |                  |                 |       |  |  |  |  |  |

| bit 3           | -                                                                                          |                                        |               | Capture Event                | Enable bit       |                 |       |  |  |  |  |  |

|                 |                                                                                            | •                                      |               | nessage receive              |                  |                 |       |  |  |  |  |  |

|                 | 0 = Disable (                                                                              |                                        |               | Ū                            |                  |                 |       |  |  |  |  |  |

| bit 2-1         | Unimplemer                                                                                 | nted: Read as                          | '0'           |                              |                  |                 |       |  |  |  |  |  |

| bit 0           | WIN: SFR M                                                                                 | lap Window Se                          | elect bit     |                              |                  |                 |       |  |  |  |  |  |

|                 | 1 = Use filter                                                                             | window                                 |               |                              |                  |                 |       |  |  |  |  |  |

|                 | 0 = Use buffe                                                                              |                                        |               |                              |                  |                 |       |  |  |  |  |  |

### REGISTER 19-1: CiCTRL1: ECAN™ CONTROL REGISTER 1

| U-0                             | U-0                      | R-0                | R-0          | R-0                 | R-0          | R-0                | R-0   |  |

|---------------------------------|--------------------------|--------------------|--------------|---------------------|--------------|--------------------|-------|--|

| —                               |                          |                    |              | FBP<5               | :0>          |                    |       |  |

| pit 15                          |                          |                    |              |                     |              |                    | bit 8 |  |

|                                 |                          |                    |              |                     |              |                    |       |  |

| U-0                             | U-0                      | R-0                | R-0          | R-0                 | R-0          | R-0                | R-0   |  |

|                                 |                          |                    |              | FNRB<               | 5:0>         |                    |       |  |

| oit 7                           |                          |                    |              |                     |              |                    | bit C |  |

|                                 |                          |                    |              |                     |              |                    |       |  |

| L <b>egend:</b><br>R = Readable | e bit                    | W = Writable b     | it           | U = Unimplemer      | ited bit, re | ad as '0'          |       |  |

| n = Value at                    | POR                      | '1' = Bit is set   |              | '0' = Bit is cleare | d            | x = Bit is unknown |       |  |

|                                 |                          |                    |              |                     |              |                    |       |  |

| oit 15-14                       | Unimpleme                | ented: Read as '0' | 1            |                     |              |                    |       |  |

| oit 13-8                        | FBP<5:0>:                | FIFO Write Buffer  | Pointer bits |                     |              |                    |       |  |

|                                 | 011111 <b>= F</b>        |                    |              |                     |              |                    |       |  |

|                                 | 011110 <b>= F</b>        | RB30 buffer        |              |                     |              |                    |       |  |

|                                 | •                        |                    |              |                     |              |                    |       |  |

|                                 | •                        |                    |              |                     |              |                    |       |  |

|                                 | 000001 = T<br>000000 = T |                    |              |                     |              |                    |       |  |

| oit 7-6                         |                          | ented: Read as '0' |              |                     |              |                    |       |  |

| oit 5-0                         | -                        | : FIFO Next Read   |              | tor hite            |              |                    |       |  |

| 510 5-0                         | 011111 = F               |                    |              |                     |              |                    |       |  |

|                                 | 011111 <b>–</b> F        |                    |              |                     |              |                    |       |  |

|                                 | •                        |                    |              |                     |              |                    |       |  |

|                                 | •                        |                    |              |                     |              |                    |       |  |

|                                 | •<br>000001 = T          |                    |              |                     |              |                    |       |  |

|                                 |                          |                    |              |                     |              |                    |       |  |

### REGISTER 19-5: CiFIFO: ECAN™ FIFO STATUS REGISTER

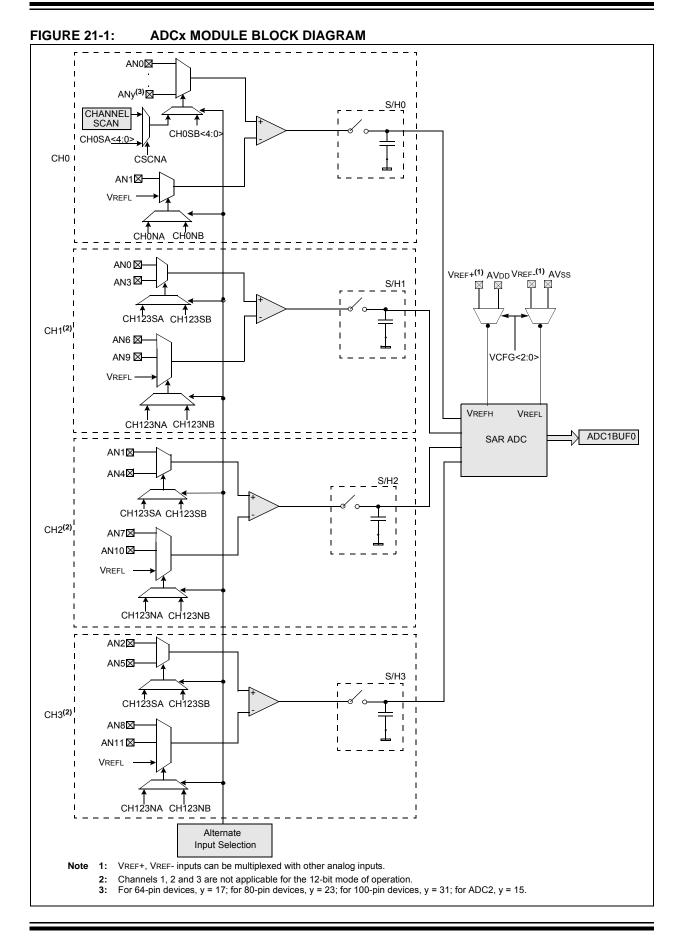

### 21.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprereference source. То hensive complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have up to 32 ADC input channels. These devices also have up to 2 ADC modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

**Note:** The ADC module needs to be disabled before modifying the AD12B bit.

### 21.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device.

A block diagram of the ADC is shown in Figure 21-1.

### 21.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>).

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>).

- Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>).

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>).

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>).

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>).

- g) Turn on ADC module (ADxCON1<15>).

- 2. Configure ADC interrupt (if required):

- a) Clear the ADxIF bit.

- b) Select ADC interrupt priority.

### 21.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

### 24.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 24.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 24.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### TABLE 25-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |              |                    |     |       |                                      |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       | Min          | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCK Input Frequency                                                                                                                                                                                                                                                         | —            | _                  | 11  | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                                                                                                                                                                                                                                                | —            |                    |     | ns    | See parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                                                                                                                                                                                                                                                | _            |                    | _   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                                                                                                          | —            | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                                                                                                          | —            | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                                                                                                           | —            | 6                  | 20  | ns    | —                                    |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                                                                                                                        | 30           | —                  | _   | ns    | —                                    |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                          | 30           | _                  | _   | ns    | —                                    |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                           | 30           |                    |     | ns    | —                                    |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\uparrow$ or SCKx Input                                                                                                                                                                                                                 | 120          |                    | —   | ns    | —                                    |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>                                                                                                                                                                                                                               | 10           | _                  | 50  | ns    | —                                    |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                                                                                                                                                                                                                                 | 1.5 TCY + 40 |                    |     | ns    | See Note 4                           |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                                                                                                                                                                                                                            |              | —                  | 50  | ns    | —                                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specificiation.

**4:** Assumes 50 pF load on all SPIx pins.

NOTES:

NOTES:

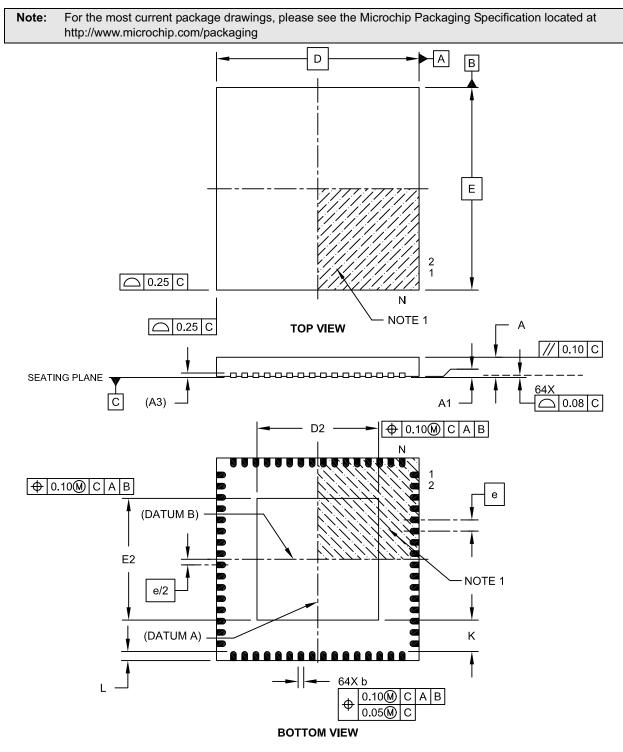

### 28.2 Package Details

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

NOTES: