Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp206a-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

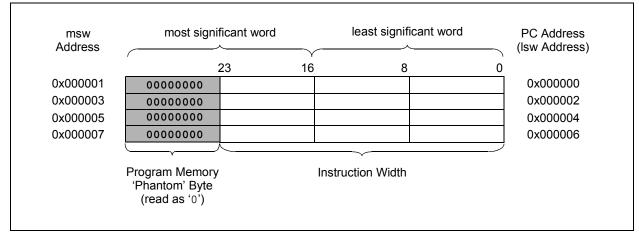

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXGPX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXGPX06A/X08A/X10A devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

## 5.0 FLASH PROGRAM MEMORY

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and

Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

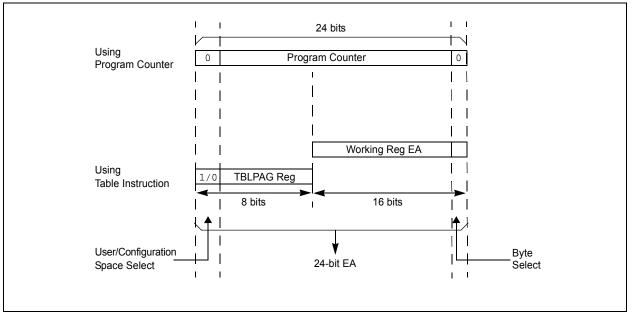

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### 5.2 RTSP Operation

The dsPIC33FJXXXGPX06A/X08A/X10A Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 25-12 illustrates typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

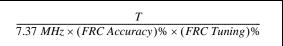

The programming time depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 25-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

### 5.4 Control Registers

The two SFRs that are used to read and write the program Flash memory are:

NVMCON: Flash Memory Control Register

#### • NVMKEY: Non-Volatile Memory Key Register

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| U-0          | R/W-1        | R/W-0                | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------|----------------|------------------|-----------------|-----------------|-------|

| _            |              | C2RXIP<2:0>          |                | _                |                 | INT4IP<2:0>     |       |

| oit 15       |              |                      |                |                  |                 |                 | bit   |

|              |              |                      |                |                  |                 |                 |       |

| U-0          | R/W-1        | R/W-0                | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _            |              | INT3IP<2:0>          |                | —                |                 | T9IP<2:0>       |       |

| bit 7        | ·            |                      |                |                  |                 |                 | bit   |

| Legend:      |              |                      |                |                  |                 |                 |       |

| R = Readab   | le bit       | W = Writable I       | oit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value a |              | '1' = Bit is set     |                | '0' = Bit is cle |                 | x = Bit is unkn | own   |

|              |              |                      |                |                  |                 |                 |       |

| bit 15       | Unimpleme    | nted: Read as '0     | )'             |                  |                 |                 |       |

| bit 14-12    | -            | 0>: ECAN2 Rece       |                | ady Interrupt Pr | iority bits     |                 |       |

|              |              | upt is priority 7 (ł |                |                  | 2               |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | 001 = Interr | upt is priority 1    |                |                  |                 |                 |       |

|              |              | upt source is disa   | abled          |                  |                 |                 |       |

| bit 11       | Unimpleme    | nted: Read as '0     | )'             |                  |                 |                 |       |

| bit 10-8     | INT4IP<2:0   | External Interr      | upt 4 Priority | bits             |                 |                 |       |

|              | 111 = Interr | upt is priority 7 (h | nighest priori | ty interrupt)    |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | 001 = Interr | upt is priority 1    |                |                  |                 |                 |       |

|              | 000 = Interr | upt source is disa   | abled          |                  |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as '0     | )'             |                  |                 |                 |       |

| bit 6-4      | INT3IP<2:0   | : External Interr    | upt 3 Priority | bits             |                 |                 |       |

|              | 111 = Interr | upt is priority 7 (ł | nighest priori | ty interrupt)    |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              |              | upt is priority 1    |                |                  |                 |                 |       |

|              |              | upt source is disa   |                |                  |                 |                 |       |

| bit 3        | -            | nted: Read as '0     |                |                  |                 |                 |       |

| oit 2-0      |              | Timer9 Interrupt     | -              |                  |                 |                 |       |

|              | 111 = Interr | upt is priority 7 (h | nighest priori | ty interrupt)    |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              | •            |                      |                |                  |                 |                 |       |

|              |              | upt is priority 1    |                |                  |                 |                 |       |

|              | 000 - Interr | upt source is disa   |                |                  |                 |                 |       |

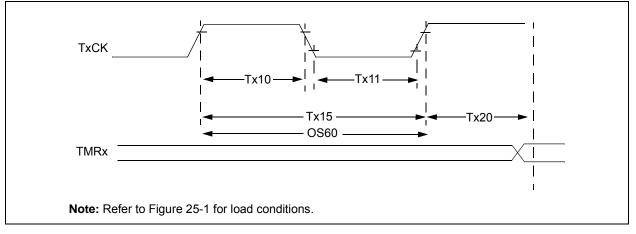

### 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-bit Timers (e.g., Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit Timer

- Single 32-bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

- ADC2 Event Trigger (Timer4/5 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2, Timer4, Timer6 or Timer8 is the least significant word; Timer3, Timer5, Timer7 or Timer9 is the most significant word of the 32-bit timers.

Note: For 32-bit operation, T3CON, T5CON, T7CON and T9CON control bits are ignored. Only T2CON, T4CON, T6CON and T8CON control bits are used for setup and control. Timer2, Timer4, Timer6 and Timer8 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3, Timer5, Ttimer7 and Timer9 interrupt flags.

To configure Timer2/3, Timer4/5, Timer6/7 or Timer8/9 for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2, Timer4, Timer6 or Timer8 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3, PR5, PR7 or PR9 contains the most significant word of the value, while PR2, PR4, PR6 or PR8 contains the least significant word.

- If interrupts are required, set the interrupt enable bit, T3IE, T5IE, T7IE or T9IE. Use the priority bits, T3IP<2:0>, T5IP<2:0>, T7IP<2:0> or T9IP<2:0>, to set the interrupt priority. While Timer2, Timer4, Timer6 or Timer8 control the timer, the interrupt appears as a Timer3, Timer5, Timer7 or Timer9 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, TMR5:TMR4, TMR7:TMR6 or TMR9:TMR8. TMR3, TMR5, TMR7 or TMR9 always contains the most significant word of the count, while TMR2, TMR4, TMR6 or TMR8 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

A block diagram for a 32-bit timer pair (Timer4/5) example is shown in Figure 13-1 and a timer (Timer4) operating in 16-bit mode example is shown in Figure 13-2.

Note: Only Timer2 and Timer3 can trigger a DMA data transfer.

© 2009-2012 Microchip Technology Inc.

NOTES:

| U-0           | U-0                                                                                          | R-0                                   | R-0             | R-0              | R-0              | R-0             | R-0   |  |

|---------------|----------------------------------------------------------------------------------------------|---------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|

|               |                                                                                              | ТХВО                                  | TXBP            | RXBP             | TXWAR            | RXWAR           | EWARN |  |

| bit 15        |                                                                                              |                                       |                 |                  |                  |                 | bit 8 |  |

| R/C-0         | R/C-0                                                                                        | R/C-0                                 | U-0             | R/C-0            | R/C-0            | R/C-0           | R/C-0 |  |

| IVRIF         | WAKIF                                                                                        | ERRIF                                 | 0-0             | FIFOIF           | RBOVIF           | RBIF            | TBIF  |  |

| bit 7         | WAKIF                                                                                        | ERRIF                                 |                 | FIFUIF           | RBOVIE           | RBIF            | bit   |  |

|               |                                                                                              |                                       |                 |                  |                  |                 | DIL   |  |

| Legend:       |                                                                                              | C = Clear on                          | y bit           |                  |                  |                 |       |  |

| R = Readable  | e bit                                                                                        | W = Writable                          | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set                      |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

| bit 15-14     | Unimplemen                                                                                   | nted: Read as '                       | 0'              |                  |                  |                 |       |  |

| bit 13        | -                                                                                            | smitter in Error                      |                 | bit              |                  |                 |       |  |

|               |                                                                                              | ter is in Bus Of                      |                 |                  |                  |                 |       |  |

|               | 0 = Transmitt                                                                                | ter is not in Bus                     | Off state       |                  |                  |                 |       |  |

| bit 12        | TXBP: Trans                                                                                  | mitter in Error                       | State Bus Pas   | sive bit         |                  |                 |       |  |

|               |                                                                                              | ter is in Bus Pa<br>ter is not in Bus |                 | -                |                  |                 |       |  |

| bit 11        |                                                                                              |                                       |                 |                  |                  |                 |       |  |

|               | <b>RXBP:</b> Receiver in Error State Bus Passive bit<br>1 = Receiver is in Bus Passive state |                                       |                 |                  |                  |                 |       |  |

|               |                                                                                              | is not in Bus P                       |                 |                  |                  |                 |       |  |

| bit 10        | TXWAR: Transmitter in Error State Warning bit                                                |                                       |                 |                  |                  |                 |       |  |

|               | 1 = Transmitter is in Error Warning state                                                    |                                       |                 |                  |                  |                 |       |  |

|               | 0 = Transmitt                                                                                | ter is not in Erro                    | or Warning sta  | ate              |                  |                 |       |  |

| bit 9         |                                                                                              | ceiver in Error                       | •               | bit              |                  |                 |       |  |

|               |                                                                                              | is in Error War                       |                 |                  |                  |                 |       |  |

| L:1 0         |                                                                                              | is not in Error                       |                 |                  | L:4              |                 |       |  |

| bit 8         |                                                                                              | nsmitter or Rec<br>ter or receiver i  |                 |                  | DIT              |                 |       |  |

|               |                                                                                              | ter or receiver i                     |                 | •                |                  |                 |       |  |

| bit 7         |                                                                                              | d Message Rec                         |                 | •                |                  |                 |       |  |

|               |                                                                                              | request has oc                        |                 | 5                |                  |                 |       |  |

|               | 0 = Interrupt                                                                                | request has no                        | t occurred      |                  |                  |                 |       |  |

| bit 6         |                                                                                              | Wake-up Activ                         |                 | ag bit           |                  |                 |       |  |

|               |                                                                                              | request has oc                        |                 |                  |                  |                 |       |  |

| 6:4 <i>5</i>  | -                                                                                            | request has no                        |                 |                  |                  |                 |       |  |

| bit 5         |                                                                                              |                                       |                 | ources in Clin   | F<13:8> regist   | er)             |       |  |

|               |                                                                                              | request has oc<br>request has no      |                 |                  |                  |                 |       |  |

| bit 4         | -                                                                                            | nted: Read as '                       |                 |                  |                  |                 |       |  |

| bit 3         | -                                                                                            | ) Almost Full In                      |                 | it               |                  |                 |       |  |

|               |                                                                                              | request has oc                        |                 |                  |                  |                 |       |  |

|               | •                                                                                            | request has no                        |                 |                  |                  |                 |       |  |

| bit 2         | <b>RBOVIF:</b> RX                                                                            | Buffer Overflo                        | w Interrupt Fla | ag bit           |                  |                 |       |  |

|               |                                                                                              | request has oc                        |                 |                  |                  |                 |       |  |

|               |                                                                                              | request has no                        |                 |                  |                  |                 |       |  |

| bit 1         |                                                                                              | Iffer Interrupt Fl                    | -               |                  |                  |                 |       |  |

|               | •                                                                                            | request has oc<br>request has no      |                 |                  |                  |                 |       |  |

|               |                                                                                              | i oquest nas nu                       |                 |                  |                  |                 |       |  |

| hit ()        | TRIF. TY Duf                                                                                 | ffor Interrupt El                     | aa hit          |                  |                  |                 |       |  |

| bit 0         |                                                                                              | ffer Interrupt Fla<br>request has oc  | -               |                  |                  |                 |       |  |

### REGISTER 19-6: CIINTF: ECAN™ INTERRUPT FLAG REGISTER

### **REGISTER 19-8:** CiEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0                               | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                            | R-0                                                                                                                                                                                          |  |

|-----------------------------------|------------------|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                   |                  | TERRO                         | CNT<7:0>                                     |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|                                   |                  |                               |                                              |                                                                                                                                           |                                                                                                | bit 8                                                                                                                                                                                        |  |

|                                   |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

| R-0                               | R-0              | R-0                           | R-0                                          | R-0                                                                                                                                       | R-0                                                                                            | R-0                                                                                                                                                                                          |  |

|                                   |                  | RERR                          | CNT<7:0>                                     |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|                                   |                  |                               |                                              |                                                                                                                                           |                                                                                                | bit 0                                                                                                                                                                                        |  |

|                                   |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

|                                   |                  |                               |                                              |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

| R = Readable bit W = Writable bit |                  |                               | U = Unimplemented bit, read as '0'           |                                                                                                                                           |                                                                                                |                                                                                                                                                                                              |  |

| OR                                | '1' = Bit is set |                               | '0' = Bit is cleared x = Bit is              |                                                                                                                                           | x = Bit is unkr                                                                                | nown                                                                                                                                                                                         |  |

|                                   | R-0              | R-0 R-0<br>bit W = Writable b | R-0 R-0 R-0<br>RERRO<br>bit W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>            bit         W = Writable bit         U = Unimplement | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | R-0         R-0         R-0         R-0         R-0         R-0           Bit         W = Writable bit         U = Unimplemented bit, read as '0'         U = Unimplemented bit, read as '0' |  |

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

| R/W-x                             | R/W-x        | R/W-x                                                                                                                                | R/W-x          | R/W-x            | R/W-x              | R/W-x           | R/W-x            |  |  |

|-----------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------------|-----------------|------------------|--|--|

|                                   |              |                                                                                                                                      | SID            | <10:3>           |                    |                 |                  |  |  |

| bit 15                            |              |                                                                                                                                      |                |                  |                    |                 | bit 8            |  |  |

|                                   |              |                                                                                                                                      |                |                  |                    |                 |                  |  |  |

| R/W-x                             | R/W-x        | R/W-x                                                                                                                                | U-0            | R/W-x            | U-0                | R/W-x           | R/W-x            |  |  |

|                                   | SID<2:0>     |                                                                                                                                      |                | MIDE             |                    | EID<1           | 7:16>            |  |  |

| bit 7                             |              |                                                                                                                                      |                |                  |                    |                 | bit C            |  |  |

| Legend:                           |              |                                                                                                                                      |                |                  |                    |                 |                  |  |  |

| R = Readable bit W = Writable bit |              | oit                                                                                                                                  | U = Unimpler   | mented bit, read | d as '0'           |                 |                  |  |  |

| -n = Value at POR '1' = Bit       |              | '1' = Bit is set                                                                                                                     |                | '0' = Bit is cle | ared               | x = Bit is unkr | nown             |  |  |

|                                   |              |                                                                                                                                      |                |                  |                    |                 |                  |  |  |

| bit 15-5                          | SID<10:0>:   | Standard Identif                                                                                                                     | ier bits       |                  |                    |                 |                  |  |  |

|                                   | 1 = Include  | bit SIDx in filter c                                                                                                                 | omparison      |                  |                    |                 |                  |  |  |

|                                   | 0 = Bit SIDx | is don't care in fi                                                                                                                  | ilter comparis | son              |                    |                 |                  |  |  |

| bit 4                             | Unimpleme    | nted: Read as '0                                                                                                                     | )'             |                  |                    |                 |                  |  |  |

| bit 3                             | MIDE: Iden   | tifier Receive Mo                                                                                                                    | de bit         |                  |                    |                 |                  |  |  |

|                                   | 0 = Match e  | only message typ<br>either standard or<br>(Filter SID) = (Me                                                                         | extended a     | ddress messag    | e if filters match | י.<br>ו         | DE bit in filter |  |  |

| bit 2                             | Unimpleme    | nted: Read as 'o                                                                                                                     | )'             |                  |                    |                 |                  |  |  |

| bit 1-0                           | EID<17:16>   | : Extended Ident                                                                                                                     | ifier bits     |                  |                    |                 |                  |  |  |

|                                   | 1 = Include  | EID<17:16>: Extended Identifier bits<br>1 = Include bit EIDx in filter comparison<br>0 = Bit EIDx is don't care in filter comparison |                |                  |                    |                 |                  |  |  |

### REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x                | R/W-x | R/W-x              | R/W-x |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

|                                   |       |                  | EID                                | <15:8>               |       |                    |       |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x                | R/W-x | R/W-x              | R/W-x |

|                                   |       |                  | EID                                | )<7:0>               |       |                    |       |

| bit 7                             |       |                  |                                    |                      |       |                    | bit 0 |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

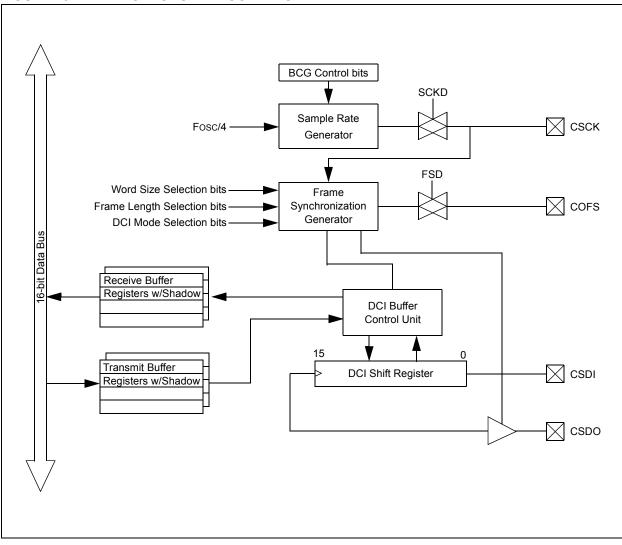

### FIGURE 20-1: DCI MODULE BLOCK DIAGRAM

| U-0          | U-0                                         | U-0                                                                                                                                            | U-0                   | R/W-0                              | R/W-0            | U-0            | R/W-0  |  |  |  |  |

|--------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|------------------|----------------|--------|--|--|--|--|

|              | —                                           | _                                                                                                                                              |                       | BLEN                               | l<1:0>           |                | COFSG3 |  |  |  |  |

| bit 15       | ·                                           |                                                                                                                                                |                       |                                    |                  |                | bit    |  |  |  |  |

|              |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

| R/W-0        | R/W-0                                       | R/W-0                                                                                                                                          | U-0                   | R/W-0                              | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | COFSG<2:0>                                  |                                                                                                                                                |                       |                                    | WS               | <3:0>          |        |  |  |  |  |

| bit 7        |                                             |                                                                                                                                                |                       |                                    |                  |                | bit    |  |  |  |  |

|              |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

| Legend:      |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

| R = Readab   |                                             | W = Writable                                                                                                                                   |                       |                                    | nented bit, read |                |        |  |  |  |  |

| -n = Value a | t POR                                       | '1' = Bit is set                                                                                                                               |                       | '0' = Bit is clea                  | ared             | x = Bit is unk | nown   |  |  |  |  |

|              |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

| bit 15-12    | -                                           | ted: Read as '                                                                                                                                 |                       |                                    |                  |                |        |  |  |  |  |

| bit 11-10    | BLEN<1:0>:                                  | Buffer Length (                                                                                                                                | Control bits          |                                    |                  |                |        |  |  |  |  |

|              |                                             |                                                                                                                                                |                       | ween interrupts                    |                  |                |        |  |  |  |  |

|              |                                             | <ul> <li>10 = Three data words will be buffered between interrupts</li> <li>01 = Two data words will be buffered between interrupts</li> </ul> |                       |                                    |                  |                |        |  |  |  |  |

|              |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              |                                             | a word will be t                                                                                                                               |                       | een interrupts                     |                  |                |        |  |  |  |  |

| bit 9        | Unimplemented: Read as '0'                  |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

| bit 8-5      | COFSG<3:0>                                  | : Frame Sync                                                                                                                                   | Generator Co          | ontrol bits                        |                  |                |        |  |  |  |  |

|              | 1111 <b>= Data</b> 1                        | frame has 16 w                                                                                                                                 | vords                 |                                    |                  |                |        |  |  |  |  |

|              | •                                           |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              | •                                           |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              | •<br>0010 = Data :                          | frame has 3 wo                                                                                                                                 | orde                  |                                    |                  |                |        |  |  |  |  |

|              |                                             | frame has 2 wo                                                                                                                                 |                       |                                    |                  |                |        |  |  |  |  |

|              |                                             | frame has 1 wo                                                                                                                                 |                       |                                    |                  |                |        |  |  |  |  |

| bit 4        | Unimplemen                                  | ted: Read as '                                                                                                                                 | 0'                    |                                    |                  |                |        |  |  |  |  |

| bit 3-0      | WS<3:0>: DC                                 | I Data Word S                                                                                                                                  | ize bits              |                                    |                  |                |        |  |  |  |  |

|              | 1111 <b>= Data</b>                          | word size is 16                                                                                                                                | bits                  |                                    |                  |                |        |  |  |  |  |

|              | •                                           |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              | •                                           |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              |                                             |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              | •                                           |                                                                                                                                                |                       |                                    |                  |                |        |  |  |  |  |

|              |                                             | word size is 5 l                                                                                                                               |                       |                                    |                  |                |        |  |  |  |  |

|              | 0011 <b>= Data</b>                          | word size is 4 b                                                                                                                               | oits                  |                                    |                  |                |        |  |  |  |  |

|              | 0011 <b>= Data</b><br>0010 <b>= Inval</b> i | word size is 4 l<br>d Selection.                                                                                                               | oits<br>)o not use. U | nexpected resul<br>nexpected resul |                  |                |        |  |  |  |  |

### REGISTER 20-2: DCICON2: DCI CONTROL REGISTER 2

#### REGISTER 20-5: RSCON: DCI RECEIVE SLOT CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| RSE15  | RSE14 | RSE13 | RSE12 | RSE11 | RSE10 | RSE9  | RSE8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RSE7  | RSE6  | RSE5  | RSE4  | RSE3  | RSE2  | RSE1  | RSE0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 RSE<15:0>: Receive Slot Enable bits

1 = CSDI data is received during the individual time slot n

0 = CSDI data is ignored during the individual time slot n

#### REGISTER 20-6: TSCON: DCI TRANSMIT SLOT CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| TSE15  | TSE14 | TSE13 | TSE12 | TSE11 | TSE10 | TSE9  | TSE8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TSE7  | TSE6  | TSE5  | TSE4  | TSE3  | TSE2  | TSE1  | TSE0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

TSE<15:0>: Transmit Slot Enable Control bits

1 = Transmit buffer contents are sent during the individual time slot n

0 = CSDO pin is tri-stated or driven to logic '0', during the individual time slot, depending on the state of the CSDOM bit

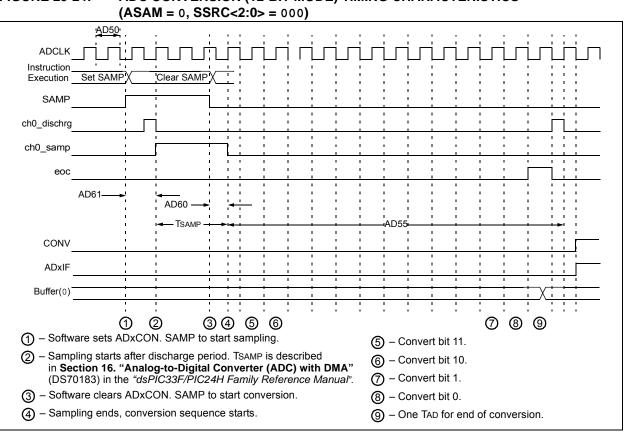

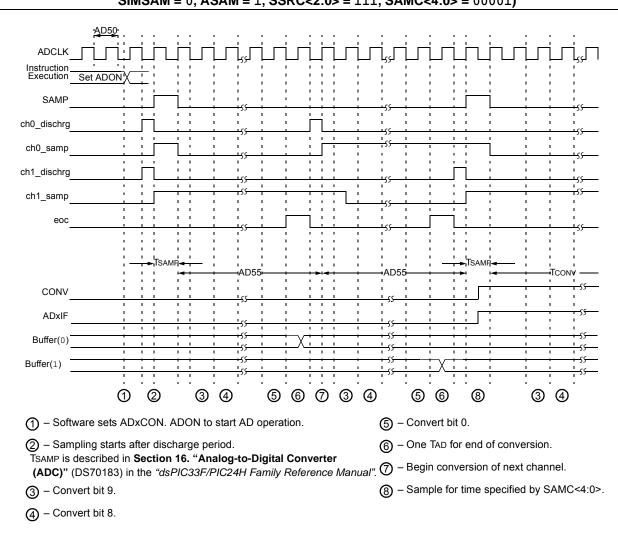

### 21.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

## 21.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browner: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/                                             |

|       | Devices.aspx?dDocName=en546064                                                                                 |

### 21.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### REGISTER 21-2: ADxCON2: ADCx CONTROL REGISTER 2 (where x = 1 or 2)

| R/W-0         | R/W-0                                                                                                                       | R/W-0                           | U-0                                         | U-0             | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|-----------------|-------------------|-------------------|--------------|--|--|--|--|

| VCFG<2:0>     |                                                                                                                             |                                 | _                                           |                 | CSCNA             | CHPS<1:0>         |              |  |  |  |  |

| bit 15        |                                                                                                                             |                                 |                                             | •               |                   |                   | bit 8        |  |  |  |  |

| R-0           | U-0                                                                                                                         | R/W-0                           | R/W-0                                       | R/W-0           | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| BUFS          | —                                                                                                                           | – SMPI<3:0>                     |                                             |                 | BUFM              | ALTS              |              |  |  |  |  |

| bit 7         |                                                                                                                             |                                 |                                             |                 |                   |                   | bit (        |  |  |  |  |

| Legend:       |                                                                                                                             |                                 |                                             |                 |                   |                   |              |  |  |  |  |

| R = Readabl   | e bit                                                                                                                       | W = Writabl                     | e bit                                       | U = Unimple     | emented bit, rea  | d as '0'          |              |  |  |  |  |

| -n = Value at | POR                                                                                                                         | '1' = Bit is s                  | et                                          | '0' = Bit is cl | eared             | x = Bit is unki   | nown         |  |  |  |  |

| bit 15-13     | VCFG<2:0>                                                                                                                   | : Converter Vo                  | oltage Reference                            | Configuration   | n bits            |                   |              |  |  |  |  |

|               |                                                                                                                             | VREF+                           | VREF-                                       |                 |                   |                   |              |  |  |  |  |

|               | 000                                                                                                                         | Avdd                            | Avss                                        |                 |                   |                   |              |  |  |  |  |

|               | 001 Exte                                                                                                                    | ernal VREF+                     | Avss                                        |                 |                   |                   |              |  |  |  |  |

|               | 010                                                                                                                         | Avdd                            | External VREF-                              |                 |                   |                   |              |  |  |  |  |

|               | 011 Exte                                                                                                                    | ernal VREF+                     | External VREF-                              |                 |                   |                   |              |  |  |  |  |

|               | 1xx                                                                                                                         | Avdd                            | Avss                                        |                 |                   |                   |              |  |  |  |  |

| bit 12-11     | Unimpleme                                                                                                                   | nted: Read as                   | <b>s</b> 'O'                                |                 |                   |                   |              |  |  |  |  |

| bit 10        | CSCNA: Sca                                                                                                                  | an Input Selec                  | tions for CH0+ d                            | uring Sample    | A bit             |                   |              |  |  |  |  |

|               | 1 = Scan inputs                                                                                                             |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | 0 = Do not s                                                                                                                | •                               |                                             |                 |                   |                   |              |  |  |  |  |

| bit 9-8       | CHPS<1:0>: Selects Channels Utilized bits                                                                                   |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | When AD12B = 1, CHPS<1:0> is: U-0, Unimplemented, Read as '0'<br>1x = Converts CH0, CH1, CH2 and CH3                        |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | 1x = Converts CH0, CH1, CH2 and CH301 = Converts CH0 and CH1                                                                |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | 00 = Conve                                                                                                                  | rts CH0                         |                                             |                 |                   |                   |              |  |  |  |  |

| bit 7         | BUFS: Buffe                                                                                                                 | er Fill Status bi               | t (only valid whe                           | n BUFM = 1)     |                   |                   |              |  |  |  |  |

|               |                                                                                                                             |                                 | g second half of b<br>g first half of buffe |                 |                   |                   |              |  |  |  |  |

| bit 6         |                                                                                                                             | nted: Read as                   |                                             |                 |                   |                   |              |  |  |  |  |

| bit 5-2       |                                                                                                                             |                                 | ment Rate for DN                            | /A Addresses    | s bits or number  | of sample/conv    | version      |  |  |  |  |

|               | operations per interrupt<br>1111 = Increments the DMA address or generates interrupt after completion of every 16th sample/ |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | conversion operation<br>1110 = Increments the DMA address or generates interrupt after completion of every 15th sample/     |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               |                                                                                                                             | ements the DI<br>version operat | •                                           | enerates inte   | rrupt after comp  | etion of every    | 15th sample  |  |  |  |  |

|               | •                                                                                                                           |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | •                                                                                                                           |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               | 0001 = Increments the DMA address or generates interrupt after completion of every 2nd sample/<br>conversion operation      |                                 |                                             |                 |                   |                   |              |  |  |  |  |

|               |                                                                                                                             | ements the DN operation         | /IA address or ge                           | enerates interr | rupt after comple | etion of every sa | ample/conver |  |  |  |  |

| bit 1         | BUFM: Buffe                                                                                                                 | er Fill Mode Se                 | elect bit                                   |                 |                   |                   |              |  |  |  |  |

|               |                                                                                                                             | -                               | of buffer on first ir                       |                 | econd half of the | e buffer on nex   | t interrupt  |  |  |  |  |

| bit 0         | ALTS: Alterr                                                                                                                | nate Input San                  | nple Mode Selec                             | t bit           |                   |                   |              |  |  |  |  |

|               | 1 = Uses ch                                                                                                                 | annel input se                  | elects for Sample input selects for         | A on first sar  | mple and Sampl    | e B on next sa    | mple         |  |  |  |  |

|               |                                                                                                                             |                                 | -                                           |                 |                   |                   |              |  |  |  |  |