Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                            |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | - ·                                                                               |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp206at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

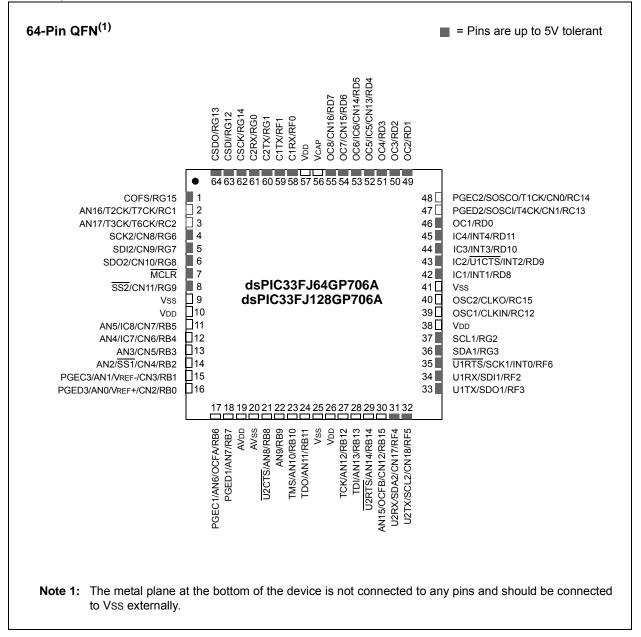

#### **Pin Diagrams (Continued)**

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the Most Significant bit (MSb) is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1}$  - 1. For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0. For a 32-bit integer, the data is -2,147,483,648 (0x8000 0000) range to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of  $3.01518 \times 10^{-5}$ . In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product which has a precision of  $4.65661 \times 10^{-10}$ .

The same multiplier is used to support the MCU multiply instructions which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

### 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter prior to accumulation.

### 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true, or complement data into the other input. In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented. The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow; they are:

- OA: AccA overflowed into guard bits

- OB: AccB overflowed into guard bits

- SA: AccA saturated (bit 31 overflow and saturation) or

AccA overflowed into guard bits and saturated (bit 39 overflow and saturation)

SB: AccB saturated (bit 31 overflow and saturation) or

AccB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register (refer to **Section 7.0 "Interrupt Controller"**) are set. This allows the user to take immediate action, for example, to correct system gain.

NOTES:

#### TABLE 4-15: ADC1 REGISTER MAP

| File Name   | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12              | Bit 11          | Bit 10    | Bit 9   | Bit 8   | Bit 7  | Bit 6     | Bit 5     | Bit 4      | Bit 3  | Bit 2  | Bit 1     | Bit 0   | All<br>Resets |

|-------------|------|--------|-----------|--------|---------------------|-----------------|-----------|---------|---------|--------|-----------|-----------|------------|--------|--------|-----------|---------|---------------|

| ADC1BUF0    | 0300 |        |           |        | ADC Data Buffer 0 x |                 |           |         |         |        |           | xxxx      |            |        |        |           |         |               |

| AD1CON1     | 0320 | ADON   | _         | ADSIDL | ADDMABM             | _               | AD12B     | FOR     | И<1:0>  | :      | SSRC<2:0> |           | _          | SIMSAM | ASAM   | SAMP      | DONE    | 0000          |

| AD1CON2     | 0322 | ١      | /CFG<2:0> | >      | _                   | CSCNA CHPS<1:0> |           |         | BUFS    | _      |           | SMPI<3:0> |            |        |        | ALTS      | 0000    |               |

| AD1CON3     | 0324 | ADRC   |           | —      |                     | SAMC<4:0>       |           |         |         |        | ADCS<7:0> |           |            |        |        | 0000      |         |               |

| AD1CHS123   | 0326 | —      |           | —      | _                   |                 | CH123N    | NB<1:0> | CH123SB |        |           |           | —          | —      | CH123N | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0     | 0328 | CH0NB  |           | —      |                     | CI              | H0SB<4:0> | >       |         | CH0NA  |           |           | CH0SA<4:0> |        |        |           | 0000    |               |

| AD1PCFGH(1) | 032A | PCFG31 | PCFG30    | PCFG29 | PCFG28              | PCFG27          | PCFG26    | PCFG25  | PCFG24  | PCFG23 | PCFG22    | PCFG21    | PCFG20     | PCFG19 | PCFG18 | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL    | 032C | PCFG15 | PCFG14    | PCFG13 | PCFG12              | PCFG11          | PCFG10    | PCFG9   | PCFG8   | PCFG7  | PCFG6     | PCFG5     | PCFG4      | PCFG3  | PCFG2  | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)  | 032E | CSS31  | CSS30     | CSS29  | CSS28               | CSS27           | CSS26     | CSS25   | CSS24   | CSS23  | CSS22     | CSS21     | CSS20      | CSS19  | CSS18  | CSS17     | CSS16   | 0000          |

| AD1CSSL     | 0330 | CSS15  | CSS14     | CSS13  | CSS12               | CSS11           | CSS10     | CSS9    | CSS8    | CSS7   | CSS6      | CSS5      | CSS4       | CSS3   | CSS2   | CSS1      | CSS0    | 0000          |

| AD1CON4     | 0332 | _      | _         | _      | —                   | _               | _         | _       | _       | _      | _         | _         | _          | _      | [      | DMABL<2:( | )>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

#### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11                                                                                               | Bit 10 | Bit 9   | Bit 8    | Bit 7     | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|------------------------------------------------------------------------------------------------------|--------|---------|----------|-----------|-------|-------|--------------|-------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         |                                                                                                      |        |         | ADC Data | Buffer 0  |       |       |              |       |        |          |         | xxxx          |

| AD2CON1   | 0360 | ADON   | _         | ADSIDL | ADDMABM | BM - AD12B FORM<1:0> SSRC<2:0> - SIMSAM ASAM SAMP DONE                                               |        |         |          |           | 0000  |       |              |       |        |          |         |               |

| AD2CON2   | 0362 | Ň      | VCFG<2:0> | >      | _       | —         CSCNA         CHPS<1:0>         BUFS         —         SMPI<3:0>         BUFM         ALTS |        |         |          |           | 0000  |       |              |       |        |          |         |               |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | SAMC<4:0>                                                                                            |        |         |          | ADCS<7:0> |       |       |              |       |        | 0000     |         |               |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _                                                                                                    | CH123N | IB<1:0> | CH123SB  | _         | _     | _     | _            | _     | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |                                                                                                      | CH0S   | B<3:0>  |          | CH0NA     | _     | _     | — CH0SA<3:0> |       |        |          | 0000    |               |

| Reserved  | 036A | _      | _         | _      | _       | _                                                                                                    | _      | _       | _        | _         | _     | _     | _            | _     | _      | _        | _       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11                                                                                               | PCFG10 | PCFG9   | PCFG8    | PCFG7     | PCFG6 | PCFG5 | PCFG4        | PCFG3 | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E | _      | _         | _      | _       | _                                                                                                    | _      | _       | _        | _         | _     | _     | _            | _     | _      | _        | _       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11                                                                                                | CSS10  | CSS9    | CSS8     | CSS7      | CSS6  | CSS5  | CSS4         | CSS3  | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       |                                                                                                      | _      | _       | _        | _         | _     | _     | _            | _     |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7      | '-8: IFS3: I    | INTERRUPT                        | FLAG STAT       | US REGIST        | ER 3             |                 |       |

|-----------------|-----------------|----------------------------------|-----------------|------------------|------------------|-----------------|-------|

| U-0             | U-0             | R/W-0                            | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |

| _               | _               | DMA5IF                           | DCIIF           | DCIEIF           | _                | —               | C2IF  |

| bit 15          |                 |                                  |                 | •                |                  |                 | bit 8 |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIF          | INT4IF          | INT3IF                           | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |

| bit 7           |                 |                                  |                 |                  |                  |                 | bit 0 |

| Legend:         |                 |                                  |                 |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable                     | bit             | U = Unimple      | mented bit, read | as '0'          |       |

| -n = Value at I |                 | '1' = Bit is set                 |                 | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                 |                 |                                  |                 |                  |                  |                 |       |

| bit 15-14       | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 13          | DMA5IF: DM      | A Channel 5 D                    | ata Transfer (  | Complete Inter   | rupt Flag Status | bit             |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 12          | DCIIF: DCI E    | vent Interrupt I                 | -lag Status bit |                  |                  |                 |       |

|                 | 1 = Interrupt   | request has oc                   | curred          |                  |                  |                 |       |

|                 | •               | request has no                   |                 |                  |                  |                 |       |

| bit 11          |                 | Error Interrupt                  | U               | it               |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 10-9        | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 8           | C2IF: ECAN2     | 2 Event Interrup                 | ot Flag Status  | bit              |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 7           | C2RXIF: ECA     | AN2 Receive D                    | ata Ready Int   | errupt Flag Sta  | atus bit         |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 6           | •               | rnal Interrupt 4                 |                 | it               |                  |                 |       |

|                 | 1 = Interrupt i | request has oc<br>request has no | curred          |                  |                  |                 |       |

| bit 5           | INT3IF: Exter   | rnal Interrupt 3                 | Flag Status b   | it               |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 4           | -               | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 | 1 = Interrupt i | request has oc                   | curred          |                  |                  |                 |       |

|                 | -               | request has no                   |                 |                  |                  |                 |       |

| bit 3           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

| bit 2           | -               | request has no<br>2 Master Even  |                 | ag Status bit    |                  |                 |       |

| SIL Z           |                 | request has oc                   | •               | ug oluluo bit    |                  |                 |       |

|                 |                 | request has no                   |                 |                  |                  |                 |       |

| bit 1           | SI2C2IF: 12C    | 2 Slave Events                   | Interrupt Flag  | g Status bit     |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

|                 | -               | request has no                   |                 |                  |                  |                 |       |

| bit 0           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

|                 |                 | iequest nas no                   |                 |                  |                  |                 |       |

| REGISTER 7      | -13: IEC3:      | INTERRUPT                         |                | ONTROL RE        | GISTER 3         |                 |       |  |  |

|-----------------|-----------------|-----------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|

| U-0             | U-0             | R/W-0                             | R/W-0          | R/W-0            | U-0              | U-0             | R/W-0 |  |  |

| —               | _               | DMA5IE                            | DCIIE          | DCIEIE           | —                | —               | C2IE  |  |  |

| bit 15          |                 |                                   | 1              | 1                |                  |                 | bit 8 |  |  |

| R/W-0           | R/W-0           | R/W-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| C2RXIE          | INT4IE          | INT3IE                            | T9IE           | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |  |  |

| bit 7           |                 |                                   |                |                  |                  |                 | bit 0 |  |  |

| Legend:         |                 |                                   |                |                  |                  |                 |       |  |  |

| R = Readable    | bit             | W = Writable                      | bit            | U = Unimpler     | mented bit, read | as '0'          |       |  |  |

| -n = Value at F |                 | '1' = Bit is set                  |                | '0' = Bit is cle |                  | x = Bit is unkr | nown  |  |  |

|                 |                 |                                   |                |                  |                  |                 |       |  |  |

| bit 15-14       | Unimplemen      | ted: Read as '                    | 0'             |                  |                  |                 |       |  |  |

| bit 13          | DMA5IE: DM      | A Channel 5 D                     | ata Transfer ( | Complete Interi  | rupt Enable bit  |                 |       |  |  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |  |  |

| bit 12          | DCIIE: DCI E    | vent Interrupt E                  | Enable bit     |                  |                  |                 |       |  |  |

|                 |                 | request enable                    |                |                  |                  |                 |       |  |  |

|                 | -               | request not ena                   |                |                  |                  |                 |       |  |  |

| bit 11          |                 | Error Interrupt                   |                |                  |                  |                 |       |  |  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |  |  |

| bit 10-9        | Unimplemen      | Unimplemented: Read as '0'        |                |                  |                  |                 |       |  |  |

| bit 8           | C2IE: ECAN2     | 2 Event Interrup                  | ot Enable bit  |                  |                  |                 |       |  |  |

|                 | •               | request enable<br>request not ena |                |                  |                  |                 |       |  |  |

| bit 7           | C2RXIE: ECA     | AN2 Receive D                     | ata Ready Int  | errupt Enable I  | bit              |                 |       |  |  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |       |  |  |

| bit 6           | •               | rnal Interrupt 4                  |                |                  |                  |                 |       |  |  |

| bit o           | 1 = Interrupt r | request enable<br>request not ena | d              |                  |                  |                 |       |  |  |

| bit 5           | •               | nal Interrupt 3                   |                |                  |                  |                 |       |  |  |

|                 | 1 = Interrupt r | request enable<br>request not ena | d              |                  |                  |                 |       |  |  |

| bit 4           | -               | Interrupt Enab                    |                |                  |                  |                 |       |  |  |

|                 | 1 = Interrupt r | request enable                    | d              |                  |                  |                 |       |  |  |

| bit 3           | -               | request not ena                   |                |                  |                  |                 |       |  |  |

| DIL 3           | 1 = Interrupt r | Interrupt Enab                    | d              |                  |                  |                 |       |  |  |

| bit 2           |                 | request not ena<br>2 Master Even  |                | nahla hit        |                  |                 |       |  |  |

|                 |                 | request enable                    |                |                  |                  |                 |       |  |  |

|                 |                 | request not ena                   |                |                  |                  |                 |       |  |  |

| bit 1           | -               | 2 Slave Events                    |                | able bit         |                  |                 |       |  |  |

|                 |                 | request enable                    |                |                  |                  |                 |       |  |  |

|                 | -               | request not ena                   |                |                  |                  |                 |       |  |  |

| bit 0           |                 | Interrupt Enab                    |                |                  |                  |                 |       |  |  |

|                 | •               | request enable<br>request not ena |                |                  |                  |                 |       |  |  |

| U-0           | R/W-1                                                        | R/W-0                                    | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|---------------|--------------------------------------------------------------|------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| —             |                                                              | T1IP<2:0>                                |                |                  |                 | OC1IP<2:0>      |       |  |  |  |  |

| bit 15        |                                                              |                                          |                |                  |                 |                 | bi    |  |  |  |  |

|               |                                                              |                                          |                |                  |                 |                 |       |  |  |  |  |

| U-0           | R/W-1                                                        | R/W-0                                    | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| _             |                                                              | IC1IP<2:0>                               |                |                  |                 | INT0IP<2:0>     |       |  |  |  |  |

| bit 7         |                                                              |                                          |                |                  |                 |                 | bi    |  |  |  |  |

| Legend:       |                                                              |                                          |                |                  |                 |                 |       |  |  |  |  |

| R = Readabl   | e bit                                                        | W = Writable I                           | bit            | U = Unimple      | mented bit, rea | id as '0'       |       |  |  |  |  |

| -n = Value at | POR                                                          | '1' = Bit is set                         |                | '0' = Bit is cle |                 | x = Bit is unkn | own   |  |  |  |  |

|               |                                                              |                                          |                |                  |                 |                 |       |  |  |  |  |

| bit 15        | Unimpleme                                                    | ented: Read as 'o                        | )'             |                  |                 |                 |       |  |  |  |  |

| bit 14-12     | T1IP<2:0>:                                                   | Timer1 Interrupt                         | Priority bits  |                  |                 |                 |       |  |  |  |  |

|               | 111 = Interr                                                 | rupt is priority 7 (ł                    | nighest priori | ty interrupt)    |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               |                                                              | upt is priority 1<br>upt source is dis   | abled          |                  |                 |                 |       |  |  |  |  |

| bit 11        |                                                              | ented: Read as '                         |                |                  |                 |                 |       |  |  |  |  |

| bit 10-8      | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)   |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | 001 = Interrupt is priority 1                                |                                          |                |                  |                 |                 |       |  |  |  |  |

|               |                                                              | upt source is dis                        | abled          |                  |                 |                 |       |  |  |  |  |

| bit 7         | Unimpleme                                                    | ented: Read as 'o                        | )'             |                  |                 |                 |       |  |  |  |  |

| bit 6-4       | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits  |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | 111 = Interr                                                 | rupt is priority 7 (I                    | nighest priori | ty interrupt)    |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               |                                                              | upt is priority 1                        | ablad          |                  |                 |                 |       |  |  |  |  |

| bit 3         |                                                              | upt source is disa<br>ented: Read as 'o  |                |                  |                 |                 |       |  |  |  |  |

| bit 2-0       | -                                                            |                                          |                | , bite           |                 |                 |       |  |  |  |  |

| DIL 2-0       |                                                              | External Interr<br>upt is priority 7 (I) |                |                  |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          | gricot priori  | , monuply        |                 |                 |       |  |  |  |  |

|               | •                                                            |                                          |                |                  |                 |                 |       |  |  |  |  |

|               | •<br>001 - Interr                                            | upt is priority 1                        |                |                  |                 |                 |       |  |  |  |  |

|               |                                                              |                                          |                |                  |                 |                 |       |  |  |  |  |

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                   |       |                  | STA   | <15:8>                             |       |                 |       |  |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                   |       |                  | ST/   | \<7:0>                             |       |                 |       |  |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at P                   | POR   | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

|                   |       |                  | STB   | <15:8>           |                 |                    |       |  |

| bit 15            |       |                  |       |                  |                 |                    | bit 8 |  |

|                   |       |                  |       |                  |                 |                    |       |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|                   |       |                  | STE   | 3<7:0>           |                 |                    |       |  |

| bit 7             |       |                  |       |                  |                 |                    | bit 0 |  |

|                   |       |                  |       |                  |                 |                    |       |  |

| Legend:           |       |                  |       |                  |                 |                    |       |  |

| R = Readable      | bit   | W = Writable I   | bit   | U = Unimpler     | mented bit, rea | id as '0'          |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |

|                   |       |                  |       |                  |                 |                    |       |  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

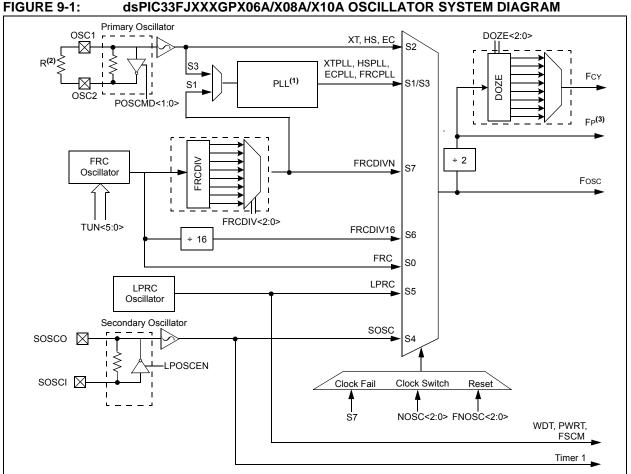

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, not intended to it is be а comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

A simplified diagram of the oscillator system is shown in Figure 9-1.

Note 1: See Figure 9-2 for PLL details.

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 M $\Omega$  must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while Fcy refers to the clock source for the CPU. Throughout this document FP and Fcy are used interchangeably, except in the case of Doze mode. FP and Fcy will be different when Doze mode is used in any ratio other than 1:1, which is the default.

### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXGPX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| btss | PORTB, #13 | i | Next Instruction                |

|      |            |   |                                 |

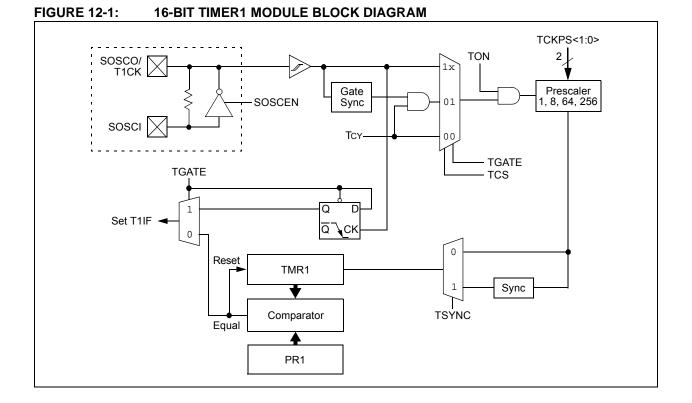

### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### TABLE 23-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                            |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                            |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                        |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                             |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                 |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                             |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                          |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2,<br>[W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2,<br>[W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2,<br>[W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2,<br>[W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| TABLE 23-2:        |                      | INSTRU          | UCTION SET OVERVIE                  | -                                      |               |                |                          |

|--------------------|----------------------|-----------------|-------------------------------------|----------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                     | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 29                 | DIV                  | DIV.S           | Wm, Wn                              | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD          | Wm,Wn                               | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.U           | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.UD          | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF            | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |

| 31                 | DO                   | DO              | #lit14,Expr                         | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |

|                    |                      | DO              | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |

| 32                 | ED                   | ED              | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC            | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH            | Wns,Wnd                             | Swap Wns with Wnd                      | 1             | 1              | None                     |

| 35                 | FBCL                 | FBCL            | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |

| 36                 | FF1L                 | FF1L            | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1             | 1              | С                        |

| 37                 | FF1R                 | FF1R            | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1             | 1              | С                        |

| 38                 | GOTO                 | GOTO            | Expr                                | Go to address                          | 2             | 2              | None                     |

|                    |                      | GOTO            | Wn                                  | Go to indirect                         | 1             | 2              | None                     |

| 39                 | INC                  | INC             | f                                   | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC             | f,WREG                              | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC             | Ws,Wd                               | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2            | f                                   | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2            | f,WREG                              | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2            | Ws,Wd                               | Wd = Ws + 2                            | 1             | 1              | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR             | f                                   | f = f .IOR. WREG                       | 1             | 1              | N,Z                      |

|                    |                      | IOR             | f,WREG                              | WREG = f .IOR. WREG                    | 1             | 1              | N,Z                      |

|                    |                      | IOR             | #lit10,Wn                           | Wd = lit10 .IOR. Wd                    | 1             | 1              | N,Z                      |

|                    |                      | IOR             | Wb,Ws,Wd                            | Wd = Wb .IOR. Ws                       | 1             | 1              | N,Z                      |

|                    |                      | IOR             | Wb,#lit5,Wd                         | Wd = Wb .IOR. lit5                     | 1             | 1              | N,Z                      |

| 42                 | LAC                  | LAC             | Wso,#Slit4,Acc                      | Load Accumulator                       | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK             | #lit14                              | Link Frame Pointer                     | 1             | 1              | None                     |

| 44                 | LSR                  | LSR             | f                                   | f = Logical Right Shift f              | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR             | f,WREG                              | WREG = Logical Right Shift f           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR             | Ws,Wd                               | Wd = Logical Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR             | Wb,Wns,Wnd                          | Wnd = Logical Right Shift Wb by Wns    | 1             | 1              | N,Z                      |

|                    |                      | LSR             | Wb,#lit5,Wnd                        | Wnd = Logical Right Shift Wb by lit5   | 1             | 1              | N,Z                      |

| 45                 | MAC                  | MAC             | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd             | Square and Accumulate                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 46                 | MOV                  | MOV             | f,Wn                                | Move f to Wn                           | 1             | 1              | None                     |

|                    |                      | MOV             | f                                   | Move f to f                            | 1             | 1              | None                     |

|                    |                      | MOV             | f,WREG                              | Move f to WREG                         | 1             | 1              | N,Z                      |

|                    |                      | MOV             | #lit16,Wn                           | Move 16-bit literal to Wn              | 1             | 1              | None                     |

|                    |                      | MOV.b           | #lit8,Wn                            | Move 8-bit literal to Wn               | 1             | 1              | None                     |

|                    |                      | MOV             | Wn,f                                | Move Wn to f                           | 1             | 1              | None                     |

|                    |                      | MOV             | Wso,Wdo                             | Move Ws to Wd                          | 1             | 1              | None                     |

|                    |                      | MOV             | WREG, f                             | Move WREG to f                         | 1             | 1              | None                     |

|                    |                      | MOV.D           | Wns,Wd                              | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |

|                    |                      | MOV.D           | Ws,Wnd                              | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |

| 47                 | MOVSAC               | MOVSAC          | Acc,Wx,Wxd,Wy,Wyd,AWB               | Prefetch and store accumulator         | 1             | 1              | None                     |

#### 1110

|              |        |                                                                                |                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |                                                                                                            |  |  |  |

|--------------|--------|--------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                                                                 | Min                | Тур <sup>(1)</sup>                                                                                                                                                                                                                                                                    | Max        | Units  | Conditions                                                                                                 |  |  |  |

|              | VIL    | Input Low Voltage                                                              |                    |                                                                                                                                                                                                                                                                                       |            |        |                                                                                                            |  |  |  |

| DI10         |        | I/O pins                                                                       | Vss                | —                                                                                                                                                                                                                                                                                     | 0.2 VDD    | V      |                                                                                                            |  |  |  |

| DI15         |        | MCLR                                                                           | Vss                | _                                                                                                                                                                                                                                                                                     | 0.2 VDD    | V      |                                                                                                            |  |  |  |

| DI16         |        | I/O Pins with OSC1 or SOSCI                                                    | Vss                | _                                                                                                                                                                                                                                                                                     | 0.2 VDD    | V      |                                                                                                            |  |  |  |

| DI18         |        | I/O Pins with I <sup>2</sup> C                                                 | Vss                | _                                                                                                                                                                                                                                                                                     | 0.3 VDD    | V      | SMBus disabled                                                                                             |  |  |  |

| DI19         |        | I/O Pins with I <sup>2</sup> C                                                 | Vss                | —                                                                                                                                                                                                                                                                                     | 0.8 V      | V      | SMBus enabled                                                                                              |  |  |  |

|              | Vih    | Input High Voltage                                                             |                    |                                                                                                                                                                                                                                                                                       |            |        |                                                                                                            |  |  |  |

| DI20         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup> | 0.7 Vdd<br>0.7 Vdd | _                                                                                                                                                                                                                                                                                     | Vdd<br>5.5 | V<br>V |                                                                                                            |  |  |  |

| DI28         |        | SDAx, SCLx                                                                     | 0.7 Vdd            | _                                                                                                                                                                                                                                                                                     | 5.5        | V      | SMBus disabled                                                                                             |  |  |  |

| DI29         |        | SDAx, SCLx                                                                     | 2.1                | —                                                                                                                                                                                                                                                                                     | 5.5        | V      | SMBus enabled                                                                                              |  |  |  |

|              | ICNPU  | CNx Pull-up Current                                                            |                    |                                                                                                                                                                                                                                                                                       |            |        |                                                                                                            |  |  |  |

| DI30         |        |                                                                                | 50                 | 250                                                                                                                                                                                                                                                                                   | 400        | μA     | VDD = 3.3V, VPIN = VSS                                                                                     |  |  |  |

| DI50         | lı∟    | Input Leakage Current <sup>(2,3)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup>  | _                  | _                                                                                                                                                                                                                                                                                     | ±2         | μA     | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                                                           |  |  |  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                  | —                                                                                                                                                                                                                                                                                     | ±1         | μA     | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +85°C                      |  |  |  |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                  | —                                                                                                                                                                                                                                                                                     | ±2         | μA     | Shared with external reference pins, -40°C $\leq$ TA $\leq$ +85°C                                          |  |  |  |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | _                  | —                                                                                                                                                                                                                                                                                     | ±3.5       | μA     | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +125°C                        |  |  |  |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                        | —                  | —                                                                                                                                                                                                                                                                                     | ±8         | μA     | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                   |  |  |  |

| DI55         |        | MCLR                                                                           | —                  | _                                                                                                                                                                                                                                                                                     | ±2         | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                   |  |  |  |

| DI56         |        | OSC1                                                                           | —                  | —                                                                                                                                                                                                                                                                                     | ±2         | μA     | $\label{eq:VSS} \begin{split} &Vss \leq V PIN \leq V DD, \\ &XT \text{ and } HS \text{ modes} \end{split}$ |  |  |  |

#### TABLE 25-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

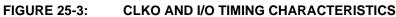

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |                    |     |       |            |  |

|--------------------|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Character                         | istic                                                                                                                                                                                                                                                                                 | Min | Typ <sup>(1)</sup> | Max | Units | Conditions |  |

| DO31               | TioR   | Port Output Rise Tim              |                                                                                                                                                                                                                                                                                       | 10  | 25                 | ns  |       |            |  |

| DO32               | TIOF   | Port Output Fall Time             |                                                                                                                                                                                                                                                                                       | _   | 10                 | 25  | ns    | _          |  |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                                                                                                                                                                                                                                                       | 20  |                    |     | ns    | —          |  |

| DI40               | Trbp   | CNx High or Low Tim               | 2                                                                                                                                                                                                                                                                                     |     |                    | TCY | _     |            |  |

|  | TABLE 25-20: | <b>I/O TIMING REQUIREMENTS</b> |

|--|--------------|--------------------------------|

|--|--------------|--------------------------------|