Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

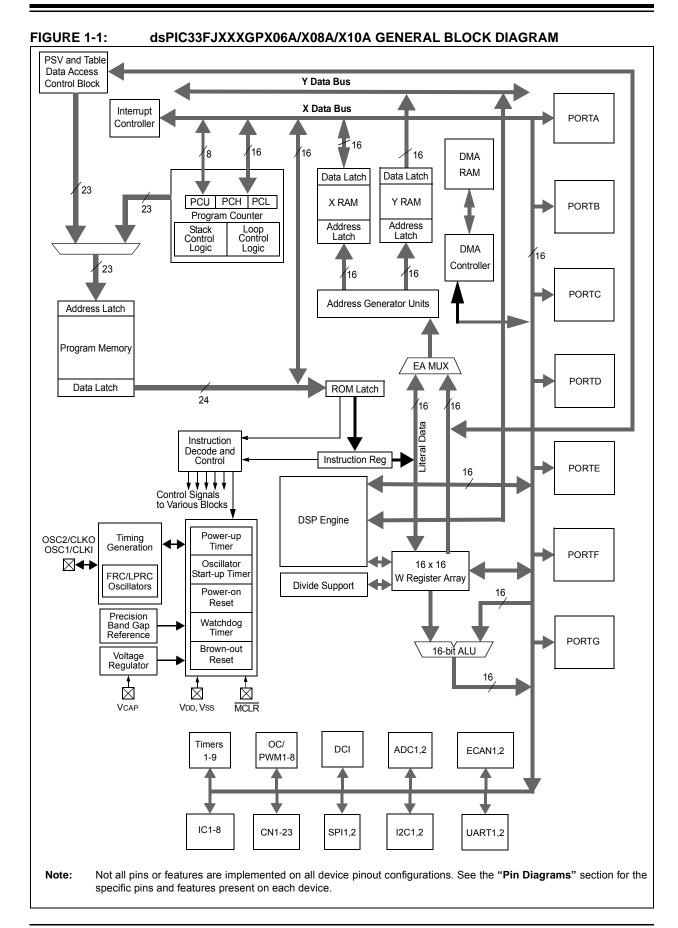

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp306at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0                                                                                                                           | U-0                                    | R/W-0          | R/W-0              | R-0             | R-0              | R-0   |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|--------------------|-----------------|------------------|-------|--|--|--|--|--|--|

| —               | —                                                                                                                             | —                                      | US             | EDT <sup>(1)</sup> |                 | DL<2:0>          |       |  |  |  |  |  |  |

| bit 15          |                                                                                                                               |                                        |                |                    |                 |                  | bit   |  |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                         | R/W-1                                  | R/W-0          | R/C-0              | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |  |  |

| SATA            | SATB                                                                                                                          | SATDW                                  | ACCSAT         | IPL3(2)            | PSV             | RND              | IF    |  |  |  |  |  |  |

| bit 7           | ·                                                                                                                             |                                        |                | ·                  |                 | ·                | bit   |  |  |  |  |  |  |

| Legend:         |                                                                                                                               | C = Clear onl                          | y bit          |                    |                 |                  |       |  |  |  |  |  |  |

| R = Readable    | e bit                                                                                                                         | W = Writable                           | bit            | -n = Value at      | POR             | '1' = Bit is set |       |  |  |  |  |  |  |

| 0' = Bit is cle | ared                                                                                                                          | 'x = Bit is unk                        | nown           | U = Unimpler       | nented bit, rea | d as '0'         |       |  |  |  |  |  |  |

| bit 15-13       | Unimplemen                                                                                                                    | ted: Read as '                         | 0'             |                    |                 |                  |       |  |  |  |  |  |  |

| bit 12          | US: DSP Mul                                                                                                                   | tiply Unsigned                         | Signed Contr   | ol bit             |                 |                  |       |  |  |  |  |  |  |

|                 | Ų                                                                                                                             | 1 = DSP engine multiplies are unsigned |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | •                                                                                                                             | ne multiplies a                        | •              | (1)                |                 |                  |       |  |  |  |  |  |  |

| bit 11          | -                                                                                                                             | D Loop Termina                         |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | <ul> <li>⊥ = Terminate</li> <li>0 = No effect</li> </ul>                                                                      | e executing DO                         | loop at end o  | f current loop it  | eration         |                  |       |  |  |  |  |  |  |

| bit 10-8        | DL<2:0>: DO                                                                                                                   | Loop Nesting                           | Level Status b | oits               |                 |                  |       |  |  |  |  |  |  |

|                 | 111 = 7 DO loops active                                                                                                       |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | •                                                                                                                             |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | 001 = 1 DO lo                                                                                                                 | 001 = 1 DO loop active                 |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | 000 = 0 DO loops active                                                                                                       |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 7           | SATA: AccA Saturation Enable bit                                                                                              |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 |                                                                                                                               | ator A saturatio                       |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 6           | 0 = Accumulator A saturation disabled<br><b>SATB:</b> AccB Saturation Enable bit                                              |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit o           | 1 = Accumulator B saturation enabled                                                                                          |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | 0 = Accumulator B saturation disabled                                                                                         |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 5           | SATDW: Data Space Write from DSP Engine Saturation Enable bit                                                                 |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | 1 = Data space write saturation enabled<br>0 = Data space write saturation disabled                                           |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 4           | <ul> <li>0 = Data space write saturation disabled</li> <li>ACCSAT: Accumulator Saturation Mode Select bit</li> </ul>          |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 |                                                                                                                               | ration (super s                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 |                                                                                                                               | ration (normal                         |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 3           | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |                                        |                |                    |                 |                  |       |  |  |  |  |  |  |

| bit 2           |                                                                                                                               | n Space Visibil                        |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 |                                                                                                                               | space visible ir                       |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | 0 = Program                                                                                                                   | space not visib                        | le in data spa | се                 |                 |                  |       |  |  |  |  |  |  |

| bit 1           |                                                                                                                               | ng Mode Seleo                          |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | ,                                                                                                                             | onventional) ro<br>(convergent) r      | 0              |                    |                 |                  |       |  |  |  |  |  |  |

| bit 0           |                                                                                                                               | Fractional Mul                         | -              |                    |                 |                  |       |  |  |  |  |  |  |

|                 |                                                                                                                               | ode enabled fo                         |                |                    |                 |                  |       |  |  |  |  |  |  |

|                 | ∩ = Fractiona                                                                                                                 | I mode enable                          | d for DSP mul  | Itinly ons         |                 |                  |       |  |  |  |  |  |  |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

Note 1: This bit will always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXGPX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXGPX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXGPX06A/X08A/X10A is a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- · Conventional or convergent rounding (RND)

- Automatic saturation on/off for AccA (SATA)

- Automatic saturation on/off for AccB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

Table 3-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | A = A + x2              | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

| TABLE 4-2  | 1: E | CAN2 R  | EGISTE    | R MAP   | WHEN (  |         | 1.WIN =   | 0 OR 1   |                   | dsPIC33F | JXXXC     | GP706A | \/708A  | /710A D   | EVICE             | <u>S ONL'</u> | Y      |               |

|------------|------|---------|-----------|---------|---------|---------|-----------|----------|-------------------|----------|-----------|--------|---------|-----------|-------------------|---------------|--------|---------------|

| File Name  | Addr | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10    | Bit 9    | Bit 8             | Bit 7    | Bit 6     | Bit 5  | Bit 4   | Bit 3     | Bit 2             | Bit 1         | Bit 0  | All<br>Resets |

| C2CTRL1    | 0500 | _       | _         | CSIDL   | ABAT    | _       | RI        | EQOP<2:0 | >                 | OPN      | /IODE<2:0 | ∧      |         | CANCAP    | _                 | _             | WIN    | 0480          |

| C2CTRL2    | 0502 | _       | _         | _       | _       | _       | _         | —        | _                 | _        | _         | _      |         | C         | NCNT<4:           | )>            |        | 0000          |

| C2VEC      | 0504 | _       | _         | _       |         | FI      | LHIT<4:0> |          |                   | —        |           |        |         | ICODE<6:0 | )>                |               |        | 0000          |

| C2FCTRL    | 0506 | C       | MABS<2:0> | >       | _       | _       | -         | _        | _                 | —        | _         | —      |         |           | FSA<4:0>          |               |        | 0000          |

| C2FIFO     | 0508 | _       | _         |         |         | FBP<5   | :0>       |          |                   | _        | _         |        |         | FNRE      | 3<5:0>            |               |        | 0000          |

| C2INTF     | 050A | _       | _         | ТХВО    | TXBP    | RXBP    | TXWAR     | RXWAR    | EWARN             | IVRIF    | WAKIF     | ERRIF  | _       | FIFOIF    | RBOVIF            | RBIF          | TBIF   | 0000          |

| C2INTE     | 050C | _       | _         | _       | _       | _       | _         | _        | _                 | IVRIE    | WAKIE     | ERRIE  | _       | FIFOIE    | RBOVIE            | RBIE          | TBIE   | 0000          |

| C2EC       | 050E |         |           |         | TERRCN  | Γ<7:0>  |           |          |                   |          |           |        | RERRC   | NT<7:0>   |                   |               |        | 0000          |

| C2CFG1     | 0510 | _       | _         | _       | _       | _       | _         | _        | _                 | SJW<1    | 1:0>      |        |         | BRP       | <5:0>             |               |        | 0000          |

| C2CFG2     | 0512 | _       | WAKFIL    | _       | _       | _       | SE        | G2PH<2:0 | )>                | SEG2PHTS | SAM       | SE     | EG1PH<2 | 2:0>      | P                 | RSEG<2:0      | 0>     | 0000          |

| C2FEN1     | 0514 | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10   | FLTEN9   | FLTEN8            | FLTEN7   | FLTEN6    | FLTEN5 | FLTEN4  | FLTEN3    | FLTEN2            | FLTEN1        | FLTEN0 | FFFF          |

| C2FMSKSEL1 | 0518 | F7MSł   | <<1:0>    | F6MSI   | <<1:0>  | F5MSk   | <1:0>     | F4MS     | <b>&lt;</b> <1:0> | F3MSK<   | <1:0>     | F2MSH  | <1:0>   | F1MS      | <b>&lt;</b> <1:0> | F0MS          | K<1:0> | 0000          |

| C2FMSKSEL2 | 051A | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>    | F12MS    | K<1:0>            | F11MSK   | <1:0>     | F10MS  | K<1:0>  | F9MSł     | <<1:0>            | F8MS          | K<1:0> | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 FOR dsPIC33FJXXXGP706A/708A/710A DEVICES ONLY **TABLE 4-22:**

| File Name | Addr          | Bit 15  | Bit 14      | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9   | Bit 8      | Bit 7     | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-------------|-------------|------------|------------|---------|---------|------------|-----------|-------------|-------------|------------|------------|---------|---------|---------|---------------|

|           | 0500-<br>051E |         |             |             |            |            |         | See     | definition | when WIN  | = x         |             |            |            |         |         |         |               |

| C2RXFUL1  | 0520          | RXFUL15 | RXFUL14     | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7    | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C2RXFUL2  | 0522          | RXFUL31 | RXFUL30     | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23   | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C2RXOVF1  | 0528          | RXOVF15 | RXOVF14     | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF09 | RXOVF08    | RXOVF7    | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C2RXOVF2  | 052A          | RXOVF31 | RXOVF30     | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23   | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C2TR01CON | 0530          | TXEN1   | TX<br>ABAT1 | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PF   | RI<1:0>    | TXEN0     | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C2TR23CON | 0532          | TXEN3   | TX<br>ABAT3 | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF   | RI<1:0>    | TXEN2     | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C2TR45CON | 0534          | TXEN5   | TX<br>ABAT5 | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF   | RI<1:0>    | TXEN4     | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C2TR67CON | 0536          | TXEN7   | TX<br>ABAT7 | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PF   | RI<1:0>    | TXEN6     | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C2RXD     | 0540          |         |             |             |            |            |         |         | Recieved [ | Data Word |             |             |            |            |         |         |         | xxxx          |

| C2TXD     | 0542          |         |             |             |            |            |         |         | Transmit D | ata Word  |             |             |            |            |         |         |         | xxxx          |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (e.g., [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when:

- BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing).

- 2. The BREN bit is set in the XBREV register.

- 3. The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for Register Indirect with Pre-Increment or Post-Increment Addressing and word sized data writes. It will not function for any other addressing mode or for byte sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed<br>Addressing should not be enabled |

|-------|------------------------------------------------------------------------|

|       | together. In the event that the user                                   |

|       | attempts to do so, Bit-Reversed Address-                               |

|       | ing will assume priority when active for the                           |

|       | X WAGU and X WAGU Modulo Addressing                                    |

|       | will be disabled. However, Modulo                                      |

|       | Addressing will continue to function in the X                          |

|       | RAGU.                                                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |

|------------------|--------------------------------------|-------------------|-------------------|------------------------------------|

| 54               | 46                                   | 0x000070          | 0x000170          | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072          | 0x000172          | T6 – Timer6                        |

| 56               | 48                                   | 0x000074          | 0x000174          | T7 – Timer7                        |

| 57               | 49                                   | 0x000076          | 0x000176          | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078          | 0x000178          | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A          | 0x00017A          | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C          | 0x00017C          | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E          | 0x00017E          | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080          | 0x000180          | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082          | 0x000182          | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084          | 0x000184          | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086          | 0x000186          | Reserved                           |

| 66               | 58                                   | 0x000088          | 0x000188          | Reserved                           |

| 67               | 59                                   | 0x00008A          | 0x00018A          | DCIE – DCI Error                   |

| 68               | 60                                   | 0x00008C          | 0x00018C          | DCID – DCI Transfer Done           |

| 69               | 61                                   | 0x00008E          | 0x00018E          | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090          | 0x000190          | Reserved                           |

| 71               | 63                                   | 0x000092          | 0x000192          | Reserved                           |

| 72               | 64                                   | 0x000094          | 0x000194          | Reserved                           |

| 73               | 65                                   | 0x000096          | 0x000196          | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098          | 0x000198          | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A          | 0x00019A          | Reserved                           |

| 76               | 68                                   | 0x00009C          | 0x00019C          | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E          | 0x00019E          | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0          | 0x0001A0          | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2          | 0x0001A2          | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-0x0000FE | 0x0001A4-0x0001FE | Reserved                           |

### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| REGISTER /      | -3: INTCC                                                                                                                                                    | INT: INTERR                           | UPICONTR        | COL REGISTE       | :K 1       |                 |       |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------------------|------------|-----------------|-------|--|--|--|--|

| R/W-0           | R/W-0                                                                                                                                                        | R/W-0                                 | R/W-0           | R/W-0             | R/W-0      | R/W-0           | R/W-0 |  |  |  |  |

| NSTDIS          | OVAERR                                                                                                                                                       | OVBERR                                | COVAERR         | COVBERR           | OVATE      | OVBTE           | COVTE |  |  |  |  |

| bit 15          |                                                                                                                                                              |                                       |                 |                   |            |                 | bit 8 |  |  |  |  |

| <b></b>         |                                                                                                                                                              |                                       |                 |                   |            |                 |       |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                        | R/W-0                                 | R/W-0           | R/W-0             | R/W-0      | R/W-0           | U-0   |  |  |  |  |

| SFTACERR        | DIV0ERR                                                                                                                                                      | DMACERR                               | MATHERR         | ADDRERR           | STKERR     | OSCFAIL         | —     |  |  |  |  |

| bit 7           |                                                                                                                                                              |                                       |                 |                   |            |                 | bit 0 |  |  |  |  |

|                 |                                                                                                                                                              |                                       |                 |                   |            |                 |       |  |  |  |  |

| Legend:         | L :4                                                                                                                                                         |                                       | L :4            |                   |            | d = = (0)       |       |  |  |  |  |

| R = Readable    |                                                                                                                                                              | W = Writable                          |                 | U = Unimplem      |            |                 |       |  |  |  |  |

| -n = Value at F | 'UR                                                                                                                                                          | '1' = Bit is set                      |                 | '0' = Bit is clea | irea       | x = Bit is unkr | IOWN  |  |  |  |  |

| bit 15          |                                                                                                                                                              | errupt Nesting D                      | )isabla hit     |                   |            |                 |       |  |  |  |  |

| bit 15          |                                                                                                                                                              | nesting is disat                      |                 |                   |            |                 |       |  |  |  |  |

|                 | •                                                                                                                                                            | nesting is enab                       |                 |                   |            |                 |       |  |  |  |  |

| bit 14          | OVAERR: Ac                                                                                                                                                   | cumulator A O                         | verflow Trap F  | lag bit           |            |                 |       |  |  |  |  |

|                 |                                                                                                                                                              | caused by ove                         |                 |                   |            |                 |       |  |  |  |  |

|                 | •                                                                                                                                                            | not caused by                         |                 |                   |            |                 |       |  |  |  |  |

| bit 13          | OVBERR: Accumulator B Overflow Trap Flag bit                                                                                                                 |                                       |                 |                   |            |                 |       |  |  |  |  |

|                 | <ul> <li>1 = Trap was caused by overflow of Accumulator B</li> <li>0 = Trap was not caused by overflow of Accumulator B</li> </ul>                           |                                       |                 |                   |            |                 |       |  |  |  |  |

| bit 12          | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit                                                                                            |                                       |                 |                   |            |                 |       |  |  |  |  |

| Sit 12          | 1 = Trap was caused by catastrophic overflow of Accumulator A                                                                                                |                                       |                 |                   |            |                 |       |  |  |  |  |

|                 |                                                                                                                                                              |                                       |                 | overflow of Accu  |            |                 |       |  |  |  |  |

| bit 11          | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit                                                                                                   |                                       |                 |                   |            |                 |       |  |  |  |  |

|                 | <ul> <li>1 = Trap was caused by catastrophic overflow of Accumulator B</li> <li>0 = Trap was not caused by catastrophic overflow of Accumulator B</li> </ul> |                                       |                 |                   |            |                 |       |  |  |  |  |

| bit 10          | -                                                                                                                                                            | -                                     | -               |                   |            |                 |       |  |  |  |  |

|                 | <b>OVATE:</b> Accumulator A Overflow Trap Enable bit<br>1 = Trap overflow of Accumulator A                                                                   |                                       |                 |                   |            |                 |       |  |  |  |  |

|                 | 0 = Trap disa                                                                                                                                                |                                       |                 |                   |            |                 |       |  |  |  |  |

| bit 9           | OVBTE: Acc                                                                                                                                                   | umulator B Ove                        | erflow Trap En  | able bit          |            |                 |       |  |  |  |  |

|                 | 1 = Trap over<br>0 = Trap disa                                                                                                                               | rflow of Accum<br>bled                | ulator B        |                   |            |                 |       |  |  |  |  |

| bit 8           | COVTE: Cata                                                                                                                                                  | astrophic Overf                       | low Trap Enat   | ole bit           |            |                 |       |  |  |  |  |

|                 | <ul> <li>1 = Trap on catastrophic overflow of Accumulator A or B enabled</li> <li>0 = Trap disabled</li> </ul>                                               |                                       |                 |                   |            |                 |       |  |  |  |  |

| bit 7           | •                                                                                                                                                            | Shift Accumula                        | tor Error Statu | us bit            |            |                 |       |  |  |  |  |

|                 | 1 = Math erro                                                                                                                                                | or trap was cau                       | sed by an inva  | lid accumulator   |            |                 |       |  |  |  |  |

| hit C           |                                                                                                                                                              |                                       | •               | invalid accumul   | ator shift |                 |       |  |  |  |  |

| bit 6           | -                                                                                                                                                            | rithmetic Error S<br>or trap was caus |                 | a by zero         |            |                 |       |  |  |  |  |

|                 |                                                                                                                                                              | or trap was cau                       | •               | •                 |            |                 |       |  |  |  |  |

| bit 5           |                                                                                                                                                              | DMA Controller                        | -               | -                 |            |                 |       |  |  |  |  |

|                 | 1 = DMA con                                                                                                                                                  | troller error trap                    | has occurred    | 1                 |            |                 |       |  |  |  |  |

|                 | 0 = DMA con                                                                                                                                                  | troller error trap                    | o has not occu  | rred              |            |                 |       |  |  |  |  |

| bit 4           | MATHERR: A                                                                                                                                                   | Arithmetic Error                      | Status bit      |                   |            |                 |       |  |  |  |  |

|                 |                                                                                                                                                              | or trap has occu                      |                 |                   |            |                 |       |  |  |  |  |

|                 | v = wath error                                                                                                                                               | or trap has not o                     | occurred        |                   |            |                 |       |  |  |  |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| R/W-0                | U-0                    | U-0                    | U-0                    | U-0                                | U-0                    | U-0                | U-0        |  |  |

|----------------------|------------------------|------------------------|------------------------|------------------------------------|------------------------|--------------------|------------|--|--|

| FORCE <sup>(1)</sup> | —                      | —                      | -                      | —                                  | —                      | —                  | —          |  |  |

| bit 15               |                        |                        |                        |                                    |                        |                    | bit 8      |  |  |

|                      |                        |                        |                        |                                    |                        |                    |            |  |  |

| U-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                              | R/W-0                  | R/W-0              | R/W-0      |  |  |

| —                    | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2)                         | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2)         | IRQSEL0(2) |  |  |

| bit 7                |                        |                        |                        |                                    |                        |                    | bit 0      |  |  |

|                      |                        |                        |                        |                                    |                        |                    |            |  |  |

| Legend:              |                        |                        |                        |                                    |                        |                    |            |  |  |

| R = Readable         | bit                    | W = Writable           | bit                    | U = Unimplemented bit, read as '0' |                        |                    |            |  |  |

| -n = Value at F      | POR                    | '1' = Bit is set       |                        | '0' = Bit is cle                   | ared                   | x = Bit is unknown |            |  |  |

|                      |                        |                        |                        |                                    |                        |                    |            |  |  |

| bit 15               | FORCE: Force           | e DMA Transfe          | er bit <sup>(1)</sup>  |                                    |                        |                    |            |  |  |

|                      |                        | ingle DMA tran         | •                      | ,                                  |                        |                    |            |  |  |

|                      |                        | DMA transfer           | -                      | MA request                         |                        |                    |            |  |  |

| bit 14-7             | Unimplemen             | ted: Read as '         | 0'                     |                                    |                        |                    |            |  |  |

| bit 6-0              | IRQSEL<6:0>            | DMA Periph             | eral IRQ Numl          | ber Select bits                    | (2)                    |                    |            |  |  |

|                      | 1111111 <b>= D</b>     | MAIRQ127 se            | lected to be C         | hannel DMARI                       | EQ                     |                    |            |  |  |

|                      | •                      |                        |                        |                                    |                        |                    |            |  |  |

|                      | •                      |                        |                        |                                    |                        |                    |            |  |  |

|                      | •                      |                        |                        |                                    |                        |                    |            |  |  |

|                      | 0000000 = DN           | MAIRQ0 select          | ed to be Chan          | nel DMAREQ                         |                        |                    |            |  |  |

|                      |                        |                        |                        |                                    |                        |                    |            |  |  |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

- 2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

#### bit 0 OSWEN: Oscillator Switch Enable bit

bit 1

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This is register is reset only on a Power-on Reset (POR).

#### 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU stops executing instructions

- · The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLK-DIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLK-DIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLK-DIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

Note: The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM.

#### REGISTER 19-27: CITRBnSID: ECAN™ BUFFER n STANDARD IDENTIFIER (n = 0, 1, ..., 31)

|                                        | N-x       |  |  |  |  |  |  |

|----------------------------------------|-----------|--|--|--|--|--|--|

|                                        |           |  |  |  |  |  |  |

|                                        | bit 8     |  |  |  |  |  |  |

| U-0 U-0 U-0 R/W-X R/W-X R/W-X R/W-X R/ | SID<10:6> |  |  |  |  |  |  |

|                                        | N-x       |  |  |  |  |  |  |

| SID<5:0> | SRR | IDE   |

|----------|-----|-------|

| bit 7    |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 12-2  | SID<10:0>: Standard Identifier bits                                                          |

| bit 1     | SRR: Substitute Remote Request bit                                                           |

|           | <ol> <li>1 = Message will request remote transmission</li> <li>0 = Normal message</li> </ol> |

| bit 0     | IDE: Extended Identifier bit                                                                 |

|           | 1 = Message will transmit extended identifier                                                |

0 = Message will transmit standard identifier

### REGISTER 19-28: CITRBnEID: ECAN™ BUFFER n EXTENDED IDENTIFIER (n = 0, 1, ..., 31)

| U-0             | U-0   | U-0              | U-0   | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                 | _     |                  |       |                                    | EID<  | 17:14>          |       |  |

| bit 15          |       |                  |       | ·                                  |       |                 | bit 8 |  |

|                 |       |                  |       |                                    |       |                 |       |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                 |       |                  | EID   | <13:6>                             |       |                 |       |  |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |  |

|                 |       |                  |       |                                    |       |                 |       |  |

| Legend:         |       |                  |       |                                    |       |                 |       |  |

| R = Readable    | bit   | W = Writable I   | oit   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

#### REGISTER 21-5: ADxCHS123: ADCx INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0                | U-0                                                                                                   | U-0                                                                                                                                     | U-0                                                                                                                                                  | U-0                                                                                                                                       | R/W-0                                                                                                  | R/W-0                                                    | R/W-0   |

|--------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------|

| _                  |                                                                                                       |                                                                                                                                         | —                                                                                                                                                    |                                                                                                                                           | CH123                                                                                                  | NB<1:0>                                                  | CH123SB |

| bit 15             | ·                                                                                                     |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          | bit 8   |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

| U-0                | U-0                                                                                                   | U-0                                                                                                                                     | U-0                                                                                                                                                  | U-0                                                                                                                                       | R/W-0                                                                                                  | R/W-0                                                    | R/W-0   |

| _                  | —                                                                                                     | _                                                                                                                                       |                                                                                                                                                      |                                                                                                                                           | CH123                                                                                                  | VA<1:0>                                                  | CH123SA |

| bit 7              |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          | bit C   |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

| Legend:            |                                                                                                       |                                                                                                                                         | .,                                                                                                                                                   |                                                                                                                                           |                                                                                                        |                                                          |         |

| R = Readable       |                                                                                                       | W = Writable b                                                                                                                          | it                                                                                                                                                   | U = Unimplen                                                                                                                              |                                                                                                        |                                                          |         |

| -n = Value at      | POR                                                                                                   | '1' = Bit is set                                                                                                                        |                                                                                                                                                      | '0' = Bit is clea                                                                                                                         | ared                                                                                                   | x = Bit is unk                                           | nown    |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

| bit 15-11          | •                                                                                                     | ted: Read as '0                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

| bit 10-9           |                                                                                                       | 0>: Channel 1,                                                                                                                          | •                                                                                                                                                    | •                                                                                                                                         | •                                                                                                      | S                                                        |         |

|                    |                                                                                                       | s = 1, CHxNB is                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

|                    |                                                                                                       | ative input is A                                                                                                                        |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |

|                    |                                                                                                       | ative input is Al                                                                                                                       |                                                                                                                                                      |                                                                                                                                           | N7, CH3 negat                                                                                          | ive input is AN                                          | 8       |

|                    |                                                                                                       | I2, CH3 negativ                                                                                                                         | •                                                                                                                                                    |                                                                                                                                           |                                                                                                        |                                                          |         |