Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp310a-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the dsPIC33FJ256GP710A product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit<sup>™</sup> (I2C<sup>™</sup>)" (DS70195)

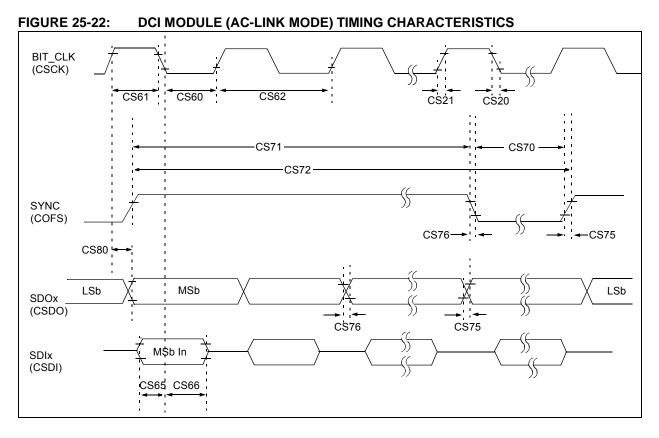

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Section 22. "Direct Memory Access (DMA)" (DS70182)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

#### TABLE 4-24: DCI REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                           | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9      | Bit 8       | Bit 7     | Bit 6  | Bit 5 | Bit 4               | Bit 3               | Bit 2               | Bit 1   | Bit 0  | Reset State         |

|-------------|-------|--------|----------------------------------|---------|--------|--------|-----------|------------|-------------|-----------|--------|-------|---------------------|---------------------|---------------------|---------|--------|---------------------|

| DCICON1     | 0280  | DCIEN  | —                                | DCISIDL | —      | DLOOP  | CSCKD     | CSCKE      | COFSD       | UNFM      | CSDOM  | DJST  |                     |                     | —                   | COFSM1  | COFSM0 | 0000 0000 0000 0000 |

| DCICON2     | 0282  | _      | _                                | _       | _      | BLEN1  | BLEN0     | _          |             | COFSO     | G<3:0> |       | -                   |                     | V                   | VS<3:0> |        | 0000 0000 0000 0000 |

| DCICON3     | 0284  | _      | _                                | _       | _      |        | BCG<11:0> |            |             |           |        |       |                     |                     | 0000 0000 0000 0000 |         |        |                     |

| DCISTAT     | 0286  | _      | _                                | _       | _      | SLOT3  | SLOT2     | SLOT1      | SLOT0       |           | _      | -     | -                   | ROV                 | RFUL                | TUNF    | TMPTY  | 0000 0000 0000 0000 |

| TSCON       | 0288  | TSE15  | TSE14                            | TSE13   | TSE12  | TSE11  | TSE10     | TSE9       | TSE8        | TSE7      | TSE6   | TSE5  | TSE4                | TSE3                | TSE2                | TSE1    | TSE0   | 0000 0000 0000 0000 |

| RSCON       | 028C  | RSE15  | RSE14                            | RSE13   | RSE12  | RSE11  | RSE10     | RSE9       | RSE8        | RSE7      | RSE6   | RSE5  | RSE4                | RSE3                | RSE2                | RSE1    | RSE0   | 0000 0000 0000 0000 |

| RXBUF0      | 0290  |        |                                  |         |        |        |           | Receive E  | Buffer #0 D | ata Regis | ster   |       |                     |                     |                     |         |        | 0000 0000 0000 0000 |

| RXBUF1      | 0292  |        |                                  |         |        |        |           | Receive E  | Buffer #1 D | ata Regis | ster   |       |                     |                     |                     |         |        | 0000 0000 0000 0000 |

| RXBUF2      | 0294  |        |                                  |         |        |        |           | Receive E  | Buffer #2 D | ata Regis | ster   |       |                     |                     |                     |         |        | 0000 0000 0000 0000 |

| RXBUF3      | 0296  |        |                                  |         |        |        |           | Receive E  | Buffer #3 D | ata Regis | ster   |       |                     |                     |                     |         |        | 0000 0000 0000 0000 |

| TXBUF0      | 0298  |        |                                  |         |        |        |           | Transmit I | Buffer #0 D | ata Regi  | ster   |       |                     |                     |                     |         |        | 0000 0000 0000 0000 |

| TXBUF1      | 029A  |        | Transmit Buffer #1 Data Register |         |        |        |           |            |             |           |        |       |                     | 0000 0000 0000 0000 |                     |         |        |                     |

| TXBUF2      | 029C  |        | Transmit Buffer #2 Data Register |         |        |        |           |            |             |           |        |       |                     | 0000 0000 0000 0000 |                     |         |        |                     |

| TXBUF3      | 029E  |        | Transmit Buffer #3 Data Register |         |        |        |           |            |             |           |        |       | 0000 0000 0000 0000 |                     |                     |         |        |                     |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend:

— = unimplemented, read as '0'. Refer to the *"dsPIC33F/PIC24H Family Reference Manual"* for descriptions of register bit fields. Note 1:

### TABLE 4-25: PORTA REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA               | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | _      | TRISA10 | TRISA9 |       | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA               | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA                | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA <sup>(2)</sup> | 06C0 | ODCA15  | ODCA14  | _       | _       | _      | _       | _      |       | _      |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices. Legend:

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-26: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | XXXX          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| REGISTER 7      | -11: IEC1:                         | INTERRUPT                                             | ENABLE C            |                  | GISTER 1        |                 |         |

|-----------------|------------------------------------|-------------------------------------------------------|---------------------|------------------|-----------------|-----------------|---------|

| R/W-0           | R/W-0                              | R/W-0                                                 | R/W-0               | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| U2TXIE          | U2RXIE                             | INT2IE                                                | T5IE                | T4IE             | OC4IE           | OC3IE           | DMA2IE  |

| oit 15          |                                    |                                                       |                     |                  |                 | -               | bi      |

| R/W-0           | R/W-0                              | R/W-0                                                 | R/W-0               | R/W-0            | U-0             | R/W-0           | R/W-0   |

| IC8IE           | IC7IE                              | AD2IE                                                 | INT1IE              | CNIE             | _               | MI2C1IE         | SI2C1IE |

| bit 7           |                                    |                                                       |                     |                  |                 |                 | bi      |

| Legend:         |                                    |                                                       |                     |                  |                 |                 |         |

| R = Readable    | bit                                | W = Writable                                          | bit                 | U = Unimplen     | nented bit, rea | d as '0'        |         |

| -n = Value at F | POR                                | '1' = Bit is set                                      | :                   | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |

| bit 15          | 1 = Interrupt i<br>0 = Interrupt i | RT2 Transmitte<br>request enable<br>request not ena   | d<br>abled          |                  |                 |                 |         |

| bit 14          | 1 = Interrupt i                    | RT2 Receiver I<br>request enable<br>request not ena   | d .                 | le bit           |                 |                 |         |

| bit 13          | 1 = Interrupt i                    | rnal Interrupt 2<br>request enable<br>request not ena | d                   |                  |                 |                 |         |

| bit 12          | 1 = Interrupt i                    | Interrupt Enab<br>request enable<br>request not ena   | d                   |                  |                 |                 |         |

| bit 11          | 1 = Interrupt i                    | Interrupt Enab<br>request enable<br>request not ena   | d                   |                  |                 |                 |         |

| bit 10          | 1 = Interrupt i                    | ut Compare Ch<br>request enable<br>request not ena    | d                   | rupt Enable bit  |                 |                 |         |

| bit 9           | 1 = Interrupt i                    | ut Compare Ch<br>request enable<br>request not ena    | d                   | upt Enable bit   |                 |                 |         |

| bit 8           | 1 = Interrupt i                    | A Channel 2 D<br>request enable<br>request not ena    | d                   | Complete Interr  | upt Enable bit  |                 |         |

| bit 7           | 1 = Interrupt i                    | Capture Chann<br>request enable<br>request not ena    | d                   | Enable bit       |                 |                 |         |

| bit 6           | 1 = Interrupt i                    | Capture Chann<br>request enable<br>request not ena    | d                   | Enable bit       |                 |                 |         |

| bit 5           | AD2IE: ADC2<br>1 = Interrupt i     | -                                                     | Complete Inter<br>d | rupt Enable bit  |                 |                 |         |

| bit 4           | INT1IE: Exter<br>1 = Interrupt r   | rnal Interrupt 1<br>request enable<br>request not ena | Enable bit<br>d     |                  |                 |                 |         |

#### -----

| U-0           | U-0          | U-0                                    | U-0            | R-1               | R-1              | R-1             | R-1   |

|---------------|--------------|----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| —             | _            | —                                      | —              |                   | LSTCH            | +<3:0>          |       |

| oit 15        | ·            |                                        |                |                   |                  |                 | bit   |

| R-0           | R-0          | R-0                                    | R-0            | R-0               | R-0              | R-0             | R-0   |

| PPST7         | PPST6        | PPST5                                  | PPST4          | PPST3             | PPST2            | PPST1           | PPST0 |

| bit 7         |              |                                        |                |                   |                  | I               | bit   |

| Legend:       |              |                                        |                |                   |                  |                 |       |

| R = Readabl   | e bit        | W = Writable                           | bit            | U = Unimplem      | nented bit, read | as '0'          |       |

| -n = Value at | POR          | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 15-12     | Unimplemen   | ted: Read as '                         | 0'             |                   |                  |                 |       |

| bit 11-8      | LSTCH<3:0>   | : Last DMA Ch                          | annel Active t | oits              |                  |                 |       |

|               | 1111 = No DM | MA transfer ha                         | s occurred sin | ce system Res     | et               |                 |       |

|               | 1110-1000 =  |                                        |                |                   |                  |                 |       |

|               |              | lata transfer wa                       |                |                   |                  |                 |       |

|               |              | lata transfer wa<br>lata transfer wa   |                |                   |                  |                 |       |

|               |              | lata transfer wa                       |                |                   |                  |                 |       |

|               |              | lata transfer wa                       |                |                   |                  |                 |       |

|               |              | lata transfer wa                       |                |                   |                  |                 |       |

|               |              | lata transfer wa                       |                |                   |                  |                 |       |

| bit 7         |              | lata transfer wa<br>inel 7 Ping-Por    | -              |                   |                  |                 |       |

|               | 1 = DMA7STE  | B register select<br>register select   | ted            | S Flag bit        |                  |                 |       |

| bit 6         |              | inel 6 Ping-Por                        |                | s Flag bit        |                  |                 |       |

|               |              | B register selec                       | -              |                   |                  |                 |       |

|               |              | A register selec                       |                |                   |                  |                 |       |

| bit 5         | PPST5: Chan  | nel 5 Ping-Por                         | ng Mode Statu  | s Flag bit        |                  |                 |       |

|               | 1 = DMA5STE  | B register selec                       | ted            | -                 |                  |                 |       |

|               | 0 = DMA5STA  | A register selec                       | ted            |                   |                  |                 |       |

| bit 4         | PPST4: Chan  | inel 4 Ping-Por                        | ng Mode Statu  | s Flag bit        |                  |                 |       |

|               |              | B register select<br>A register select |                |                   |                  |                 |       |

| bit 3         | PPST3: Chan  | inel 3 Ping-Por                        | ng Mode Statu  | s Flag bit        |                  |                 |       |

|               |              | B register select<br>A register select |                |                   |                  |                 |       |

| bit 2         | PPST2: Chan  | inel 2 Ping-Por                        | ng Mode Statu  | s Flag bit        |                  |                 |       |

|               | 1 = DMA2STE  | B register select                      | cted           |                   |                  |                 |       |

| bit 1         |              | inel 1 Ping-Por                        |                | s Flao bit        |                  |                 |       |

|               | 1 = DMA1STE  | B register select<br>register select   | cted           |                   |                  |                 |       |

| bit 0         |              | inel 0 Ping-Por                        |                | s Flag bit        |                  |                 |       |

|               |              | B register selec                       | -              |                   |                  |                 |       |

| U-0          | U-0                                                                                                         | U-0                                                              | U-0   | U-0              | U-0                                | U-0                | R/W-0 <sup>(1)</sup> |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------------------|------------------------------------|--------------------|----------------------|--|--|--|

|              | _                                                                                                           |                                                                  | _     | _                | _                                  | _                  | PLLDIV<8>            |  |  |  |

| bit 15       | ·                                                                                                           | ·                                                                | ·     | •                | •                                  | •                  | bit 8                |  |  |  |

| R/W-0        | R/W-0                                                                                                       | R/W-1                                                            | R/W-1 | R/W-0            | R/W-0                              | R/W-0              | R/W-0                |  |  |  |

| R/W-U        | R/W-0                                                                                                       | R/ W- I                                                          |       | IV<7:0>          | R/W-0                              | R/ W-U             | R/W-0                |  |  |  |

| bit 7        |                                                                                                             |                                                                  | FLLD  | 10~7.02          |                                    |                    | bit 0                |  |  |  |

|              |                                                                                                             |                                                                  |       |                  |                                    |                    | DILU                 |  |  |  |

| Legend:      |                                                                                                             |                                                                  |       |                  |                                    |                    |                      |  |  |  |

| -            | Legend:<br>R = Readable bit W = Writable bit                                                                |                                                                  |       |                  | U = Unimplemented bit, read as '0' |                    |                      |  |  |  |

|              |                                                                                                             |                                                                  |       |                  |                                    | x = Bit is unknown |                      |  |  |  |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | ared                               | x = Bit is unl     | known                |  |  |  |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | eared                              | x = Bit is unl     | known                |  |  |  |

| -n = Value a |                                                                                                             | '1' = Bit is set                                                 | -     | ʻ0' = Bit is cle | ared                               | x = Bit is unl     | known                |  |  |  |

|              | Unimpleme                                                                                                   |                                                                  | ʻ0'   |                  |                                    |                    | known                |  |  |  |

| bit 15-9     | Unimpleme                                                                                                   | nted: Read as '                                                  | ʻ0'   |                  |                                    |                    | known                |  |  |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                                    |                    | known                |  |  |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                                    |                    | (nown                |  |  |  |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                                    |                    | (nown                |  |  |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as '                                                  | ʻ0'   |                  |                                    |                    | (nown                |  |  |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                                    |                    | <u>known</u>         |  |  |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                                    |                    | <u>known</u>         |  |  |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                                    |                    | <u>Known</u>         |  |  |  |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)        | ʻ0'   |                  |                                    |                    | <u>Known</u>         |  |  |  |

| bit 15-9     | Unimplemen<br>PLLDIV<8:0<br>111111111<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)<br>= 4 | ʻ0'   |                  |                                    |                    | <u>Known</u>         |  |  |  |

Note 1: This is register is reset only on a Power-on Reset (POR).

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

| R/W-0                 | U-0                           | R/W-0                             | U-0            | U-0              | U-0            | U-0                | U-0  |  |  |  |

|-----------------------|-------------------------------|-----------------------------------|----------------|------------------|----------------|--------------------|------|--|--|--|

| TON                   |                               | TSIDL                             |                |                  |                |                    |      |  |  |  |

| bit 15                |                               | TOIDE                             |                |                  |                |                    | bit  |  |  |  |

|                       |                               |                                   |                |                  |                |                    |      |  |  |  |

| U-0                   | R/W-0                         | R/W-0                             | R/W-0          | R/W-0            | U-0            | R/W-0              | U-0  |  |  |  |

| _                     | TGATE                         | TCKP                              | S<1:0>         | T32              | _              | TCS <sup>(1)</sup> | _    |  |  |  |

| bit 7                 |                               |                                   |                |                  |                |                    | bit  |  |  |  |

|                       |                               |                                   |                |                  |                |                    |      |  |  |  |

| Legend:<br>R = Readab | le hit                        | W = Writable                      | hit            | U = Unimplen     | nented hit rea | d as '0'           |      |  |  |  |

| -n = Value a          |                               | '1' = Bit is set                  |                | 0' = Bit is cle  |                | x = Bit is unknown |      |  |  |  |

|                       |                               |                                   |                |                  | arcu           |                    | OWIT |  |  |  |

| bit 15                | TON: Timerx                   | On bit                            |                |                  |                |                    |      |  |  |  |

|                       | When T32 =                    | 1:                                |                |                  |                |                    |      |  |  |  |

|                       | 1 = Starts 32                 |                                   |                |                  |                |                    |      |  |  |  |

|                       | 0 = Stops 32                  | •                                 |                |                  |                |                    |      |  |  |  |

|                       | When T32 =<br>1 = Starts 16   |                                   |                |                  |                |                    |      |  |  |  |

|                       | 1 = Starts 16<br>0 = Stops 16 |                                   |                |                  |                |                    |      |  |  |  |

| bit 14                | -                             | nted: Read as '                   | 0'             |                  |                |                    |      |  |  |  |

| bit 13                | TSIDL: Stop                   | in Idle Mode bi                   | t              |                  |                |                    |      |  |  |  |

|                       |                               |                                   |                | device enters Id | le mode        |                    |      |  |  |  |

|                       | 0 = Continue                  | module operat                     | ion in Idle mo | ode              |                |                    |      |  |  |  |

| bit 12-7              | Unimplemer                    | nted: Read as '                   | 0'             |                  |                |                    |      |  |  |  |

| bit 6                 | TGATE: Time                   | erx Gated Time                    | Accumulatio    | n Enable bit     |                |                    |      |  |  |  |

|                       | When TCS =<br>This bit is ign |                                   |                |                  |                |                    |      |  |  |  |

|                       | When TCS =                    |                                   |                |                  |                |                    |      |  |  |  |

|                       | 1 = Gated tin                 | ne accumulatio                    |                |                  |                |                    |      |  |  |  |

|                       |                               | ne accumulatio                    |                |                  |                |                    |      |  |  |  |

| bit 5-4               |                               | Timerx Input                      | Clock Presca   | ale Select bits  |                |                    |      |  |  |  |

|                       | 11 = 1:256                    |                                   |                |                  |                |                    |      |  |  |  |

|                       | 10 = 1:64<br>01 = 1:8         |                                   |                |                  |                |                    |      |  |  |  |

|                       | 00 = 1:1                      |                                   |                |                  |                |                    |      |  |  |  |

| bit 3                 | T32: 32-bit T                 | imer Mode Sele                    | ect bit        |                  |                |                    |      |  |  |  |

|                       |                               | nd Timery form<br>nd Timery act a |                |                  |                |                    |      |  |  |  |

| bit 2                 | Unimplemer                    | nted: Read as '                   | 0'             |                  |                |                    |      |  |  |  |

| bit 1                 | -                             | Clock Source S                    |                |                  |                |                    |      |  |  |  |

|                       |                               | clock from pin <sup>-</sup>       |                | rising edge)     |                |                    |      |  |  |  |

|                       | Unimplemer                    | -                                 |                |                  |                |                    |      |  |  |  |

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

NOTES:

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                                                                       |

|       | <ul> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                             |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                               |

|       | 1 = Read - indicates data transfer is output from slave                                                                                                         |

|       | <ul> <li>0 = Write - indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

|       |                                                                                                                                                                 |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                             |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                           |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                      |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV.                                                         |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                            |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                                       |

|       | 0 = Transmit complete, I2CxTRN is empty                                                                                                                         |

|       | Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.                                                                   |

| REGISTER 1    |               | nSID: ECAN™        |                                       |                   |       | •     |        |  |  |

|---------------|---------------|--------------------|---------------------------------------|-------------------|-------|-------|--------|--|--|

| R/W-x         | R/W-x         | R/W-x              | R/W-x                                 | R/W-x             | R/W-x | R/W-x | R/W-x  |  |  |

|               |               |                    | SID                                   | <10:3>            |       |       |        |  |  |

| bit 15        |               |                    |                                       |                   |       |       | bit 8  |  |  |

| R/W-x         | R/W-x         | R/W-x              | U-0                                   | R/W-x             | U-0   | R/W-x | R/W-x  |  |  |

|               | SID<2:0>      |                    |                                       | EXIDE             | —     | EID<1 | 17:16> |  |  |

| bit 7         |               |                    |                                       |                   |       |       | bit C  |  |  |

|               |               |                    |                                       |                   |       |       |        |  |  |

| Legend:       |               |                    |                                       |                   |       |       |        |  |  |

| R = Readable  | e bit         | W = Writable b     | it U = Unimplemented bit, read as '0' |                   |       |       |        |  |  |

| -n = Value at | POR           | '1' = Bit is set   |                                       | '0' = Bit is cle  | nown  |       |        |  |  |

|               |               |                    |                                       |                   |       |       |        |  |  |

| bit 15-5      | SID<10:0>: \$ | Standard Identifi  | er bits                               |                   |       |       |        |  |  |

|               |               | address bit SID    |                                       |                   |       |       |        |  |  |

|               | 0 = Message   | e address bit SID  | ox must be '0                         | ' to match filter |       |       |        |  |  |

| bit 4         | Unimpleme     | nted: Read as '0   | )'                                    |                   |       |       |        |  |  |

| bit 3         | EXIDE: Exte   | ended Identifier E | Enable bit                            |                   |       |       |        |  |  |

|               | If MIDE = 1 t | hen:               |                                       |                   |       |       |        |  |  |

|               | 1 = Match or  | nly messages wit   | th extended i                         | dentifier addres  | sses  |       |        |  |  |

|               |               | nly messages wit   |                                       |                   |       |       |        |  |  |

|               | If MIDE = 0 t | hen:               |                                       |                   |       |       |        |  |  |

|               | Ignore EXID   | E bit.             |                                       |                   |       |       |        |  |  |

bit 2

Unimplemented: Read as '0'

bit 1-0

EID<17:16>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

#### REGISTER 19-17: CIRXFnEID: ECAN™ ACCEPTANCE FILTER n EXTENDED IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |       | EID   | <15:8>                                  |       |       |       |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |

|                                    | R/W-x | R/W-x |       | R/W-x                                   | R/W-x | DAM   |       |  |

| R/W-x                              | R/W-X | R/W-X | R/W-x |                                         | R/W-X | R/W-x | R/W-x |  |

|                                    |       |       | EID   | <7:0>                                   |       |       |       |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '1' to match filter

| R/W-x                                                                                                                                                                                                                                                                                              | R/W-x        | R/W-x                | R/W-x          | R/W-x                | R/W-x            | R/W-x           | R/W-x            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------|----------------|----------------------|------------------|-----------------|------------------|

|                                                                                                                                                                                                                                                                                                    |              |                      | SID            | <10:3>               |                  |                 |                  |

| bit 15                                                                                                                                                                                                                                                                                             |              |                      |                |                      |                  |                 | bit 8            |

|                                                                                                                                                                                                                                                                                                    |              |                      |                |                      |                  |                 |                  |

| R/W-x                                                                                                                                                                                                                                                                                              | R/W-x        | R/W-x                | U-0            | R/W-x                | U-0              | R/W-x           | R/W-x            |

|                                                                                                                                                                                                                                                                                                    | SID<2:0>     |                      |                | MIDE                 |                  | EID<1           | 7:16>            |

| bit 7                                                                                                                                                                                                                                                                                              |              |                      |                |                      |                  |                 | bit 0            |

| Legend:                                                                                                                                                                                                                                                                                            |              |                      |                |                      |                  |                 |                  |

| R = Readable                                                                                                                                                                                                                                                                                       | e bit        | W = Writable b       | oit            | U = Unimpler         | mented bit, read | d as '0'        |                  |

| -n = Value at POR                                                                                                                                                                                                                                                                                  |              | '1' = Bit is set     |                | '0' = Bit is cleared |                  | x = Bit is unkr | nown             |

|                                                                                                                                                                                                                                                                                                    |              |                      |                |                      |                  |                 |                  |

| bit 15-5                                                                                                                                                                                                                                                                                           | SID<10:0>:   | Standard Identif     | ier bits       |                      |                  |                 |                  |

|                                                                                                                                                                                                                                                                                                    | 1 = Include  | bit SIDx in filter c | omparison      |                      |                  |                 |                  |

|                                                                                                                                                                                                                                                                                                    | 0 = Bit SIDx | is don't care in f   | ilter comparis | son                  |                  |                 |                  |

| bit 4                                                                                                                                                                                                                                                                                              | Unimpleme    | nted: Read as '0     | )'             |                      |                  |                 |                  |

| bit 3                                                                                                                                                                                                                                                                                              | MIDE: Iden   | tifier Receive Mo    | de bit         |                      |                  |                 |                  |

| <ul> <li>1 = Match only message types (standard or extended address) that correspond to EXIDE bit in filter</li> <li>0 = Match either standard or extended address message if filters match</li> <li>(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))</li> </ul> |              |                      |                |                      |                  |                 | DE bit in filter |

| bit 2                                                                                                                                                                                                                                                                                              | Unimpleme    | nted: Read as '0     | )'             |                      |                  |                 |                  |

| bit 1-0                                                                                                                                                                                                                                                                                            | EID<17:16>   | : Extended Ident     | ifier bits     |                      |                  |                 |                  |

|                                                                                                                                                                                                                                                                                                    | 1 = Include  | bit EIDx in filter   | comparison     |                      |                  |                 |                  |

#### REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x                              | R/W-x | R/W-x | R/W-x                              | R/W-x  | R/W-x              | R/W-x | R/W-x |  |  |  |

|------------------------------------|-------|-------|------------------------------------|--------|--------------------|-------|-------|--|--|--|

|                                    |       |       | EID                                | <15:8> |                    |       |       |  |  |  |

| bit 15                             |       |       |                                    |        |                    |       | bit 8 |  |  |  |

|                                    |       |       |                                    |        |                    |       |       |  |  |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x                              | R/W-x  | R/W-x              | R/W-x | R/W-x |  |  |  |

| EID<7:0>                           |       |       |                                    |        |                    |       |       |  |  |  |

| bit 7                              |       |       |                                    |        |                    |       | bit 0 |  |  |  |

|                                    |       |       |                                    |        |                    |       |       |  |  |  |

| Legend:                            |       |       |                                    |        |                    |       |       |  |  |  |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |        |                    |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea                  | ared   | x = Bit is unknown |       |       |  |  |  |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

| U-0          | U-0                                                                                                          | U-0                                  | U-0             | R-0              | R-0              | R-0            | R-0   |

|--------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|------------------|------------------|----------------|-------|

| _            | —                                                                                                            | _                                    | —               |                  | SLO              | ۲<3:0>         |       |

| bit 15       |                                                                                                              |                                      |                 |                  |                  |                | bit   |

| U-0          | U-0                                                                                                          | U-0                                  | U-0             | R-0              | R-0              | R-0            | R-0   |

|              | —                                                                                                            | _                                    | _               | ROV              | RFUL             | TUNF           | TMPTY |

| bit 7        |                                                                                                              |                                      |                 |                  |                  |                | bit   |

| Legend:      |                                                                                                              |                                      |                 |                  |                  |                |       |

| R = Readab   | le bit                                                                                                       | W = Writable                         | bit             | U = Unimpler     | nented bit, read | d as '0'       |       |

| -n = Value a | t POR                                                                                                        | '1' = Bit is set                     | t               | '0' = Bit is cle | ared             | x = Bit is unk | nown  |

|              | 1111 = Slot #<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 2 is currently a<br>1 is currently a | active          |                  |                  |                |       |

| bit 7-4      | Unimplement                                                                                                  | ted: Read as '                       | 0'              |                  |                  |                |       |

| bit 3        | ROV: Receive<br>1 = A receive<br>0 = A receive                                                               | overflow has                         | occurred for at | t least one rece | eive register    |                |       |

| bit 2        | RFUL: Receiv<br>1 = New data<br>0 = The receiv                                                               | is available in                      | the receive re  | egisters         |                  |                |       |

| bit 1        | <b>TUNF:</b> Transn<br>1 = A transmit<br>0 = A transmit                                                      | underflow ha                         | s occurred for  | at least one tra | ansmit register  |                |       |

| bit 0        | TMPTY: Trans                                                                                                 |                                      |                 |                  |                  |                |       |

#### REGISTER 20-4: DCISTAT: DCI STATUS REGISTER

| DC CHA       | DC CHARACTERISTICS |                                                                       |                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |    |                                                                                                                                    |  |  |

|--------------|--------------------|-----------------------------------------------------------------------|--------------------|-------------------------------------------------------|---------------------|----|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                                        | Min                | Min Typ <sup>(1)</sup> Max Units Condi                |                     |    |                                                                                                                                    |  |  |

| DI60a        | licl               | Input Low Injection Current                                           | 0                  |                                                       | <sub>-5</sub> (5,8) | mA | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, and RB11                                                     |  |  |

| DI60b        | ІІСН               | Input High Injection Current                                          | 0                  | _                                                     | +5(6,7,8)           | mA | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>             |  |  |

| DI60c        | Σ ΙΙΟΤ             | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup> | _                                                     | +20 <sup>(9)</sup>  | mA | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |  |

### TABLE 25-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

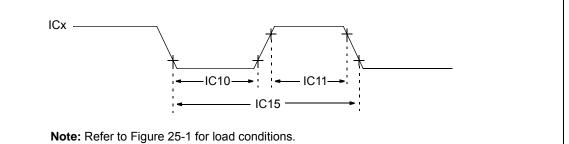

#### FIGURE 25-6: **INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS**

#### TABLE 25-25: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHA       | RACTERI | STICS                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                   |       |            |                                  |

|--------------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|------------|----------------------------------|

| Param<br>No. | Symbol  | Character             | ristic <sup>(1)</sup>                                                                                                                                                                                                                                          | Мах               | Units | Conditions |                                  |

| IC10         | TccL    | ICx Input Low Time    | No Prescaler                                                                                                                                                                                                                                                   | 0.5 Tcy + 20      |       | ns         | —                                |

|              |         |                       | With Prescaler                                                                                                                                                                                                                                                 | 10                | _     | ns         |                                  |

| IC11         | TccH    | ICx Input High Time   | No Prescaler                                                                                                                                                                                                                                                   | 0.5 Tcy + 20      | _     | ns         | —                                |

|              |         |                       | With Prescaler                                                                                                                                                                                                                                                 | 10                | _     | ns         |                                  |

| IC15         | TccP    | ICx Input Period      |                                                                                                                                                                                                                                                                | (Tcy + 40)/N      | —     | ns         | N = prescale<br>value (1, 4, 16) |

| Note 1:      | These p | arameters are charact | erized but not teste                                                                                                                                                                                                                                           | d in manufacturin | g.    | •          |                                  |

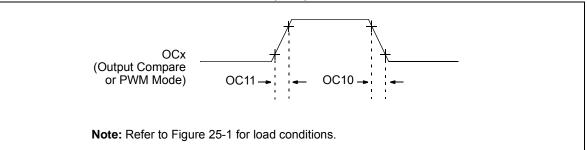

#### **FIGURE 25-7: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS**

#### TABLE 25-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |       |                    |  |  |  |

|--------------------|--------|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                       | Тур                                                                                                                                                                                                                                                          | Max | Units | Conditions         |  |  |  |

| OC10               | TccF   | OCx Output Fall Time          | —                         | _                                                                                                                                                                                                                                                            | _   | ns    | See parameter D032 |  |  |  |

| OC11               | TccR   | OCx Output Rise Time          | — — ns See parameter D031 |                                                                                                                                                                                                                                                              |     |       |                    |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

### TABLE 25-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | TICS                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------|-----------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                       | Min                                                                                                                                                                                                                                                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                         | —                                                                                                                                                                                                                                                                                     | _                  | 11  | MHz   | See Note 3                           |  |

| SP72         | TscF                  | SCKx Input Fall Time                                                | —                                                                                                                                                                                                                                                                                     |                    |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP73         | TscR                  | SCKx Input Rise Time                                                | _                                                                                                                                                                                                                                                                                     |                    | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                          | —                                                                                                                                                                                                                                                                                     | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                          | —                                                                                                                                                                                                                                                                                     | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                           | —                                                                                                                                                                                                                                                                                     | 6                  | 20  | ns    | —                                    |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                        | 30                                                                                                                                                                                                                                                                                    | _                  | _   | ns    | —                                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                          | 30                                                                                                                                                                                                                                                                                    | _                  | _   | ns    | —                                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                           | 30                                                                                                                                                                                                                                                                                    |                    |     | ns    | —                                    |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                   |                    | —   | ns    | —                                    |  |