Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp310a-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

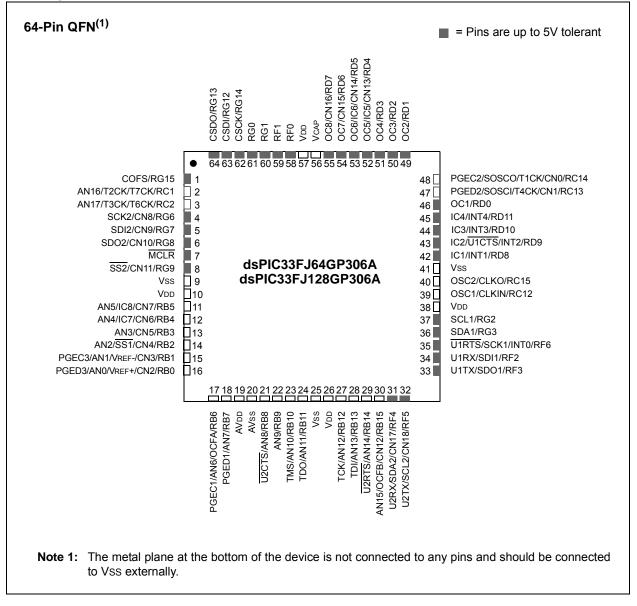

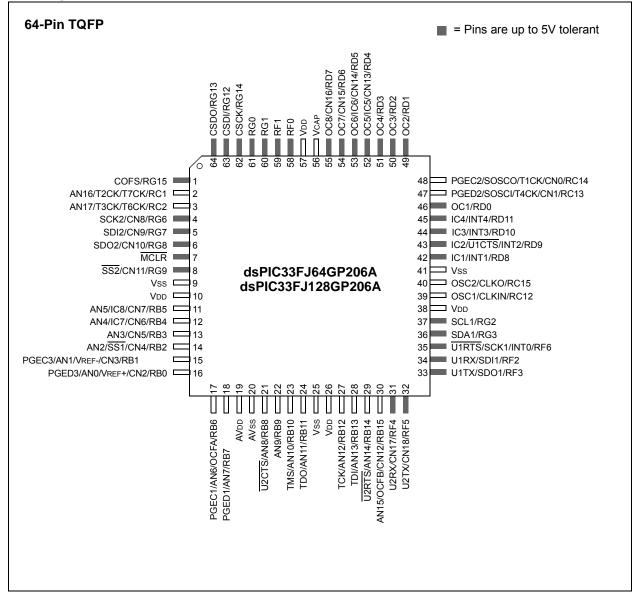

## **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/ PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXGPX06A/ X08A/X10A family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| bit 8  |    | DC: MCU ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | <ul> <li>1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data)<br/>of the result occurred</li> </ul>                                                                                                                                                                                                                                                                             |

|        |    | <ul> <li>0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                |

| bit 7- | 5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|        |    | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4  |    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |    | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3  |    | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |    | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2  |    | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |    | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                |

| bit 1  |    | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |    | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                               |

| bit 0  |    | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |    | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

| Note   | 1: | This bit may be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                  |

|        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

# 4.2.7 SOFTWARE STACK

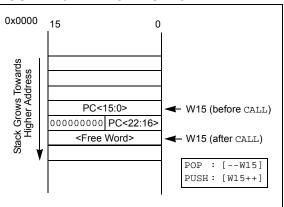

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-35 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

#### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file reg-

#### **REGISTER 5-2:** NVMKEY: NON-VOLATILE MEMORY KEY REGISTER U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_ \_\_\_\_ \_ — \_\_\_\_ bit 15 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 NVMKEY<7:0> bit 7 Legend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

bit 8

bit 0

| R/W-0            | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0          | R/W-0          |

|------------------|-----------------|----------------------------------|-----------------|------------------|------------------|----------------|----------------|

| U2TXIF<br>bit 15 | U2RXIF          | INT2IF                           | T5IF            | T4IF             | OC4IF            | OC3IF          | DMA21IF<br>bit |

|                  |                 |                                  |                 |                  |                  |                | DIL            |

| R/W-0            | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | U-0              | R/W-0          | R/W-0          |

| IC8IF            | IC7IF           | AD2IF                            | INT1IF          | CNIF             | _                | MI2C1IF        | SI2C1IF        |

| bit 7            |                 | !                                |                 | · · ·            |                  | ·              | bit            |

| Legend:          |                 |                                  |                 |                  |                  |                |                |

| R = Readable     | e bit           | W = Writable                     | bit             | U = Unimplen     | nented bit, read | d as '0'       |                |

| -n = Value at    | POR             | '1' = Bit is set                 | :               | '0' = Bit is cle | ared             | x = Bit is unk | nown           |

| bit 15           | U2TXIF: UAF     | T2 Transmitte                    | r Interrupt Fla | g Status bit     |                  |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 14           | U2RXIF: UAF     | RT2 Receiver I                   | nterrupt Flag   | Status bit       |                  |                |                |

|                  |                 | request has oc<br>request has no |                 |                  |                  |                |                |

| bit 13           | INT2IF: Exter   | nal Interrupt 2                  | Flag Status b   | it               |                  |                |                |

|                  | •               | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 12           | T5IF: Timer5    | Interrupt Flag                   | Status bit      |                  |                  |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 11           | T4IF: Timer4    | Interrupt Flag                   | Status bit      |                  |                  |                |                |

|                  | •               | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 10           | OC4IF: Outpu    | ut Compare Ch                    | annel 4 Interr  | upt Flag Status  | bit              |                |                |

|                  |                 | equest has oc<br>equest has no   |                 |                  |                  |                |                |

| bit 9            | •               | •                                |                 | upt Flag Status  | hit              |                |                |

| bit 5            | 1 = Interrupt i | equest has oc                    | curred          | upt i lag otatus | bit              |                |                |

| L:1 0            | •               | request has no                   |                 |                  |                  | - h'i          |                |

| bit 8            |                 | request has oc                   |                 | Complete Inter   | rupt Flag Statu  | IS DIL         |                |

|                  |                 | equest has no                    |                 |                  |                  |                |                |

| bit 7            | IC8IF: Input C  | Capture Chann                    | el 8 Interrupt  | Flag Status bit  |                  |                |                |

|                  |                 | equest has oc                    |                 |                  |                  |                |                |

| hit C            | -               | equest has no                    |                 | Flag Status hit  |                  |                |                |

| bit 6            | 1 = Interrupt i | equest has oc                    | curred          | Flag Status bit  |                  |                |                |

| bit 5            |                 | equest has no                    |                 | rupt Elag Statu  | - hit            |                |                |

| DIL U            |                 | equest has oc                    | -               | rupt Flag Status |                  |                |                |

|                  | •               | equest has no                    |                 |                  |                  |                |                |

|                  | INT1IF. Exter   | nal Interrunt 1                  | Flag Status b   | it               |                  |                |                |

| bit 4            |                 | nai interrupt i                  | i lug oluluo b  |                  |                  |                |                |

| U-0                     | R/W-1                                                         | R/W-0                                                                                                        | R/W-0          | U-0              | R/W-1           | R/W-0            | R/W-0 |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|------------------|-------|--|--|--|--|--|

|                         |                                                               | C1IP<2:0>                                                                                                    |                |                  |                 | C1RXIP<2:0>      |       |  |  |  |  |  |

| bit 15                  |                                                               |                                                                                                              |                |                  |                 |                  | bi    |  |  |  |  |  |

| U-0                     | R/W-1                                                         | R/W-0                                                                                                        | R/W-0          | U-0              | R/W-1           | R/W-0            | R/W-0 |  |  |  |  |  |

| _                       |                                                               | SPI2IP<2:0>                                                                                                  |                | _                |                 | SPI2EIP<2:0>     |       |  |  |  |  |  |

| bit 7                   |                                                               |                                                                                                              |                |                  |                 |                  | bi    |  |  |  |  |  |

| Louende                 |                                                               |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

| Legend:<br>R = Readable | a hit                                                         | W = Writable b                                                                                               | nit            | II – I Inimple   | mented bit, rea | ad as 'O'        |       |  |  |  |  |  |

| -n = Value at           |                                                               | '1' = Bit is set                                                                                             | JIL            | '0' = Bit is cle |                 |                  | 0000  |  |  |  |  |  |

|                         | FUR                                                           | I – DILIS SEL                                                                                                |                |                  | eareu           | x = Bit is unkno | OWIT  |  |  |  |  |  |

| bit 15                  | Unimpleme                                                     | ented: Read as '0                                                                                            | )'             |                  |                 |                  |       |  |  |  |  |  |

| bit 14-12               | -                                                             |                                                                                                              |                | ity bits         |                 |                  |       |  |  |  |  |  |

|                         |                                                               | C1IP<2:0>: ECAN1 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              | •              |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •<br>001 = Interrupt is priority 1                            |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         |                                                               | upt is priority i<br>upt source is disa                                                                      | abled          |                  |                 |                  |       |  |  |  |  |  |

| bit 11                  |                                                               | ented: Read as '0                                                                                            |                |                  |                 |                  |       |  |  |  |  |  |

| bit 10-8                | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | 111 = Interrupt is priority 7 (highest priority interrupt)    |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              | <b>J</b>       | .,,              |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             | untic priority d                                                                                             |                |                  |                 |                  |       |  |  |  |  |  |

|                         |                                                               | upt is priority 1<br>upt source is disa                                                                      | bled           |                  |                 |                  |       |  |  |  |  |  |

| bit 7                   |                                                               | ented: Read as '0                                                                                            |                |                  |                 |                  |       |  |  |  |  |  |

|                         | -                                                             |                                                                                                              |                | h / hita         |                 |                  |       |  |  |  |  |  |

| bit 6-4                 |                                                               | SPI2 Event Int<br>supt is priority 7 (k)                                                                     | -              | -                |                 |                  |       |  |  |  |  |  |

|                         | •                                                             | upt is priority 7 (h                                                                                         | lignest phon   | ty interrupt)    |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         |                                                               | 001 = Interrupt is priority 1                                                                                |                |                  |                 |                  |       |  |  |  |  |  |

|                         |                                                               | upt source is disa                                                                                           |                |                  |                 |                  |       |  |  |  |  |  |

| bit 3                   | -                                                             | ented: Read as '0                                                                                            |                |                  |                 |                  |       |  |  |  |  |  |

| bit 2-0                 |                                                               | 0>: SPI2 Error In                                                                                            | -              | -                |                 |                  |       |  |  |  |  |  |

|                         | 111 = Interr                                                  | upt is priority 7 (h                                                                                         | nighest priori | ty interrupt)    |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | •                                                             |                                                                                                              |                |                  |                 |                  |       |  |  |  |  |  |

|                         | 001 = Interr                                                  | upt is priority 1                                                                                            |                |                  |                 |                  |       |  |  |  |  |  |

|                         | 001 11001                                                     | aptio priority i                                                                                             |                |                  |                 |                  |       |  |  |  |  |  |

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

### bit 0 OSWEN: Oscillator Switch Enable bit

bit 1

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This is register is reset only on a Power-on Reset (POR).

# 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, dsPIC33FJXXXGPX06A/X08A/X10A devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 22.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and CF (OSCCON<3>) are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRC-PLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** Refer to **Section 7. "Oscillator"** (DS70186) in the *"dsPIC33F/PIC24H Family Reference Manual"* for details.

# 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2009-2012</sup> Microchip Technology Inc.

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | U-0              | U-0            | R/W-0                |

|---------------|---------------------------------|---------------------------------------|---------|-------------------|------------------|----------------|----------------------|

| T5MD          | T4MD                            | T3MD                                  | T2MD    | T1MD              |                  | _              | DCIMD                |

| bit 15        |                                 |                                       |         |                   |                  |                | bit 8                |

|               |                                 |                                       |         |                   |                  |                |                      |

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | R/W-0            | R/W-0          | R/W-0                |

| I2C1MD        | U2MD                            | U1MD                                  | SPI2MD  | SPI1MD            | C2MD             | C1MD           | AD1MD <sup>(1)</sup> |

| bit 7         |                                 |                                       |         |                   |                  |                | bit                  |

| Legend:       |                                 |                                       |         |                   |                  |                |                      |

| R = Readabl   | e bit                           | W = Writable                          | bit     | U = Unimplen      | nented bit, read | d as '0'       |                      |

| -n = Value at | POR                             | '1' = Bit is set                      |         | '0' = Bit is clea |                  | x = Bit is unk | nown                 |

|               |                                 |                                       |         |                   |                  |                |                      |

| bit 15        | T5MD: Timer                     | 5 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 14        | T4MD: Timer                     | 4 Module Disat                        | ole bit |                   |                  |                |                      |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 13        |                                 | 3 Module Disat                        |         |                   |                  |                |                      |

|               | 1 = Timer3 m                    | nodule is disable                     | ed      |                   |                  |                |                      |

|               | 0 = Timer3 m                    | nodule is enable                      | d       |                   |                  |                |                      |

| bit 12        | -                               | 2 Module Disat                        |         |                   |                  |                |                      |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 11        | T1MD: Timer                     | 1 Module Disat                        | ole bit |                   |                  |                |                      |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |

| bit 10-9      | Unimplemer                      | ted: Read as '                        | כ'      |                   |                  |                |                      |

| bit 8         | DCIMD: DCI                      | Module Disable                        | e bit   |                   |                  |                |                      |

|               |                                 | ule is disabled<br>ule is enabled     |         |                   |                  |                |                      |

| bit 7         | <b>I2C1MD:</b> I <sup>2</sup> C | 1 Module Disab                        | le bit  |                   |                  |                |                      |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

| bit 6         |                                 | T2 Module Disa                        | ble bit |                   |                  |                |                      |

|               | -                               | nodule is disabl<br>nodule is enable  |         |                   |                  |                |                      |

| bit 5         |                                 | T1 Module Disa                        |         |                   |                  |                |                      |

|               |                                 | nodule is disabl                      |         |                   |                  |                |                      |

|               | 0 = UART1 n                     | nodule is enable                      | ed      |                   |                  |                |                      |

| bit 4         | SPI2MD: SP                      | I2 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                 | dule is disabled                      |         |                   |                  |                |                      |

|               |                                 | dule is enabled                       |         |                   |                  |                |                      |

| bit 3         |                                 | 11 Module Disal                       | ole bit |                   |                  |                |                      |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

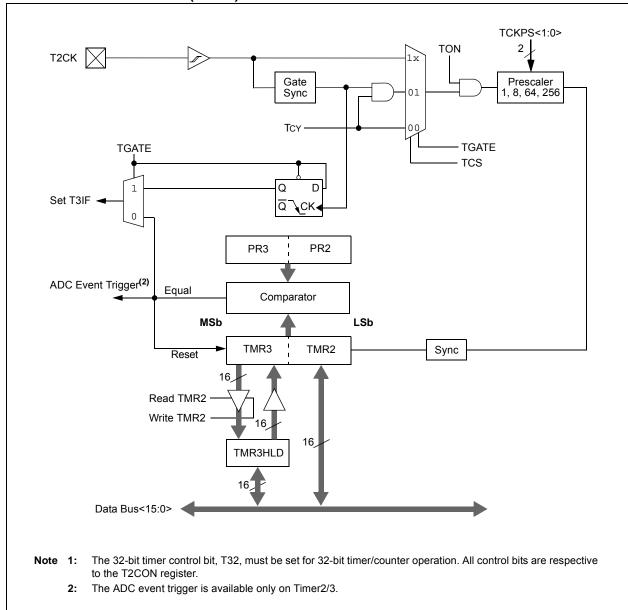

# FIGURE 13-1: TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup>

| R/W-0        | U-0                                                     | R/W-0                                                                                        | U-0                       | U-0               | U-0             | U-0                | U-0 |  |  |  |  |  |

|--------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------|-------------------|-----------------|--------------------|-----|--|--|--|--|--|

| TON          | 0-0                                                     | TSIDL                                                                                        | 0-0                       | 0-0               | 0-0             | 0-0                | 0-0 |  |  |  |  |  |

| bit 15       |                                                         | TSIDL                                                                                        | _                         | —                 |                 | —                  |     |  |  |  |  |  |

|              |                                                         |                                                                                              |                           |                   |                 |                    | bit |  |  |  |  |  |

| U-0          | R/W-0                                                   | R/W-0                                                                                        | R/W-0                     | R/W-0             | U-0             | R/W-0              | U-0 |  |  |  |  |  |

| _            | TGATE                                                   |                                                                                              | S<1:0>                    | T32               | _               | TCS <sup>(1)</sup> | _   |  |  |  |  |  |

| bit 7        |                                                         |                                                                                              |                           | 1                 |                 |                    | bit |  |  |  |  |  |

|              |                                                         |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

| Legend:      |                                                         |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

| R = Readab   | le bit                                                  | W = Writable                                                                                 | bit                       | U = Unimplen      | nented bit, rea | id as '0'          |     |  |  |  |  |  |

| -n = Value a | It POR                                                  | '1' = Bit is set                                                                             |                           | '0' = Bit is clea | ared            | x = Bit is unkn    | own |  |  |  |  |  |

|              |                                                         |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

| bit 15       | TON: Timerx                                             |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | $\frac{\text{When T32}}{1 - \text{Starte 22}}$          |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 1 = Starts 32-bit Timerx/y<br>0 = Stops 32-bit Timerx/y |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | When T32 = 0:                                           |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 1 = Starts 16                                           |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 0 = Stops 16                                            | -bit Timerx                                                                                  |                           |                   |                 |                    |     |  |  |  |  |  |

| bit 14       | Unimplemer                                              | nted: Read as '                                                                              | 0'                        |                   |                 |                    |     |  |  |  |  |  |

| bit 13       | TSIDL: Stop                                             | TSIDL: Stop in Idle Mode bit                                                                 |                           |                   |                 |                    |     |  |  |  |  |  |

|              |                                                         |                                                                                              |                           | device enters Id  | e mode          |                    |     |  |  |  |  |  |

|              |                                                         | module operat                                                                                |                           | ode               |                 |                    |     |  |  |  |  |  |

| bit 12-7     | Unimplemer                                              | nted: Read as '                                                                              | 0'                        |                   |                 |                    |     |  |  |  |  |  |

| bit 6        | TGATE: Timerx Gated Time Accumulation Enable bit        |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | When TCS =<br>This bit is ign                           |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | When TCS = 0:                                           |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 1 = Gated time accumulation enabled                     |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 0 = Gated tin                                           | ne accumulatio                                                                               | n disabled                |                   |                 |                    |     |  |  |  |  |  |

| bit 5-4      | TCKPS<1:0>                                              | -: Timerx Input                                                                              | Clock Presca              | ale Select bits   |                 |                    |     |  |  |  |  |  |

|              | 11 <b>= 1:256</b>                                       |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 10 = 1:64                                               |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

|              | 01 = 1:8<br>00 = 1:1                                    |                                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

| bit 3        |                                                         | imer Mode Sele                                                                               | ect bit                   |                   |                 |                    |     |  |  |  |  |  |

|              |                                                         | <b>T32:</b> 32-bit Timer Mode Select bit<br>1 = Timerx and Timery form a single 32-bit timer |                           |                   |                 |                    |     |  |  |  |  |  |

|              |                                                         | nd Timery act a                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

| bit 2        | Unimplemer                                              | nted: Read as '                                                                              | 0'                        |                   |                 |                    |     |  |  |  |  |  |

| bit 1        | TCS: Timerx                                             | Clock Source S                                                                               | Select bit <sup>(1)</sup> |                   |                 |                    |     |  |  |  |  |  |

|              |                                                         | clock from pin <sup>-</sup>                                                                  |                           | rising edge)      |                 |                    |     |  |  |  |  |  |

|              |                                                         | nted: Read as '                                                                              |                           |                   |                 |                    |     |  |  |  |  |  |

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

# 14.1 Input Capture Registers

#### REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0                  | U-0                                                                                                                                                               | R/W-0                              | U-0              | U-0               | U-0             | U-0              | U-0   |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-------------------|-----------------|------------------|-------|--|--|--|

| —                    | —                                                                                                                                                                 | ICSIDL                             | _                | _                 | —               | —                | _     |  |  |  |

| bit 15               |                                                                                                                                                                   |                                    |                  |                   |                 |                  | bit 8 |  |  |  |

|                      |                                                                                                                                                                   |                                    |                  |                   |                 |                  |       |  |  |  |

| R/W-0                | R/W-0                                                                                                                                                             | R/W-0                              | R-0, HC          | R-0, HC           | R/W-0           | R/W-0            | R/W-0 |  |  |  |

| ICTMR <sup>(1)</sup> | ICI                                                                                                                                                               | <1:0>                              | ICOV             | ICBNE             |                 | ICM<2:0>         |       |  |  |  |

| bit 7                |                                                                                                                                                                   |                                    |                  |                   |                 |                  | bit ( |  |  |  |

| Legend:              |                                                                                                                                                                   |                                    |                  |                   |                 |                  |       |  |  |  |

| R = Readable         | bit                                                                                                                                                               | W = Writable                       | bit              | U = Unimpler      | mented bit, rea | d as '0'         |       |  |  |  |

| -n = Value at F      | POR                                                                                                                                                               | '1' = Bit is set                   |                  | '0' = Bit is cle  | ared            | x = Bit is unkn  | own   |  |  |  |

|                      |                                                                                                                                                                   |                                    |                  |                   |                 |                  |       |  |  |  |

| bit 15-14            | Unimplemer                                                                                                                                                        | nted: Read as '                    | 0'               |                   |                 |                  |       |  |  |  |

| bit 13               | ICSIDL: Inpu                                                                                                                                                      | it Capture Mod                     | ule Stop in Idle | e Control bit     |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | ture module wi                     |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | ture module wi                     |                  | operate in CPU    | I Idle mode     |                  |       |  |  |  |

| bit 12-8             | -                                                                                                                                                                 | nted: Read as '                    |                  |                   |                 |                  |       |  |  |  |

| bit 7                | ICTMR: Input Capture Timer Select bits <sup>(1)</sup><br>1 = TMR2 contents are captured on capture event                                                          |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | 0 = TMR3 contents are captured on capture event                                                                                                                   |                                    |                  |                   |                 |                  |       |  |  |  |

| bit 6-5              | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                            |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | 11 = Interrupt on every fourth capture event                                                                                                                      |                                    |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | t on every third                   | •                |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | t on every seco<br>t on every capt |                  | /ent              |                 |                  |       |  |  |  |

| bit 4                | -                                                                                                                                                                 |                                    |                  | i bit (read-only) |                 |                  |       |  |  |  |

|                      | ICOV: Input Capture Overflow Status Flag bit (read-only)<br>1 = Input capture overflow occurred                                                                   |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | 0 = No input                                                                                                                                                      | capture overflo                    | w occurred       |                   |                 |                  |       |  |  |  |

| bit 3                | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                          |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                 |                                    |                  |                   |                 |                  |       |  |  |  |

| h ii 0 0             |                                                                                                                                                                   |                                    | . ,              | _                 |                 |                  |       |  |  |  |

| bit 2-0              |                                                                                                                                                                   | put Capture M                      |                  |                   | dovice is in SI | oon or Idlo mode | ,     |  |  |  |

|                      | 111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br>(Rising edge detect only, all other control bits are not applicable.) |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | 110 = Unused (module disabled)                                                                                                                                    |                                    |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | re mode, every                     |                  |                   |                 |                  |       |  |  |  |

|                      | •                                                                                                                                                                 | re mode, every<br>re mode, every   |                  | e                 |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | re mode, every<br>re mode, every   |                  |                   |                 |                  |       |  |  |  |

|                      | 001 = Captur                                                                                                                                                      | re mode, every                     | edge (rising a   |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                                                                   | :0> bits do not                    |                  | pt generation     | for this mode.) |                  |       |  |  |  |

|                      | 000 = input c                                                                                                                                                     | capture module                     | turnea oπ        |                   |                 |                  |       |  |  |  |

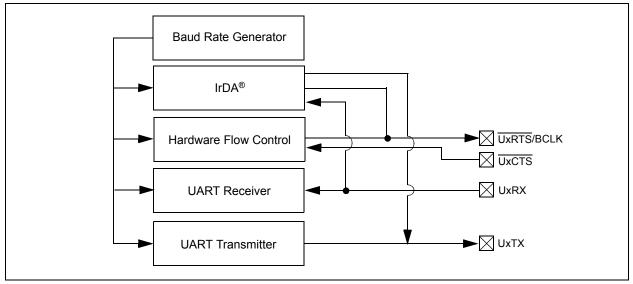

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJXXXGPX06A/X08A/X10A device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of the key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

- **Note 1:** Both UART1 and UART2 can trigger a DMA data transfer. If U1TX, U1RX, U2TX or U2RX is selected as a DMA IRQ source, a DMA transfer occurs when the U1TXIF, U1RXIF, U2TXIF or U2RXIF bit gets set as a result of a UART1 or UART2 transmission or reception.

- 2: If DMA transfers are required, the UART TX/RX FIFO buffer must be set to a size of 1 byte/word (i.e., UTXISEL<1:0> = 00 and URXISEL<1:0> = 00).

# 18.3 UART Control Registers

#### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                          | R/W-0                                             | R/W-0                         | R/W-0                                   | U-0                                                             | R/W-0             | R/W-0           |

|-----------------------|------------------------------|---------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------------------------------|-------------------|-----------------|

| UARTEN <sup>(1)</sup> | _                            | USIDL                                             | IREN <sup>(2)</sup>           | RTSMD                                   | —                                                               | UEN               | <1:0>           |

| bit 15                |                              |                                                   |                               | ·                                       |                                                                 |                   | bit 8           |

|                       |                              |                                                   |                               |                                         |                                                                 |                   |                 |

| R/W-0 HC              | R/W-0                        | R/W-0 HC                                          | R/W-0                         | R/W-0                                   | R/W-0                                                           | R/W-0             | R/W-0           |

| WAKE                  | LPBACK                       | ABAUD                                             | URXINV                        | BRGH                                    | PDSEL                                                           | _<1:0>            | STSEL           |

| bit 7                 |                              |                                                   |                               |                                         |                                                                 |                   | bit 0           |