Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp310at-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

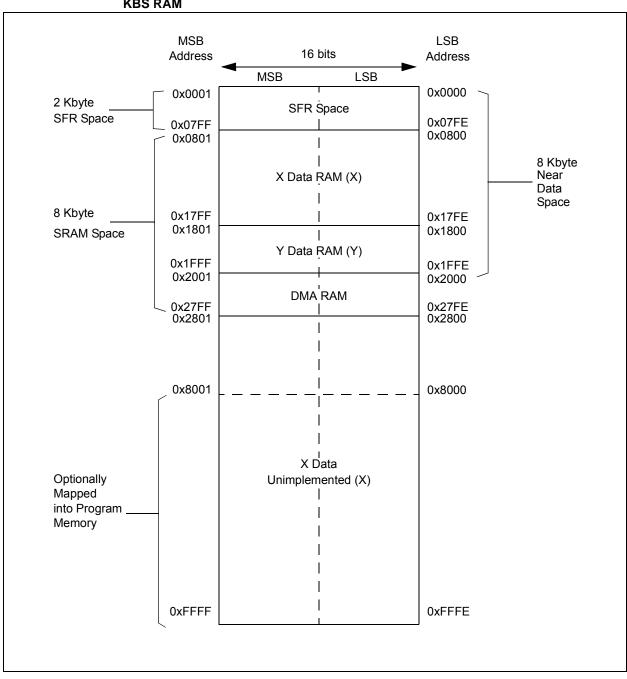

### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 8 KBS RAM

after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register   | Indirect  | with    | Register    | Offset |

|-------|------------|-----------|---------|-------------|--------|

|       | Addressir  | ng mode i | is only | v available | for W9 |

|       | (in X spac | ce) and W | /11 (in | Y space).   |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

# 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers which have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a bidirectional mode (i.e., address boundary checks will be performed on both the lower and upper address boundaries).

### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word sized data (LSb of every EA is always clear).

# 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, dsPIC33FJXXXGPX06A/X08A/X10A devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

# 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 22.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

# 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and CF (OSCCON<3>) are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRC-PLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

# 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2009-2012</sup> Microchip Technology Inc.

# 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

# 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the "*dsPIC33F/PIC24H Family Reference Manual*".

| R/W-0         | U-0                           | R/W-0                                 | R/W-1 HC          | R/W-0            | R/W-0                   | R/W-0              | R/W-0         |

|---------------|-------------------------------|---------------------------------------|-------------------|------------------|-------------------------|--------------------|---------------|

| I2CEN         |                               | I2CSIDL                               | SCLREL            | IPMIEN           | A10M                    | DISSLW             | SMEN          |

| bit 15        |                               |                                       |                   |                  |                         |                    | bit 8         |

|               |                               |                                       |                   |                  |                         |                    |               |

| R/W-0         | R/W-0                         | R/W-0                                 | R/W-0 HC          | R/W-0 HC         | R/W-0 HC                | R/W-0 HC           | R/W-0 HC      |

| GCEN          | STREN                         | ACKDT                                 | ACKEN             | RCEN             | PEN                     | RSEN               | SEN           |

| bit 7         |                               |                                       |                   |                  |                         |                    | bit 0         |

| Legend:       |                               | U = Unimplei                          | nented bit, rea   | d as '0'         |                         |                    |               |

| R = Readable  | e hit                         | W = Writable                          |                   | HS = Set in h    | ardware                 | HC = Cleared       | in hardware   |

| -n = Value at |                               | '1' = Bit is se                       |                   | '0' = Bit is cle |                         | x = Bit is unkr    |               |

|               | TOIN                          |                                       |                   |                  |                         |                    |               |

| bit 15        | <b>12CEN:</b> 12Cx            | Enable bit                            |                   |                  |                         |                    |               |

|               | 1 = Enables t                 | the I2Cx modu                         | le and configur   | es the SDAx a    | and SCLx pins a         | as serial port pir | าร            |

|               |                               |                                       |                   |                  | by port functio         |                    |               |

| bit 14        | Unimplemen                    | ted: Read as                          | ʻ0'               |                  |                         |                    |               |

| bit 13        | I2CSIDL: Sto                  | p in Idle Mode                        | bit               |                  |                         |                    |               |

|               |                               | •                                     | eration when de   |                  | n Idle mode             |                    |               |

|               |                               | -                                     | tion in Idle mod  |                  | 1 <sup>2</sup> 0 1      |                    |               |

| bit 12        |                               |                                       | ontrol bit (when  | operating as     | I <sup>2</sup> C slave) |                    |               |

|               | 1 = Release 3                 | SCLX CIOCK<br>_X Clock low (cl        | ock stretch)      |                  |                         |                    |               |

|               | If STREN = 1                  | •                                     |                   |                  |                         |                    |               |

|               |                               |                                       | y write '0' to in | itiate stretch a | nd write '1' to re      | elease clock). H   | ardware clear |

|               |                               |                                       |                   |                  | d of slave rece         |                    |               |

|               | If STREN = 0                  |                                       |                   |                  |                         |                    |               |

|               | Bit is R/S (i.e transmission. |                                       | y only write '1'  | to release clo   | ck). Hardware c         | lear at beginnin   | g of slave    |

| bit 11        | IPMIEN: Intel                 | lligent Periphe                       | ral Managemer     | nt Interface (IF | MI) Enable bit          |                    |               |

|               | 1 = IPMI mod<br>0 = IPMI mod  |                                       | all addresses A   | cknowledged      |                         |                    |               |

| bit 10        | A10M: 10-bit                  | Slave Address                         | s bit             |                  |                         |                    |               |

|               | 1 = I2CxADD                   | ) is a 10-bit sla                     | ve address        |                  |                         |                    |               |

|               | 0 = I2CxADD                   | ) is a 7-bit slave                    | e address         |                  |                         |                    |               |

| bit 9         |                               | able Slew Rate                        |                   |                  |                         |                    |               |

|               |                               | e control disable<br>e control enable |                   |                  |                         |                    |               |

| bit 8         |                               | us Input Levels                       |                   |                  |                         |                    |               |

|               |                               | -                                     | ds compliant wi   | th SMBus spe     | cification              |                    |               |

|               |                               | SMBus input th                        |                   | ·                |                         |                    |               |

| bit 7         |                               |                                       | e bit (when ope   | •                | ,                       |                    |               |

|               |                               |                                       |                   | ddress is rece   | eived in the I2C        | xRSR               |               |

|               | •                             | is enabled for                        | • •               |                  |                         |                    |               |

| hit C         |                               | call address di                       |                   | han anaratia -   | $a_{12}$                |                    |               |

| bit 6         |                               |                                       | h Enable bit (w   | nen operating    | as I-C slave)           |                    |               |

|               |                               | unction with SC<br>oftware or rece    | VEREL Dit.        | hina             |                         |                    |               |

|               |                               |                                       | eive clock stret  | •                |                         |                    |               |

|               |                               |                                       |                   |                  |                         |                    |               |

# 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

# 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546064                                        |

### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0          | U-0                                         | U-0                              | U-0                   | R/W-0                              | R/W-0            | U-0            | R/W-0  |

|--------------|---------------------------------------------|----------------------------------|-----------------------|------------------------------------|------------------|----------------|--------|

|              | —                                           | _                                |                       | BLEN                               | l<1:0>           |                | COFSG3 |

| bit 15       | ·                                           |                                  |                       |                                    |                  |                | bit    |

|              |                                             |                                  |                       |                                    |                  |                |        |

| R/W-0        | R/W-0                                       | R/W-0                            | U-0                   | R/W-0                              | R/W-0            | R/W-0          | R/W-0  |

|              | COFSG<2:0>                                  |                                  |                       |                                    | WS               | <3:0>          |        |

| bit 7        |                                             |                                  |                       |                                    |                  |                | bit    |

|              |                                             |                                  |                       |                                    |                  |                |        |

| Legend:      |                                             |                                  |                       |                                    |                  |                |        |

| R = Readab   |                                             | W = Writable                     |                       |                                    | nented bit, read |                |        |

| -n = Value a | t POR                                       | '1' = Bit is set                 |                       | '0' = Bit is clea                  | ared             | x = Bit is unk | nown   |

|              |                                             |                                  |                       |                                    |                  |                |        |

| bit 15-12    | -                                           | ted: Read as '                   |                       |                                    |                  |                |        |

| bit 11-10    | BLEN<1:0>:                                  | Buffer Length (                  | Control bits          |                                    |                  |                |        |

|              |                                             |                                  |                       | ween interrupts                    |                  |                |        |

|              |                                             |                                  |                       | etween interrupt                   | S                |                |        |

|              |                                             |                                  |                       | ween interrupts                    |                  |                |        |

|              |                                             | a word will be t                 |                       | een interrupts                     |                  |                |        |

| bit 9        | -                                           | ted: Read as '                   |                       |                                    |                  |                |        |

| bit 8-5      | COFSG<3:0>                                  | : Frame Sync                     | Generator Co          | ontrol bits                        |                  |                |        |

|              | 1111 <b>= Data</b> 1                        | frame has 16 w                   | vords                 |                                    |                  |                |        |

|              | •                                           |                                  |                       |                                    |                  |                |        |

|              | •                                           |                                  |                       |                                    |                  |                |        |

|              | •<br>0010 = Data :                          | frame has 3 wo                   | orde                  |                                    |                  |                |        |

|              |                                             | frame has 2 wo                   |                       |                                    |                  |                |        |

|              |                                             | frame has 1 wo                   |                       |                                    |                  |                |        |

| bit 4        | Unimplemen                                  | ted: Read as '                   | 0'                    |                                    |                  |                |        |

| bit 3-0      | WS<3:0>: DC                                 | I Data Word S                    | ize bits              |                                    |                  |                |        |

|              | 1111 <b>= Data</b>                          | word size is 16                  | bits                  |                                    |                  |                |        |

|              | •                                           |                                  |                       |                                    |                  |                |        |

|              | •                                           |                                  |                       |                                    |                  |                |        |

|              |                                             |                                  |                       |                                    |                  |                |        |

|              | •                                           |                                  |                       |                                    |                  |                |        |

|              |                                             | word size is 5 l                 |                       |                                    |                  |                |        |

|              | 0011 <b>= Data</b>                          | word size is 4 b                 | oits                  |                                    |                  |                |        |

|              | 0011 <b>= Data</b><br>0010 <b>= Inval</b> i | word size is 4 l<br>d Selection. | oits<br>)o not use. U | nexpected resul<br>nexpected resul |                  |                |        |

# REGISTER 20-2: DCICON2: DCI CONTROL REGISTER 2

NOTES:

# 22.0 SPECIAL FEATURES

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section "CodeGuard™ 23. Security" (DS70199), Section 24. "Programming and Diagnostics" (DS70207), and Section 25. "Device Configuration" (DS70194) in the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJXXXGPX06A/X08A/X10A devices include the following features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

#### Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 0xF80000 FBS RBS<1:0> BSS<2:0> BWRP SWRP 0xF80002 FSS RSS<1:0> SSS<2:0> 0xF80004 FGS GSS1 GSS0 GWRP Reserved<sup>(2)</sup> FNOSC<2:0> 0xF80006 FOSCSEL **IESO** OSCIOFNC POSCMD<1:0> 0xF80008 FOSC FCKSM<1:0> 0xF8000A FWDT FWDTEN WINDIS PLLKEN<sup>(3)</sup> WDTPRE WDTPOST<3:0> 0xF8000C FPOR Reserved<sup>(4)</sup> FPWRT<2:0> Reserved<sup>(1)</sup> 0xF8000E FICD **JTAGEN** ICS<1:0> 0xF80010 FUID0 User Unit ID Byte 0 0xF80012 FUID1 User Unit ID Byte 1 0xF80014 FUID2 User Unit ID Byte 2 0xF80016 FUID3 User Unit ID Byte 3

# TABLE 22-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed as '1'.

- 2: When read, this bit returns the current programmed value.

- **3:** This bit is unimplemented on dsPIC33FJ64GPX06A/X08A/X10A and dsPIC33FJ128GPX06A/X08A/X10A devices and reads as '0'.

- 4: These bits are reserved and always read as '1'.

# 22.1 Configuration Bits

dsPIC33FJXXXGPX06A/X08A/X10A devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25.** "**Device Configuration**" (DS70194) of the "*dsPIC33F/PIC24H Family Reference Manual*", for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The device Configuration register map is shown in Table 22-1.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 22-2.

Note that address 0xF80000 is beyond the user program memory space. In fact, it belongs to the configuration memory space (0x800000-0xFFFFF) which can only be accessed using table reads and table writes.

| TABLE 25-11: | ELECTRICAL CHARACTERISTICS: BOR |

|--------------|---------------------------------|

|--------------|---------------------------------|

| DC CHARACTERISTICS |           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                  |                    |        |                    |       |            |

|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------|--------------------|-------|------------|

| Param.             | Symbol    | Characteristic <sup>(1)</sup>                                                                                                                                                                        |                  | Min <sup>(1)</sup> | Тур    | Max <sup>(1)</sup> | Units | Conditions |

| BO10               | VBOR      | BOR Event on VDD transition high-to-low                                                                                                                                                              |                  | 2.40               | _      | 2.55               | V     | Vdd        |

| Noto 1             | Doromotor | aro for dosign quidanco                                                                                                                                                                              | only and are not | tootod in          | monufo | oturina            |       |            |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

### TABLE 25-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                                      |        | Standard Operating Col<br>(unless otherwise state<br>Operating temperature |      |       |                                                            |  |  |

|--------------------|--------|--------------------------------------|--------|----------------------------------------------------------------------------|------|-------|------------------------------------------------------------|--|--|

| Param.             | Symbol | Characteristic <sup>(3)</sup>        | Min    | Typ <sup>(1)</sup>                                                         | Max  | Units | Conditions                                                 |  |  |

|                    |        | Program Flash Memory                 |        |                                                                            |      |       |                                                            |  |  |

| D130               | Eр     | Cell Endurance                       | 10,000 | _                                                                          | _    | E/W   |                                                            |  |  |

| D131               | Vpr    | VDD for Read                         | VMIN   | _                                                                          | 3.6  | V     | Vмın = Minimum operating<br>voltage                        |  |  |

| D132b              | VPEW   | VDD for Self-Timed Write             | VMIN   | —                                                                          | 3.6  | V     | Vмın = Minimum operating<br>voltage                        |  |  |

| D134               | TRETD  | Characteristic Retention             | 20     | —                                                                          | —    | Year  | Provided no other specifications are violated              |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | —      | 10                                                                         | —    | mA    |                                                            |  |  |

| D136a              | Trw    | Row Write Time                       | 1.32   | —                                                                          | 1.74 | ms    | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |  |  |

| D136b              | Trw    | Row Write Time                       | 1.28   | —                                                                          | 1.79 | ms    | Trw = 11064 FRC cycles,<br>Ta = +150°C, See <b>Note 2</b>  |  |  |

| D137a              | TPE    | Page Erase Time                      | 20.1   | —                                                                          | 26.5 | ms    | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |  |

| D137b              | TPE    | Page Erase Time                      | 19.5   | —                                                                          | 27.3 | ms    | TPE = 168517 FRC cycles,<br>TA = +150°C, See <b>Note 2</b> |  |  |

| D138a              | Tww    | Word Write Cycle Time                | 42.3   | —                                                                          | 55.9 | μs    | Tww = 355 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>     |  |  |

| D138b              | Tww    | Word Write Cycle Time                | 41.1   | —                                                                          | 57.6 | μs    | Tww = 355 FRC cycles,<br>Ta = +150°C, See <b>Note 2</b>    |  |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b '011111 (for Min), TUN<5:0> = b '100000 (for Max). This parameter depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

3: These parameters are assured by design, but are not characterized or tested in manufacturing.

#### TABLE 25-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |        |                                                |     |     |     |       |                                                    |  |  |  |

|--------------------------------------------------------------------------|--------|------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------|--|--|--|

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |        |                                                |     |     |     |       |                                                    |  |  |  |

| Param.                                                                   | Symbol | Characteristics                                | Min | Тур | Max | Units | Comments                                           |  |  |  |

| —                                                                        | Cefc   | External Filter Capacitor Value <sup>(1)</sup> | 4.7 | 10  | —   | μF    | Capacitor must be low series resistance (< 5 ohms) |  |  |  |

**Note 1:** Typical VCORE voltage = 2.5V when  $VDD \ge VDDMIN$ .

# 26.1 High Temperature DC Characteristics

# TABLE 26-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Max MIPS                     |

|----------------|-----------------------------|-------------------|------------------------------|

| Characteristic | (in Volts)                  | (in °C)           | dsPIC33FJXXXGPX06A/X08A/X10A |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 25-11 for the minimum and maximum BOR values.

# TABLE 26-2: THERMAL OPERATING CONDITIONS

| TABLE 20-2. THERMAL OPERATING CONDITIONS                                                                                                                                               |        |               |     |      |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур | Max  | Unit |

| High Temperature Devices                                                                                                                                                               |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | —   | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     |               |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (Тј - Та)/θја |     |      | W    |

## TABLE 26-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |       |                 |

|--------------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|

| Parameter<br>No.   | Symbol    | Characteristic | Min                                                                                                                                                    | Тур | Мах | Units | Conditions      |

| Operating V        | Voltage   |                |                                                                                                                                                        |     |     |       |                 |

| HDC10              | Supply Vo | Itage          |                                                                                                                                                        |     |     |       |                 |

|                    | Vdd       | _              | 3.0                                                                                                                                                    | 3.3 | 3.6 | V     | -40°C to +150°C |

### TABLE 26-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARAC                                                                                                     | TERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |            |      |                                          |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------------------------------------|--|--|--|--|--|

| Parameter<br>No.                                                                                              | Typical   | Мах  | Units                                                                                                                                                  | Conditions |      |                                          |  |  |  |  |  |

| Power-Down Current (IPD)                                                                                      |           |      |                                                                                                                                                        |            |      |                                          |  |  |  |  |  |

| HDC60e                                                                                                        | 250       | 2000 | μA                                                                                                                                                     | +150°C     | 3.3V | Base Power-Down Current <sup>(1,3)</sup> |  |  |  |  |  |

| Note 1. Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and |           |      |                                                                                                                                                        |            |      |                                          |  |  |  |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

# 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters for high temperature devices. However, all AC timing specifications in this section are the same as those in Section 25.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter OS53 in Section 25.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

# TABLE 26-7: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|

|                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$                  |  |  |  |

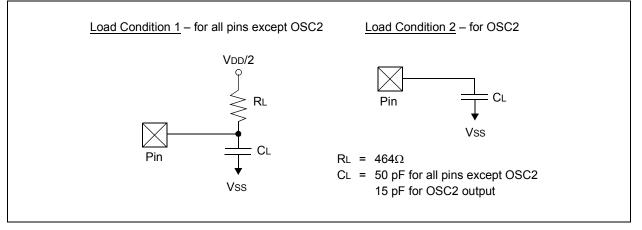

# FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

# TABLE 26-8: PLL CLOCK TIMING SPECIFICATIONS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |    |     |     |       |                             |  |  |

|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|-------|-----------------------------|--|--|

| Param<br>No.          | Symbol | bol Characteristic                                                                                                                                      |    | Тур | Max | Units | Conditions                  |  |  |

| HOS53                 | DCLK   | CLKO Stability (Jitter) <sup>(1)</sup>                                                                                                                  | -5 | 0.5 | 5   | %     | Measured over 100 ms period |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

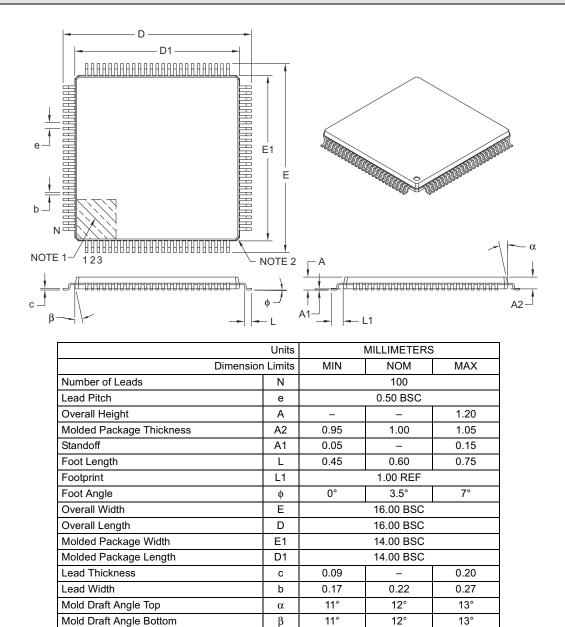

# 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B