Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                  |                                                                                  |

|-------------------------|----------------------------------------------------------------------------------|

| oduct Status            | Active                                                                           |

| re Processor            | dsPIC                                                                            |

| re Size                 | 16-Bit                                                                           |

| eed                     | 40 MIPs                                                                          |

| nnectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| ripherals               | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| mber of I/O             | 53                                                                               |

| ogram Memory Size       | 64KB (64K x 8)                                                                   |

| gram Memory Type        | FLASH                                                                            |

| ROM Size                | -                                                                                |

| M Size                  | 16K x 8                                                                          |

| tage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| a Converters            | A/D 18x10b/12b                                                                   |

| illator Type            | Internal                                                                         |

| erating Temperature     | -40°C ~ 85°C (TA)                                                                |

| unting Type             | Surface Mount                                                                    |

| ckage / Case            | 64-VFQFN Exposed Pad                                                             |

| pplier Device Package   | 64-VQFN (9x9)                                                                    |

| rchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp706a-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

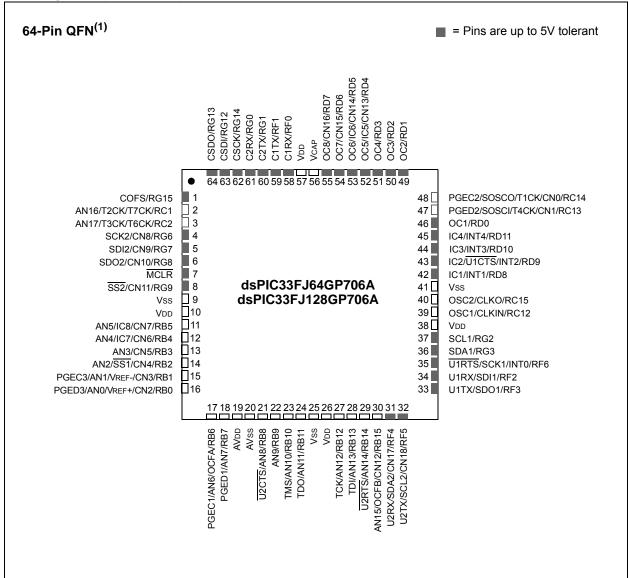

# Pin Diagrams (Continued)

**Note 1:** The metal plane at the bottom of the device is not connected to any pins and should be connected to Vss externally.

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq 8$  MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG and ADPCFG2 registers.

The bits in the registers that correspond to the A/D pins that are initialized by ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG and ADPCFG2 registers during initialization of the ADC module.

When ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG and ADPCFG2 registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

### 3.0 CPU

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

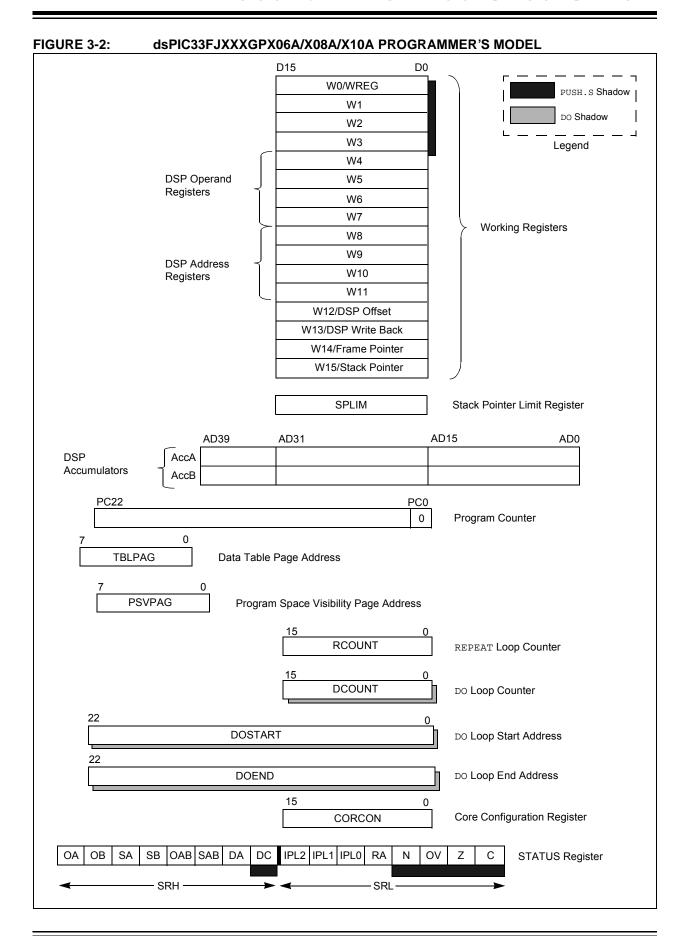

The dsPIC33FJXXXGPX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPlC33FJXXXGPX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPlC33FJXXXGPX06A/X08A/X10A is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJXXXGPX06A/X08A/X10A is shown in Figure 3-2.

# 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own indepen-

dent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space. The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

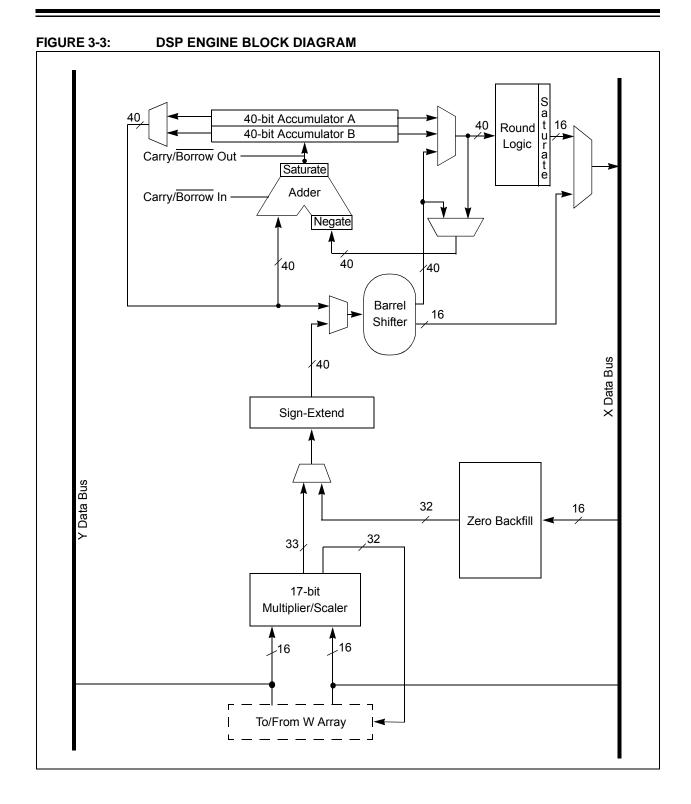

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value, up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

### 3.3 Special MCU Features

The dsPIC33FJXXXGPX06A/X08A/X10A features a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJXXXGPX06A/X08A/X10A supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit, left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

### 3.6.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly, For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

### 3.6.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and between bit positions 0 to 16 for left shifts.

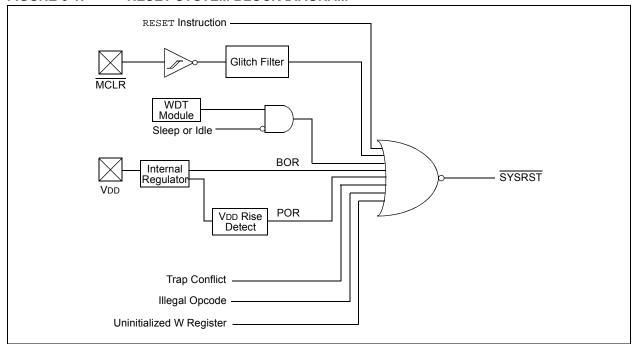

### 6.0 RESET

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

POR: Power-on ResetBOR: Brown-out Reset

MCLR: Master Clear Pin Reset

SWR: RESET Instruction

WDT: Watchdog Timer Reset

TRAPR: Trap Conflict Reset

IOPUWR: Illegal Opcode and Uninitialized W Register Reset A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the POR bit (RCON<0>), that are set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

bit 3

ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred

0 = Address error trap has not occurred

bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1 OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred0 = Oscillator failure trap has not occurred

bit 0 **Unimplemented:** Read as '0'

### 14.1 Input Capture Registers

### REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| _      | _   | ICSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0                | R/W-0 | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|----------------------|-------|-------|---------|---------|-------|----------|-------|

| ICTMR <sup>(1)</sup> | ICI<  | 1:0>  | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7                |       |       |         |         |       |          | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 ICSIDL: Input Capture Module Stop in Idle Control bit

1 = Input capture module will halt in CPU Idle mode

0 = Input capture module will continue to operate in CPU Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 ICTMR: Input Capture Timer Select bits<sup>(1)</sup>

1 = TMR2 contents are captured on capture event 0 = TMR3 contents are captured on capture event

bit 6-5 ICI<1:0>: Select Number of Captures per Interrupt bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow occurred0 = No input capture overflow occurred

bit 3 **ICBNE:** Input Capture Buffer Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode

(Rising edge detect only, all other control bits are not applicable.)

110 = Unused (module disabled)

101 = Capture mode, every 16th rising edge

100 = Capture mode, every 4th rising edge

011 = Capture mode, every rising edge

010 = Capture mode, every falling edge

001 = Capture mode, every edge (rising and falling)

(ICI<1:0> bits do not control interrupt generation for this mode.)

000 = Input capture module turned off

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0                |

|---------------------|-------|-------|--------------------------|-------|-------|-------|----------------------|

| SSEN <sup>(3)</sup> | CKP   | MSTEN | SPRE<2:0> <sup>(2)</sup> |       |       | PPRE< | <1:0> <sup>(2)</sup> |

| bit 7               |       |       |                          |       |       |       | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12 **DISSCK:** Disable SCKx pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled, pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 DISSDO: Disable SDOx pin bit

1 = SDOx pin is not used by module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)<sup>(3)</sup>

$1 = \overline{SSx}$  pin used for Slave mode

$0 = \overline{SSx}$  pin not used by module. Pin controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

# REGISTER 19-8: CIEC: ECAN™ TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0          | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|--------------|-----|-----|-----|-----|-----|-----|-------|--|

| TERRCNT<7:0> |     |     |     |     |     |     |       |  |

| bit 15       |     |     |     |     |     |     | bit 8 |  |

| R-0          | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|--------------|-----|-----|-----|-----|-----|-----|-------|--|

| RERRCNT<7:0> |     |     |     |     |     |     |       |  |

| bit 7        |     |     |     |     |     |     | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 19-10: CICFG2: ECAN™ BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0 | U-0 | U-0 | R/W-x | R/W-x       | R/W-x |

|--------|--------|-----|-----|-----|-------|-------------|-------|

| _      | WAKFIL | _   | _   | _   | ;     | SEG2PH<2:0> |       |

| bit 15 |        |     |     |     |       |             | bit 8 |

| R/W-x    | R/W-x | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x      | R/W-x |

|----------|-------|-------|-------------|-------|-------|------------|-------|

| SEG2PHTS | SAM   |       | SEG1PH<2:0> | ,     |       | PRSEG<2:0> |       |

| bit 7    |       |       |             |       |       |            | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit

1 = Use CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 **Unimplemented:** Read as '0'

bit 10-8 **SEG2PH<2:0>:** Phase Buffer Segment 2 bits

111 = Length is 8 x TQ 000 = Length is 1 x TQ

bit 7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater

bit 6 SAM: Sample of the CAN bus Line bit

1 = Bus line is sampled three times at the sample point0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Buffer Segment 1 bits

111 = Length is 8 x TQ 000 = Length is 1 x TQ

bit 2-0 PRSEG<2:0>: Propagation Time Segment bits

111 = Length is 8 x TQ 000 = Length is 1 x TQ

# REGISTER 19-16: CIRXFnSID: ECAN™ ACCEPTANCE FILTER n STANDARD IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | SID<  | 10:3> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x    | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|----------|-------|-----|-------|-----|-------|-------|

|       | SID<2:0> |       | _   | EXIDE | _   | EID<1 | 7:16> |

| bit 7 |          |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit SIDx must be '1' to match filter 0 = Message address bit SIDx must be '0' to match filter

bit 4 **Unimplemented:** Read as '0'

bit 3 **EXIDE**: Extended Identifier Enable bit

If MIDE = 1 then:

1 = Match only messages with extended identifier addresses0 = Match only messages with standard identifier addresses

If MIDE = 0 then:

Ignore EXIDE bit.

bit 2 Unimplemented: Read as '0'

bit 1-0 EID<17:16>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter 0 = Message address bit EIDx must be '0' to match filter

### REGISTER 19-17: CIRXFnEID: ECAN™ ACCEPTANCE FILTER n EXTENDED IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|

| EID<15:8> |       |       |       |       |       |       |       |  |

| bit 15    |       |       |       |       |       |       | bit 8 |  |

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|

| EID<7:0> |       |       |       |       |       |       |       |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EID<15:0>:** Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

### REGISTER 20-2: DCICON2: DCI CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0     | R/W-0 | U-0 | R/W-0  |

|--------|-----|-----|-----|-----------|-------|-----|--------|

| _      | _   | _   | _   | BLEN<1:0> |       | _   | COFSG3 |

| bit 15 |     |     |     |           |       |     | bit 8  |

| R/W-0 | R/W-0      | R/W-0 | U-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |  |

|-------|------------|-------|-----|---------|-------|-------|-------|--|

|       | COFSG<2:0> |       | _   | WS<3:0> |       |       |       |  |

| bit 7 |            |       |     |         |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-10 **BLEN<1:0>:** Buffer Length Control bits

11 = Four data words will be buffered between interrupts

10 = Three data words will be buffered between interrupts

01 = Two data words will be buffered between interrupts

00 = One data word will be buffered between interrupts

bit 9 Unimplemented: Read as '0'

bit 8-5 **COFSG<3:0>:** Frame Sync Generator Control bits

1111 = Data frame has 16 words

•

.

0010 = Data frame has 3 words 0001 = Data frame has 2 words 0000 = Data frame has 1 word

bit 4 Unimplemented: Read as '0'

bit 3-0 WS<3:0>: DCI Data Word Size bits

1111 = Data word size is 16 bits

•

.

0100 = Data word size is 5 bits 0011 = Data word size is 4 bits

0010 = Invalid Selection. Do not use. Unexpected results may occur

0000 = Invalid Selection. Do not use. Unexpected results may occur

### 22.0 SPECIAL FEATURES

# Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "CodeGuard™ Security" (DS70199), Section 24. "Programming and Diagnostics" (DS70207), and Section 25. "Device Configuration" (DS70194) in the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJXXXGPX06A/X08A/X10A devices include the following features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components:

- · Flexible Configuration

- · Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming™ (ICSP™)

- In-Circuit Emulation

### 22.1 Configuration Bits

dsPIC33FJXXXGPX06A/X08A/X10A devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25.** "**Device Configuration**" (DS70194) of the "dsPIC33F/PIC24H Family Reference Manual", for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The device Configuration register map is shown in Table 22-1.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 22-2.

Note that address 0xF80000 is beyond the user program memory space. In fact, it belongs to the configuration memory space (0x800000-0xFFFFFF) which can only be accessed using table reads and table writes.

### TABLE 22-1: DEVICE CONFIGURATION REGISTER MAP

| Address  | Name    | Bit 7  | Bit 6                   | Bit 5                 | Bit 4          | Bit 3                             | Bit 2    | Bit 1    | Bit 0   |

|----------|---------|--------|-------------------------|-----------------------|----------------|-----------------------------------|----------|----------|---------|

| 0xF80000 | FBS     | RBS    | <1:0>                   | _                     | _              | BSS<2:0>                          |          |          | BWRP    |

| 0xF80002 | FSS     | RSS    | <1:0>                   | _                     | _              |                                   | SSS<2:0> |          | SWRP    |

| 0xF80004 | FGS     | _      | _                       | _                     | _              | _                                 | GSS1     | GSS0     | GWRP    |

| 0xF80006 | FOSCSEL | IESO   | Reserved <sup>(2)</sup> | _                     | _              | — FNOSC<2:0                       |          | SC<2:0>  | •       |

| 0xF80008 | FOSC    | FCKSI  | M<1:0>                  | _                     | _              | <ul><li>— OSCIOFNC POSC</li></ul> |          | POSCN    | 1D<1:0> |

| 0xF8000A | FWDT    | FWDTEN | WINDIS                  | PLLKEN <sup>(3)</sup> | WDTPRE         | WDTPOST<3:0>                      |          |          |         |

| 0xF8000C | FPOR    |        | Reserved <sup>(4)</sup> |                       | _              | _                                 | FPV      | VRT<2:0> | •       |

| 0xF8000E | FICD    | Rese   | rved <sup>(1)</sup>     | JTAGEN                | _              | _                                 | _        | ICS<     | :1:0>   |

| 0xF80010 | FUID0   |        | User Unit ID Byte 0     |                       |                |                                   |          |          |         |

| 0xF80012 | FUID1   |        | User Unit ID Byte 1     |                       |                |                                   |          |          |         |

| 0xF80014 | FUID2   |        | User Unit ID Byte 2     |                       |                |                                   |          |          |         |

| 0xF80016 | FUID3   |        |                         | l                     | Jser Unit ID I | Byte 3                            |          |          |         |

**Legend:** — = unimplemented bit, read as '0'.

- Note 1: These bits are reserved for use by development tools and must be programmed as '1'.

- 2: When read, this bit returns the current programmed value.

- **3:** This bit is unimplemented on dsPIC33FJ64GPX06A/X08A/X10A and dsPIC33FJ128GPX06A/X08A/X10A devices and reads as '0'.

- 4: These bits are reserved and always read as '1'.

# 23.0 INSTRUCTION SET SUMMARY

Note:

This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · DSP operations

- Control operations

Table 23-1 illustrates the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 23-2 provides all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and may include:

- · The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

# TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                | Assembly Syntax                     | Description                                                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------------------------------|-------------------------------------|-------------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Acc,Wx,Wxd,Wy,Wyd |                                     | Multiply Wm by Wn to Accumulator                                        | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    | MPY<br>Wm*Wn         |                                | cc,Wx,Wxd,Wy,Wyd                    | Square Wm to Accumulator                                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,A               | cc,Wx,Wxd,Wy,Wyd                    | -(Multiply Wm by Wn) to Accumulator                                     | 1             | 1              | None                     |

| 50                 | MSC                  | MSC                            | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Subtract from Accumulator                                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS                         | Wb, Ws, Wnd                         | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)                                | 1             | 1              | None                     |

|                    |                      | MUL.SU                         | Wb, Ws, Wnd                         | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                              | 1             | 1              | None                     |

|                    |                      | MUL.US                         | Wb, Ws, Wnd                         | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)                              | 1             | 1              | None                     |

|                    |                      | MUL.UU                         | Wb,Ws,Wnd                           | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)                            | 1             | 1              | None                     |

|                    |                      | MUL.SU                         | Wb,#lit5,Wnd                        | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)                            | 1             | 1              | None                     |

|                    |                      | MUL.UU                         | Wb,#lit5,Wnd                        | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)                          | 1             | 1              | None                     |

|                    |                      | MUL                            | f                                   | W3:W2 = f * WREG                                                        | 1             | 1              | None                     |

| 52                 | NEG                  | NEG                            | Acc                                 | Negate Accumulator                                                      | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG                            | f                                   | $f = \overline{f} + 1$                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG                            | f,WREG                              | WREG = <del>f</del> + 1                                                 | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG Ws, Wd                     |                                     | $Wd = \overline{Ws} + 1$                                                | 1             | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP                            |                                     | No Operation                                                            | 1             | 1              | None                     |

|                    |                      | NOPR                           |                                     | No Operation                                                            | 1             | 1              | None                     |

| 54                 | POP                  | POP                            | f                                   | Pop f from Top-of-Stack (TOS)                                           | 1             | 1              | None                     |

|                    |                      | POP                            | Wdo                                 | Pop from Top-of-Stack (TOS) to Wdo                                      | 1             | 1              | None                     |

|                    |                      | POP.D                          | Wnd                                 | Pop from Top-of-Stack (TOS) to W(nd):W(nd + 1)                          | 1             | 2              | None                     |

|                    |                      | POP.S                          |                                     | Pop Shadow Registers                                                    | 1             | 1              | All                      |

| 55                 | PUSH                 | PUSH                           | f                                   | Push f to Top-of-Stack (TOS)                                            | 1             | 1              | None                     |

|                    |                      | PUSH                           | Wso                                 | Push Wso to Top-of-Stack (TOS)                                          | 1             | 1              | None                     |

|                    |                      | PUSH.D                         | Wns                                 | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)                              | 1             | 2              | None                     |

|                    |                      | PUSH.S                         |                                     | Push Shadow Registers                                                   | 1             | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV                         | #lit1                               | Go into Sleep or Idle mode                                              | 1             | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL                          | Expr                                | Relative Call                                                           | 1             | 2              | None                     |

|                    |                      | RCALL                          | Wn                                  | Computed Call                                                           | 1             | 2              | None                     |

| 58                 | REPEAT               | REPEAT                         | #lit14                              | Repeat Next Instruction lit14 + 1 times                                 | 1             | 1              | None                     |

|                    |                      | REPEAT                         | Wn                                  | Repeat Next Instruction (Wn) + 1 times                                  | 1             | 1              | None                     |

| 59                 | RESET                | RESET                          |                                     | Software device Reset                                                   | 1             | 1              | None                     |

| 60                 | RETFIE               | RETFIE                         |                                     | Return from interrupt                                                   | 1             | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW                          | #lit10,Wn                           | Return with literal in Wn                                               | 1             | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN                         |                                     | Return from Subroutine                                                  | 1             | 3 (2)          | None                     |

| 63                 | RLC                  | RLC                            | f                                   | f = Rotate Left through Carry f                                         | 1             | 1              | C,N,Z                    |

|                    |                      | RLC                            | f,WREG                              | WREG = Rotate Left through Carry Ma                                     | 1             | 1              | C,N,Z                    |

| 64                 | DING                 | RLC                            | Ws,Wd                               | Wd = Rotate Left through Carry Ws                                       | 1             | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC                           | frg                                 | f = Rotate Left (No Carry) f                                            | 1             | 1              | N,Z                      |

|                    |                      | RLNC                           | f,WREG                              | WREG = Rotate Left (No Carry) f                                         | 1             | 1              | N,Z                      |

| 65                 | DDC.                 | RLNC                           | Ws,Wd                               | Wd = Rotate Left (No Carry) Ws                                          | 1             | 1              | N,Z                      |

| 65                 | RRC                  | RRC                            | f WREC                              | f = Rotate Right through Carry f                                        | 1             | 1              | C,N,Z                    |

|                    |                      | RRC                            | f,WREG<br>Ws,Wd                     | WREG = Rotate Right through Carry f  Wd = Rotate Right through Carry Ws | 1             | 1              | C,N,Z<br>C,N,Z           |

# 25.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXGPX06A/X08A/X10A AC characteristics and timing parameters.

### TABLE 25-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                            |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |  |  |  |  |

|                    | -40°C ≤ TA ≤ +125°C for Extended                                                                 |  |  |  |  |

|                    | Operating voltage VDD range as described in Table 25-1.                                          |  |  |  |  |

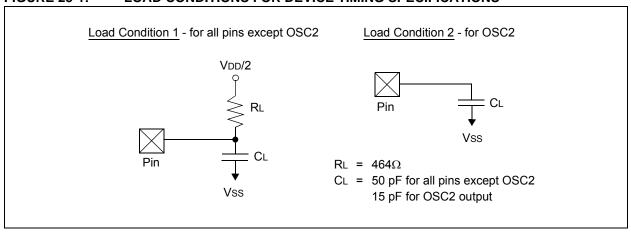

### FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 25-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                   |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | _   | 15  | pF    | In XT and HS modes when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O pins and OSC2 | _   | _   | 50  | pF    | EC mode                                                      |

| DO58         | Св     | SCLx, SDAx            | _   |     | 400 | pF    | In I <sup>2</sup> C™ mode                                    |

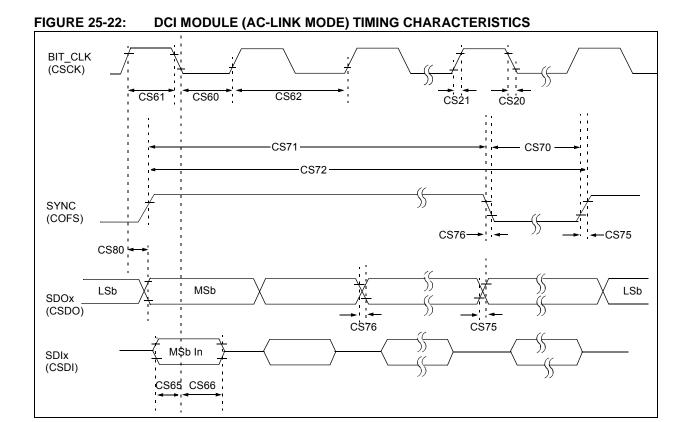

TABLE 25-39: DCI MODULE (AC-LINK MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} -40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |     |       |                         |  |

|--------------------|---------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------|--|

| Param<br>No.       | Symbol  | Characteristic <sup>(1,2)</sup>                | Min                                                                                                                                                                                                                             | Typ <sup>(3)</sup> | Max | Units | Conditions              |  |

| CS60               | TBCLKL  | BIT_CLK Low Time                               | 36                                                                                                                                                                                                                              | 40.7               | 45  | ns    | _                       |  |

| CS61               | TBCLKH  | BIT_CLK High Time                              | 36                                                                                                                                                                                                                              | 40.7               | 45  | ns    | _                       |  |

| CS62               | TBCLK   | BIT_CLK Period                                 | _                                                                                                                                                                                                                               | 81.4               | _   | ns    | Bit clock is input      |  |

| CS65               | TSACL   | Input Setup Time to Falling Edge of BIT_CLK    | _                                                                                                                                                                                                                               | _                  | 10  | ns    | _                       |  |

| CS66               | THACL   | Input Hold Time from Falling Edge of BIT_CLK   | _                                                                                                                                                                                                                               | _                  | 10  | ns    | _                       |  |

| CS70               | TSYNCLO | SYNC Data Output Low Time                      | _                                                                                                                                                                                                                               | 19.5               | _   | μS    | Note 1                  |  |

| CS71               | TSYNCHI | SYNC Data Output High Time                     | _                                                                                                                                                                                                                               | 1.3                | _   | μS    | Note 1                  |  |

| CS72               | TSYNC   | SYNC Data Output Period                        | _                                                                                                                                                                                                                               | 20.8               | _   | μS    | Note 1                  |  |

| CS75               | TRACL   | Rise Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                               | 10                 | 25  | ns    | CLOAD = 50 pF, VDD = 5V |  |

| CS76               | TFACL   | Fall Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                               | 10                 | 25  | ns    | CLOAD = 50 pF, VDD = 5V |  |

| CS77               | TRACL   | Rise Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                               | _                  | 30  | ns    | CLOAD = 50 pF, VDD = 3V |  |

| CS78               | TFACL   | Fall Time, SYNC, SDATA_OUT                     | _                                                                                                                                                                                                                               | _                  | 30  | ns    | CLOAD = 50 pF, VDD = 3V |  |

| CS80               | TOVDACL | Output Valid Delay from Rising Edge of BIT_CLK | _                                                                                                                                                                                                                               | _                  | 15  | ns    | _                       |  |

- **Note 1:** These parameters are characterized but not tested in manufacturing.

- 2: These values assume BIT\_CLK frequency is 12.288 MHz.

- **3:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

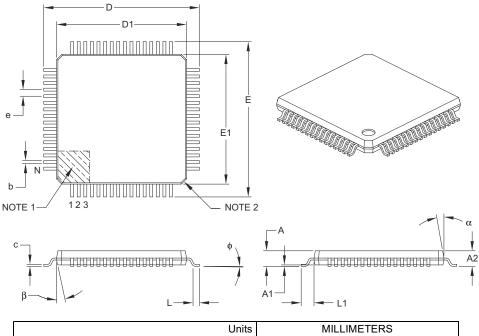

# 64-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |           |      |  |

|--------------------------|------------------|-------------|-----------|------|--|

|                          | Dimension Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          | N                |             | 64        |      |  |

| Lead Pitch               | е                |             | 0.50 BSC  |      |  |

| Overall Height           | A                | _           | _         | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1               | 0.05        | _         | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |           |      |  |

| Foot Angle               | ф                | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E                |             | 12.00 BSC |      |  |

| Overall Length           | D                |             | 12.00 BSC |      |  |

| Molded Package Width     | E1               |             | 10.00 BSC |      |  |

| Molded Package Length    | D1               |             | 10.00 BSC |      |  |

| Lead Thickness           | С                | 0.09        | _         | 0.20 |  |

| Lead Width               | b                | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B