Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$= K \in$

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

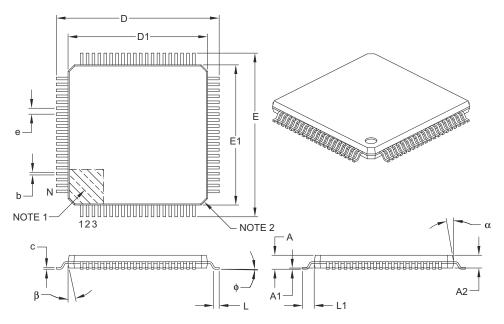

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp706at-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section

2. "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

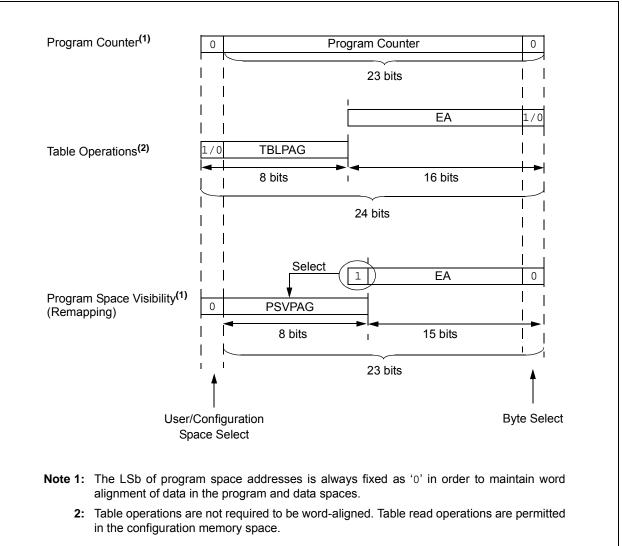

The dsPIC33FJXXXGPX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXGPX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPIC33FJXXXGPX06A/X08A/X10A is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJXXXGPX06A/ X08A/X10A is shown in Figure 3-2.

### 3.1 Data Addressing Overview

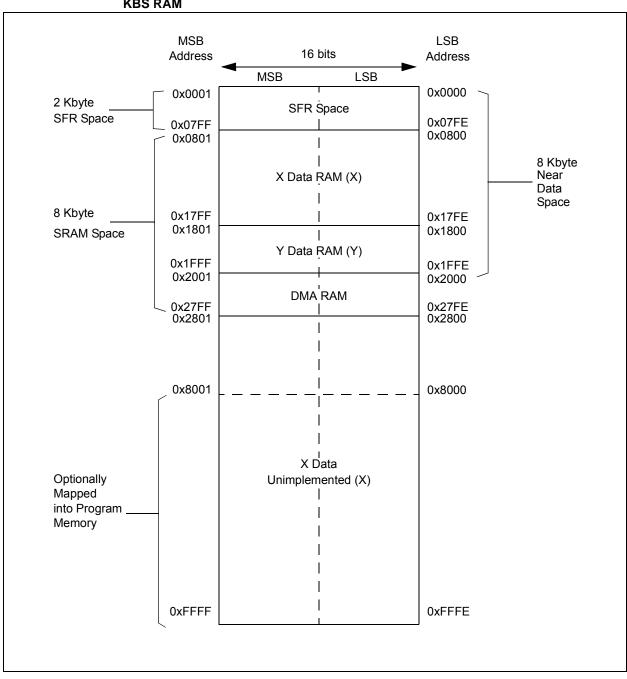

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own indepen-

dent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space. The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value, up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

### 3.3 Special MCU Features

The dsPIC33FJXXXGPX06A/X08A/X10A features a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJXXXGPX06A/X08A/X10A supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit, left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 8 KBS RAM

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX10A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       | —       | —       | _       | _       | _       | _      | _      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX08A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | —       |         | _       | _       |         | —       |        | _      | _      |        | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       |         | _       | _       |         | _       |        |        | _      |        | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX06A DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       |        |        | _      | _      | CN21IE  | CN20IE  |        | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21PUE | CN20PUE |        | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|         | 1-6:        |        |        | STER N |        |        |        |              |              |               |                |       |        |       |       |       |       |               |

|---------|-------------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------------|----------------|-------|--------|-------|-------|-------|-------|---------------|

|         | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1    | 0100        |        |        |        |        |        |        |              | Timer1       | Register      |                |       |        |       |       |       |       | 0000          |

| PR1     | 0102        |        |        |        |        |        |        |              |              | Register 1    |                |       |        |       |       |       |       | FFFF          |

| T1CON   | 0104        | TON    | —      | TSIDL  | _      | —      | —      | —            | —            | —             | TGATE          | TCKP  | S<1:0> | _     | TSYNC | TCS   | —     | 0000          |

| TMR2    | 0106        |        |        |        |        |        |        |              | Timer2       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR3HLD | 0108        |        |        |        |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time | r operations o | only) |        |       |       |       |       | xxxx          |

| TMR3    | 010A        |        |        |        |        |        |        |              | Timer3       | Register      |                |       |        |       |       |       |       | 0000          |

| PR2     | 010C        |        |        |        |        |        |        |              | Period F     | Register 2    |                |       |        |       |       |       |       | FFFF          |

| PR3     | 010E        |        |        |        |        |        |        |              | Period F     | Register 3    |                |       |        |       |       |       |       | FFFF          |

| T2CON   | 0110        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T3CON   | 0112        | TON    | _      | TSIDL  | _      | _      | —      | _            | _            | _             | TGATE          | TCKP  | S<1:0> |       | _     | TCS   | _     | 0000          |

| TMR4    | 0114        |        |        |        |        |        |        |              | Timer4       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR5HLD | 0116        |        |        |        |        |        | -      | Timer5 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR5    | 0118        |        |        |        |        |        |        |              | Timer5       | Register      |                |       |        |       |       |       |       | 0000          |

| PR4     | 011A        |        |        |        |        |        |        |              | Period F     | Register 4    |                |       |        |       |       |       |       | FFFF          |

| PR5     | 011C        |        |        |        |        |        |        |              | Period F     | Register 5    |                |       |        |       |       |       |       | FFFF          |

| T4CON   | 011E        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON   | 0120        | TON    | —      | TSIDL  | _      |        | -      |              | —            |               | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   |       | 0000          |

| TMR6    | 0122        |        |        |        |        |        |        |              | Timer6       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR7HLD | 0124        |        |        |        |        |        | -      | Timer7 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR7    | 0126        |        |        |        |        |        |        |              | Timer7       | Register      |                |       |        |       |       |       |       | 0000          |

| PR6     | 0128        |        |        |        |        |        |        |              | Period F     | Register 6    |                |       |        |       |       |       |       | FFFF          |

| PR7     | 012A        |        |        |        |        |        |        |              | Period F     | Register 7    |                |       |        |       |       |       |       | FFFF          |

| T6CON   | 012C        | TON    | —      | TSIDL  |        |        |        |              | —            |               | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T7CON   | 012E        | TON    | —      | TSIDL  |        |        |        |              | —            |               | TGATE          | TCKP  | S<1:0> |       | —     | TCS   |       | 0000          |

| TMR8    | 0130        |        |        |        |        |        |        |              | Timer8       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR9HLD | 0132        |        |        |        |        |        | -      | Timer9 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR9    | 0134        |        |        |        |        |        |        |              | Timer9       | Register      |                |       |        |       |       |       |       | 0000          |

| PR8     | 0136        |        |        |        |        |        |        |              | Period F     | Register 8    |                |       |        |       |       |       |       | FFFF          |

| PR9     | 0138        |        |        |        |        |        |        |              | Period F     | Register 9    |                |       |        |       |       |       |       | FFFF          |

| T8CON   | 013A        | TON    | —      | TSIDL  | _      | _      | —      | —            | —            | _             | TGATE          | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T9CON   | 013C        | TON    | —      | TSIDL  | —      | —      | —      | —            | —            | —             | TGATE          | TCKP  | S<1:0> | —     | —     | TCS   | —     | 0000          |

#### TABLE 4-6: TIMER REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33FJXXXGPX06A/X08A/X10A

| TABLE 4   | I-17: | DMA           | REGIS            | TER M  | AP (CO | NTINUE     | D)     |        |        |          |        |        |        |           |        |        |        |              |

|-----------|-------|---------------|------------------|--------|--------|------------|--------|--------|--------|----------|--------|--------|--------|-----------|--------|--------|--------|--------------|

| File Name | Addr  | Bit 15        | Bit 14           | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9  | Bit 8  | Bit 7    | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Reset |

| DMA5CNT   | 03C6  | _             | _                | _      | _      | _          | _      |        |        |          |        | CN1    | <9:0>  |           |        |        |        | 0000         |

| DMA6CON   | 03C8  | CHEN          | SIZE             | DIR    | HALF   | NULLW      | _      | _      | _      | _        | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000         |

| DMA6REQ   | 03CA  | FORCE         | _                | _      | _      | _          | _      | —      | _      | _        |        |        |        | RQSEL<6:0 | >      |        |        | 0000         |

| DMA6STA   | 03CC  |               |                  |        |        |            |        |        | S      | TA<15:0> |        |        |        |           |        |        |        | 0000         |

| DMA6STB   | 03CE  |               |                  |        |        |            |        |        | S      | TB<15:0> |        |        |        |           |        |        |        | 0000         |

| DMA6PAD   | 03D0  | PAD<15:0> 000 |                  |        |        |            |        |        |        |          |        |        |        | 0000      |        |        |        |              |

| DMA6CNT   | 03D2  |               |                  |        |        |            |        |        |        |          |        |        |        | 0000      |        |        |        |              |

| DMA7CON   | 03D4  | CHEN          | SIZE             | DIR    | HALF   | NULLW      | _      |        | _      | _        | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000         |

| DMA7REQ   | 03D6  | FORCE         | —                | _      | _      | _          | _      |        | _      | _        |        |        | I      | RQSEL<6:0 | >      |        |        | 0000         |

| DMA7STA   | 03D8  |               | •                | •      | •      |            |        |        | S      | TA<15:0> | •      |        |        |           |        |        |        | 0000         |

| DMA7STB   | 03DA  |               |                  |        |        |            |        |        | S      | TB<15:0> |        |        |        |           |        |        |        | 0000         |

| DMA7PAD   | 03DC  |               |                  |        |        |            |        |        | P      | AD<15:0> |        |        |        |           |        |        |        | 0000         |

| DMA7CNT   | 03DE  | _             | _                | _      | _      | _          | —      |        |        |          |        | CNT    | <9:0>  |           |        |        |        | 0000         |

| DMACS0    | 03E0  | PWCOL7        | PWCOL6           | PWCOL5 | PWCOL4 | PWCOL3     | PWCOL2 | PWCOL1 | PWCOL0 | XWCOL7   | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000         |

| DMACS1    | 03E2  | —             | _                | _      | _      |            | LSTCH  | 1<3:0> |        | PPST7    | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000         |

| DSADR     | 03E4  |               | DSADR<15:0> 0000 |        |        |            |        |        |        |          |        |        |        |           |        |        |        |              |

| امعمماه   |       |               |                  |        |        | a abour in |        |        |        |          |        |        |        |           |        |        |        |              |

#### \_\_\_\_\_

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

dsPIC33FJXXXGPX06A/X08A/X10A

| File Name  | Addr          | Bit 15    | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7      | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|-----------|------------------------|--------|--------|--------|--------|--------|-------------|------------|----------|--------|-------|-------|-------|--------|--------|---------------|

|            | 0400-<br>041E |           |                        |        |        |        |        |        | See definit | ion when V | /IN = x  |        |       |       |       |        |        |               |

| C1BUFPNT1  | 0420          |           | F3BP                   | <3:0>  |        |        | F2BF   | ><3:0> |             |            | F1BP     | <3:0>  |       |       | F0BP  | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |           | F7BP                   | <3:0>  |        |        | F6BF   | ><3:0> |             |            | F5BP     | <3:0>  |       |       | F4BP  | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |           | F11BF                  | ><3:0> |        |        | F10B   | P<3:0> |             |            | F9BP     | <3:0>  |       |       | F8BP  | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15BF                  | P<3:0> |        |        | F14B   | P<3:0> |             |            | F13B     | P<3:0> |       |       | F12BF | °<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | MIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  | •     |        |        | xxxx          |

| C1RXM1SID  | 0434          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  | •     |        |        | xxxx          |

| C1RXM2SID  | 0438          |           | SID<10:3><br>EID<15:8> |        |        |        |        |        |             |            | SID<2:0> |        | —     | MIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |           | EID<15:8>              |        |        |        |        |        |             |            |          |        | EID<  | 7:0>  |       | •      |        | xxxx          |

| C1RXF0SID  | 0440          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | _     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |           | EID<15:8>              |        |        |        |        |        |             |            |          |        | EID<  | 7:0>  |       | •      |        | xxxx          |

| C1RXF1SID  | 0444          |           | SID<10:3>              |        |        |        |        |        |             |            | SID<2:0> |        | _     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |           | SID<10:3><br>EID<15:8> |        |        |        |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF2SID  | 0448          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |       | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF3SID  | 044C          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | _     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF4SID  | 0450          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | _     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF5SID  | 0454          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF6SID  | 0458          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF7SID  | 045C          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          | EID<15:8> |                        |        |        |        |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF8SID  | 0460          |           | SID<10:3>              |        |        |        |        |        |             |            | SID<2:0> |        | —     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF9SID  | 0464          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | _     | EXIDE | _     | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF10SID | 0468          |           |                        |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |           |                        |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### FIGURE 4-9: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER 7      | '-8: IFS3: I    | INTERRUPT                        | FLAG STAT       | US REGIST        | ER 3             |                 |       |

|-----------------|-----------------|----------------------------------|-----------------|------------------|------------------|-----------------|-------|

| U-0             | U-0             | R/W-0                            | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |

| _               | _               | DMA5IF                           | DCIIF           | DCIEIF           | _                | —               | C2IF  |

| bit 15          |                 |                                  |                 | •                |                  |                 | bit 8 |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIF          | INT4IF          | INT3IF                           | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |

| bit 7           |                 |                                  |                 |                  |                  |                 | bit 0 |

| Legend:         |                 |                                  |                 |                  |                  |                 |       |

| R = Readable    | bit             | W = Writable                     | bit             | U = Unimple      | mented bit, read | as '0'          |       |

| -n = Value at I |                 | '1' = Bit is set                 |                 | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                 |                 |                                  |                 |                  |                  |                 |       |

| bit 15-14       | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 13          | DMA5IF: DM      | A Channel 5 D                    | ata Transfer (  | Complete Inter   | rupt Flag Status | bit             |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 12          | DCIIF: DCI E    | vent Interrupt I                 | -lag Status bit |                  |                  |                 |       |

|                 | 1 = Interrupt   | request has oc                   | curred          |                  |                  |                 |       |

|                 | •               | request has no                   |                 |                  |                  |                 |       |

| bit 11          |                 | Error Interrupt                  | U               | it               |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 10-9        | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |

| bit 8           | C2IF: ECAN2     | 2 Event Interrup                 | ot Flag Status  | bit              |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 7           | C2RXIF: ECA     | AN2 Receive D                    | ata Ready Int   | errupt Flag Sta  | atus bit         |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 6           | •               | rnal Interrupt 4                 |                 | it               |                  |                 |       |

|                 | 1 = Interrupt i | request has oc<br>request has no | curred          |                  |                  |                 |       |

| bit 5           | INT3IF: Exter   | rnal Interrupt 3                 | Flag Status b   | it               |                  |                 |       |

|                 | •               | request has oc<br>request has no |                 |                  |                  |                 |       |

| bit 4           | -               | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 | 1 = Interrupt i | request has oc                   | curred          |                  |                  |                 |       |

|                 | 0 = Interrupt   | request has no                   | t occurred      |                  |                  |                 |       |

| bit 3           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

| bit 2           | -               | request has no<br>2 Master Even  |                 | ag Status bit    |                  |                 |       |

| SIL Z           |                 | request has oc                   | •               | ug oluluo bit    |                  |                 |       |

|                 |                 | request has no                   |                 |                  |                  |                 |       |

| bit 1           | SI2C2IF: 12C    | 2 Slave Events                   | Interrupt Flag  | g Status bit     |                  |                 |       |

|                 |                 | request has oc                   |                 |                  |                  |                 |       |

|                 | -               | request has no                   |                 |                  |                  |                 |       |

| bit 0           |                 | Interrupt Flag                   |                 |                  |                  |                 |       |

|                 |                 | request has oc<br>request has no |                 |                  |                  |                 |       |

|                 |                 | iequest nas no                   |                 |                  |                  |                 |       |

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | ST/   | \<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                 |                 |       |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

### 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 25-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 25.0 "Electrical Characteristics" for additional information.

### 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546064

#### 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

|               |            |                                         |                 |                  | •              |                |       |

|---------------|------------|-----------------------------------------|-----------------|------------------|----------------|----------------|-------|

| U-0           | U-0        | R/W-0                                   | U-0             | U-0              | U-0            | U-0            | U-0   |

| _             | _          | OCSIDL                                  | _               | _                |                | —              | _     |

| bit 15        |            |                                         |                 |                  |                |                | bit 8 |

|               |            |                                         |                 |                  |                |                |       |

| U-0           | U-0        | U-0                                     | R-0, HC         | R/W-0            | R/W-0          | R/W-0          | R/W-0 |

| —             | —          | —                                       | OCFLT           | OCTSEL           |                | OCM<2:0>       |       |

| bit 7         |            |                                         |                 |                  |                |                | bit 0 |

|               |            |                                         |                 |                  |                |                |       |

| Legend:       |            | HC = Hardware                           | Clearable bit   |                  |                |                |       |

| R = Readable  | e bit      | W = Writable bit                        |                 | U = Unimple      | mented bit, re | ad as '0'      |       |

| -n = Value at | POR        | '1' = Bit is set                        |                 | '0' = Bit is cle | eared          | x = Bit is unk | nown  |

|               |            |                                         |                 |                  |                |                |       |

| bit 15-14     | Unimpleme  | nted: Read as '0'                       |                 |                  |                |                |       |

| bit 13        | OCSIDL: St | op Output Compa                         | re in Idle Mode | Control bit      |                |                |       |

|               |            | Compare x halts in<br>Compare x continu |                 |                  | de             |                |       |

- bit 12-5 Unimplemented: Read as '0'

- bit 4 OCFLT: PWM Fault Condition Status bit

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111)

- bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for Compare x

- 0 = Timer2 is the clock source for Compare x

#### bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx, Fault pin enabled

- 110 = PWM mode on OCx, Fault pin disabled

- 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low, generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high, compare event forces OCx pin low

- 001 = Initialize OCx pin low, compare event forces OCx pin high

- 000 = Output compare channel is disabled

| U-0                 | U-0                          | U-0                                   | R/W-0                  | R/W-0                                  | R/W-0              | R/W-0              | R/W-0                |

|---------------------|------------------------------|---------------------------------------|------------------------|----------------------------------------|--------------------|--------------------|----------------------|

| —                   |                              |                                       | DISSCK                 | DISSDO                                 | MODE16             | SMP                | CKE <sup>(1)</sup>   |

| bit 15              |                              |                                       |                        |                                        |                    |                    | bit                  |

|                     |                              |                                       |                        |                                        |                    |                    |                      |

| R/W-0               | R/W-0                        | R/W-0                                 | R/W-0                  | R/W-0                                  | R/W-0              | R/W-0              | R/W-0                |

| SSEN <sup>(3)</sup> | CKP                          | MSTEN                                 |                        | SPRE<2:0>(2                            | -)                 | PPRE<              | <1:0> <sup>(2)</sup> |

| bit 7               |                              |                                       |                        |                                        |                    |                    | bit                  |

| Legend:             |                              |                                       |                        |                                        |                    |                    |                      |

| R = Readab          | le bit                       | W = Writable                          | bit                    | U = Unimplen                           | nented bit, read   | as '0'             |                      |

| -n = Value a        | t POR                        | '1' = Bit is set                      | :                      | '0' = Bit is cle                       | ared               | x = Bit is unkr    | nown                 |

|                     |                              |                                       |                        |                                        |                    |                    |                      |

| bit 15-13           | Unimplemen                   | nted: Read as '                       | 0'                     |                                        |                    |                    |                      |

| bit 12              |                              | able SCKx pin                         | -                      |                                        |                    |                    |                      |

|                     |                              | SPI clock is disa<br>SPI clock is ena |                        | ctions as I/O                          |                    |                    |                      |

| bit 11              |                              | able SDOx pin                         |                        |                                        |                    |                    |                      |

|                     |                              | -                                     |                        | functions as I/O                       | )                  |                    |                      |

|                     |                              | is controlled b                       |                        |                                        | ,                  |                    |                      |

| bit 10              | MODE16: Wo                   | ord/Byte Comm                         | nunication Sel         | ect bit                                |                    |                    |                      |

|                     |                              | ication is word-<br>ication is byte-  |                        |                                        |                    |                    |                      |

| bit 9               |                              | ata Input Sam                         |                        |                                        |                    |                    |                      |

|                     | Master mode                  |                                       |                        |                                        |                    |                    |                      |

|                     |                              | a sampled at e                        |                        |                                        |                    |                    |                      |

|                     | Slave mode:                  | a sampled at m                        |                        | Sulput lime                            |                    |                    |                      |

|                     |                              | e cleared when                        | SPIx is used           | in Slave mode.                         |                    |                    |                      |

| bit 8               | CKE: SPIx C                  | lock Edge Sele                        | ect bit <sup>(1)</sup> |                                        |                    |                    |                      |

|                     |                              |                                       |                        |                                        | clock state to Id  |                    |                      |

| bit 7               |                              | Select Enable                         |                        |                                        | ock state to activ | e clock state (    | see bit 0)           |

|                     |                              | used for Slave                        |                        | ue).                                   |                    |                    |                      |

|                     |                              |                                       |                        | rolled by port fu                      | unction            |                    |                      |

| bit 6               | CKP: Clock F                 | Polarity Select                       | oit                    |                                        |                    |                    |                      |

|                     |                              |                                       | •                      | ve state is a lov<br>e state is a higł |                    |                    |                      |

| bit 5               | MSTEN: Mas                   | ster Mode Enat                        | ole bit                |                                        |                    |                    |                      |

|                     | 1 = Master m<br>0 = Slave mo |                                       |                        |                                        |                    |                    |                      |

|                     | The CKE bit is not           |                                       | amed SPI mo            | des. The user s                        | should program     | this bit to '0' fo | or the Frame         |

|                     | SPI modes (FRME              | $\pm in = \pm j.$                     |                        |                                        |                    |                    |                      |

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

| U-0          | U-0                                                       | U-0                                                                                                                                         | U-0                   | R/W-0                              | R/W-0               | U-0            | R/W-0  |  |  |  |  |

|--------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|---------------------|----------------|--------|--|--|--|--|

|              |                                                           | _                                                                                                                                           | —                     | BLEN                               | <b>\&lt;1:0&gt;</b> |                | COFSG3 |  |  |  |  |

| bit 15       |                                                           |                                                                                                                                             |                       |                                    |                     |                | bit    |  |  |  |  |

|              |                                                           |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

| R/W-0        | R/W-0                                                     | R/W-0                                                                                                                                       | U-0                   | R/W-0                              | R/W-0               | R/W-0          | R/W-0  |  |  |  |  |

|              | COFSG<2:0>                                                |                                                                                                                                             |                       |                                    | WS                  | <3:0>          |        |  |  |  |  |

| bit 7        |                                                           |                                                                                                                                             |                       |                                    |                     |                | bit    |  |  |  |  |

|              |                                                           |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

| Legend:      |                                                           |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

| R = Readab   |                                                           | W = Writable                                                                                                                                |                       |                                    | nented bit, read    |                |        |  |  |  |  |

| -n = Value a | t POR                                                     | '1' = Bit is set                                                                                                                            |                       | '0' = Bit is clea                  | ared                | x = Bit is unk | nown   |  |  |  |  |

|              |                                                           |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

| bit 15-12    | -                                                         | ted: Read as '                                                                                                                              |                       |                                    |                     |                |        |  |  |  |  |

| bit 11-10    | BLEN<1:0>:                                                | Buffer Length (                                                                                                                             | Control bits          |                                    |                     |                |        |  |  |  |  |

|              |                                                           | 11 = Four data words will be buffered between interrupts                                                                                    |                       |                                    |                     |                |        |  |  |  |  |

|              | 10 = Three data words will be buffered between interrupts |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              |                                                           | <ul> <li>01 = Two data words will be buffered between interrupts</li> <li>00 = One data word will be buffered between interrupts</li> </ul> |                       |                                    |                     |                |        |  |  |  |  |

|              |                                                           |                                                                                                                                             |                       | een interrupts                     |                     |                |        |  |  |  |  |

| bit 9        | -                                                         | ted: Read as '                                                                                                                              |                       |                                    |                     |                |        |  |  |  |  |

| bit 8-5      | COFSG<3:0>: Frame Sync Generator Control bits             |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | 1111 = Data frame has 16 words                            |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | •                                                         |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | •                                                         |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | •<br>0010 = Data :                                        | frame has 3 wo                                                                                                                              | orde                  |                                    |                     |                |        |  |  |  |  |

|              |                                                           | frame has 2 wo                                                                                                                              |                       |                                    |                     |                |        |  |  |  |  |

|              |                                                           | frame has 1 wo                                                                                                                              |                       |                                    |                     |                |        |  |  |  |  |

| bit 4        | Unimplemen                                                | ted: Read as '                                                                                                                              | 0'                    |                                    |                     |                |        |  |  |  |  |

| bit 3-0      | WS<3:0>: DO                                               | I Data Word S                                                                                                                               | ize bits              |                                    |                     |                |        |  |  |  |  |

|              | 1111 <b>= Data</b>                                        | word size is 16                                                                                                                             | bits                  |                                    |                     |                |        |  |  |  |  |

|              | •                                                         |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | •                                                         |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              |                                                           |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              | •                                                         |                                                                                                                                             |                       |                                    |                     |                |        |  |  |  |  |

|              |                                                           | word size is 5 k                                                                                                                            |                       |                                    |                     |                |        |  |  |  |  |

|              | 0011 <b>= Data</b>                                        | word size is 4 b                                                                                                                            | oits                  |                                    | 40                  |                |        |  |  |  |  |

|              | 0011 <b>= Data</b><br>0010 <b>= Inval</b>                 | word size is 4 t<br>d Selection. D                                                                                                          | oits<br>Io not use. U | nexpected resul<br>nexpected resul |                     |                |        |  |  |  |  |

#### REGISTER 20-2: DCICON2: DCI CONTROL REGISTER 2

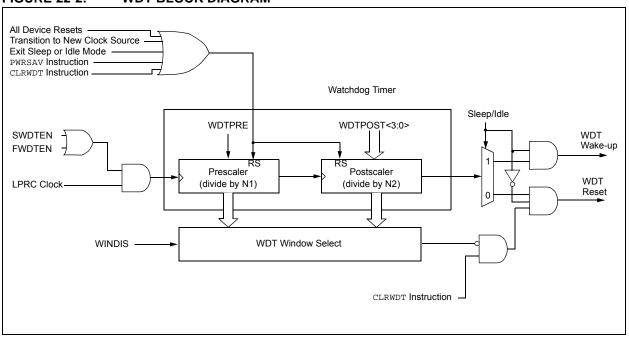

### 22.4 Watchdog Timer (WDT)

For dsPIC33FJXXXGPX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler and then can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

### FIGURE 22-2: WDT BLOCK DIAGRAM

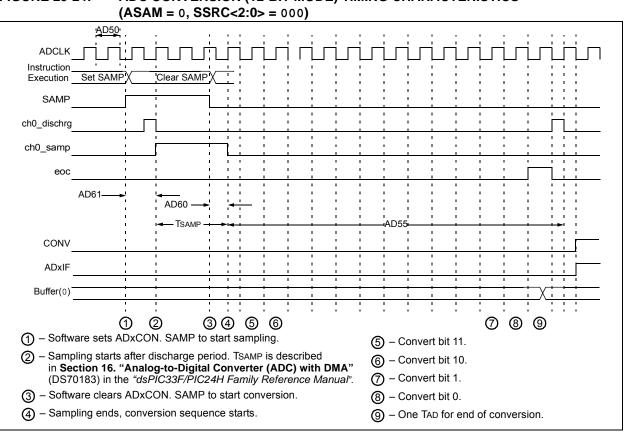

# FIGURE 25-24: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS

#### TABLE 26-14: ADC MODULE SPECIFICATIONS

| AC<br>CHARACTERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |                     |           |            |                                                                |  |  |

|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----------|------------|----------------------------------------------------------------|--|--|

| Param<br>No. Symbol   |      | Characteristic                                                                                                                                          | Min | Min Typ Max Units C |           | Conditions |                                                                |  |  |

| Reference Inputs      |      |                                                                                                                                                         |     |                     |           |            |                                                                |  |  |

| HAD08                 | IREF | Current Drain                                                                                                                                           |     | 250<br>—            | 600<br>50 | μΑ<br>μΑ   | ADC operating, See <b>Note 1</b><br>ADC off, See <b>Note 1</b> |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

**2:** These parameters are characterized, but are not tested in manufacturing.

#### TABLE 26-15: ADC MODULE SPECIFICATIONS (12-BIT MODE)<sup>(3)</sup>

| -            | AC<br>TERISTICS                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |     |       |                                                  |  |  |

|--------------|------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----|-----|-------|--------------------------------------------------|--|--|