Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp708a-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| bit 8  |    | DC: MCU ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | <ul> <li>1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data)<br/>of the result occurred</li> </ul>                                                                                                                                                                                                                                                                             |

|        |    | <ul> <li>0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                |

| bit 7- | 5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|        |    | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4  |    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |    | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3  |    | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |    | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2  |    | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |    | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                |

| bit 1  |    | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |    | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                               |

| bit 0  |    | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |    | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

| Note   | 1: | This bit may be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                                                  |

|        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

|         | 1-6:        |        |        | STER N |        |        |        |              |              |               |                |       |        |       |       |       |       |               |

|---------|-------------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------------|----------------|-------|--------|-------|-------|-------|-------|---------------|

|         | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1    | 0100        |        |        |        |        |        |        |              | Timer1       | Register      |                |       |        |       |       |       |       | 0000          |

| PR1     | 0102        |        |        |        |        |        |        |              |              | Register 1    |                |       |        |       |       |       |       | FFFF          |

| T1CON   | 0104        | TON    | —      | TSIDL  | _      | —      | —      | —            | —            | —             | TGATE          | TCKP  | S<1:0> | _     | TSYNC | TCS   | —     | 0000          |

| TMR2    | 0106        |        |        |        |        |        |        |              | Timer2       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR3HLD | 0108        |        |        |        |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time | r operations o | only) |        |       |       |       |       | xxxx          |

| TMR3    | 010A        |        |        |        |        |        |        |              | Timer3       | Register      |                |       |        |       |       |       |       | 0000          |

| PR2     | 010C        |        |        |        |        |        |        |              | Period F     | Register 2    |                |       |        |       |       |       |       | FFFF          |

| PR3     | 010E        |        |        |        |        |        |        |              | Period F     | Register 3    |                |       |        |       |       |       |       | FFFF          |

| T2CON   | 0110        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T3CON   | 0112        | TON    | _      | TSIDL  | _      | _      | —      | _            | _            | _             | TGATE          | TCKP  | S<1:0> |       | _     | TCS   | _     | 0000          |

| TMR4    | 0114        |        |        |        |        |        |        |              | Timer4       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR5HLD | 0116        |        |        |        |        |        | -      | Timer5 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR5    | 0118        |        |        |        |        |        |        |              | Timer5       | Register      |                |       |        |       |       |       |       | 0000          |

| PR4     | 011A        |        |        |        |        |        |        |              | Period F     | Register 4    |                |       |        |       |       |       |       | FFFF          |

| PR5     | 011C        |        |        |        |        |        |        |              | Period F     | Register 5    |                |       |        |       |       |       |       | FFFF          |

| T4CON   | 011E        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON   | 0120        | TON    | —      | TSIDL  | _      |        | _      |              | —            |               | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   |       | 0000          |

| TMR6    | 0122        |        |        |        |        |        |        |              | Timer6       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR7HLD | 0124        |        |        |        |        |        | -      | Timer7 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR7    | 0126        |        |        |        |        |        |        |              | Timer7       | Register      |                |       |        |       |       |       |       | 0000          |

| PR6     | 0128        |        |        |        |        |        |        |              | Period F     | Register 6    |                |       |        |       |       |       |       | FFFF          |

| PR7     | 012A        |        |        |        |        |        |        |              | Period F     | Register 7    |                |       |        |       |       |       |       | FFFF          |

| T6CON   | 012C        | TON    | —      | TSIDL  |        |        |        |              | —            |               | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T7CON   | 012E        | TON    | —      | TSIDL  |        |        |        |              | —            |               | TGATE          | TCKP  | S<1:0> |       | —     | TCS   |       | 0000          |

| TMR8    | 0130        |        |        |        |        |        |        |              | Timer8       | Register      |                |       |        |       |       |       |       | 0000          |

| TMR9HLD | 0132        |        |        |        |        |        | -      | Timer9 Hold  | ing Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR9    | 0134        |        |        |        |        |        |        |              | Timer9       | Register      |                |       |        |       |       |       |       | 0000          |

| PR8     | 0136        |        |        |        |        |        |        |              | Period F     | Register 8    |                |       |        |       |       |       |       | FFFF          |

| PR9     | 0138        |        |        |        |        |        |        |              | Period F     | Register 9    |                |       |        |       |       |       |       | FFFF          |

| T8CON   | 013A        | TON    | —      | TSIDL  | _      | _      | —      | —            | —            | _             | TGATE          | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T9CON   | 013C        | TON    | —      | TSIDL  | —      | —      | —      | —            | —            | —             | TGATE          | TCKP  | S<1:0> | —     | —     | TCS   | —     | 0000          |

#### TABLE 4-6: TIMER REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33FJXXXGPX06A/X08A/X10A

#### TABLE 4-17: DMA REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|---------------|

| DMA0CON   | 0380 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        |       | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA0REQ   | 0382 | FORCE  | _      | _      | _      | _      | _      | _     | _     | _        |       |       |        | RQSEL<6:0 | >     | -     | -     | 0000          |

| DMA0STA   | 0384 | I      |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0STB   | 0386 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0PAD   | 0388 |        |        |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0CNT   | 038A | _      | —      | _      | —      | _      | _      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA1CON   | 038C | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | —     | _        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA1REQ   | 038E | FORCE  | _      | _      | —      | _      | _      | _     | _     | _        |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA1STA   | 0390 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1STB   | 0392 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1PAD   | 0394 |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1CNT   | 0396 | —      | —      |        | —      | —      | _      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA2CON   | 0398 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | _     | —     |          | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA2REQ   | 039A | FORCE  | —      |        | _      | _      | —      | _     | —     |          |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA2STA   | 039C |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2STB   | 039E |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2PAD   | 03A0 |        |        |        | -      |        |        | -     | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2CNT   | 03A2 | —      | _      | —      | —      | _      | _      |       | -     |          |       | CN    | <9:0>  | _         | -     | -     |       | 0000          |

| DMA3CON   | 03A4 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | -         | —     | MODE  | <1:0> | 0000          |

| DMA3REQ   | 03A6 | FORCE  | _      | _      | —      | —      | _      | —     | —     | _        |       |       |        | RQSEL<6:0 | >     |       |       | 0000          |

| DMA3STA   | 03A8 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3STB   | 03AA |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3PAD   | 03AC |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3CNT   | 03AE | —      | —      | —      | —      | —      | —      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA4CON   | 03B0 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA4REQ   | 03B2 | FORCE  | —      | —      | —      | —      | —      | —     | —     | —        |       |       | l      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA4STA   | 03B4 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4STB   | 03B6 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4PAD   | 03B8 |        |        |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4CNT   | 03BA | —      | —      | —      | —      | —      | —      |       |       |          |       | CN    | <9:0>  |           |       |       |       | 0000          |

| DMA5CON   | 03BC | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | _        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000          |

| DMA5REQ   | 03BE | FORCE  | —      | —      | —      | —      |        | —     | —     | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000          |

| DMA5STA   | 03C0 |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA5STB   | 03C2 |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA5PAD   | 03C4 |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

© 2009-2012 Microchip Technology Inc.

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70593D-page 56

#### TABLE 4-27: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 |        | _      |       |       | _     | —     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 |       | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | _      | _     | -     | _     | _     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  |        |        | _     |       | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-28: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-29: PORTE REGISTER MAP<sup>(1)</sup>

|           | -    | -      |        |        |        |        |        |       |       |        |        |        |        |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | —      | —      | —      | —      | _      | _     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | OOFF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-30: PORTF REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF     | 02DE | _      | _      | TRISF13 | TRISF12 | —      | -      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF     | 02E0 | _      | _      | RF13    | RF12    | _      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF      | 02E2 | _      | _      | LATF13  | LATF12  | _      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF      | 06DE | _      | _      | ODCF13  | ODCF12  | _      | _      | _     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### 5.0 FLASH PROGRAM MEMORY

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and

Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

#### 5.1 Table Instructions and Flash Programming

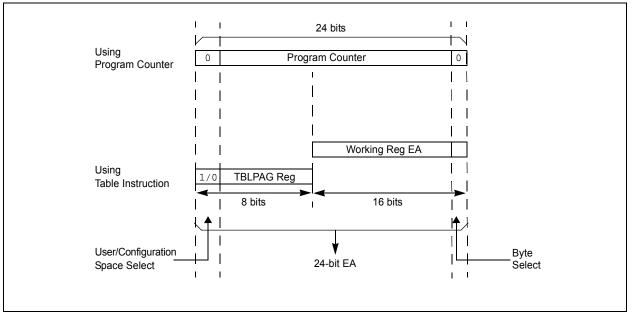

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE bit (NVMCON<6>) and the WREN bit (NVMCON<14>).

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | i                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

| REGISTER 7-20: IP | PC5: INTERRUPT PRIORITY CONTROL REGISTER 5 |

|-------------------|--------------------------------------------|

|-------------------|--------------------------------------------|

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|-----------------|--------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _               |                    | IC8IP<2:0>                              |                 | —                |                 | IC7IP<2:0>      |       |

| bit 15          |                    |                                         |                 |                  |                 |                 | bit 8 |

|                 |                    |                                         |                 |                  |                 |                 |       |

| U-0             | R/W-1              | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

| —               |                    | AD2IP<2:0>                              |                 | —                |                 | INT1IP<2:0>     |       |

| bit 7           |                    |                                         |                 |                  |                 |                 | bit   |

| Legend:         |                    |                                         |                 |                  |                 |                 |       |

| R = Readable    | bit                | W = Writable t                          | oit             | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at I | POR                | '1' = Bit is set                        |                 | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

| bit 15          | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 14-12       | -                  | Input Capture C                         |                 | rrunt Priority h | nite            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Interr  | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 11          |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 10-8        | -                  | Input Capture C                         |                 | rrupt Priority b | oits            |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 = Interru | upt is priority 1                       |                 |                  |                 |                 |       |

|                 |                    | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 7           | Unimpleme          | nted: Read as '0                        | )'              |                  |                 |                 |       |

| bit 6-4         | AD2IP<2:0>         | : ADC2 Convers                          | ion Complete    | e Interrupt Pric | rity bits       |                 |       |

|                 | 111 = Interru      | upt is priority 7 (h                    | nighest priorit | y interrupt)     |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 |                    | upt is priority 1<br>upt source is disa | abled           |                  |                 |                 |       |

| bit 3           |                    | nted: Read as '0                        |                 |                  |                 |                 |       |

| bit 2-0         | -                  | : External Interr                       |                 | hits             |                 |                 |       |

|                 |                    | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|                 | •                  |                                         |                 | ,                |                 |                 |       |

|                 | •                  |                                         |                 |                  |                 |                 |       |

|                 | •<br>001 - Intern  | int is priority 1                       |                 |                  |                 |                 |       |

|                 | 001 = merrl        | upt is priority 1                       |                 |                  |                 |                 |       |

#### **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  | 5444  | 54446            |                 | <b>B</b> 111 A  |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PAI   | 0<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-------|---------------------|

| —      | _   | -   | —   | —   | —   | CNT<  | 9:8> <sup>(2)</sup> |

| bit 15 |     |     |     |     |     |       | bit 8               |

|        |     |     |     |     |     |       |                     |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <b>(2)</b> |       |       |       |

| bit 7 |       |       |       |                 |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

| U-0           | U-0                                            | U-0                                                                                              | U-0            | R-1               | R-1              | R-1             | R-1   |  |  |  |  |

|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| —             | _                                              | —                                                                                                | —              |                   | LSTCH            | +<3:0>          |       |  |  |  |  |

| oit 15        | ÷                                              |                                                                                                  |                |                   |                  |                 | bit   |  |  |  |  |

| R-0           | R-0                                            | R-0                                                                                              | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

| PPST7         | PPST6                                          | PPST5                                                                                            | PPST4          | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |

| bit 7         |                                                |                                                                                                  |                |                   |                  | I               | bit   |  |  |  |  |

| Legend:       |                                                |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

| R = Readabl   | e bit                                          | W = Writable                                                                                     | bit            | U = Unimplem      | nented bit, read | as '0'          |       |  |  |  |  |

| -n = Value at | POR                                            | '1' = Bit is set                                                                                 |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 15-12     | Unimplemen                                     | ted: Read as '                                                                                   | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 11-8      | LSTCH<3:0>                                     | : Last DMA Ch                                                                                    | annel Active t | oits              |                  |                 |       |  |  |  |  |

|               | 1111 = No DM                                   | MA transfer ha                                                                                   | s occurred sin | ce system Res     | et               |                 |       |  |  |  |  |

|               | 1110-1000 =                                    |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|               |                                                | lata transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |

|               |                                                | lata transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |

|               |                                                | 0101 = Last data transfer was by DMA Channel 5<br>0100 = Last data transfer was by DMA Channel 4 |                |                   |                  |                 |       |  |  |  |  |

|               | 0010 – Last data transfer was by DMA Channel 3 |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |

|               |                                                | lata transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |

|               |                                                | lata transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |

| bit 7         |                                                | lata transfer wa<br>inel 7 Ping-Por                                                              | -              |                   |                  |                 |       |  |  |  |  |

|               | 1 = DMA7STE                                    | B register select<br>register select                                                             | ted            | S Flag bit        |                  |                 |       |  |  |  |  |

| bit 6         |                                                | inel 6 Ping-Por                                                                                  |                | s Flag bit        |                  |                 |       |  |  |  |  |

|               |                                                | B register selec                                                                                 | -              |                   |                  |                 |       |  |  |  |  |

|               |                                                | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |

| bit 5         | PPST5: Chan                                    | nel 5 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |

|               | 1 = DMA5STE                                    | B register selec                                                                                 | ted            | -                 |                  |                 |       |  |  |  |  |

|               | 0 = DMA5STA                                    | A register selec                                                                                 | ted            |                   |                  |                 |       |  |  |  |  |

| bit 4         | PPST4: Chan                                    | inel 4 Ping-Por                                                                                  | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |

|               |                                                | B register select<br>A register select                                                           |                |                   |                  |                 |       |  |  |  |  |

| bit 3         | PPST3: Chan                                    | inel 3 Ping-Por                                                                                  | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |

|               |                                                | B register select<br>A register select                                                           |                |                   |                  |                 |       |  |  |  |  |

| bit 2         | PPST2: Chan                                    | inel 2 Ping-Por                                                                                  | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |

|               | 1 = DMA2STE                                    | B register select                                                                                | ted            |                   |                  |                 |       |  |  |  |  |

| bit 1         |                                                | inel 1 Ping-Por                                                                                  |                | s Flao bit        |                  |                 |       |  |  |  |  |

|               | 1 = DMA1STE                                    | B register select<br>register select                                                             | cted           |                   |                  |                 |       |  |  |  |  |

| bit 0         |                                                | inel 0 Ping-Por                                                                                  |                | s Flag bit        |                  |                 |       |  |  |  |  |

|               |                                                | B register selec                                                                                 | -              |                   |                  |                 |       |  |  |  |  |

#### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

#### bit 0 OSWEN: Oscillator Switch Enable bit

bit 1

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This is register is reset only on a Power-on Reset (POR).

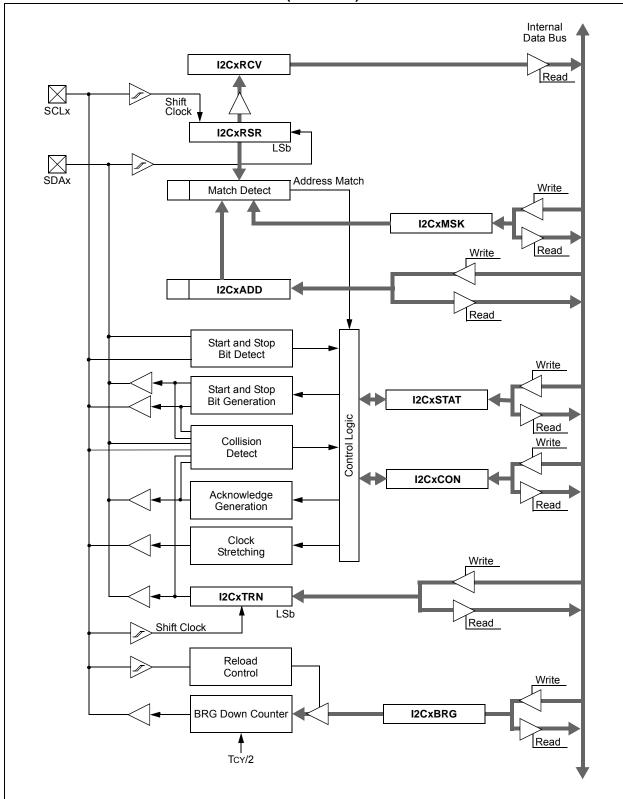

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (X = 1 OR 2)

#### **REGISTER 19-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

|               |                    |                                      | 11.0                   |                |                  |                    | 11.0           |

|---------------|--------------------|--------------------------------------|------------------------|----------------|------------------|--------------------|----------------|

| U-0           | U-0                | U-0                                  | U-0                    | U-0            | U-0              | U-0                | U-0            |

|               | —                  | —                                    | —                      |                | —                | —                  |                |

| bit 15        |                    |                                      |                        |                |                  |                    | bit 8          |

| 5444          | 5444.0             |                                      | <b>DM/</b> 0           | <b>D</b> 444 A | 5444.0           | 5444.0             | <b>D</b> 4 4 4 |

| R/W-0         | R/W-0              | R/W-0                                | R/W-0                  | R/W-0          | R/W-0            | R/W-0              | R/W-0          |

|               | N<1:0>             |                                      |                        | BRI            | P<5:0>           |                    |                |

| bit 7         |                    |                                      |                        |                |                  |                    | bit 0          |

|               |                    |                                      |                        |                |                  |                    |                |

| Legend:       |                    |                                      |                        |                |                  |                    |                |

| R = Readabl   | e bit              | W = Writable                         | bit                    | U = Unimpler   | mented bit, read | l as '0'           |                |

| -n = Value at | t POR              | '1' = Bit is set                     | t '0' = Bit is cleared |                |                  | x = Bit is unknown |                |

|               |                    |                                      |                        |                |                  |                    |                |

| bit 15-8      | Unimplemer         | nted: Read as '                      | 0'                     |                |                  |                    |                |

| bit 7-6       | SJW<1:0>: S        | Synchronization                      | Jump Width I           | bits           |                  |                    |                |

|               | 11 = Length        | is 4 x Tq                            |                        |                |                  |                    |                |

|               | 10 = Length        |                                      |                        |                |                  |                    |                |

|               | 01 = Length        |                                      |                        |                |                  |                    |                |

|               | 00 = Length        |                                      |                        |                |                  |                    |                |

| bit 5-0       |                    | Baud Rate Pres                       |                        |                |                  |                    |                |

|               |                    | [q = 2 x 64 x 1/                     | FCAN                   |                |                  |                    |                |

|               | •                  |                                      |                        |                |                  |                    |                |

|               | •                  |                                      |                        |                |                  |                    |                |

|               | •                  |                                      |                        |                |                  |                    |                |

|               |                    | $Q = 2 \times 3 \times 1/F$          |                        |                |                  |                    |                |

|               |                    | 「q = 2 x 2 x 1/F<br>「q = 2 x 1 x 1/F |                        |                |                  |                    |                |

|               | 00 0000 <b>- 1</b> |                                      |                        |                |                  |                    |                |

| U-0                            | R/W-x                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                 | U-0                            | U-0               | R/W-x            | R/W-x           | R/W-x |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------|-------------------|------------------|-----------------|-------|

|                                | WAKFIL                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     | _                              |                   |                  | SEG2PH<2:0>     |       |

| bit 15                         |                                                                                                                                                                                                                                                                                                                                                                                                 | ·                                                                                   |                                | · · · ·           |                  |                 | bit 8 |

| R/W-x                          | R/W-x                                                                                                                                                                                                                                                                                                                                                                                           | R/W-x                                                                               | R/W-x                          | R/W-x             | R/W-x            | R/W-x           | R/W-x |

| SEG2PHTS                       | SAM                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     | SEG1PH<2:0>                    | >                 |                  | PRSEG<2:0>      |       |

| bit 7                          |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |                                |                   |                  |                 | bit ( |

| Legend:                        |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                     |                                |                   |                  |                 |       |

| R = Readable                   | bit                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable                                                                        | bit                            | U = Unimplen      | nented bit, read | as '0'          |       |

| -n = Value at P                | OR                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                                                    | :                              | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 13-11<br>bit 10-8<br>bit 7 | <ul> <li>WAKFIL: Select CAN bus Line Filter for Wake-up bit</li> <li>1 = Use CAN bus line filter for wake-up</li> <li>0 = CAN bus line filter is not used for wake-up</li> <li>Unimplemented: Read as '0'</li> <li>SEG2PH&lt;2:0&gt;: Phase Buffer Segment 2 bits</li> <li>111 = Length is 8 x TQ</li> <li>000 = Length is 1 x TQ</li> <li>SEG2PHTS: Phase Segment 2 Time Select bit</li> </ul> |                                                                                     |                                |                   |                  |                 |       |

| bit 6                          | SAM: Samp<br>1 = Bus line i                                                                                                                                                                                                                                                                                                                                                                     | ogrammable<br>n of SEG1PH b<br>le of the CAN b<br>is sampled thre<br>is sampled onc | ous Line bit<br>e times at the | sample point      | Time (IPT), wh   | ichever is grea | ter   |

| bit 5-3                        |                                                                                                                                                                                                                                                                                                                                                                                                 | <b>0&gt;:</b> Phase Buff<br>n is 8 x TQ                                             |                                | •                 |                  |                 |       |

| bit 2-0                        | PRSEG<2:0:<br>111 = Length<br>000 = Length                                                                                                                                                                                                                                                                                                                                                      |                                                                                     | Time Segmer                    | nt bits           |                  |                 |       |

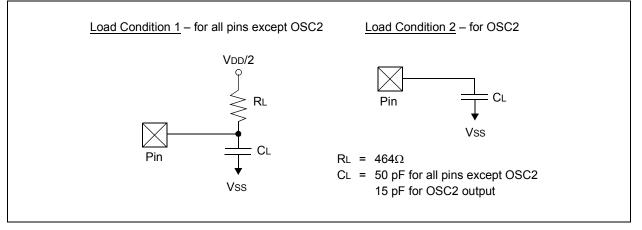

### 25.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJXXXGPX06A/X08A/X10A electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJXXXGPX06A/X08A/X10A family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                |                      |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0V^{(4)}$ | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} < 3.0V^{(4)}$ | 0.3V to 3.6V         |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                   |                      |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                 | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                 |                      |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                 |                      |

| Maximum current sunk by all ports                                             |                      |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 25-2).

- 3: Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

| DC CHA       | DC CHARACTERISTICS |                                                                       |                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |       |                                                                                                                                    |  |

|--------------|--------------------|-----------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol             | Characteristic                                                        | Min                | Typ <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max                 | Units | Conditions                                                                                                                         |  |

| DI60a        | licl               | Input Low Injection Current                                           | 0                  | _                                                                                                                                                                                                                                                                                       | <sub>-5</sub> (5,8) | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, and RB11                                                     |  |

| DI60b        | ІІСН               | Input High Injection Current                                          | 0                  | _                                                                                                                                                                                                                                                                                       | +5(6,7,8)           | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>             |  |