Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp708a-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 4-5: | INTERRUPT CONTROLLER REGISTER MAP |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Name A<br>INTCON1 0 | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13     |         |         |        |            |        |          |         |             |         |           |         |            |               |               |

|---------------------|-------------|--------|--------|------------|---------|---------|--------|------------|--------|----------|---------|-------------|---------|-----------|---------|------------|---------------|---------------|

|                     |             |        |        | 61113      | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8  | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2   | Bit 1      | Bit 0         | All<br>Resets |

| INTCON2 0           | 0080        | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE  | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR   | STKERR  | OSCFAIL    | _             | 0000          |

|                     | 0082        | ALTIVT | DISI   | —          | _       | _       | _      | _          | _      | _        | _       | _           | INT4EP  | INT3EP    | INT2EP  | INT1EP     | INT0EP        | 0000          |

| IFS0 C              | 0084        | —      | DMA1IF | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF   | T2IF     | OC2IF   | IC2IF       | DMA0IF  | T1IF      | OC1IF   | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1 C              | 0086        | U2TXIF | U2RXIF | INT2IF     | T5IF    | T4IF    | OC4IF  | OC3IF      | DMA2IF | IC8IF    | IC7IF   | AD2IF       | INT1IF  | CNIF      | —       | MI2C1IF    | SI2C1IF       | 0000          |

| IFS2 C              | 8800        | T6IF   | DMA4IF | —          | OC8IF   | OC7IF   | OC6IF  | OC5IF      | IC6IF  | IC5IF    | IC4IF   | IC3IF       | DMA3IF  | C1IF      | C1RXIF  | SPI2IF     | SPI2EIF       | 0000          |

| IFS3 0              | 008A        | _      | _      | DMA5IF     | DCIIF   | DCIEIF  |        | _          | C2IF   | C2RXIF   | INT4IF  | INT3IF      | T9IF    | T8IF      | MI2C2IF | SI2C2IF    | T7IF          | 0000          |

| IFS4 0              | 008C        | _      | _      | _          | _       | -       |        | _          | _      | C2TXIF   | C1TXIF  | DMA7IF      | DMA6IF  | _         | U2EIF   | U1EIF      | _             | 0000          |

| IEC0 C              | 0094        | _      | DMA1IE | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE   | T2IE     | OC2IE   | IC2IE       | DMA0IE  | T1IE      | OC1IE   | IC1IE      | INT0IE        | 0000          |

| IEC1 C              | 0096        | U2TXIE | U2RXIE | INT2IE     | T5IE    | T4IE    | OC4IE  | OC3IE      | DMA2IE | IC8IE    | IC7IE   | AD2IE       | INT1IE  | CNIE      | _       | MI2C1IE    | SI2C1IE       | 0000          |

| IEC2 C              | 0098        | T6IE   | DMA4IE | _          | OC8IE   | OC7IE   | OC6IE  | OC5IE      | IC6IE  | IC5IE    | IC4IE   | IC3IE       | DMA3IE  | C1IE      | C1RXIE  | SPI2IE     | SPI2EIE       | 0000          |

| IEC3 0              | 009A        | _      | _      | DMA5IE     | DCIIE   | DCIEIE  |        | _          | C2IE   | C2RXIE   | INT4IE  | INT3IE      | T9IE    | T8IE      | MI2C2IE | SI2C2IE    | T7IE          | 0000          |

| IEC4 0              | 009C        | —      | —      | _          | —       | _       | _      | -          |        | C2TXIE   | C1TXIE  | DMA7IE      | DMA6IE  | —         | U2EIE   | U1EIE      |               | 0000          |

| IPC0 0              | 00A4        | —      |        | T1IP<2:0>  | •       | _       | (      | OC1IP<2:0  | )>     | —        |         | IC1IP<2:0>  |         | —         | 11      | NT0IP<2:0> |               | 4444          |

| IPC1 0              | 00A6        | —      |        | T2IP<2:0>  | •       | _       | (      | OC2IP<2:0  | )>     | —        |         | IC2IP<2:0>  |         | —         | DI      | MA0IP<2:0  | >             | 4444          |

| IPC2 0              | 00A8        | —      | L      | J1RXIP<2:( | )>      | _       | S      | SPI1IP<2:0 | )>     | —        | :       | SPI1EIP<2:0 | >       | —         |         | T3IP<2:0>  |               | 4444          |

| IPC3 0              | 00AA        | —      | —      | _          | —       | _       | D      | MA1IP<2:   | 0>     | —        |         | AD1IP<2:0>  | •       | —         | U       | 1TXIP<2:0> | >             | 0444          |

| IPC4 0              | 00AC        | —      |        | CNIP<2:0>  | >       | —       | -      |            |        | —        | I       | MI2C1IP<2:0 | )>      | _         | SI      | 2C1IP<2:0  | >             | 4044          |

| IPC5 0              | 00AE        | —      |        | IC8IP<2:0> | >       | —       |        | IC7IP<2:0  | >      | —        |         | AD2IP<2:0>  | •       | _         | 11      | VT1IP<2:0> |               | 4444          |

| IPC6 0              | 00B0        | —      |        | T4IP<2:0>  | •       | —       | (      | C4IP<2:0   | )>     | —        |         | OC3IP<2:0>  | >       | _         | DI      | MA2IP<2:0  | >             | 4444          |

| IPC7 0              | 00B2        | _      | ι      | J2TXIP<2:0 | )>      | -       | U      | I2RXIP<2:  | 0>     | _        |         | INT2IP<2:0  | >       | _         |         | T5IP<2:0>  |               | 4444          |

| IPC8 0              | 00B4        | —      |        | C1IP<2:0>  | >       | —       | С      | 1RXIP<2:   | 0>     | —        |         | SPI2IP<2:0  | >       | _         | SF      | PI2EIP<2:0 | >             | 4444          |

| IPC9 0              | 00B6        | —      |        | IC5IP<2:0> | >       | —       |        | IC4IP<2:0  | >      | —        |         | IC3IP<2:0>  |         | _         | DI      | MA3IP<2:0  | >             | 4444          |

| IPC10 0             | 00B8        | —      | (      | OC7IP<2:0  | >       | —       | (      | C6IP<2:0   | )>     | —        |         | OC5IP<2:0>  | >       | _         | I       | C6IP<2:0>  |               | 4444          |

| IPC11 0             | 00BA        | —      |        | T6IP<2:0>  | •       | —       | D      | MA4IP<2:   | 0>     | —        | _       |             |         | _         | C       | 0C8IP<2:0> |               | 4404          |

| IPC12 0             | 00BC        | _      |        | T8IP<2:0>  | •       | -       | Μ      | II2C2IP<2: | 0>     | _        |         | SI2C2IP<2:0 | >       | _         |         | T7IP<2:0>  |               | 4444          |

| IPC13 0             | 00BE        | _      | C      | 2RXIP<2:0  | )>      | _       | I      | NT4IP<2:0  | )>     | -        |         | INT3IP<2:0  | >       | _         |         | T9IP<2:0>  |               | 4444          |

| IPC14 0             | 00C0        | _      | 0      | DCIEIP<2:0 | )>      | _       | _      | —          | —      | —        | —       | —           | —       | —         | (       | C2IP<2:0>  |               | 4004          |

| IPC15 0             | 00C2        | _      | —      | _          | —       | _       | _      | —          | _      | —        |         | DMA5IP<2:0  | >       | _         | [       | OCIIP<2:0> |               | 0044          |

| IPC16 0             | 00C4        | _      | —      | _          | —       | _       | l      | J2EIP<2:0  | >      | —        |         | U1EIP<2:0>  | •       | _         |         | —          | —             | 0440          |

| IPC17 0             | 00C6        | _      |        | C2TXIP<2:0 | )>      | _       | C      | 1TXIP<2:   | 0>     | _        |         | DMA7IP<2:0  | >       | _         | DI      | MA6IP<2:0  | >             | 4444          |

| INTTREG 0           | 00E0        | _      | —      | —          | —       |         | ILR<   | 3:0>       |        | _        |         |             | VE      | CNUM<6:0> |         |            |               | 0000          |

© 2009-2012 Microchip Technology Inc.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

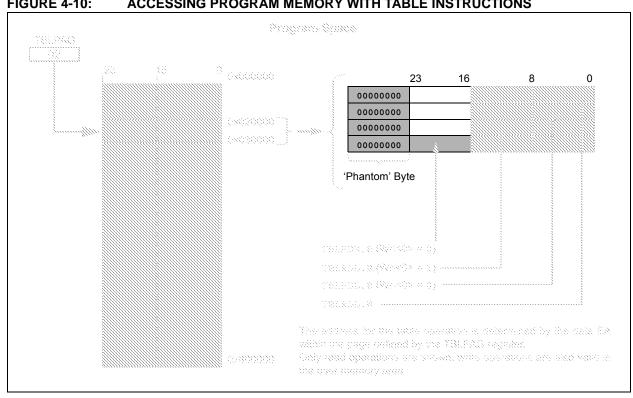

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### **REGISTER 5-2:** NVMKEY: NON-VOLATILE MEMORY KEY REGISTER U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_ \_\_\_\_ \_ — \_\_\_\_ bit 15 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 NVMKEY<7:0> bit 7 Legend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

bit 8

bit 0

#### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

|                 |                                                                                                                           | T2IP<2:0>            |                  | —                |                 | OC2IP<2:0>           |       |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|-----------------|----------------------|-------|--|--|--|--|--|

| bit 15          |                                                                                                                           |                      |                  |                  |                 |                      | bit   |  |  |  |  |  |

|                 |                                                                                                                           | DAMO                 |                  | 11.0             |                 | DAALO                |       |  |  |  |  |  |

| U-0             | R/W-1                                                                                                                     | R/W-0<br>IC2IP<2:0>  | R/W-0            | U-0              | R/W-1           | R/W-0<br>DMA0IP<2:0> | R/W-0 |  |  |  |  |  |

| bit 7           |                                                                                                                           | 10211 42.05          |                  |                  |                 | Division 42.05       | bit   |  |  |  |  |  |

|                 |                                                                                                                           |                      |                  |                  |                 |                      |       |  |  |  |  |  |

| Legend:         |                                                                                                                           |                      |                  |                  |                 |                      |       |  |  |  |  |  |

| R = Readable    |                                                                                                                           | W = Writable k       | Dit              | •                | mented bit, rea |                      |       |  |  |  |  |  |

| -n = Value at F | POR                                                                                                                       | '1' = Bit is set     |                  | '0' = Bit is cle | eared           | x = Bit is unkn      | iown  |  |  |  |  |  |

| bit 15          | Unimplemer                                                                                                                | nted: Read as '0     | )'               |                  |                 |                      |       |  |  |  |  |  |

| bit 14-12       | T2IP<2:0>: Timer2 Interrupt Priority bits                                                                                 |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | 111 = Interru                                                                                                             | ıpt is priority 7 (h | nighest priority | y interrupt)     |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | 001 = Interru                                                                                                             | pt is priority 1     |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | 000 = Interrupt source is disabled                                                                                        |                      |                  |                  |                 |                      |       |  |  |  |  |  |

| bit 11          | Unimplemer                                                                                                                | nted: Read as '0     | )'               |                  |                 |                      |       |  |  |  |  |  |

| bit 10-8        | <b>OC2IP&lt;2:0&gt;:</b> Output Compare Channel 2 Interrupt Priority bits                                                 |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                                 |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                      |                  |                  |                 |                      |       |  |  |  |  |  |

| bit 7           |                                                                                                                           | nted: Read as '0     |                  |                  |                 |                      |       |  |  |  |  |  |

| bit 6-4         | -                                                                                                                         |                      |                  | rrupt Priority b | its             |                      |       |  |  |  |  |  |

|                 | IC2IP<2:0>: Input Capture Channel 2 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                  |                      |                  |                  |                 |                      |       |  |  |  |  |  |

| bit 3           |                                                                                                                           | nted: Read as '0     |                  |                  |                 |                      |       |  |  |  |  |  |

| bit 2-0         | -                                                                                                                         | >: DMA Channe        |                  | sfer Complete    | Interrupt Prio  | rity bits            |       |  |  |  |  |  |

| 511 2 0         |                                                                                                                           | ipt is priority 7 (h |                  | -                |                 | ing bito             |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      | 5                | ,,               |                 |                      |       |  |  |  |  |  |

|                 | •                                                                                                                         |                      |                  |                  |                 |                      |       |  |  |  |  |  |

|                 | •<br>001 = Intern                                                                                                         | pt is priority 1     |                  |                  |                 |                      |       |  |  |  |  |  |

|                 |                                                                                                                           | ipt source is disa   | abled            |                  |                 |                      |       |  |  |  |  |  |

#### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-level 15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0        | R-0                  | R-0                                                                                                        | R-0              | U-0                    | R/W-y           | R/W-y            | R/W-y          |  |  |  |  |  |

|------------|----------------------|------------------------------------------------------------------------------------------------------------|------------------|------------------------|-----------------|------------------|----------------|--|--|--|--|--|

| _          |                      | COSC<2:0>                                                                                                  |                  |                        |                 | NOSC<2:0>(2)     |                |  |  |  |  |  |

| bit 15     |                      |                                                                                                            |                  |                        |                 |                  | bit 8          |  |  |  |  |  |

|            |                      |                                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

| R/W-0      | U-0                  | R-0                                                                                                        | U-0              | R/C-0                  | U-0             | R/W-0            | R/W-0          |  |  |  |  |  |

| CLKLOC     | СК —                 | LOCK                                                                                                       | _                | CF                     |                 | LPOSCEN          | OSWEN          |  |  |  |  |  |

| bit 7      |                      |                                                                                                            |                  |                        |                 |                  | bit 0          |  |  |  |  |  |

| Legend:    |                      | y = Value set                                                                                              | from Configur    | ation bits on P        | POR             | C = Clea         | r only bit     |  |  |  |  |  |

| R = Reada  | able bit             | W = Writable                                                                                               | bit              | U = Unimplei           | mented bit, rea | d as '0'         |                |  |  |  |  |  |

| -n = Value | at POR               | '1' = Bit is set                                                                                           |                  | '0' = Bit is cle       | eared           | x = Bit is unkn  | own            |  |  |  |  |  |

| bit 15     | Unimplemer           | nted: Read as '                                                                                            | )'               |                        |                 |                  |                |  |  |  |  |  |

| bit 14-12  | COSC<2:0>:           | Current Oscilla                                                                                            | tor Selection    | bits (read-only        | ()              |                  |                |  |  |  |  |  |

|            |                      | C oscillator (FF                                                                                           |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      |                                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 110 = Fast RC oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC oscillator (LPRC)                   |                  |                        |                 |                  |                |  |  |  |  |  |

|            | 100 <b>= Secon</b>   | 100 = Secondary oscillator (Sosc)                                                                          |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 011 = Primary oscillator (XT, HS, EC) with PLL                                                             |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 010 = Primary oscillator (XT, HS, EC)                                                                      |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCDIVN + PLL)<br>000 = Fast RC oscillator (FRC)  |                  |                        |                 |                  |                |  |  |  |  |  |

| .:         |                      | •                                                                                                          | •                |                        |                 |                  |                |  |  |  |  |  |

| oit 11     | -                    | Unimplemented: Read as '0'                                                                                 |                  |                        |                 |                  |                |  |  |  |  |  |

| oit 10-8   |                      | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup><br>111 = Fast RC oscillator (FRC) with Divide-by-N |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 111 = Fast RC oscillator (FRC) with Divide-by-N<br>110 = Fast RC oscillator (FRC) with Divide-by-16        |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 110 = Fast RC oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC oscillator (LPRC)                   |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 101 = Low-Power RC oscillator (LPRC)<br>100 = Secondary oscillator (Sosc)                                  |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | ry oscillator (XT,                                                                                         |                  | I PLL                  |                 |                  |                |  |  |  |  |  |

|            |                      | y oscillator (XT,                                                                                          |                  |                        |                 |                  |                |  |  |  |  |  |

|            | 001 <b>= Fast R</b>  | C Oscillator (FF                                                                                           | RC) with Divid   | e-by-N and PL          | L (FRCDIVN +    | ⊦ PLL)           |                |  |  |  |  |  |

|            |                      | C oscillator (FF                                                                                           | ,                |                        |                 |                  |                |  |  |  |  |  |

| bit 7      |                      | Clock Lock Enal                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked                                          |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | If (FCKSM0 = 0), then clock and PLL configurations may be modified                                         |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | Id PLL selection                                                                                           |                  | ked, configurat        | ions may be m   | odified          |                |  |  |  |  |  |

| bit 6      | -                    | nted: Read as '                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

| bit 5      |                      | ₋ock Status bit (<br>s that PLL is in I                                                                    | 3,               | lart un timor in       | eatiefied       |                  |                |  |  |  |  |  |

|            |                      | s that PLL is in i                                                                                         |                  |                        |                 | l is disabled    |                |  |  |  |  |  |

| bit 4      |                      | nted: Read as '                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

| bit 3      |                      | ail Detect bit (rea                                                                                        |                  | plication)             |                 |                  |                |  |  |  |  |  |

|            |                      | as detected clo                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

|            |                      | as not detected                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

| bit 2      | Unimplemer           | nted: Read as '                                                                                            | )'               |                        |                 |                  |                |  |  |  |  |  |

| Note 1:    | Writes to this regis | ster require an u                                                                                          | Inlock sequer    | ice. Refer to <b>S</b> | ection 7. "Oso  | cillator" (DS701 | 86) in the     |  |  |  |  |  |

|            | "dsPIC33F/PIC24      |                                                                                                            |                  |                        |                 |                  | , -            |  |  |  |  |  |

| 2:         | Direct clock switch  | nes between any                                                                                            | / primary osci   | llator mode wit        | th PLL and FRO  | CPLL mode are r  | not permitted. |  |  |  |  |  |

|            | This applies to clo  | ck switches in e                                                                                           | either direction | n. In these inst       | ances, the app  |                  |                |  |  |  |  |  |

|            | mode as a transiti   | on clock source                                                                                            | between the      | two PLL mode           | es.             |                  |                |  |  |  |  |  |

| _          |                      |                                                                                                            |                  |                        |                 |                  |                |  |  |  |  |  |

3: This is register is reset only on a Power-on Reset (POR).

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | U-0              | U-0            | R/W-0                |  |

|---------------|---------------------------------|---------------------------------------|---------|-------------------|------------------|----------------|----------------------|--|

| T5MD          | T4MD                            | T3MD                                  | T2MD    | T1MD              |                  | _              | DCIMD                |  |

| bit 15        |                                 |                                       |         |                   |                  |                | bit 8                |  |

|               |                                 |                                       |         |                   |                  |                |                      |  |

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0   | R/W-0             | R/W-0            | R/W-0          | R/W-0                |  |

| I2C1MD        | U2MD                            | U1MD                                  | SPI2MD  | SPI1MD            | C2MD             | C1MD           | AD1MD <sup>(1)</sup> |  |

| bit 7         |                                 |                                       |         |                   |                  |                | bit                  |  |

| Legend:       |                                 |                                       |         |                   |                  |                |                      |  |

| R = Readabl   | e bit                           | W = Writable                          | bit     | U = Unimplen      | nented bit, read | d as '0'       |                      |  |

| -n = Value at | POR                             | '1' = Bit is set                      |         | '0' = Bit is clea |                  | x = Bit is unk | nown                 |  |

|               |                                 |                                       |         |                   |                  |                |                      |  |

| bit 15        | T5MD: Timer                     | 5 Module Disat                        | ole bit |                   |                  |                |                      |  |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |  |

| bit 14        | T4MD: Timer                     | 4 Module Disat                        | ole bit |                   |                  |                |                      |  |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |  |

| bit 13        |                                 | 3 Module Disat                        |         |                   |                  |                |                      |  |

|               | 1 = Timer3 m                    | nodule is disable                     | ed      |                   |                  |                |                      |  |

|               | 0 = Timer3 m                    | nodule is enable                      | d       |                   |                  |                |                      |  |

| bit 12        | T2MD: Timer2 Module Disable bit |                                       |         |                   |                  |                |                      |  |

|               | -                               | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |  |

| bit 11        | T1MD: Timer                     | 1 Module Disat                        | ole bit |                   |                  |                |                      |  |

|               |                                 | nodule is disable<br>nodule is enable |         |                   |                  |                |                      |  |

| bit 10-9      | Unimplemer                      | ted: Read as '                        | כ'      |                   |                  |                |                      |  |

| bit 8         | DCIMD: DCI                      | Module Disable                        | e bit   |                   |                  |                |                      |  |

|               |                                 | ule is disabled<br>ule is enabled     |         |                   |                  |                |                      |  |

| bit 7         | <b>I2C1MD:</b> I <sup>2</sup> C | 1 Module Disab                        | le bit  |                   |                  |                |                      |  |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |  |

| bit 6         |                                 | T2 Module Disa                        | ble bit |                   |                  |                |                      |  |

|               | -                               | nodule is disabl<br>nodule is enable  |         |                   |                  |                |                      |  |

| bit 5         |                                 | T1 Module Disa                        |         |                   |                  |                |                      |  |

|               |                                 | nodule is disabl                      |         |                   |                  |                |                      |  |

|               | 0 = UART1 n                     | nodule is enable                      | ed      |                   |                  |                |                      |  |

| bit 4         | SPI2MD: SP                      | I2 Module Disal                       | ole bit |                   |                  |                |                      |  |

|               |                                 | dule is disabled                      |         |                   |                  |                |                      |  |

|               |                                 | dule is enabled                       |         |                   |                  |                |                      |  |

| bit 3         |                                 | 11 Module Disal                       | ole bit |                   |                  |                |                      |  |

|               |                                 | dule is disabled<br>dule is enabled   |         |                   |                  |                |                      |  |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

NOTES:

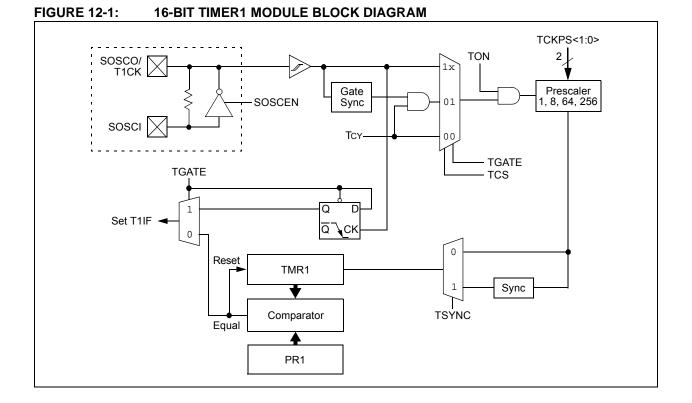

#### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

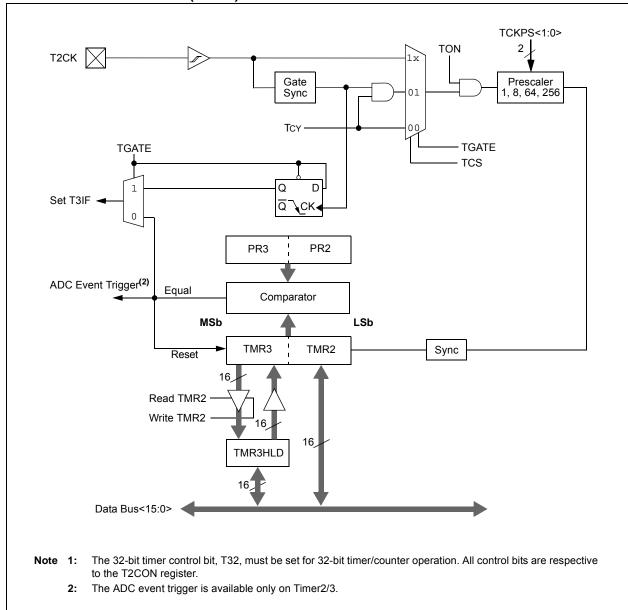

#### FIGURE 13-1: TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup>

| TON <sup>(1)</sup> | U-0                                                                                                              | R/W-0                                                                                                                                 | U-0                                         | U-0               | U-0             | U-0                  | U-0 |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------|-----------------|----------------------|-----|--|--|--|--|--|--|

| TON                | —                                                                                                                | TSIDL <sup>(2)</sup>                                                                                                                  | —                                           |                   | _               | —                    | _   |  |  |  |  |  |  |

| bit 15             |                                                                                                                  |                                                                                                                                       |                                             |                   |                 | 1                    | bit |  |  |  |  |  |  |

|                    |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| U-0                | R/W-0                                                                                                            | R/W-0                                                                                                                                 | R/W-0                                       | U-0               | U-0             | R/W-0                | U-0 |  |  |  |  |  |  |

| _                  | TGATE <sup>(1)</sup>                                                                                             | TCKPS                                                                                                                                 | <1:0> <sup>(1)</sup>                        | —                 | —               | TCS <sup>(1,3)</sup> |     |  |  |  |  |  |  |

| bit 7              |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      | bit |  |  |  |  |  |  |

| Legend:            |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| R = Readable       | e bit                                                                                                            | W = Writable I                                                                                                                        | oit                                         | U = Unimplen      | nented bit, rea | id as '0'            |     |  |  |  |  |  |  |

| -n = Value at      | POR                                                                                                              | '1' = Bit is set                                                                                                                      |                                             | '0' = Bit is clea | ared            | x = Bit is unkno     | own |  |  |  |  |  |  |

|                    |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 15             | TON: Timery                                                                                                      | On bit <sup>(1)</sup>                                                                                                                 |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    |                                                                                                                  | 1 = Starts 16-bit Timery<br>0 = Stops 16-bit Timery                                                                                   |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | -                                                                                                                | -                                                                                                                                     |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 14             | -                                                                                                                | ted: Read as '0                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 13             |                                                                                                                  | <b>TSIDL:</b> Stop in Idle Mode bit <sup>(2)</sup>                                                                                    |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    |                                                                                                                  | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 12-7           |                                                                                                                  | -                                                                                                                                     |                                             | ue                |                 |                      |     |  |  |  |  |  |  |

| bit 6              | Unimplemented: Read as '0'                                                                                       |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup><br>When TCS = 1:                          |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | This bit is ignored.                                                                                             |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | When TCS = $0$ :                                                                                                 |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | 1 = Gated time accumulation enabled                                                                              |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    |                                                                                                                  | e accumulation                                                                                                                        |                                             |                   |                 |                      |     |  |  |  |  |  |  |

|                    | TCKPS<1:0>: Timer3 Input Clock Prescale Select bits <sup>(1)</sup>                                               |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 5-4            | 11 = 1:256                                                                                                       |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 5-4            |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 5-4            | 10 <b>= 1:64</b>                                                                                                 |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 5-4            |                                                                                                                  |                                                                                                                                       |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 5-4<br>bit 3-2 | 10 = 1:64<br>01 = 1:8<br>00 = 1:1                                                                                | ted: Read as '0                                                                                                                       | )'                                          |                   |                 |                      |     |  |  |  |  |  |  |

|                    | 10 = 1:64<br>01 = 1:8<br>00 = 1:1<br>Unimplemen                                                                  | <b>ted:</b> Read as '0<br>Clock Source S                                                                                              |                                             |                   |                 |                      |     |  |  |  |  |  |  |

| bit 3-2            | 10 = 1:64<br>01 = 1:8<br>00 = 1:1<br>Unimplemen<br>TCS: Timery                                                   | Clock Source S<br>clock from pin T                                                                                                    | elect bit <sup>(1,3)</sup>                  |                   |                 |                      |     |  |  |  |  |  |  |

| bit 3-2            | 10 = 1:64<br>01 = 1:8<br>00 = 1:1<br><b>Unimplemen</b><br><b>TCS:</b> Timery<br>1 = External o<br>0 = Internal o | Clock Source S<br>clock from pin T                                                                                                    | elect bit <sup>(1,3)</sup><br>yCK (on the r |                   |                 |                      |     |  |  |  |  |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $l^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the "*dsPIC33F/PIC24H Family Reference Manual*".

| U-0                                          | U-0                        | R-0                | R-0          | R-0                                | R-0  | R-0                | R-0   |  |  |  |  |

|----------------------------------------------|----------------------------|--------------------|--------------|------------------------------------|------|--------------------|-------|--|--|--|--|

| —                                            |                            |                    |              | FBP<5                              | :0>  |                    |       |  |  |  |  |

| pit 15                                       |                            |                    |              |                                    |      |                    | bit 8 |  |  |  |  |

|                                              |                            |                    |              |                                    |      |                    |       |  |  |  |  |

| U-0                                          | U-0                        | R-0                | R-0          | R-0                                | R-0  | R-0                | R-0   |  |  |  |  |

| _                                            | —                          |                    |              | FNRB<                              | 5:0> |                    |       |  |  |  |  |

| oit 7                                        |                            |                    |              |                                    |      |                    | bit C |  |  |  |  |

|                                              |                            |                    |              |                                    |      |                    |       |  |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit |                            |                    | it           | U = Unimplemented bit, read as '0' |      |                    |       |  |  |  |  |

| -n = Value at POR                            |                            | '1' = Bit is set   |              | '0' = Bit is cleare                | d    | x = Bit is unknown |       |  |  |  |  |

|                                              |                            |                    |              |                                    |      |                    |       |  |  |  |  |

| oit 15-14                                    | Unimpleme                  | ented: Read as '0' |              |                                    |      |                    |       |  |  |  |  |

| oit 13-8                                     | FBP<5:0>:                  | FIFO Write Buffer  | Pointer bits |                                    |      |                    |       |  |  |  |  |

|                                              | 011111 <b>= F</b>          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | 011110 <b>= F</b>          | RB30 buffer        |              |                                    |      |                    |       |  |  |  |  |

|                                              | •                          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | •                          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | 000001 = T<br>000000 = T   |                    |              |                                    |      |                    |       |  |  |  |  |

| oit 7-6                                      |                            | ented: Read as '0' |              |                                    |      |                    |       |  |  |  |  |

| oit 5-0                                      | -                          | : FIFO Next Read   |              | tor bite                           |      |                    |       |  |  |  |  |

| л 5-0                                        | 011111 = F                 |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | 011111 <b>–</b> F          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | •                          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | •                          |                    |              |                                    |      |                    |       |  |  |  |  |

|                                              | •<br>000001 = T            | DD1 huffor         |              |                                    |      |                    |       |  |  |  |  |

|                                              | $\cdots \cdots \cdots = 1$ |                    |              |                                    |      |                    |       |  |  |  |  |

#### REGISTER 19-5: CiFIFO: ECAN™ FIFO STATUS REGISTER

| U-0          | U-0                                                                                                                      | U-0                                                 | U-0             | R-0              | R-0             | R-0            | R-0   |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|------------------|-----------------|----------------|-------|--|--|--|

| _            | —                                                                                                                        | _                                                   | —               |                  | SLO             | <3:0>          |       |  |  |  |

| bit 15       |                                                                                                                          |                                                     |                 |                  |                 |                | bit   |  |  |  |

| U-0          | U-0                                                                                                                      | U-0                                                 | U-0             | R-0              | R-0             | R-0            | R-0   |  |  |  |

|              | —                                                                                                                        | —                                                   | _               | ROV              | RFUL            | TUNF           | TMPTY |  |  |  |

| bit 7        |                                                                                                                          |                                                     |                 |                  |                 |                | bit   |  |  |  |

| Legend:      |                                                                                                                          |                                                     |                 |                  |                 |                |       |  |  |  |

| R = Readab   | le bit                                                                                                                   | W = Writable bit U = Unimplemented bit, read as '0' |                 |                  |                 |                |       |  |  |  |

| -n = Value a | t POR                                                                                                                    | '1' = Bit is set                                    | t               | '0' = Bit is cle | ared            | x = Bit is unk | nown  |  |  |  |

|              | •<br>•<br>0010 = Slot #2 is currently active<br>0001 = Slot #1 is currently active<br>0000 = Slot #0 is currently active |                                                     |                 |                  |                 |                |       |  |  |  |

| bit 7-4      | Unimplement                                                                                                              | t <b>ed:</b> Read as '                              | 0'              |                  |                 |                |       |  |  |  |

| bit 3        | ROV: Receive<br>1 = A receive<br>0 = A receive                                                                           | overflow has                                        | occurred for at | t least one rece | eive register   |                |       |  |  |  |

| bit 2        | RFUL: Receiv<br>1 = New data<br>0 = The receiv                                                                           | is available in                                     | the receive re  | egisters         |                 |                |       |  |  |  |

| bit 1        | <b>TUNF:</b> Transn<br>1 = A transmit<br>0 = A transmit                                                                  | underflow ha                                        | s occurred for  | at least one tra | ansmit register |                |       |  |  |  |

| bit 0        | TMPTY: Trans                                                                                                             |                                                     | npty Status bit |                  |                 |                |       |  |  |  |

#### REGISTER 20-4: DCISTAT: DCI STATUS REGISTER

### 21.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.