Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp708at-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

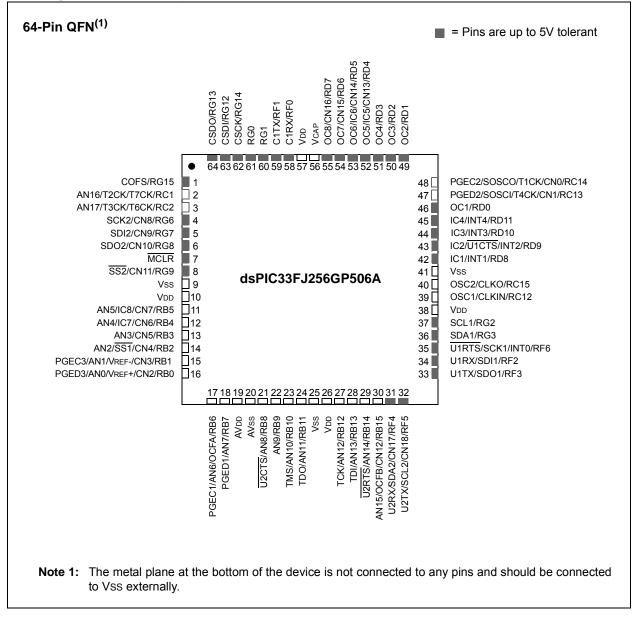

### Pin Diagrams (Continued)

NOTES:

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206A

- dsPIC33FJ64GP306A

- dsPIC33FJ64GP310A

- dsPIC33FJ64GP706A

- dsPIC33FJ64GP708A

- dsPIC33FJ64GP710A

- dsPIC33FJ128GP206A

- dsPIC33FJ128GP306A

- dsPIC33FJ128GP310A

- dsPIC33FJ128GP706A

- dsPIC33FJ128GP708A

- dsPIC33FJ128GP710A

- dsPIC33FJ256GP506A

- dsPIC33FJ256GP510A

- dsPIC33FJ256GP710A

The dsPIC33FJXXXGPX06A/X08A/X10A General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes). This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

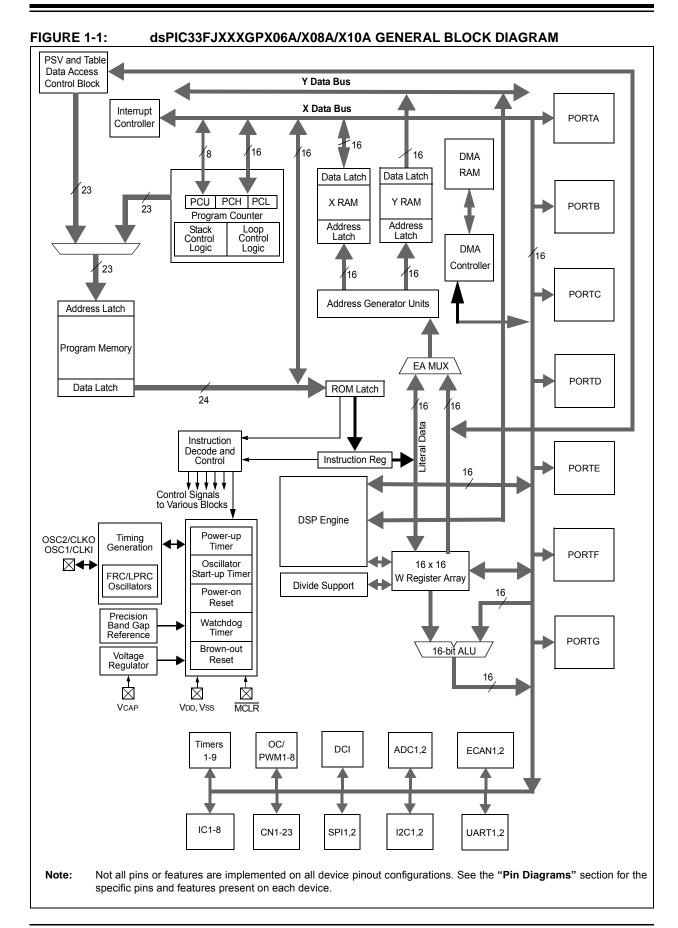

The dsPIC33FJXXXGPX06A/X08A/X10A device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06A/X08A/X10A Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXGPX06A/X08A/X10A devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06A/X08A/X10A devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

NOTES:

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                      | Bit 8    | Bit 7    | Bit 6    | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|--------|--------|----------------------------|----------|----------|----------|--------|-------|--------|--------|-------|--------|---------------|

| C2RXF10EID | 056A |           |           |        | EID<   | 15:8>  |        |                            |          | EID<7:0> |          |        |       |        |        |       | xxxx   |               |

| C2RXF11SID | 056C |           |           |        | SID<   | 10:3>  |        |                            |          |          | SID<2:0> |        | —     | EXIDE  | _      | EID<1 | 17:16> | xxxx          |

| C2RXF11EID | 056E |           |           |        | EID<   | 15:8>  |        |                            |          | EID<7:0> |          |        |       |        |        | xxxx  |        |               |

| C2RXF12SID | 0570 | SID<10:3> |           |        |        |        |        | SID<2:0>                   |          | —        | EXIDE    | —      | EID<1 | 17:16> | xxxx   |       |        |               |

| C2RXF12EID | 0572 |           |           |        | EID<   | 15:8>  |        |                            |          | EID<7:0> |          |        |       |        |        | xxxx  |        |               |

| C2RXF13SID | 0574 |           | SID<10:3> |        |        |        |        | SID<2:0> — EXIDE — EID<17: |          |          |          | 17:16> | xxxx  |        |        |       |        |               |

| C2RXF13EID | 0576 |           |           |        | EID<   | 15:8>  |        |                            |          |          |          |        | EID<  | <7:0>  |        |       |        | xxxx          |

| C2RXF14SID | 0578 |           |           |        | SID<   | 10:3>  |        |                            |          |          | SID<2:0> |        |       | EXIDE  | _      | EID<1 | 17:16> | xxxx          |

| C2RXF14EID | 057A |           | EID<15:8> |        |        |        |        | EID<7:0>                   |          |          |          |        |       | xxxx   |        |       |        |               |

| C2RXF15SID | 057C |           | SID<10:3> |        |        |        |        |                            | SID<2:0> |          | _        | EXIDE  | _     | EID<1  | 17:16> | xxxx  |        |               |

| C2RXF15EID | 057E |           | EID<15:8> |        |        |        |        |                            |          |          | EID<     | <7:0>  |       |        |        | xxxx  |        |               |

#### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR dsPIC33FJXXXGP706A/708A/710A DEVICES ONLY (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-0          | R/W-0                                                                                        | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |  |  |

|--------------|----------------|----------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|-----------------|--|--|--|--|--|--|

| -            | DMA1IE         | AD1IE                                                                                        | U1TXIE          | U1RXIE            | SPI1IE           | SPI1EIE         | T3IE            |  |  |  |  |  |  |

| bit 15       |                |                                                                                              |                 |                   |                  |                 | b               |  |  |  |  |  |  |

| R/W-0        | DAM 0          | D/M/ 0                                                                                       | DAM 0           | R/W-0             | R/W-0            | D/M/ O          | D/M/ O          |  |  |  |  |  |  |

| T2IE         | R/W-0<br>OC2IE | R/W-0                                                                                        | R/W-0<br>DMA0IE | T1IE              | OC1IE            | R/W-0<br>IC1IE  | R/W-0<br>INT0IE |  |  |  |  |  |  |

| oit 7        | OCZIE          | ICZIE                                                                                        | DIVIAULE        | 111               | OCTIE            | ICTIE           | b               |  |  |  |  |  |  |

|              |                |                                                                                              |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| Legend:      |                |                                                                                              |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| R = Readabl  | e bit          | W = Writable                                                                                 | bit             | U = Unimplem      | nented bit, read | d as '0'        |                 |  |  |  |  |  |  |

| n = Value at | POR            | '1' = Bit is se                                                                              | t               | '0' = Bit is clea | ared             | x = Bit is unkn | own             |  |  |  |  |  |  |

|              |                |                                                                                              |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 15       | Unimpleme      | nted: Read as                                                                                | ʻ0'             |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 14       |                | /A Channel 1 E                                                                               |                 | Complete Interru  | upt Enable bit   |                 |                 |  |  |  |  |  |  |

|              |                | request enable<br>request not en                                                             |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 13       | •              | 1 Conversion (                                                                               |                 | runt Enable bit   |                  |                 |                 |  |  |  |  |  |  |

|              |                | request enable                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | request not en                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 12       | U1TXIE: UA     | U1TXIE: UART1 Transmitter Interrupt Enable bit                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                           |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| -:- 44       |                | •                                                                                            |                 | - 1-14            |                  |                 |                 |  |  |  |  |  |  |

| oit 11       |                | <b>U1RXIE:</b> UART1 Receiver Interrupt Enable bit<br>1 = Interrupt request enabled          |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | 0 = Interrupt request not enabled                                                            |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 10       | SPI1IE: SPI    | SPI1IE: SPI1 Event Interrupt Enable bit                                                      |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | request enable                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | -              | request not en                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 9        |                | SPI1EIE: SPI1 Error Interrupt Enable bit<br>1 = Interrupt request enabled                    |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | request enable                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 8        | -              | T3IE: Timer3 Interrupt Enable bit                                                            |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | 1 = Interrupt  | 1 = Interrupt request enabled                                                                |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | •              | 0 = Interrupt request not enabled                                                            |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 7        |                | T2IE: Timer2 Interrupt Enable bit                                                            |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              |                | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 6        | •              | OC2IE: Output Compare Channel 2 Interrupt Enable bit                                         |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | -              | 1 = Interrupt request enabled                                                                |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | 0 = Interrupt  | request not en                                                                               | abled           |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 5        | •              | Capture Chanr                                                                                | •               | Enable bit        |                  |                 |                 |  |  |  |  |  |  |

|              |                | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 4        |                | /IA Channel 0 E                                                                              |                 | Complete Interru  | upt Enable bit   |                 |                 |  |  |  |  |  |  |

|              |                | request enable                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

|              | -              | request not en                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

| ait 0        | T1IE: Timer1   | 1 Interrupt Engl                                                                             | la hit          |                   |                  |                 |                 |  |  |  |  |  |  |

| oit 3        |                | request enable                                                                               |                 |                   |                  |                 |                 |  |  |  |  |  |  |

###

| U-0          | R/W-1                                    | R/W-0                                                                                                                                                                                                                                                       | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |

|--------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-----------------|-----------------|-------|--|--|

| —            |                                          | T6IP<2:0>                                                                                                                                                                                                                                                   |       |                  |                 | DMA4IP<2:0>     |       |  |  |

| pit 15       |                                          |                                                                                                                                                                                                                                                             |       |                  |                 |                 | bit 8 |  |  |

| U-0          | U-0                                      | U-0                                                                                                                                                                                                                                                         | U-0   | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |

| _            | —                                        | _                                                                                                                                                                                                                                                           |       | —                |                 | OC8IP<2:0>      |       |  |  |

| bit 7        |                                          | -                                                                                                                                                                                                                                                           |       |                  | •               |                 | bit 0 |  |  |

| Legend:      |                                          |                                                                                                                                                                                                                                                             |       |                  |                 |                 |       |  |  |

| R = Readab   | le bit                                   | W = Writable I                                                                                                                                                                                                                                              | oit   | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |

| -n = Value a | t POR                                    | '1' = Bit is set                                                                                                                                                                                                                                            |       | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |  |  |

| pit 11       | 000 = Interru                            | upt is priority 1<br>upt source is disa<br>n <b>ted:</b> Read as '0                                                                                                                                                                                         |       |                  |                 |                 |       |  |  |

| bit 10-8     | 111 = Interru<br>•<br>•<br>001 = Interru | Unimplemented: Read as '0'<br>DMA4IP<2:0>: DMA Channel 4 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |       |                  |                 |                 |       |  |  |

| bit 7-3      | Unimplemer                               | nted: Read as 'o                                                                                                                                                                                                                                            | )'    |                  |                 |                 |       |  |  |

| bit 2-0      |                                          | : Output Compa<br>ıpt is priority 7 (ł                                                                                                                                                                                                                      |       |                  | ity bits        |                 |       |  |  |

|              |                                          | upt is priority 1<br>upt source is disa                                                                                                                                                                                                                     | abled |                  |                 |                 |       |  |  |

### 10.0 POWER-SAVING FEATURES

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) in "dsPIC33F/PIC24H Familv the Reference Manual", which is available the site from Microchip web (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXGPX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXGPX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXGPX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into SLEEP modePWRSAV#IDLE\_MODE; Put the device into IDLE mode

| REGISTER '    | <u>10-2:</u> PMD2                          | 2: PERIPHER                        |                  | DISABLE C         | ONTROL RE        | GISTER 2        |       |  |  |  |  |  |

|---------------|--------------------------------------------|------------------------------------|------------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| R/W-0         | R/W-0                                      | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| IC8MD         | IC7MD                                      | IC6MD                              | IC5MD            | IC4MD             | IC3MD            | IC2MD           | IC1MD |  |  |  |  |  |

| bit 15        |                                            |                                    |                  |                   |                  |                 | bit 8 |  |  |  |  |  |

| R/W-0         | R/W-0                                      | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| OC8MD         | OC7MD                                      | OC6MD                              | OC5MD            | OC4MD             | OC3MD            | OC2MD           | OC1MD |  |  |  |  |  |

| bit 7         |                                            |                                    |                  |                   |                  |                 | bit 0 |  |  |  |  |  |

| Legend:       |                                            |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

| R = Readable  | e bit                                      | W = Writable                       | bit              | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                                        | '1' = Bit is set                   |                  | '0' = Bit is clea | ared             | x = Bit is unkr | lown  |  |  |  |  |  |

| bit 15        | IC8MD: Input                               | Capture 8 Mod                      | lule Disable bit | t                 |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 8 module i<br>ture 8 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 14        | IC7MD: Input                               | Capture 7 Mod                      | lule Disable bit | t                 |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 7 module i<br>ture 7 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 13        |                                            | Capture 6 Mod                      |                  | ŀ                 |                  |                 |       |  |  |  |  |  |

|               | 1 = Input Cap                              | ture 6 module i<br>ture 6 module i | s disabled       |                   |                  |                 |       |  |  |  |  |  |

| bit 12        | IC5MD: Input Capture 5 Module Disable bit  |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 5 module i<br>ture 5 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 11        | IC4MD: Input Capture 4 Module Disable bit  |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 4 module i<br>ture 4 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 10        | IC3MD: Input Capture 3 Module Disable bit  |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 3 module i<br>ture 3 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 9         | IC2MD: Input Capture 2 Module Disable bit  |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 2 module i<br>ture 2 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 8         | IC1MD: Input Capture 1 Module Disable bit  |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ture 1 module i<br>ture 1 module i |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 7         | OC8MD: Output Compare 8 Module Disable bit |                                    |                  |                   |                  |                 |       |  |  |  |  |  |

|               |                                            | ompare 8 modu<br>ompare 8 modu     |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 6         | OC7MD: Out                                 | put Compare 4                      | Module Disabl    | e bit             |                  |                 |       |  |  |  |  |  |

|               |                                            | ompare 7 modu<br>ompare 7 modu     |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 5         | -                                          | put Compare 6                      |                  | e bit             |                  |                 |       |  |  |  |  |  |

|               | •                                          | ompare 6 modu<br>ompare 6 modu     |                  |                   |                  |                 |       |  |  |  |  |  |

| bit 4         | OC5MD: Out                                 | put Compare 5                      | Module Disabl    | e bit             |                  |                 |       |  |  |  |  |  |

|               |                                            | ompare 5 modu<br>ompare 5 modu     |                  |                   |                  |                 |       |  |  |  |  |  |

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

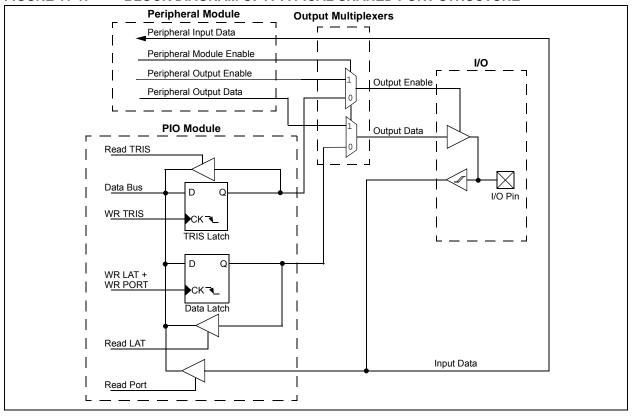

### 11.0 I/O PORTS

- This data sheet summarizes the features Note 1: of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in "dsPIC33F/PIC24H the Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

© 2009-2012 Microchip Technology Inc.

| U-0                             | U-0                                                                | R-0                | R-0 | R-0                 | R-0          | R-0                | R-0   |  |  |  |  |  |

|---------------------------------|--------------------------------------------------------------------|--------------------|-----|---------------------|--------------|--------------------|-------|--|--|--|--|--|

| —                               |                                                                    |                    |     | FBP<5               | :0>          |                    |       |  |  |  |  |  |

| pit 15                          |                                                                    |                    |     |                     |              |                    | bit 8 |  |  |  |  |  |

|                                 |                                                                    |                    |     |                     |              |                    |       |  |  |  |  |  |

| U-0                             | U-0                                                                | R-0                | R-0 | R-0                 | R-0          | R-0                | R-0   |  |  |  |  |  |

|                                 |                                                                    |                    |     | FNRB<               | 5:0>         |                    |       |  |  |  |  |  |

| oit 7                           |                                                                    |                    |     |                     |              |                    | bit C |  |  |  |  |  |

|                                 |                                                                    |                    |     |                     |              |                    |       |  |  |  |  |  |

| L <b>egend:</b><br>R = Readable | e bit                                                              | W = Writable b     | it  | U = Unimplemer      | ited bit, re | ad as '0'          |       |  |  |  |  |  |

| n = Value at                    | POR                                                                | '1' = Bit is set   |     | '0' = Bit is cleare | d            | x = Bit is unknown |       |  |  |  |  |  |

|                                 |                                                                    |                    |     |                     |              |                    |       |  |  |  |  |  |

| oit 15-14                       | Unimpleme                                                          | ented: Read as '0' | 1   |                     |              |                    |       |  |  |  |  |  |

| oit 13-8                        | FBP<5:0>: FIFO Write Buffer Pointer bits                           |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | 011111 = RB31 buffer                                               |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | 011110 <b>= F</b>                                                  | RB30 buffer        |     |                     |              |                    |       |  |  |  |  |  |

|                                 | •                                                                  |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | •                                                                  |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | 000001 = T<br>000000 = T                                           |                    |     |                     |              |                    |       |  |  |  |  |  |

| oit 7-6                         |                                                                    | ented: Read as '0' |     |                     |              |                    |       |  |  |  |  |  |

| oit 5-0                         | -                                                                  |                    |     | tor hite            |              |                    |       |  |  |  |  |  |

| 510 5-0                         | FNRB<5:0>: FIFO Next Read Buffer Pointer bits 011111 = RB31 buffer |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | 011111 <b>–</b> F                                                  |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | •                                                                  |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | •                                                                  |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 | •<br>000001 = T                                                    |                    |     |                     |              |                    |       |  |  |  |  |  |

|                                 |                                                                    |                    |     |                     |              |                    |       |  |  |  |  |  |

### REGISTER 19-5: CiFIFO: ECAN™ FIFO STATUS REGISTER

#### REGISTER 19-13: CIBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                         | R/W-0                   | R/W-0          | R/W-0           | R/W-0 |  |

|---------------|--------------------------------|---------------------------------------------------------|-------------------------------|-------------------------|----------------|-----------------|-------|--|

|               | F7BP                           | <3:0>                                                   |                               | F6BP<3:0>               |                |                 |       |  |

| bit 15        |                                |                                                         |                               |                         |                |                 | bit   |  |

|               |                                |                                                         |                               |                         |                |                 |       |  |

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                         | R/W-0                   | R/W-0          | R/W-0           | R/W-0 |  |

|               | F5BP                           | <3:0>                                                   |                               |                         | F4B            | P<3:0>          |       |  |

| bit 7         |                                |                                                         |                               |                         |                |                 | bit   |  |

| Legend:       |                                |                                                         |                               |                         |                |                 |       |  |

| R = Readable  | e bit                          | W = Writable                                            | bit                           | U = Unimplem            | ented bit, rea | ad as '0'       |       |  |

| -n = Value at | POR                            | '1' = Bit is set                                        |                               | '0' = Bit is clea       |                | x = Bit is unkı | nown  |  |

| bit 15-12     |                                | RX Buffer Writt                                         |                               |                         |                |                 |       |  |

|               |                                | hits received ir hits received ir                       |                               | -                       |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               |                                | hits received ir hits received ir                       |                               |                         |                |                 |       |  |

| bit 11-8      | 1111 = Filter                  | RX Buffer Writt<br>hits received ir<br>hits received ir | NRX FIFO bu                   | uffer                   |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               |                                | hits received ir hits received ir                       |                               |                         |                |                 |       |  |

| bit 7-4       | 1111 = Filter<br>1110 = Filter | RX Buffer Writt<br>hits received in<br>hits received in | RX FIFO bu                    | uffer                   |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               |                                | hits received ir<br>hits received ir                    |                               |                         |                |                 |       |  |

| bit 3-0       | F4BP<3:0>:<br>1111 = Filter    | RX Buffer Writt<br>hits received ir<br>hits received ir | en when Filte<br>n RX FIFO bu | er 4 Hits bits<br>uffer |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | •                              |                                                         |                               |                         |                |                 |       |  |

|               | 0001 = Filter<br>0000 = Filter | hits received ir                                        |                               |                         |                |                 |       |  |

| R/W-0         | U-0                                                                                                                     | U-0                                              | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|----------------------|-----------------|-----------------|-------|--|--|--|--|--|

| ADRC          |                                                                                                                         | _                                                |               |                      | SAMC<4:0>(      | 1)              |       |  |  |  |  |  |

| bit 15        |                                                                                                                         |                                                  |               |                      |                 |                 | bit 8 |  |  |  |  |  |

|               |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                   | R/W-0                                            | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|               |                                                                                                                         |                                                  | ADCS          | <7:0> <sup>(2)</sup> |                 |                 |       |  |  |  |  |  |

| bit 7         |                                                                                                                         |                                                  |               |                      |                 |                 | bit ( |  |  |  |  |  |

| Legend:       |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

| R = Readabl   | e hit                                                                                                                   | W = Writable b                                   | hit           | U = Unimpler         | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value at |                                                                                                                         | '1' = Bit is set                                 |               | '0' = Bit is cle     |                 | x = Bit is unkr | าดพท  |  |  |  |  |  |

|               |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

| bit 15        | ADRC: ADO                                                                                                               | C Conversion Clo                                 | ck Source bit |                      |                 |                 |       |  |  |  |  |  |

|               | 1 = ADC internal RC clock                                                                                               |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 0 = Clock de                                                                                                            | erived from syster                               | m clock       |                      |                 |                 |       |  |  |  |  |  |

| bit 14-13     | Unimpleme                                                                                                               | ented: Read as '0                                | ,             |                      |                 |                 |       |  |  |  |  |  |

| bit 12-8      | SAMC<4:0>: Auto Sample Time bits <sup>(1)</sup>                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 11111 = 31 TAD                                                                                                          |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | • $-1$                                                                                                                  |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 00001 = 1 TAD<br>00000 = 0 TAD                                                                                          |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

| bit 7-0       | ADCS<7:0>: ADC Conversion Clock Select bits <sup>(2)</sup>                                                              |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 11111111 = Reserved                                                                                                     |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 0100000 = Reserved                                                                                                      |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 01000000 - Reserved<br>$00111111 = \text{Tcy} \cdot (\text{ADCS}<7:0> + 1) = 64 \cdot \text{Tcy} = \text{Tad}$          |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                       |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               | 00000010:                                                                                                               | 00000010 = Tcy · (ADCS<7:0> + 1) = 3 · Tcy = Tad |               |                      |                 |                 |       |  |  |  |  |  |

|               | $0000001 = TCY \cdot (ADCS<7.0> + 1) = 3 \cdot TCY = TAD$<br>$00000001 = TCY \cdot (ADCS<7.0> + 1) = 2 \cdot TCY = TAD$ |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                         |                                                  |               |                      |                 |                 |       |  |  |  |  |  |

2: This bit is not used if ADxCON3<15> (ADRC) = 1.

NOTES:

### TABLE 23-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                            |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                            |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                        |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                             |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                 |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                             |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                          |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2,<br>[W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2,<br>[W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2,<br>[W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2,<br>[W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

### 24.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 24.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 24.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

NOTES:

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187

Fax: 86-571-2819-3189 China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820