Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp710a-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXGPX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXGPX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

## 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.6 DSP Engine

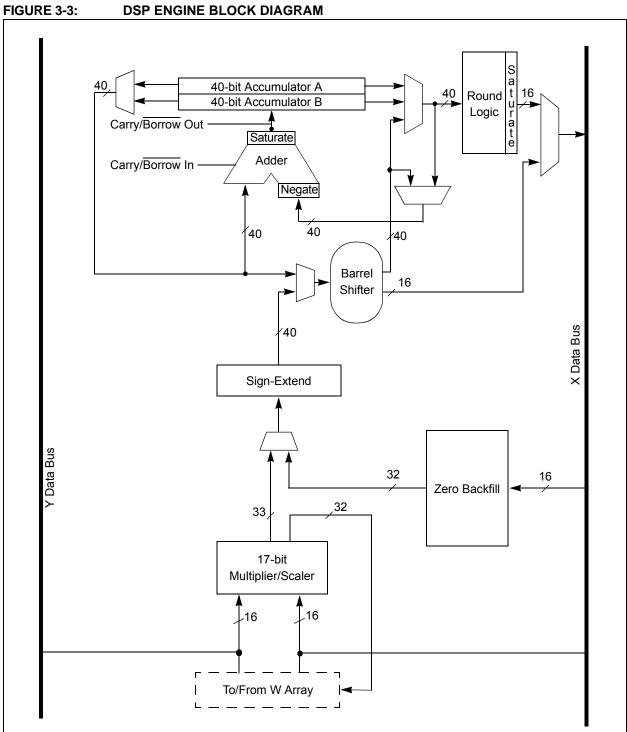

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXGPX06A/X08A/X10A is a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- · Conventional or convergent rounding (RND)

- Automatic saturation on/off for AccA (SATA)

- Automatic saturation on/off for AccB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

Table 3-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | A = A + x2              | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

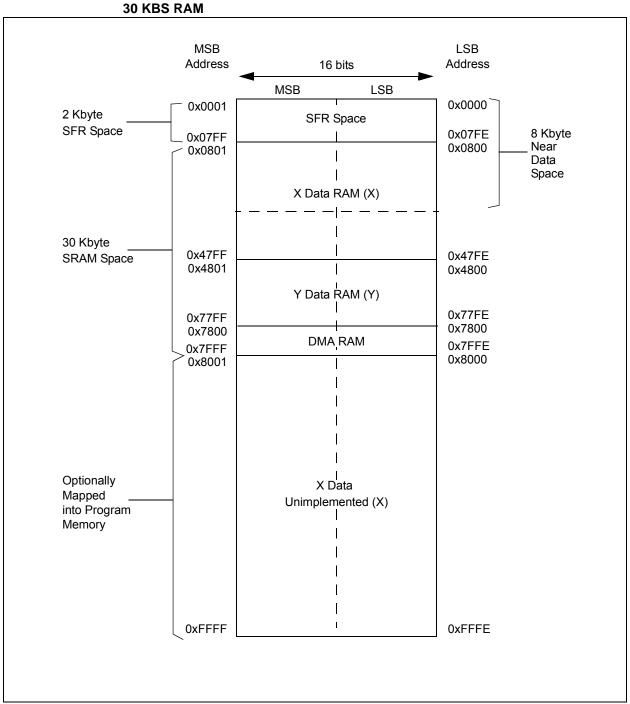

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 30 KBS RAM

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                           | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Reset |

|----------|-------------|--------|----------------------------------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|---------------|--------------|-------------|---------|-------|--------------|

| WREG0    | 0000        |        |                                  |        |        |        |        |         | Working Re    | gister 0      |        |           |               |              |             |         |       | xxx          |

| WREG1    | 0002        |        |                                  |        |        |        |        |         | Working Re    | gister 1      |        |           |               |              |             |         |       | XXX          |

| WREG2    | 0004        |        |                                  |        |        |        |        |         | Working Re    | gister 2      |        |           |               |              |             |         |       | xxxx         |

| WREG3    | 0006        |        |                                  |        |        |        |        |         | Working Re    | gister 3      |        |           |               |              |             |         |       | XXXX         |

| WREG4    | 8000        |        |                                  |        |        |        |        |         | Working Re    | gister 4      |        |           |               |              |             |         |       | XXXX         |

| WREG5    | 000A        |        |                                  |        |        |        |        |         | Working Re    | gister 5      |        |           |               |              |             |         |       | XXXX         |

| WREG6    | 000C        |        |                                  |        |        |        |        |         | Working Re    | gister 6      |        |           |               |              |             |         |       | XXXX         |

| WREG7    | 000E        |        |                                  |        |        |        |        |         | Working Re    | gister 7      |        |           |               |              |             |         |       | XXXX         |

| WREG8    | 0010        |        |                                  |        |        |        |        |         | Working Re    | gister 8      |        |           |               |              |             |         |       | XXXX         |

| WREG9    | 0012        |        |                                  |        |        |        |        |         | Working Re    | gister 9      |        |           |               |              |             |         |       | XXXX         |

| WREG10   | 0014        |        |                                  |        |        |        |        |         | Working Re    | gister 10     |        |           |               |              |             |         |       | XXXX         |

| WREG11   | 0016        |        |                                  |        |        |        |        |         | Working Re    | gister 11     |        |           |               |              |             |         |       | XXXX         |

| WREG12   | 0018        |        |                                  |        |        |        |        |         | Working Re    | gister 12     |        |           |               |              |             |         |       | XXXX         |

| WREG13   | 001A        |        |                                  |        |        |        |        |         | Working Re    | gister 13     |        |           |               |              |             |         |       | XXXX         |

| WREG14   | 001C        |        |                                  |        |        |        |        |         | Working Re    | gister 14     |        |           |               |              |             |         |       | XXXX         |

| WREG15   | 001E        |        |                                  |        |        |        |        |         | Working Re    | gister 15     |        |           |               |              |             |         |       | 0800         |

| SPLIM    | 0020        |        | Stack Pointer Limit Register     |        |        |        |        |         |               |               |        |           |               |              | XXXX        |         |       |              |

| ACCAL    | 0022        |        | Accumulator A Low Word Register  |        |        |        |        |         |               |               |        |           |               |              | 0000        |         |       |              |

| ACCAH    | 0024        |        | Accumulator A High Word Register |        |        |        |        |         |               |               |        |           |               |              |             | 0000    |       |              |

| ACCAU    | 0026        |        |                                  |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | lister |           |               |              |             |         |       | 0000         |

| ACCBL    | 0028        |        |                                  |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |               |              |             |         |       | 0000         |

| ACCBH    | 002A        |        |                                  |        |        |        |        | Accum   | ulator B High | Word Regi     | ster   |           |               |              |             |         |       | 0000         |

| ACCBU    | 002C        |        |                                  |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | lister |           |               |              |             |         |       | 0000         |

| PCL      | 002E        |        |                                  |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |               |              |             |         |       | 0000         |

| PCH      | 0030        | -      | _                                | _      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter     | High Byte R  | legister    |         |       | 0000         |

| TBLPAG   | 0032        | -      | _                                | _      | _      | _      | _      | _       | _             |               |        | Table F   | Page Addres   | ss Pointer F | Register    |         |       | 0000         |

| PSVPAG   | 0034        | -      | _                                | _      | _      | _      | _      | _       | _             |               | Progra | am Memory | Visibility Pa | age Addres   | s Pointer R | egister |       | 0000         |

| RCOUNT   | 0036        |        |                                  |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |               |              |             |         |       | XXXX         |

| DCOUNT   | 0038        |        |                                  |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |               |              |             |         |       | xxxx         |

| DOSTARTL | 003A        |        |                                  |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |               |              |             |         | 0     | xxxx         |

| DOSTARTH | 003C        | _      | _                                | _      | _      | _      |        | _       | _             | _             |        |           |               | DOSTAF       | RTH<5:0>    |         |       | 00xx         |

| DOENDL   | 003E        |        |                                  |        |        |        |        | DO      | ENDL<15:1     | >             |        |           |               |              |             |         | 0     | xxxx         |

| DOENDH   | 0040        | _      | _                                | _      | _      | _      |        | _       | _             | —             |        |           |               | DOE          | NDH         |         |       | 00xx         |

| SR       | 0042        | OA     | OB                               | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA            | Ν            | OV          | Z       | С     | 0000         |

| CORCON   | 0044        | _      | _                                | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT        | IPL3         | PSV         | RND     | IF    | 0020         |

| MODCON   | 0046        | XMODEN | YMODEN                           | _      | _      |        | BWM    | 1<3:0>  |               |               | YWM    | <3:0>     |               |              | XWM         | <3:0>   |       | 0000         |

| XMODSRT  | 0048        |        |                                  |        |        |        |        | )       | (S<15:1>      |               |        |           |               |              |             |         | 0     | XXXX         |

| XMODEND  | 004A        |        |                                  |        |        |        |        | )       | (E<15:1>      |               |        |           |               |              |             |         | 1     | XXXX         |

| YMODSRT  | 004C        |        |                                  |        |        |        |        | ١       | ′S<15:1>      |               |        |           |               |              |             |         | 0     | XXXX         |

| YMODEND  | 004E        |        |                                  |        |        |        |        | ١       | ′E<15:1>      |               |        |           |               |              |             |         | 1     | XXXX         |

#### TABLE 4-1. CPU CORE REGISTERS MAP

dsPIC33FJXXXGPX06A/X08A/X10A

| SFR Name | SFR<br>Addr | Bit 15     | Bit 14                   | Bit 13      | Bit 12     | Bit 11      | Bit 10     | Bit 9      | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|------------|--------------------------|-------------|------------|-------------|------------|------------|-------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |            |                          |             |            |             |            |            | Input 1 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _          | _                        | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |            |                          |             |            |             |            |            | Input 2 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        | _          | _                        | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |            |                          |             |            |             |            |            | Input 3 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        | _          | _                        | ICSIDL      | —          | —           | —          | —          | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |            | Input 4 Capture Register |             |            |             |            |            |             |              |       | xxxx  |       |       |       |          |       |               |

| IC4CON   | 014E        | _          | _                        | ICSIDL      | _          | _           | _          | _          | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |            |                          |             |            |             |            |            | Input 5 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        |            |                          | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |            |                          |             |            |             |            |            | Input 6 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        |            |                          | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |            |                          |             |            |             |            |            | Input 7 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        |            |                          | ICSIDL      |            |             | _          |            |             | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |            |                          |             |            |             |            |            | Input 8 Ca  | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _          | _                        | ICSIDL      | —          | —           | —          | _          | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Legend:  | x = unkno   | wn value c | n Reset, -               | – = unimple | emented, r | ead as '0'. | Reset valu | es are sho | wn in hexad | lecimal.     |       |       |       |       |       |          |       |               |

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

dsPIC33FJXXXGPX06A/X08A/X10A

#### TABLE 4-15: ADC1 REGISTER MAP

| File Name   | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11    | Bit 10    | Bit 9   | Bit 8    | Bit 7    | Bit 6     | Bit 5  | Bit 4      | Bit 3  | Bit 2  | Bit 1     | Bit 0   | All<br>Resets |

|-------------|------|--------|-----------|--------|---------|-----------|-----------|---------|----------|----------|-----------|--------|------------|--------|--------|-----------|---------|---------------|

| ADC1BUF0    | 0300 |        |           |        |         |           |           |         | ADC Data | Buffer 0 |           |        |            |        |        |           |         | xxxx          |

| AD1CON1     | 0320 | ADON   | _         | ADSIDL | ADDMABM | _         | AD12B     | FOR     | И<1:0>   | :        | SSRC<2:0> |        | _          | SIMSAM | ASAM   | SAMP      | DONE    | 0000          |

| AD1CON2     | 0322 | ١      | /CFG<2:0> | >      | _       | _         | CSCNA     | CHP     | S<1:0>   | BUFS     | _         |        | SMPI       | <3:0>  |        | BUFM      | ALTS    | 0000          |

| AD1CON3     | 0324 | ADRC   |           | —      |         | SAMC<4:0> |           |         |          |          | ADCS<7:0> |        |            |        |        |           | 0000    |               |

| AD1CHS123   | 0326 | _      |           | —      | _       |           | CH123N    | NB<1:0> | CH123SB  |          |           |        | —          | —      | CH123N | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0     | 0328 | CH0NB  |           | —      |         | CI        | H0SB<4:0> | >       |          | CH0NA    |           |        | CH0SA<4:0> |        |        |           |         | 0000          |

| AD1PCFGH(1) | 032A | PCFG31 | PCFG30    | PCFG29 | PCFG28  | PCFG27    | PCFG26    | PCFG25  | PCFG24   | PCFG23   | PCFG22    | PCFG21 | PCFG20     | PCFG19 | PCFG18 | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL    | 032C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11    | PCFG10    | PCFG9   | PCFG8    | PCFG7    | PCFG6     | PCFG5  | PCFG4      | PCFG3  | PCFG2  | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)  | 032E | CSS31  | CSS30     | CSS29  | CSS28   | CSS27     | CSS26     | CSS25   | CSS24    | CSS23    | CSS22     | CSS21  | CSS20      | CSS19  | CSS18  | CSS17     | CSS16   | 0000          |

| AD1CSSL     | 0330 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11     | CSS10     | CSS9    | CSS8     | CSS7     | CSS6      | CSS5   | CSS4       | CSS3   | CSS2   | CSS1      | CSS0    | 0000          |

| AD1CON4     | 0332 | _      | _         | _      | —       | _         | _         | _       | _        | _        | _         | _      | _          | _      | [      | DMABL<2:( | )>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

#### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8    | Bit 7    | Bit 6    | Bit 5 | Bit 4        | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|--------|----------|---------|----------|----------|----------|-------|--------------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         |        |          |         | ADC Data | Buffer 0 |          |       |              |        |        |          |         | xxxx          |

| AD2CON1   | 0360 | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B    | FORI    | M<1:0>   | Ş        | SSRC<2:0 | >     | _            | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 | Ň      | VCFG<2:0> | >      | _       | _      | CSCNA    | CHP     | S<1:0>   | BUFS     | _        |       | SMPI         | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | _         | _      |         | S      | AMC<4:0> |         |          |          |          |       | ADC          | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366 | _      | _         | _      | _       | _      | CH123N   | IB<1:0> | CH123SB  | _        | _        | _     | _            | _      | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | _      | _       |        | CH0S     | B<3:0>  |          | CH0NA    | _        | _     | — CH0SA<3:0> |        |        |          | 0000    |               |

| Reserved  | 036A | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _            | _      | _      | _        | _       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10   | PCFG9   | PCFG8    | PCFG7    | PCFG6    | PCFG5 | PCFG4        | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _            | _      | _      | _        | _       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8     | CSS7     | CSS6     | CSS5  | CSS4         | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | _      | _       |        | _        | _       | _        | _        | _        | _     | _            | _      |        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3 |                 |                                  |                 |                  |                  |                 |       |  |  |  |  |  |  |

|------------------------------------------------------|-----------------|----------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| U-0                                                  | U-0             | R/W-0                            | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |  |  |  |  |  |  |

| _                                                    | _               | DMA5IF                           | DCIIF           | DCIEIF           | _                | —               | C2IF  |  |  |  |  |  |  |

| bit 15                                               |                 |                                  |                 | •                |                  |                 | bit 8 |  |  |  |  |  |  |

| R/W-0                                                | R/W-0           | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |

| C2RXIF                                               | INT4IF          | INT3IF                           | T9IF            | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |  |  |  |  |  |  |

| bit 7                                                |                 |                                  |                 |                  |                  |                 | bit 0 |  |  |  |  |  |  |

| Legend:                                              |                 |                                  |                 |                  |                  |                 |       |  |  |  |  |  |  |

| R = Readable                                         | bit             | W = Writable                     | bit             | U = Unimple      | mented bit, read | as '0'          |       |  |  |  |  |  |  |

| -n = Value at I                                      |                 | '1' = Bit is set                 |                 | '0' = Bit is cle |                  | x = Bit is unkn | own   |  |  |  |  |  |  |

|                                                      |                 |                                  |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 15-14                                            | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |  |  |  |  |  |  |

| bit 13                                               | DMA5IF: DM      | A Channel 5 D                    | ata Transfer (  | Complete Inter   | rupt Flag Status | bit             |       |  |  |  |  |  |  |

|                                                      |                 | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 12                                               | DCIIF: DCI E    | vent Interrupt I                 | -lag Status bit |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      | 1 = Interrupt   | request has oc                   | curred          |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      | •               | request has no                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 11                                               |                 | Error Interrupt                  | U               | it               |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 10-9                                             | Unimplemen      | ted: Read as '                   | 0'              |                  |                  |                 |       |  |  |  |  |  |  |

| bit 8                                                | C2IF: ECAN2     | 2 Event Interrup                 | ot Flag Status  | bit              |                  |                 |       |  |  |  |  |  |  |

|                                                      | •               | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 7                                                | C2RXIF: ECA     | AN2 Receive D                    | ata Ready Int   | errupt Flag Sta  | atus bit         |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 6                                                | •               | rnal Interrupt 4                 |                 | it               |                  |                 |       |  |  |  |  |  |  |

|                                                      | 1 = Interrupt i | request has oc<br>request has no | curred          |                  |                  |                 |       |  |  |  |  |  |  |

| bit 5                                                | INT3IF: Exter   | rnal Interrupt 3                 | Flag Status b   | it               |                  |                 |       |  |  |  |  |  |  |

|                                                      | •               | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 4                                                | -               | Interrupt Flag                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      | 1 = Interrupt i | request has oc                   | curred          |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      | 0 = Interrupt   | request has no                   | t occurred      |                  |                  |                 |       |  |  |  |  |  |  |

| bit 3                                                |                 | Interrupt Flag                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has oc                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 2                                                | -               | request has no<br>2 Master Even  |                 | ag Status bit    |                  |                 |       |  |  |  |  |  |  |

| SIL Z                                                |                 | request has oc                   | •               | ug oluluo bit    |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has no                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 1                                                | SI2C2IF: 12C    | 2 Slave Events                   | Interrupt Flag  | g Status bit     |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has oc                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      | -               | request has no                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

| bit 0                                                |                 | Interrupt Flag                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | request has oc<br>request has no |                 |                  |                  |                 |       |  |  |  |  |  |  |

|                                                      |                 | iequest nas no                   |                 |                  |                  |                 |       |  |  |  |  |  |  |

### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0<br>—<br>bit 15 | U-0           | U-0                              | U-0            | U-0              | U-0              | U-0               | U-0   |

|--------------------|---------------|----------------------------------|----------------|------------------|------------------|-------------------|-------|

|                    |               |                                  |                |                  |                  |                   |       |

|                    |               |                                  |                | _                | _                |                   | bit a |

| <b>D</b> # 4 / 0   |               |                                  |                |                  |                  |                   | bitt  |

| R/W-0              | R/W-0         | R/W-0                            | R/W-0          | U-0              | R/W-0            | R/W-0             | U-0   |

| C2TXIF             | C1TXIF        | DMA7IF                           | DMA6IF         | _                | U2EIF            | U1EIF             |       |

| bit 7              |               | ·                                |                |                  |                  |                   | bit ( |

| Legend:            |               |                                  |                |                  |                  |                   |       |

| R = Readable       | - hit         | W = Writable                     | hit            | II – Unimplor    | nented bit, read | ac 'O'            |       |

| -n = Value at      |               | '1' = Bit is set                 |                | '0' = Bit is cle |                  | x = Bit is unknow | n     |

|                    | FUR           | I - DILIS SEL                    |                |                  | areu             | X - DILIS UNKNOW  | []    |

| bit 15-8           | Unimploment   | ted: Read as '                   | o'             |                  |                  |                   |       |

| bit 7              | •             |                                  |                | starrupt Flag S  | tatua hit        |                   |       |

| DIL 7              |               | AN2 Transmit D                   | -              | iterrupt Flag S  | datus dit        |                   |       |

|                    |               | request has oc<br>request has no |                |                  |                  |                   |       |

| bit 6              | •             | AN1 Transmit D                   |                | nterrunt Flag S  | tatus hit        |                   |       |

| bit o              |               | request has oc                   | -              | iterrupt i lag e |                  |                   |       |

|                    |               | request has no                   |                |                  |                  |                   |       |

| bit 5              | DMA7IF: DM    | IA Channel 7 D                   | ata Transfer C | omplete Interr   | upt Flag Status  | bit               |       |

|                    |               | request has oc                   |                | - F              |                  |                   |       |

|                    |               | request has no                   |                |                  |                  |                   |       |

| bit 4              | DMA6IF: DM    | IA Channel 6 D                   | ata Transfer C | omplete Interr   | upt Flag Status  | bit               |       |

|                    | 1 = Interrupt | request has oc                   | curred         |                  |                  |                   |       |

|                    | 0 = Interrupt | request has no                   | t occurred     |                  |                  |                   |       |

| bit 3              | Unimplemer    | nted: Read as '                  | 0'             |                  |                  |                   |       |

| bit 2              | U2EIF: UAR    | T2 Interrupt Fla                 | g Status bit   |                  |                  |                   |       |

|                    | 1 = Interrupt | request has oc                   | curred         |                  |                  |                   |       |

|                    | 0 = Interrupt | request has no                   | t occurred     |                  |                  |                   |       |

| bit 1              | U1EIF: UAR    | T1 Interrupt Fla                 | g Status bit   |                  |                  |                   |       |

|                    |               | request has oc                   |                |                  |                  |                   |       |

|                    | 0 = Interrupt | request has no                   | t occurred     |                  |                  |                   |       |

|                    |               | requeet nue no                   | coourica       |                  |                  |                   |       |

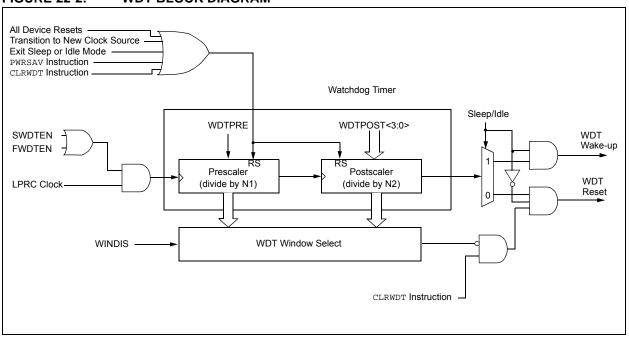

## 22.4 Watchdog Timer (WDT)

For dsPIC33FJXXXGPX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler and then can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

## FIGURE 22-2: WDT BLOCK DIAGRAM

| DC CHA       | RACTER | ISTICS                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                     |       |                                                                                                                                    |  |  |  |  |

|--------------|--------|-----------------------------------------------------------------------|------------------------------------------------------|--------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol | Characteristic                                                        | Min                                                  | Typ <sup>(1)</sup> | Max                 | Units | Conditions                                                                                                                         |  |  |  |  |

| DI60a        | licl   | Input Low Injection Current                                           | 0                                                    | _                  | <sub>-5</sub> (5,8) | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, and RB11                                                     |  |  |  |  |

| DI60b        | ІІСН   | Input High Injection Current                                          | 0                                                    | _                  | +5(6,7,8)           | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>             |  |  |  |  |

| DI60c        | Σ ΙΙΟΤ | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                   | _                  | +20 <sup>(9)</sup>  | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |  |  |  |

## TABLE 25-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

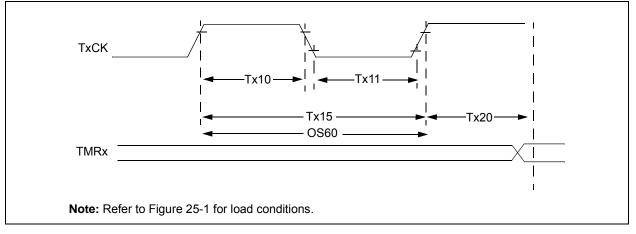

### FIGURE 25-5: TIMER1, 2, 3, 4, 5, 6, 7, 8 AND 9 EXTERNAL CLOCK TIMING CHARACTERISTICS

| TABLE 25-22: TIME | <b>R1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup></b> |

|-------------------|------------------------------------------------------------|

|-------------------|------------------------------------------------------------|

| AC CH        | ARACTERIS | TICS                                                                | (unle                     | dard Operating of the state of | <b>ated)</b><br>e -40° | <b>cons: 3.0V to 3.6</b><br>$C \le TA \le +85^{\circ}$<br>$C \le TA \le +125^{\circ}$ | C for In |                                          |

|--------------|-----------|---------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------|----------|------------------------------------------|

| Param<br>No. | Symbol    | Charact                                                             | eristic                   | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Тур                    | Мах                                                                                   | Units    | Conditions                               |

| TA10         | ТтхН      | TxCK High Time                                                      | Synchronous no prescaler  | , TCY + 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                      | _                                                                                     | ns       | Must also meet parameter TA15            |

|              |           |                                                                     | Synchronous with prescale |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                      | —                                                                                     | ns       |                                          |

|              |           |                                                                     | Asynchronou               | s 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                      | —                                                                                     | ns       |                                          |

| TA11         | TTXL      | TxCK Low Time                                                       | Synchronous no prescaler  | , (Tcy + 20)/N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                      | —                                                                                     | ns       | Must also meet parameter TA15            |

|              |           |                                                                     | Synchronous with prescale |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                      | _                                                                                     | ns       | N = prescale<br>value                    |

|              |           |                                                                     | Asynchronou               | s 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                      | —                                                                                     | ns       | (1,8,64,256)                             |

| TA15         | ΤτχΡ      | TxCK Input<br>Period                                                | Synchronous no prescaler  | , 2Tcy + 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                      | —                                                                                     | ns       | —                                        |

|              |           |                                                                     | Synchronous with prescale |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                      | _                                                                                     | —        | N = prescale<br>value<br>(1, 8, 64, 256) |

|              |           |                                                                     | Asynchronou               | s 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                      | —                                                                                     | ns       | —                                        |

| OS60         | Ft1       | SOSC1/T1CK O<br>frequency Range<br>enabled by settir<br>(T1CON<1>)) | e (oscillator             | DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                      | 50                                                                                    | kHz      | —                                        |