Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp710a-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

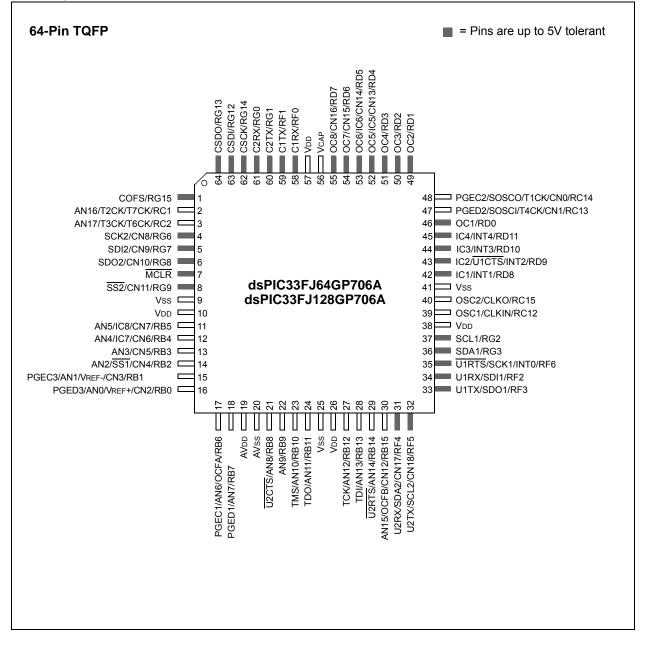

#### **Pin Diagrams (Continued)**

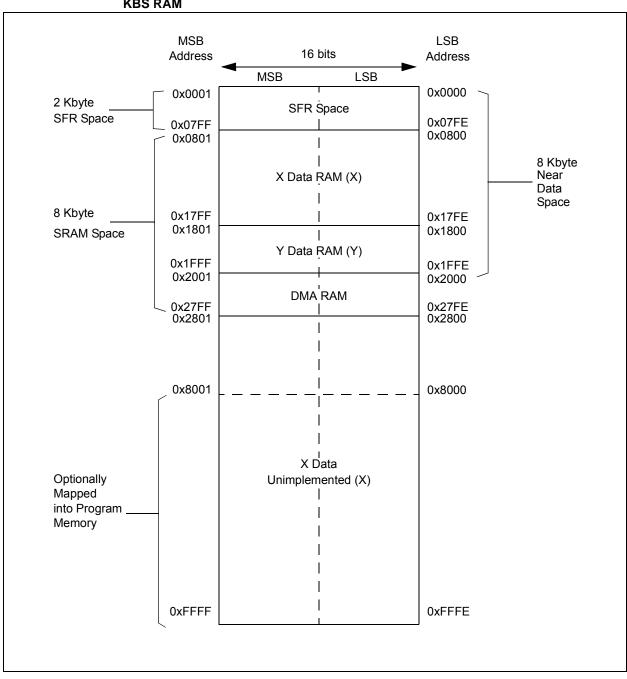

#### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 8 KBS RAM

#### **REGISTER 5-2:** NVMKEY: NON-VOLATILE MEMORY KEY REGISTER U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_ \_\_\_\_ \_ — \_\_\_\_ bit 15 W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0 NVMKEY<7:0> bit 7 Legend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

bit 8

bit 0

|              |              | 11.0                             |                           | DAALO            |                  |                 |         |

|--------------|--------------|----------------------------------|---------------------------|------------------|------------------|-----------------|---------|

| R/W-0        | R/W-0        | U-0                              | R/W-0                     | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| T6IE         | DMA4IE       |                                  | OC8IE                     | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15       |              |                                  |                           |                  |                  |                 | bi      |

| R/W-0        | R/W-0        | R/W-0                            | R/W-0                     | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE        | IC4IE        | IC3IE                            | DMA3IE                    | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7        | IOAL         | IOUL                             | DIVINOIL                  | OTIL             | Onvie            |                 | bi      |

|              |              |                                  |                           |                  |                  |                 | ~.      |

| Legend:      |              |                                  |                           |                  |                  |                 |         |

| R = Readable | e bit        | W = Writable                     | bit                       | U = Unimpler     | nented bit, read | as '0'          |         |

| n = Value at | POR          | '1' = Bit is se                  | t                         | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

|              |              |                                  |                           |                  |                  |                 |         |

| bit 15       |              | Interrupt Enal                   |                           |                  |                  |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

| bit 14       | •            | request not en                   | abled<br>Data Transfer C  | omplete Interr   | unt Enable bit   |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

|              |              | request not en                   |                           |                  |                  |                 |         |

| bit 13       | Unimplemer   | nted: Read as                    | '0'                       |                  |                  |                 |         |

| bit 12       | OC8IE: Outp  | ut Compare C                     | hannel 8 Interru          | upt Enable bit   |                  |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

| bit 11       |              | request not en                   | abled<br>hannel 7 Interru | int Enable bit   |                  |                 |         |

|              | -            | request enable                   |                           |                  |                  |                 |         |

|              |              | request not en                   |                           |                  |                  |                 |         |

| bit 10       | OC6IE: Outp  | ut Compare C                     | hannel 6 Interru          | upt Enable bit   |                  |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

| bit 9        | •            | request not en                   | abled<br>hannel 5 Interru | unt Encollo bit  |                  |                 |         |

| UIL 9        |              | request enable                   |                           | ipt Enable bit   |                  |                 |         |

|              |              | request not en                   |                           |                  |                  |                 |         |

| bit 8        | IC6IE: Input | Capture Chani                    | nel 6 Interrupt E         | Enable bit       |                  |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

| L:1 7        |              | request not en                   |                           | achla bit        |                  |                 |         |

| bit 7        | •            | request enable                   | nel 5 Interrupt E<br>ad   | nadie dit        |                  |                 |         |

|              | -            | request enable                   |                           |                  |                  |                 |         |

| bit 6        | IC4IE: Input | Capture Chani                    | nel 4 Interrupt E         | Enable bit       |                  |                 |         |

|              |              | request enable                   |                           |                  |                  |                 |         |

|              | •            | request not en                   |                           |                  |                  |                 |         |

| bit 5        | -            | -                                | nel 3 Interrupt E         | nable bit        |                  |                 |         |

|              |              | request enable<br>request not en |                           |                  |                  |                 |         |

| bit 4        | -            | -                                | Data Transfer C           | omplete Interr   | upt Enable bit   |                 |         |

|              |              | request enable                   |                           | ·                |                  |                 |         |

|              | -            | request not en                   |                           |                  |                  |                 |         |

| bit 3        | C1IE: ECAN   | 1 Event Interru                  | pt Enable bit             |                  |                  |                 |         |

|              |              | request enable                   | •                         |                  |                  |                 |         |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|---------------|-------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| —             |                   | T1IP<2:0>                                |                |                   |                 | OC1IP<2:0>      |       |

| bit 15        |                   |                                          |                |                   |                 |                 | bi    |

|               |                   |                                          |                |                   |                 |                 |       |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _             |                   | IC1IP<2:0>                               |                |                   |                 | INT0IP<2:0>     |       |

| bit 7         |                   |                                          |                |                   |                 |                 | bi    |

| Legend:       |                   |                                          |                |                   |                 |                 |       |

| R = Readabl   | e bit             | W = Writable I                           | bit            | U = Unimple       | mented bit, rea | id as '0'       |       |

| -n = Value at | POR               | '1' = Bit is set                         |                | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|               |                   |                                          |                |                   |                 |                 |       |

| bit 15        | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 14-12     | T1IP<2:0>:        | Timer1 Interrupt                         | Priority bits  |                   |                 |                 |       |

|               | 111 = Interr      | rupt is priority 7 (ł                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1<br>upt source is dis   | abled          |                   |                 |                 |       |

| bit 11        |                   | ented: Read as '                         |                |                   |                 |                 |       |

| bit 10-8      | -                 | >: Output Compa                          |                | 1 Interrupt Prior | ritv bits       |                 |       |

|               |                   | upt is priority 7 (I                     |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | 001 = Interr      | upt is priority 1                        |                |                   |                 |                 |       |

|               |                   | upt source is dis                        | abled          |                   |                 |                 |       |

| bit 7         | Unimpleme         | ented: Read as 'o                        | )'             |                   |                 |                 |       |

| bit 6-4       |                   | : Input Capture C                        |                |                   | oits            |                 |       |

|               | 111 = Interr      | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | upt is priority 1                        | ablad          |                   |                 |                 |       |

| bit 3         |                   | upt source is disa<br>ented: Read as 'o  |                |                   |                 |                 |       |

| bit 2-0       | -                 |                                          |                | , bite            |                 |                 |       |

| DIL 2-0       |                   | External Interr<br>upt is priority 7 (I) |                |                   |                 |                 |       |

|               | •                 |                                          | gricot priori  | , monuply         |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •<br>001 - Interr | upt is priority 1                        |                |                   |                 |                 |       |

|               | <u> </u>          |                                          |                |                   |                 |                 |       |

| R/W-0                | U-0                    | U-0                    | U-0                    | U-0                         | U-0                    | U-0                | U-0        |

|----------------------|------------------------|------------------------|------------------------|-----------------------------|------------------------|--------------------|------------|

| FORCE <sup>(1)</sup> | —                      | —                      | -                      | —                           | —                      | —                  | —          |

| bit 15               |                        |                        |                        |                             |                        |                    | bit 8      |

|                      |                        |                        |                        |                             |                        |                    |            |

| U-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                       | R/W-0                  | R/W-0              | R/W-0      |

| —                    | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2)                  | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2)         | IRQSEL0(2) |

| bit 7                |                        |                        |                        |                             |                        |                    | bit 0      |

|                      |                        |                        |                        |                             |                        |                    |            |

| Legend:              |                        |                        |                        |                             |                        |                    |            |

| R = Readable         | bit                    | W = Writable bit       |                        | U = Unimplemented bit, read |                        | 1 as '0'           |            |

| -n = Value at F      | POR                    | '1' = Bit is set       |                        | '0' = Bit is cleared        |                        | x = Bit is unknown |            |

|                      |                        |                        |                        |                             |                        |                    |            |

| bit 15               | FORCE: Force           | e DMA Transfe          | er bit <sup>(1)</sup>  |                             |                        |                    |            |

|                      |                        | ingle DMA tran         | •                      | ,                           |                        |                    |            |

|                      |                        | DMA transfer           | -                      | MA request                  |                        |                    |            |

| bit 14-7             | Unimplemen             | ted: Read as '         | 0'                     |                             |                        |                    |            |

| bit 6-0              | IRQSEL<6:0>            | DMA Periph             | eral IRQ Numl          | ber Select bits             | (2)                    |                    |            |

|                      | 1111111 <b>= D</b>     | MAIRQ127 se            | lected to be C         | hannel DMARI                | EQ                     |                    |            |

|                      | •                      |                        |                        |                             |                        |                    |            |

|                      | •                      |                        |                        |                             |                        |                    |            |

|                      | •                      |                        |                        |                             |                        |                    |            |

|                      | 0000000 = DN           | MAIRQ0 select          | ed to be Chan          | nel DMAREQ                  |                        |                    |            |

|                      |                        |                        |                        |                             |                        |                    |            |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

- 2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

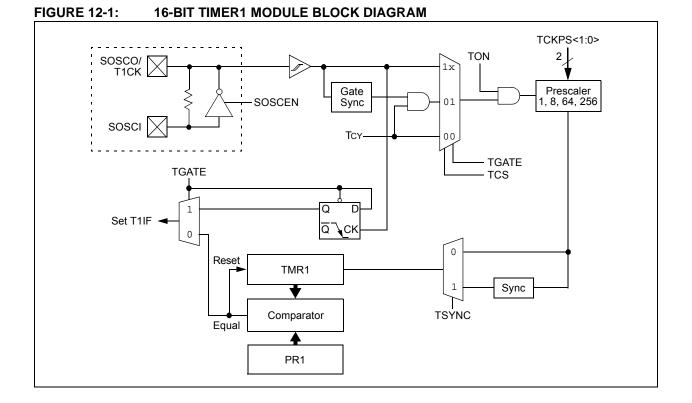

### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

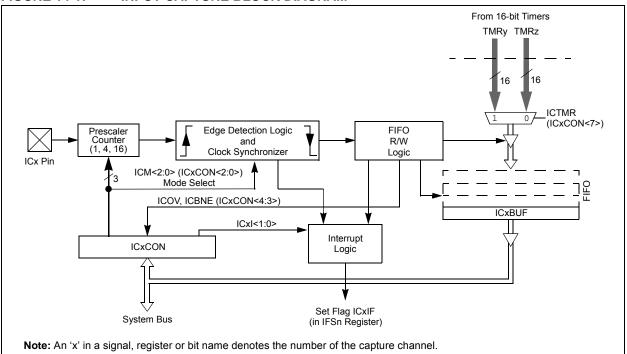

### 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJXXXGPX06A/X08A/X10A devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- · Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to 1 (ICI<1:0> = 00).

FIGURE 14-1: INPUT CAPTURE BLOCK DIAGRAM

## 17.2 <sup>2</sup>C Resources

Many useful resources related to  $I^2C$  are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en546064                                                       |

#### 17.2.1 KEY RESOURCES

- Section 11. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### 17.3 I<sup>2</sup>C Control Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0 HC | R/W-0                | R-0   | R-1   |

|----------|--------|----------|-----|----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK   | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15   |        |          |     |          |                      |       | bit 8 |

| R/W-0  | R/W-0   | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

|--------|---------|-------|-------|------|------|-------|-------|

| URXISE | EL<1:0> | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7  |         |       |       |      |      |       | bit 0 |

| Legend: HC = Hardware cleared |                  | C = Clear only bit    |                    |

|-------------------------------|------------------|-----------------------|--------------------|

| R = Readable bit              | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR             | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15.13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits 11 = Reserved; do not use 10 = Interrupt when a character is transferred to the Transmit Shift Register, and as a result, the transmit buffer becomes empty 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer) bit 14 UTXINV: Transmit Polarity Inversion bit If IREN = 0: 1 = UxTX Idle state is '0' 0 = UxTX Idle state is '1' If IREN = 1: 1 = IrDA<sup>®</sup> encoded UxTX Idle state is '1' 0 = IrDA<sup>®</sup> encoded UxTX Idle state is '0' bit 12 Unimplemented: Read as '0' bit 11 UTXBRK: Transmit Break bit 1 = Send Sync Break on next transmission - Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion 0 = Sync Break transmission disabled or completed UTXEN: Transmit Enable bit<sup>(1)</sup> bit 10 1 = Transmit enabled, UxTX pin controlled by UARTx 0 = Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled by port bit 9 UTXBF: Transmit Buffer Full Status bit (read-only) 1 = Transmit buffer is full 0 = Transmit buffer is not full, at least one more character can be written bit 8 **TRMT:** Transmit Shift Register Empty bit (read-only) 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit Shift Register is not empty, a transmission is in progress or queued bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bits 11 = Interrupt is set on UxRSR transfer making the receive buffer full (i.e., has 4 data characters) 10 = Interrupt is set on UxRSR transfer making the receive buffer 3/4 full (i.e., has 3 data characters) 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters

**Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

### **19.3 Modes of Operation**

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

### 19.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

### 19.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 19.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 19.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

#### REGISTER 19-12: CiBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                                      | R/W-0                                                                                                      | R/W-0                                      | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------|------------------|-----------------|-------|

|               | F3BF                                       | P<3:0>                                                                                                     |                                            |                   | F2BF             | P<3:0>          |       |

| bit 15        |                                            |                                                                                                            |                                            |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0                                      | R/W-0                                                                                                      | R/W-0                                      | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|               | F1BF                                       | P<3:0>                                                                                                     |                                            |                   | F0BF             | °<3:0>          |       |

| bit 7         |                                            |                                                                                                            |                                            |                   |                  |                 | bit ( |

| Legend:       |                                            |                                                                                                            |                                            |                   |                  |                 |       |

| R = Readable  | e bit                                      | W = Writable                                                                                               | bit                                        | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR                                        | '1' = Bit is set                                                                                           |                                            | '0' = Bit is clea | ared             | x = Bit is unkn | IOWN  |

| bit 15-12     | 1111 = Filte                               | : RX Buffer Writt<br>r hits received in<br>r hits received in                                              | RX FIFO bu                                 | ffer              |                  |                 |       |

| bit 11-8      | 0000 = Filte<br>F2BP<3:0>:<br>1111 = Filte | r hits received in<br>r hits received in<br>: RX Buffer Writte<br>r hits received in<br>r hits received in | RX Buffer 0<br>en when Filte<br>RX FIFO bu | ffer              |                  |                 |       |

|               | 0000 = Filte                               | r hits received in<br>r hits received in                                                                   | RX Buffer 0                                |                   |                  |                 |       |

| bit 7-4       | 1111 = Filte                               | RX Buffer Writte<br>r hits received in<br>r hits received in                                               | RX FIFO bu                                 | ffer              |                  |                 |       |

| bit 3-0       | 0000 = Filte<br>F0BP<3:0>:                 | r hits received in<br>r hits received in<br>RX Buffer Writte                                               | RX Buffer 0<br>en when Filte               |                   |                  |                 |       |

|               |                                            | r hits received in<br>r hits received in                                                                   |                                            | -                 |                  |                 |       |

|               |                                            | r hits received in<br>r hits received in                                                                   |                                            |                   |                  |                 |       |

Note: The buffers, SID, EID, DLC, Data Field and Receive Status registers are located in DMA RAM.

#### REGISTER 19-27: CITRBnSID: ECAN™ BUFFER n STANDARD IDENTIFIER (n = 0, 1, ..., 31)

|                                        | N-x   |

|----------------------------------------|-------|

|                                        |       |

|                                        | bit 8 |

| U-0 U-0 U-0 R/W-X R/W-X R/W-X R/W-X R/ |       |

|                                        | N-x   |

| SID<5:0> | SRR | IDE   |

|----------|-----|-------|

| bit 7    |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 12-2  | SID<10:0>: Standard Identifier bits                                                          |

| bit 1     | SRR: Substitute Remote Request bit                                                           |

|           | <ol> <li>1 = Message will request remote transmission</li> <li>0 = Normal message</li> </ol> |

| bit 0     | IDE: Extended Identifier bit                                                                 |

|           | 1 = Message will transmit extended identifier                                                |

0 = Message will transmit standard identifier

### REGISTER 19-28: CITRBnEID: ECAN™ BUFFER n EXTENDED IDENTIFIER (n = 0, 1, ..., 31)

| U-0             | U-0   | U-0              | U-0   | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                 | _     |                  |       |                                    | EID<  | 17:14>          |       |

| bit 15          |       |                  |       | ·                                  |       |                 | bit 8 |

|                 |       |                  |       |                                    |       |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                 |       |                  | EID   | <13:6>                             |       |                 |       |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |

|                 |       |                  |       |                                    |       |                 |       |

| Legend:         |       |                  |       |                                    |       |                 |       |

| R = Readable    | bit   | W = Writable I   | oit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

### 21.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, it is not intended to be a comprereference source. То hensive complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have up to 32 ADC input channels. These devices also have up to 2 ADC modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

**Note:** The ADC module needs to be disabled before modifying the AD12B bit.

### 21.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device.

A block diagram of the ADC is shown in Figure 21-1.

### 21.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>).

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>).

- Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>).

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>).

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>).

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>).

- g) Turn on ADC module (ADxCON1<15>).

- 2. Configure ADC interrupt (if required):

- a) Clear the ADxIF bit.

- b) Select ADC interrupt priority.

### 21.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

#### REGISTER 21-5: ADxCHS123: ADCx INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0                | U-0                                                                                                   | U-0                                                                                                                                     | U-0                                                                                                                                                  | U-0                                                                                                                                       | R/W-0                                                                                                  | R/W-0                                                    | R/W-0   |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------|--|--|--|

| _                  |                                                                                                       |                                                                                                                                         | —                                                                                                                                                    |                                                                                                                                           | CH123NB<1:0>                                                                                           |                                                          | CH123SB |  |  |  |

| bit 15             | ·                                                                                                     |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          | bit 8   |  |  |  |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| U-0                | U-0                                                                                                   | U-0                                                                                                                                     | U-0                                                                                                                                                  | U-0                                                                                                                                       | R/W-0                                                                                                  | R/W-0                                                    | R/W-0   |  |  |  |

| _                  | —                                                                                                     | _                                                                                                                                       |                                                                                                                                                      |                                                                                                                                           | CH123                                                                                                  | VA<1:0>                                                  | CH123SA |  |  |  |

| bit 7              |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          | bit C   |  |  |  |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| Legend:            |                                                                                                       |                                                                                                                                         | .,                                                                                                                                                   |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| R = Readable       |                                                                                                       | W = Writable b                                                                                                                          | it                                                                                                                                                   | U = Unimplen                                                                                                                              |                                                                                                        |                                                          |         |  |  |  |

| -n = Value at      | POR                                                                                                   | '1' = Bit is set                                                                                                                        |                                                                                                                                                      | '0' = Bit is clea                                                                                                                         | ared                                                                                                   | x = Bit is unk                                           | nown    |  |  |  |

|                    |                                                                                                       |                                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| bit 15-11          | •                                                                                                     | ted: Read as '0                                                                                                                         |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| bit 10-9           |                                                                                                       | 0>: Channel 1,                                                                                                                          | •                                                                                                                                                    | •                                                                                                                                         | •                                                                                                      | S                                                        |         |  |  |  |

|                    |                                                                                                       | /hen AD12B = 1, CHxNB is: U-0, Unimplemented, Read as '0'                                                                               |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

|                    |                                                                                                       | 11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11                                                  |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

|                    |                                                                                                       | ative input is Al                                                                                                                       |                                                                                                                                                      |                                                                                                                                           | N7, CH3 negat                                                                                          | ive input is AN                                          | 8       |  |  |  |

|                    |                                                                                                       | I2, CH3 negativ                                                                                                                         | •                                                                                                                                                    |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| bit 8              |                                                                                                       | nannel 1, 2, 3 P                                                                                                                        | -                                                                                                                                                    | -                                                                                                                                         |                                                                                                        |                                                          |         |  |  |  |

|                    |                                                                                                       | = 1, CHxSB is                                                                                                                           |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

|                    |                                                                                                       | ive input is AN3                                                                                                                        | , CH2 positive                                                                                                                                       |                                                                                                                                           | CH3 positive                                                                                           | nout is AN5                                              |         |  |  |  |

|                    | 0 = CH1 posit                                                                                         | iva input is ANC                                                                                                                        |                                                                                                                                                      |                                                                                                                                           |                                                                                                        |                                                          |         |  |  |  |

| hit 7-3            | •                                                                                                     | •                                                                                                                                       | , CH2 positive                                                                                                                                       | e input is AN4,<br>e input is AN1,                                                                                                        |                                                                                                        |                                                          |         |  |  |  |

| bit 7-3<br>bit 2-1 | Unimplemen                                                                                            | ted: Read as '0                                                                                                                         | , CH2 positive                                                                                                                                       | e input is AN1,                                                                                                                           | CH3 positive                                                                                           | nput is AN2                                              |         |  |  |  |

| bit 7-3<br>bit 2-1 | Unimplemen<br>CH123NA<1:                                                                              | ted: Read as '0<br>0>: Channel 1,                                                                                                       | , CH2 positive<br>2, 3 Negative                                                                                                                      | e input is AN1,<br>Input Select fo                                                                                                        | CH3 positive                                                                                           | nput is AN2                                              |         |  |  |  |

|                    | Unimplemen<br>CH123NA<1:<br>When AD12E                                                                | ted: Read as '0<br>0>: Channel 1,<br>5 = 1, CHxNA is                                                                                    | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b>                                                                                              | e input is AN1,<br>Input Select fo<br>Iemented, Rea                                                                                       | CH3 positive<br>r Sample A bi<br>ad as '0'                                                             | nput is AN2                                              | N11     |  |  |  |

|                    | Unimplemen<br>CH123NA<1:<br>When AD12E<br>11 = CH1 neg                                                | ted: Read as '0<br>0>: Channel 1,<br>3 = 1, CHxNA is<br>jative input is Al                                                              | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b><br>N9, CH2 nega                                                                              | e input is AN1,<br>Input Select fo<br>Ilemented, Rea<br>ative input is AN                                                                 | CH3 positive<br>r Sample A bi<br>ad as '0'<br>N10, CH3 nega                                            | nput is AN2<br>is<br>ative input is A                    |         |  |  |  |

|                    | Unimplemen<br>CH123NA<1:<br>When AD12E<br>11 = CH1 neg<br>10 = CH1 neg                                | ted: Read as '0<br>0>: Channel 1,<br>5 = 1, CHxNA is                                                                                    | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b><br>N9, CH2 nega<br>N6, CH2 nega                                                              | e input is AN1,<br>Input Select fo<br>Iemented, Rea<br>ative input is AN<br>ative input is AN                                             | CH3 positive<br>r Sample A bi<br>ad as '0'<br>N10, CH3 nega                                            | nput is AN2<br>is<br>ative input is A                    |         |  |  |  |

|                    | Unimplemen<br>CH123NA<1:<br>When AD12E<br>11 = CH1 neg<br>10 = CH1 neg<br>0x = CH1, CH                | <b>ted:</b> Read as '0<br><b>0&gt;:</b> Channel 1,<br><b>b = 1, CHxNA is</b><br>pative input is Al<br>pative input is Al                | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b><br>N9, CH2 nega<br>N6, CH2 nega<br>e input is VRE                                            | e input is AN1,<br>Input Select fo<br>Ilemented, Rea<br>ative input is AN<br>ative input is AN<br>F-                                      | CH3 positive<br>r Sample A bi<br>ad as '0'<br>N10, CH3 nega<br>N7, CH3 negat                           | nput is AN2<br>is<br>ative input is A                    |         |  |  |  |

| bit 2-1            | Unimplemen<br>CH123NA<1:<br>When AD12E<br>11 = CH1 neg<br>10 = CH1 neg<br>0x = CH1, CH<br>CH123SA: Ch | ted: Read as '0<br>0>: Channel 1,<br>B = 1, CHxNA is<br>pative input is Al<br>pative input is Al<br>12, CH3 negativ                     | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b><br>N9, CH2 nega<br>N6, CH2 nega<br>e input is VRE<br>psitive Input S                         | e input is AN1,<br>Input Select fo<br>Ilemented, Rea<br>ative input is AN<br>ative input is AN<br>F-<br>Select for Samp                   | CH3 positive<br>r Sample A bi<br>ad as '0'<br>N10, CH3 nega<br>N7, CH3 negat                           | nput is AN2<br>is<br>ative input is A                    |         |  |  |  |

| bit 2-1            | Unimplemen<br>CH123NA<1:<br>When AD12E<br>11 = CH1 neg<br>0x = CH1 neg<br>0x = CH1, CH<br>CH123SA: CH | ted: Read as '0<br>0>: Channel 1,<br>3 = 1, CHxNA is<br>pative input is Al<br>pative input is Al<br>12, CH3 negativ<br>nannel 1, 2, 3 P | , CH2 positive<br>2, 3 Negative<br><b>:: U-0, Unimp</b><br>N9, CH2 nega<br>N6, CH2 nega<br>e input is VRE<br>psitive Input S<br><b>:: U-0, Unimp</b> | e input is AN1,<br>Input Select fo<br>Ilemented, Rea<br>ative input is AN<br>ative input is AN<br>F-<br>Select for Samp<br>Ilemented, Rea | CH3 positive<br>r Sample A bi<br>ad as '0'<br>N10, CH3 nega<br>N7, CH3 negat<br>ble A bit<br>ad as '0' | nput is AN2<br>is<br>ative input is A<br>ive input is AN |         |  |  |  |

#### 24.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 24.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 24.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 24.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 24.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |                    |         |       |                                                           |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|---------|-------|-----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                          | Min.      | Typ <sup>(1)</sup> | Max.    | Units | Conditions                                                |

|                    | -      | Cloc                                                                                                                                                                                                                                                                                    | k Parame  | ters               |         |       | ·                                                         |

| AD50b              | TAD    | ADC Clock Period                                                                                                                                                                                                                                                                        | 76        |                    | _       | ns    | —                                                         |

| AD51b              | TRC    | ADC Internal RC Oscillator Period                                                                                                                                                                                                                                                       | _         | 250                | _       | ns    | —                                                         |

|                    |        | Con                                                                                                                                                                                                                                                                                     | version F | late               |         |       |                                                           |