Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

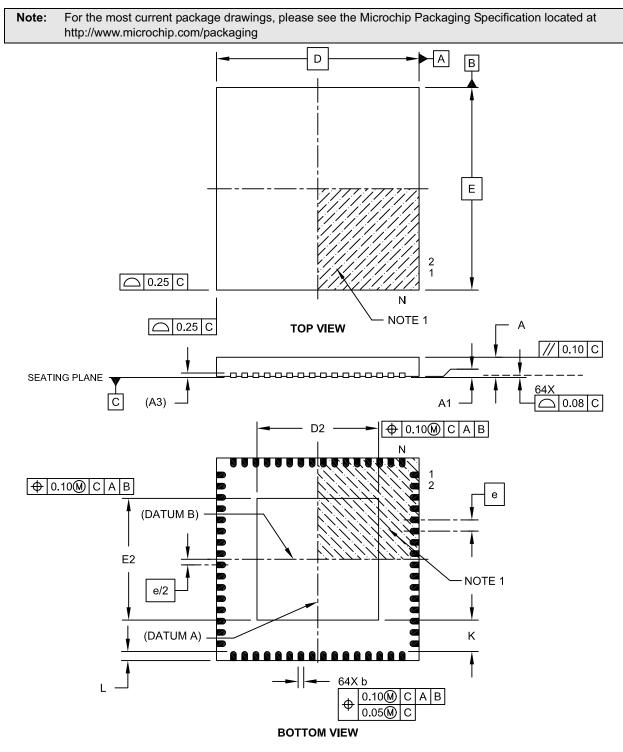

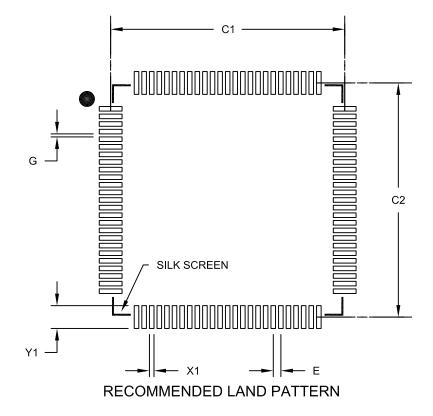

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp710a-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206A

- dsPIC33FJ64GP306A

- dsPIC33FJ64GP310A

- dsPIC33FJ64GP706A

- dsPIC33FJ64GP708A

- dsPIC33FJ64GP710A

- dsPIC33FJ128GP206A

- dsPIC33FJ128GP306A

- dsPIC33FJ128GP310A

- dsPIC33FJ128GP706A

- dsPIC33FJ128GP708A

- dsPIC33FJ128GP710A

- dsPIC33FJ256GP506A

- dsPIC33FJ256GP510A

- dsPIC33FJ256GP710A

The dsPIC33FJXXXGPX06A/X08A/X10A General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes).

This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXGPX06A/X08A/X10A device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06A/X08A/X10A Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXGPX06A/X08A/X10A devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06A/X08A/X10A devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

### 4.2 Data Address Space

The dsPIC33FJXXXGPX06A/X08A/X10A CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXGPX06A/X08A/X10A devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJXXXGPX06A/X08A/X10A instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXGPX06A/X08A/X10A core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-34.

| Note: | The actual set of peripheral features and interrupts varies by the device. Please   |

|-------|-------------------------------------------------------------------------------------|

|       | refer to the corresponding device tables<br>and pinout diagrams for device-specific |

|       | information.                                                                        |

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

### TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

|          | •••••       |        |        |        | <b>\</b> - | -      | - /    |       |         |                  |           |          |       |       |        |        |        |               |

|----------|-------------|--------|--------|--------|------------|--------|--------|-------|---------|------------------|-----------|----------|-------|-------|--------|--------|--------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7            | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| XBREV    | 0050        | BREN   |        |        |            |        |        |       | )       | <b>(</b> B<14:0> |           |          |       |       |        |        |        | xxxx          |

| DISICNT  | 0052        | —      | —      |        |            |        |        |       | Disable | e Interrupts     | Counter R | legister |       |       |        |        |        | xxxx          |

| BSRAM    | 0750        | —      | —      | _      | —          |        | _      | _     | _       | —                | _         | -        | —     | —     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM    | 0752        | —      | —      | —      | _          | —      | —      | —     | —       | _                |           | —        |       | _     | IW_SSR | IR_SSR | RL_SSR | 0000          |

| 1        |             |        |        |        |            |        | .1 .1  |       |         |                  |           |          |       |       |        |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-1  | 8: E | ECAN1 F | REGIST            | ER MAP     | WHEN    | C1CTR   | L1.WIN :   | = 0 OR    | 1 FOR   | dsPIC33F | -JXXXC   | SP506A | /51A0/7           | 706A/70   | BA/710/  | A DEV    | CES (  | ONLY          |

|------------|------|---------|-------------------|------------|---------|---------|------------|-----------|---------|----------|----------|--------|-------------------|-----------|----------|----------|--------|---------------|

| File Name  | Addr | Bit 15  | Bit 14            | Bit 13     | Bit 12  | Bit 11  | Bit 10     | Bit 9     | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4             | Bit 3     | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400 | —       | —                 | CSIDL      | ABAT    | -       | R          | EQOP<2:0  | >       | OPI      | MODE<2:0 | >      | —                 | CANCAP    | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402 | _       | _                 | _          | _       | _       | _          | _         | _       | _        | _        | _      |                   | DN        | CNT<4:0> |          |        | 0000          |

| C1VEC      | 0404 | _       | _                 | _          |         | F       | ILHIT<4:0> |           |         | _        |          |        | IC                | CODE<6:0> |          |          |        | 0000          |

| C1FCTRL    | 0406 | C       | MABS<2:0          | <<br>      | —       | -       | —          | _         | -       | _        | —        | —      |                   | F         | SA<4:0>  |          |        | 0000          |

| C1FIFO     | 0408 | _       | _                 |            |         | FBP<    | 5:0>       |           |         | _        | —        |        |                   | FNRB<     | 5:0>     |          |        | 0000          |

| C1INTF     | 040A | _       | _                 | ТХВО       | TXBP    | RXBP    | TXWAR      | RXWAR     | EWARN   | IVRIF    | WAKIF    | ERRIF  | _                 | FIFOIF    | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C | —       | —                 | —          | —       |         | —          | —         | —       | IVRIE    | WAKIE    | ERRIE  | —                 | FIFOIE    | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E |         |                   |            | TERRC   | NT<7:0> |            |           |         |          |          |        | RERRCNT           | [<7:0>    |          |          |        | 0000          |

| C1CFG1     | 0410 | —       | —                 | —          | —       |         | —          | —         | —       | SJW<     | 1:0>     |        |                   | BRP<5     | :0>      |          |        | 0000          |

| C1CFG2     | 0412 | —       | WAKFIL            | —          | —       |         | SE         | EG2PH<2:( | )>      | SEG2PHTS | SAM      | S      | EG1PH<2:          | :0>       | PF       | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414 | FLTEN15 | FLTEN14           | FLTEN13    | FLTEN12 | FLTEN11 | FLTEN10    | FLTEN9    | FLTEN8  | FLTEN7   | FLTEN6   | FLTEN5 | FLTEN4            | FLTEN3    | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418 | F7MSł   | <b>&lt;</b> <1:0> | F6MSł      | <1:0>   | F5MS    | K<1:0>     | F4MS      | K<1:0>  | F3MSK    | <1:0>    | F2MSI  | <b>&lt;</b> <1:0> | F1MSK     | <1:0>    | F0MSI    | <1:0>  | 0000          |

| C1FMSKSEL2 | 041A | F15MS   | K<1:0>            | F14MS      | K<1:0>  | F13MS   | SK<1:0>    | F12MS     | SK<1:0> | F11MSK   | <1:0>    | F10MS  | K<1:0>            | F9MSK     | <1:0>    | F8MSł    | <1:0>  | 0000          |

| Laward     |      |         |                   | Desetualus |         |         |            |           |         |          |          |        |                   |           |          |          |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-19: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 FOR dsPIC33FJXXXGP506A/510A/706A/708A/710A DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8      | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|---------|---------|---------|---------|---------|---------|------------|-----------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |         |         |         |         |         | See     | definition | when WIN  | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7    | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23   | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8     | RXOVF7    | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23   | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>    | TXEN0     | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>    | TXEN2     | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>    | TXEN4     | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>    | TXEN6     | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |         |         |         |         |         |         |         | Received [ | Data Word |         |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |         |         |         |         |         |         | Transmit E | Data Word |         |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: DCI REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7     | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0  | Reset State         |

|-------------|-------|--------|--------|---------|--------|--------|--------|------------|-------------|-----------|--------|-------|-------|-------|-------|---------|--------|---------------------|

| DCICON1     | 0280  | DCIEN  | —      | DCISIDL | —      | DLOOP  | CSCKD  | CSCKE      | COFSD       | UNFM      | CSDOM  | DJST  |       |       | —     | COFSM1  | COFSM0 | 0000 0000 0000 0000 |

| DCICON2     | 0282  | _      | _      | _       | _      | BLEN1  | BLEN0  | _          |             | COFSO     | G<3:0> |       | -     |       | V     | VS<3:0> |        | 0000 0000 0000 0000 |

| DCICON3     | 0284  | _      | _      | _       | _      |        |        |            |             |           | BCG<1  | 1:0>  |       |       |       |         |        | 0000 0000 0000 0000 |

| DCISTAT     | 0286  | _      | _      | _       | _      | SLOT3  | SLOT2  | SLOT1      | SLOT0       |           | _      | -     | -     | ROV   | RFUL  | TUNF    | TMPTY  | 0000 0000 0000 0000 |

| TSCON       | 0288  | TSE15  | TSE14  | TSE13   | TSE12  | TSE11  | TSE10  | TSE9       | TSE8        | TSE7      | TSE6   | TSE5  | TSE4  | TSE3  | TSE2  | TSE1    | TSE0   | 0000 0000 0000 0000 |

| RSCON       | 028C  | RSE15  | RSE14  | RSE13   | RSE12  | RSE11  | RSE10  | RSE9       | RSE8        | RSE7      | RSE6   | RSE5  | RSE4  | RSE3  | RSE2  | RSE1    | RSE0   | 0000 0000 0000 0000 |

| RXBUF0      | 0290  |        |        |         |        |        |        | Receive E  | Buffer #0 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF1      | 0292  |        |        |         |        |        |        | Receive E  | Buffer #1 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF2      | 0294  |        |        |         |        |        |        | Receive E  | Buffer #2 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF3      | 0296  |        |        |         |        |        |        | Receive E  | Buffer #3 D | ata Regis | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF0      | 0298  |        |        |         |        |        |        | Transmit I | Buffer #0 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF1      | 029A  |        |        |         |        |        |        | Transmit I | Buffer #1 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF2      | 029C  |        |        |         |        |        |        | Transmit I | Buffer #2 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF3      | 029E  |        |        |         |        |        |        | Transmit I | Buffer #3 D | ata Regi  | ster   |       |       |       |       |         |        | 0000 0000 0000 0000 |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend:

— = unimplemented, read as '0'. Refer to the *"dsPIC33F/PIC24H Family Reference Manual"* for descriptions of register bit fields. Note 1:

### TABLE 4-25: PORTA REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA               | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | _      | TRISA10 | TRISA9 |       | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA               | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA                | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA <sup>(2)</sup> | 06C0 | ODCA15  | ODCA14  | _       | _       | _      | _       | _      |       | _      |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices. Legend:

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-26: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | XXXX          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

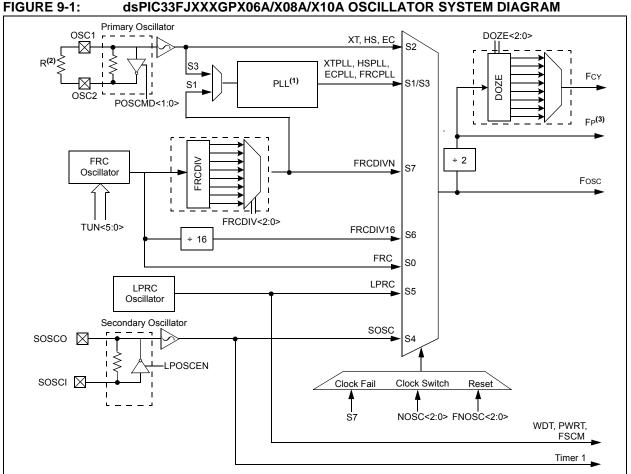

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A family of devices. However, not intended to it is be а comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

A simplified diagram of the oscillator system is shown in Figure 9-1.

Note 1: See Figure 9-2 for PLL details.

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 M $\Omega$  must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while Fcy refers to the clock source for the CPU. Throughout this document FP and Fcy are used interchangeably, except in the case of Doze mode. FP and Fcy will be different when Doze mode is used in any ratio other than 1:1, which is the default.

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0        | R-0                  | R-0                                     | R-0              | U-0                    | R/W-y           | R/W-y            | R/W-y          |

|------------|----------------------|-----------------------------------------|------------------|------------------------|-----------------|------------------|----------------|

| _          |                      | COSC<2:0>                               |                  |                        |                 | NOSC<2:0>(2)     |                |

| bit 15     |                      |                                         |                  |                        |                 |                  | bit 8          |

|            |                      |                                         |                  |                        |                 |                  |                |

| R/W-0      | U-0                  | R-0                                     | U-0              | R/C-0                  | U-0             | R/W-0            | R/W-0          |

| CLKLOC     | СК —                 | LOCK                                    | _                | CF                     |                 | LPOSCEN          | OSWEN          |

| bit 7      |                      |                                         |                  |                        |                 |                  | bit 0          |

| Legend:    |                      | y = Value set                           | from Configur    | ation bits on P        | POR             | C = Clea         | r only bit     |

| R = Reada  | able bit             | W = Writable                            | bit              | U = Unimplei           | mented bit, rea | d as '0'         |                |

| -n = Value | at POR               | '1' = Bit is set                        |                  | '0' = Bit is cle       | eared           | x = Bit is unkn  | own            |

| bit 15     | Unimplemer           | nted: Read as '                         | )'               |                        |                 |                  |                |

| bit 14-12  | COSC<2:0>:           | Current Oscilla                         | tor Selection    | bits (read-only        | ()              |                  |                |

|            |                      | C oscillator (FF                        |                  |                        |                 |                  |                |

|            |                      | C oscillator (FF                        |                  |                        |                 |                  |                |

|            |                      | ower RC oscilla                         | ,                | 5                      |                 |                  |                |

|            | 100 <b>= Secon</b>   | dary oscillator (                       | Sosc)            |                        |                 |                  |                |

|            |                      | ry oscillator (XT,                      |                  | I PLL                  |                 |                  |                |

|            |                      | y oscillator (XT,                       |                  |                        |                 |                  |                |

|            |                      | C Oscillator (FF                        |                  | e-by-N and PL          | L (FRCDIVN +    | FPLL)            |                |

| .:. 11     |                      | C oscillator (FF                        | •                |                        |                 |                  |                |

| oit 11     | -                    | nted: Read as '                         |                  | (2)                    |                 |                  |                |

| oit 10-8   |                      | New Oscillator                          |                  |                        |                 |                  |                |

|            |                      | C oscillator (FF<br>C oscillator (FF    |                  |                        |                 |                  |                |

|            |                      | ower RC oscilla                         |                  | e-by-10                |                 |                  |                |

|            |                      | dary oscillator (                       |                  |                        |                 |                  |                |

|            |                      | ry oscillator (XT,                      |                  | I PLL                  |                 |                  |                |

|            |                      | y oscillator (XT,                       |                  |                        |                 |                  |                |

|            | 001 <b>= Fast R</b>  | C Oscillator (FF                        | RC) with Divid   | e-by-N and PL          | L (FRCDIVN +    | ⊦ PLL)           |                |

|            |                      | C oscillator (FF                        | ,                |                        |                 |                  |                |

| bit 7      |                      | Clock Lock Enal                         |                  |                        |                 |                  |                |

|            |                      | M0 = 1), then c                         |                  |                        |                 |                  |                |

|            |                      | M0 = 0), then c                         |                  |                        |                 |                  |                |

|            |                      | Id PLL selection                        |                  | ked, configurat        | ions may be m   | odified          |                |

| bit 6      | -                    | nted: Read as '                         |                  |                        |                 |                  |                |

| bit 5      |                      | ₋ock Status bit (<br>s that PLL is in I | 3,               | lart un timor in       | eatiefied       |                  |                |

|            |                      | s that PLL is in i                      |                  |                        |                 | l is disabled    |                |

| bit 4      |                      | nted: Read as '                         |                  |                        |                 |                  |                |

| bit 3      |                      | ail Detect bit (rea                     |                  | plication)             |                 |                  |                |

|            |                      | as detected clo                         |                  |                        |                 |                  |                |

|            |                      | as not detected                         |                  |                        |                 |                  |                |

| bit 2      | Unimplemer           | nted: Read as '                         | )'               |                        |                 |                  |                |

| Note 1:    | Writes to this regis | ster require an u                       | Inlock sequer    | ice. Refer to <b>S</b> | ection 7. "Oso  | cillator" (DS701 | 86) in the     |

|            | "dsPIC33F/PIC24      |                                         |                  |                        |                 |                  | , -            |

| 2:         | Direct clock switch  | nes between any                         | / primary osci   | llator mode wit        | th PLL and FRO  | CPLL mode are r  | not permitted. |

|            | This applies to clo  | ck switches in e                        | either direction | n. In these inst       | ances, the app  |                  |                |

|            | mode as a transiti   | on clock source                         | between the      | two PLL mode           | es.             |                  |                |

| _          |                      |                                         |                  |                        |                 |                  |                |

3: This is register is reset only on a Power-on Reset (POR).

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

### bit 0 OSWEN: Oscillator Switch Enable bit

bit 1

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: This is register is reset only on a Power-on Reset (POR).

| U-0          | U-0                                                                                                         | U-0                                                              | U-0   | U-0              | U-0             | U-0            | R/W-0 <sup>(1)</sup> |

|--------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------------------|-----------------|----------------|----------------------|

|              | _                                                                                                           |                                                                  | _     | _                | _               | _              | PLLDIV<8>            |

| bit 15       | ·                                                                                                           | ·                                                                | ·     | •                | •               | •              | bit 8                |

| R/W-0        | R/W-0                                                                                                       | R/W-1                                                            | R/W-1 | R/W-0            | R/W-0           | R/W-0          | R/W-0                |

| R/W-U        | R/W-0                                                                                                       | R/ W- I                                                          |       | IV<7:0>          | R/W-0           | R/ W-U         | R/W-0                |

| bit 7        |                                                                                                             |                                                                  | FLLD  | 10~7.02          |                 |                | bit 0                |

|              |                                                                                                             |                                                                  |       |                  |                 |                | DILU                 |

| Legend:      |                                                                                                             |                                                                  |       |                  |                 |                |                      |

| R = Readab   | le bit                                                                                                      | W = Writable                                                     | bit   | U = Unimple      | mented bit, rea | d as '0'       |                      |

|              |                                                                                                             |                                                                  |       |                  |                 |                |                      |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | ared            | x = Bit is unl | known                |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                                 | t     | '0' = Bit is cle | eared           | x = Bit is unl | known                |

| -n = Value a |                                                                                                             | '1' = Bit is set                                                 | -     | ʻ0' = Bit is cle | ared            | x = Bit is unl | known                |

|              | Unimpleme                                                                                                   |                                                                  | ʻ0'   |                  |                 |                | known                |

| bit 15-9     | Unimpleme                                                                                                   | nted: Read as '                                                  | ʻ0'   |                  |                 |                | known                |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                | known                |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                | (nown                |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0                                                                                    | nted: Read as '                                                  | ʻ0'   |                  |                 |                | (nown                |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as '                                                  | ʻ0'   |                  |                 |                | (nown                |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                | <u>known</u>         |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                | <u>known</u>         |

| bit 15-9     | Unimplemei<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513                          | ʻ0'   |                  |                 |                | <u>Known</u>         |

| bit 15-9     | Unimplemer<br>PLLDIV<8:0<br>111111111<br>•<br>•                                                             | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)        | ʻ0'   |                  |                 |                | <u>Known</u>         |

| bit 15-9     | Unimplemen<br>PLLDIV<8:0<br>111111111<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nted: Read as<br>>: PLL Feedba<br>= 513<br>= 50 (default)<br>= 4 | ʻ0'   |                  |                 |                | <u>Known</u>         |

Note 1: This is register is reset only on a Power-on Reset (POR).

### 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, dsPIC33FJXXXGPX06A/X08A/X10A devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 22.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and CF (OSCCON<3>) are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRC-PLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

### 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2009-2012</sup> Microchip Technology Inc.

### REGISTER 19-18: CiFMSKSEL1: ECAN™ FILTER 7-0 MASK SELECTION REGISTER

| R/W-0           | R/W-0        | R/W-0                                                | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W               | /-0   |

|-----------------|--------------|------------------------------------------------------|-------------------|-------------------|------------------|-----------------|-------------------|-------|

| F7MS            | K<1:0>       | F6MSł                                                | <<1:0>            | F5MS              | K<1:0>           | F4MSł           | <b>&lt;</b> <1:0> |       |

| bit 15          |              |                                                      |                   |                   |                  |                 |                   | bit 8 |

|                 |              |                                                      |                   |                   |                  |                 |                   |       |

| R/W-0           | R/W-0        | R/W-0                                                | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W               | /-0   |

| F3MS            | K<1:0>       | F2MSł                                                | <<1:0>            | F1MS              | K<1:0>           | FOMS            | <<1:0>            |       |

| bit 7           |              |                                                      |                   |                   |                  |                 |                   | bit 0 |

| Legend:         |              |                                                      |                   |                   |                  |                 |                   |       |

| R = Readable    | bit          | W = Writable                                         | bit               | U = Unimplen      | nented bit, read | d as '0'        |                   |       |

| -n = Value at I | POR          | '1' = Bit is set                                     |                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown              |       |

|                 |              |                                                      |                   |                   |                  |                 |                   |       |

| bit 15-14       |              | : Mask Source                                        | e for Filter 7 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use<br>ince Mask 2 reg                    | nistore contain   | mask              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg                                      |                   |                   |                  |                 |                   |       |

|                 |              | nce Mask 0 reg                                       | -                 |                   |                  |                 |                   |       |

| bit 13-12       |              | : Mask Source                                        | e for Filter 6 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | maak              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   |                   |                   |                  |                 |                   |       |

|                 |              | ince Mask 0 reg                                      |                   |                   |                  |                 |                   |       |

| bit 11-10       |              | : Mask Source                                        | e for Filter 5 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | mook              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   | -                 |                   |                  |                 |                   |       |

|                 | •            | ince Mask 0 reg                                      | -                 |                   |                  |                 |                   |       |

| bit 9-8         |              | : Mask Source                                        | e for Filter 4 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | mook              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   |                   |                   |                  |                 |                   |       |

|                 |              | ince Mask 0 reg                                      | •                 |                   |                  |                 |                   |       |

| bit 7-6         |              | : Mask Source                                        | e for Filter 3 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | mook              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   |                   |                   |                  |                 |                   |       |

|                 |              | ince Mask 0 reg                                      |                   |                   |                  |                 |                   |       |

| bit 5-4         |              | : Mask Source                                        | e for Filter 2 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | mook              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   | -                 |                   |                  |                 |                   |       |

|                 |              | ince Mask 0 reg                                      |                   |                   |                  |                 |                   |       |

| bit 3-2         |              | ·: Mask Source                                       | e for Filter 1 bi | t                 |                  |                 |                   |       |

|                 |              | ed; do not use                                       | niatoro contain   | maak              |                  |                 |                   |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg                   | -                 |                   |                  |                 |                   |       |

|                 |              | ince Mask 0 reg                                      | -                 |                   |                  |                 |                   |       |

| bit 1-0         | F0MSK<1:0>   | : Mask Source                                        | e for Filter 0 bi | t                 |                  |                 |                   |       |

|                 | _            |                                                      |                   |                   |                  |                 |                   |       |

| DIL 1-0         |              | ed; do not use                                       |                   |                   |                  |                 |                   |       |

| Dit 1-0         | 10 = Accepta | ed; do not use<br>ince Mask 2 reg<br>ince Mask 1 reg | -                 |                   |                  |                 |                   |       |

| R/W-x         | R/W-x        | R/W-x                                                        | R/W-x          | R/W-x            | R/W-x              | R/W-x           | R/W-x            |

|---------------|--------------|--------------------------------------------------------------|----------------|------------------|--------------------|-----------------|------------------|

|               |              |                                                              | SID            | <10:3>           |                    |                 |                  |

| bit 15        |              |                                                              |                |                  |                    |                 | bit 8            |

|               |              |                                                              |                |                  |                    |                 |                  |

| R/W-x         | R/W-x        | R/W-x                                                        | U-0            | R/W-x            | U-0                | R/W-x           | R/W-x            |

|               | SID<2:0>     |                                                              |                | MIDE             |                    | EID<1           | 7:16>            |

| bit 7         |              |                                                              |                |                  |                    |                 | bit C            |

| Legend:       |              |                                                              |                |                  |                    |                 |                  |

| R = Readable  | e bit        | W = Writable t                                               | oit            | U = Unimpler     | mented bit, read   | d as '0'        |                  |

| -n = Value at | POR          | '1' = Bit is set                                             |                | '0' = Bit is cle | ared               | x = Bit is unkr | nown             |

|               |              |                                                              |                |                  |                    |                 |                  |

| bit 15-5      | SID<10:0>:   | Standard Identif                                             | ier bits       |                  |                    |                 |                  |

|               | 1 = Include  | bit SIDx in filter c                                         | omparison      |                  |                    |                 |                  |

|               | 0 = Bit SIDx | is don't care in fi                                          | ilter comparis | son              |                    |                 |                  |

| bit 4         | Unimpleme    | nted: Read as '0                                             | )'             |                  |                    |                 |                  |

| bit 3         | MIDE: Iden   | tifier Receive Mo                                            | de bit         |                  |                    |                 |                  |

|               | 0 = Match e  | only message typ<br>either standard or<br>(Filter SID) = (Me | extended a     | ddress messag    | e if filters match | י.<br>ו         | DE bit in filter |

| bit 2         | Unimpleme    | nted: Read as 'o                                             | )'             |                  |                    |                 |                  |

| bit 1-0       | EID<17:16>   | : Extended Ident                                             | ifier bits     |                  |                    |                 |                  |

|               | 1 = Include  | bit EIDx in filter of                                        | comparison     |                  |                    |                 |                  |

### REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |                  | EID   | <15:8>                             |       |                 |       |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                                   |       |                  | EID   | )<7:0>                             |       |                 |       |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

### 22.0 SPECIAL FEATURES

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section "CodeGuard™ 23. Security" (DS70199), Section 24. "Programming and Diagnostics" (DS70207), and Section 25. "Device Configuration" (DS70194) in the "dsPIC33F/PIC24H Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJXXXGPX06A/X08A/X10A devices include the following features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

#### Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 0xF80000 FBS RBS<1:0> BSS<2:0> BWRP SWRP 0xF80002 FSS RSS<1:0> SSS<2:0> 0xF80004 FGS GSS1 GSS0 GWRP Reserved<sup>(2)</sup> FNOSC<2:0> 0xF80006 FOSCSEL **IESO** OSCIOFNC POSCMD<1:0> 0xF80008 FOSC FCKSM<1:0> 0xF8000A FWDT FWDTEN WINDIS PLLKEN<sup>(3)</sup> WDTPRE WDTPOST<3:0> 0xF8000C FPOR Reserved<sup>(4)</sup> FPWRT<2:0> Reserved<sup>(1)</sup> 0xF8000E FICD **JTAGEN** ICS<1:0> 0xF80010 FUID0 User Unit ID Byte 0 0xF80012 FUID1 User Unit ID Byte 1 0xF80014 FUID2 User Unit ID Byte 2 0xF80016 FUID3 User Unit ID Byte 3

### TABLE 22-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed as '1'.

- 2: When read, this bit returns the current programmed value.

- **3:** This bit is unimplemented on dsPIC33FJ64GPX06A/X08A/X10A and dsPIC33FJ128GPX06A/X08A/X10A devices and reads as '0'.

- 4: These bits are reserved and always read as '1'.

### 22.1 Configuration Bits

dsPIC33FJXXXGPX06A/X08A/X10A devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25.** "**Device Configuration**" (DS70194) of the "*dsPIC33F/PIC24H Family Reference Manual*", for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The device Configuration register map is shown in Table 22-1.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 22-2.

Note that address 0xF80000 is beyond the user program memory space. In fact, it belongs to the configuration memory space (0x800000-0xFFFFF) which can only be accessed using table reads and table writes.

### 24.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 24.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 24.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHARACT                      | ERISTICS               |            | (unless othe | dard Operating Conditions: 3.0V to 3.6V<br>ss otherwise stated)<br>ating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |           |  |  |

|---------------------------------|------------------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup> | Max        | Units        | Conditions                                                                                                                                                                                         |        |           |  |  |

| Idle Current (I                 | DLE): Core OF          | F Clock ON | Base Curren  | t <sup>(1)</sup>                                                                                                                                                                                   |        |           |  |  |

| DC40d                           | 3                      | 25         | mA           | -40°C                                                                                                                                                                                              |        |           |  |  |

| DC40a                           | 3                      | 25         | mA           | +25°C                                                                                                                                                                                              |        | 10 MIPS   |  |  |

| DC40b                           | 3                      | 25         | mA           | +85°C                                                                                                                                                                                              | 3.3∨   | TO MIPS   |  |  |

| DC40c                           | 3                      | 25         | mA           | +125°C                                                                                                                                                                                             |        |           |  |  |

| DC41d                           | 4                      | 25         | mA           | -40°C                                                                                                                                                                                              |        | 16 MIPS   |  |  |

| DC41a                           | 5                      | 25         | mA           | +25°C                                                                                                                                                                                              | - 3.3V |           |  |  |

| DC41b                           | 6                      | 25         | mA           | +85°C                                                                                                                                                                                              |        | 10 1011-5 |  |  |

| DC41c                           | 6                      | 25         | mA           | +125°C                                                                                                                                                                                             |        |           |  |  |

| DC42d                           | 8                      | 25         | mA           | -40°C                                                                                                                                                                                              |        | 20 MIPS   |  |  |

| DC42a                           | 9                      | 25         | mA           | +25°C                                                                                                                                                                                              | 3.3V   |           |  |  |

| DC42b                           | 10                     | 25         | mA           | +85°C                                                                                                                                                                                              | 3.3V   |           |  |  |

| DC42c                           | 10                     | 25         | mA           | +125°C                                                                                                                                                                                             |        |           |  |  |

| DC43a                           | 15                     | 25         | mA           | +25°C                                                                                                                                                                                              |        |           |  |  |

| DC43d                           | 15                     | 25         | mA           | -40°C                                                                                                                                                                                              | 3.3V   | 30 MIPS   |  |  |

| DC43b                           | 15                     | 25         | mA           | +85°C                                                                                                                                                                                              | 3.3V   | 30 MIPS   |  |  |

| DC43c                           | 15                     | 25         | mA           | +125°C                                                                                                                                                                                             |        |           |  |  |

| DC44d                           | 16                     | 25         | mA           | -40°C                                                                                                                                                                                              |        |           |  |  |

| DC44a                           | 16                     | 25         | mA           | +25°C                                                                                                                                                                                              | 3.3V   | 40 MIPS   |  |  |

| DC44b                           | 16                     | 25         | mA           | +85°C                                                                                                                                                                                              | 3.3V   | 40 WIF5   |  |  |