Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 64KB (64K × 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp710at-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

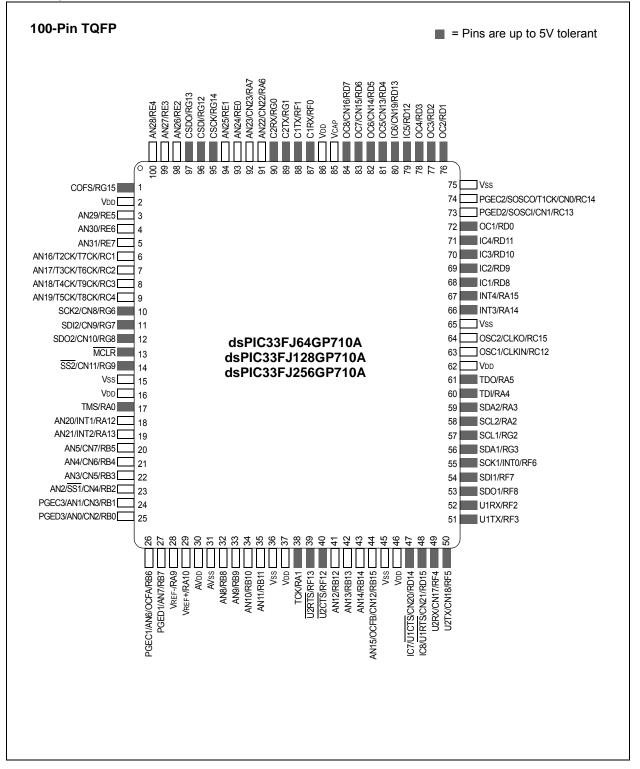

#### **Pin Diagrams (Continued)**

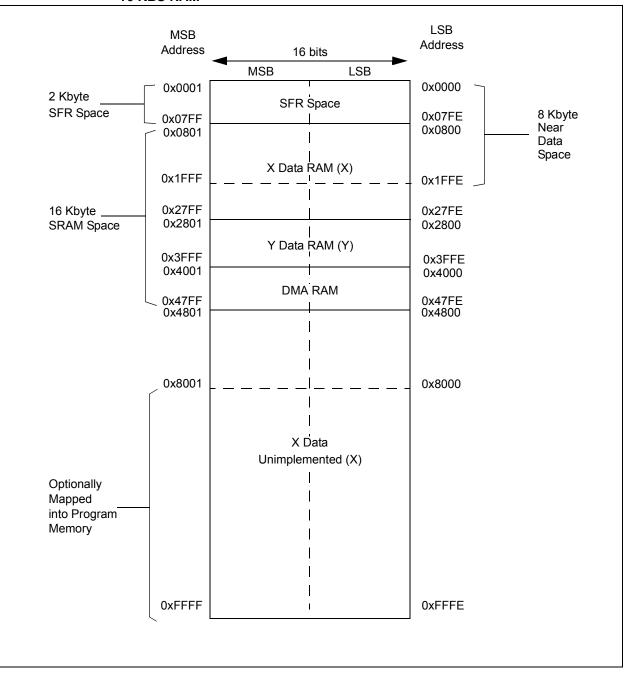

### FIGURE 4-4: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 16 KBS RAM

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6   | Bit 5             | Bit 4       | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|---------------|---------|-------------------|-------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE          | LPBACK  | ABAUD             | URXINV      | BRGH   | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXIS         | EL<1:0> | ADDEN             | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        |        | _        | _      | _      | _      | _     |            |               |         | UART <sup>-</sup> | Fransmit Re | gister |       |        |       | xxxx          |

| U1RXREG  | 0226        | _        |        | _        | _      | _      | _      | _     |            |               |         | UART              | Receive Re  | gister |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | nerator Presc | aler    |                   |             |        |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: UART2 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|---------|-------|-------------|---------|-------|--------|-------|---------------|

| U2MODE      | 0230        | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH    | PDSEI | _<1:0> | STSEL | 0000          |

| U2STA       | 0232        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISI       | EL<1:0> | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234        | _        | _      | _        | _      | _      | _      | _     |            |              |         | UART  | Transmit Re | egister |       |        |       | XXXX          |

| U2RXREG     | 0236        | _        | _      | _        | _      | _      | _      | _     |            |              |         | UART  | Receive Re  | egister |       |        |       | 0000          |

| U2BRG       | 0238        |          |        |          |        |        |        | Bauc  | l Rate Gen | erator Presc | aler    |       |             |         |       |        |       | 0000          |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: SPI1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|--------|---------|--------|--------|--------|------------|------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT    | 0240        | SPIEN  | —      | SPISIDL | _      | _      | _      | _          | —          | —            | SPIROV   | _     | _     | —         | —     | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE        | SSEN         | CKP      | MSTEN |       | SPRE<2:0> | •     | PPRE   | <1:0>  | 0000          |

| SPI1CON2    | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _          | _            | _        | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF     | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Re | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | —      | SPISIDL | —      |        |        |           |             | —            | SPIROV   | —     |       | —         |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _         | _           | _            | _        |       | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        |        |        |         |        |        |        | SPI2 Tran | smit and Re | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJXXXGPX06A/X08A/X10A architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJXXXGPX06A/X08A/X10A architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-37 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

#### TABLE 4-37: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        |      | Progra     | m Space / | Address       |       |

|--------------------------|---------------|------|------------|-----------|---------------|-------|

| Access Type              | Space         | <23> | <22:16>    | <15>      | <14:1>        | <0>   |

| Instruction Access       | User          | 0    |            | PC<22:1>  | >             | 0     |

| (Code Execution)         |               |      | 0xx xxxx x | xxx xxx   | xx xxxx xxx0  |       |

| TBLRD/TBLWT              | User          | TB   | LPAG<7:0>  |           | Data EA<15:0> |       |

| (Byte/Word Read/Write)   |               | 0    | xxx xxxx   | xxxx xx   | xx xxxx xxxx  |       |

|                          | Configuration | TB   | LPAG<7:0>  |           | Data EA<15:0> |       |

|                          |               | 1    | xxx xxxx   | xxxx x    | xxx xxxx xxxx |       |

| Program Space Visibility | User          | 0    | PSVPAG<    | 7:0>      | Data EA<14:   | 0>(1) |

| (Block Remap/Read)       |               | 0    | XXXX XXX   | x         | xxx xxxx xxxx | xxxx  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | See Notes        |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        | _                     |               | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | Tstartup + Trst        | TOST + TLOCK          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | Trst                   | _                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | —             | 3                |

| Software        | Any Clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | —             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay (10 μs nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- **3:** TRST = Internal state Reset time (20 μs nominal).

- **4:** Tos⊤ = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- 5: TLOCK = PLL lock time (20 μs nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

#### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

<sup>© 2009-2012</sup> Microchip Technology Inc.

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 CNIE: Input Change Notification Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0                           | R/W-1             | R/W-0                                   | R/W-0          | U-0                              | R/W-1           | R/W-0           | R/W-0 |

|-------------------------------|-------------------|-----------------------------------------|----------------|----------------------------------|-----------------|-----------------|-------|

| 0-0                           | FK/ VV- I         | OC7IP<2:0>                              | K/VV-U         | 0-0                              | R/W-I           | OC6IP<2:0>      | R/W-U |

| <br>bit 15                    |                   | 00711 \2.02                             |                |                                  |                 | 00011 \2.02     | bi    |

|                               |                   |                                         |                |                                  |                 |                 |       |

| U-0                           | R/W-1             | R/W-0                                   | R/W-0          | U-0                              | R/W-1           | R/W-0           | R/W-0 |

| _                             |                   | OC5IP<2:0>                              |                | _                                |                 | IC6IP<2:0>      |       |

| bit 7                         |                   |                                         |                |                                  |                 |                 | bi    |

|                               |                   |                                         |                |                                  |                 |                 |       |

| Legend:                       | a hit             |                                         | .:4            | II – Unimplo                     | monted bit rea  |                 |       |

| R = Readable<br>-n = Value at |                   | W = Writable k<br>'1' = Bit is set      | DIC            | 0' = Onimple<br>'0' = Bit is cle | mented bit, rea | x = Bit is unkn | 0.4/2 |

| -n = value at                 | PUR               | I = BILIS SEL                           |                |                                  | areu            |                 | own   |

| bit 15                        | Unimpleme         | ented: Read as '0                       | ,              |                                  |                 |                 |       |

| bit 14-12                     | -                 | >: Output Comparison                    |                | 7 Interrupt Prior                | itv bits        |                 |       |

|                               |                   | upt is priority 7 (h                    |                | •                                | ,               |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               | 001 = Interr      | rupt is priority 1                      |                |                                  |                 |                 |       |

|                               |                   | upt source is disa                      | abled          |                                  |                 |                 |       |

| bit 11                        | Unimpleme         | ented: Read as '0                       | ,              |                                  |                 |                 |       |

| bit 10-8                      | OC6IP<2:0:        | >: Output Comparison                    | re Channel 6   | 6 Interrupt Prior                | ity bits        |                 |       |

|                               | 111 = Interr      | rupt is priority 7 (h                   | ighest priori  | ty interrupt)                    |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               |                   | rupt is priority 1                      |                |                                  |                 |                 |       |

|                               |                   | upt source is disa                      |                |                                  |                 |                 |       |

| bit 7                         | -                 | ented: Read as '0                       |                |                                  |                 |                 |       |

| bit 6-4                       |                   | >: Output Compa                         |                | •                                | ity bits        |                 |       |

|                               | •                 | rupt is priority 7 (h                   | lignest priori | ty interrupt)                    |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               |                   | upt is priority 1<br>upt source is disa | abled          |                                  |                 |                 |       |

| bit 3                         |                   | ented: Read as '0                       |                |                                  |                 |                 |       |

| bit 2-0                       | -                 | : Input Capture C                       |                | errupt Prioritv b                | vits            |                 |       |

|                               |                   | upt is priority 7 (h                    |                |                                  |                 |                 |       |

|                               | •                 |                                         | - · ·          | - 1/                             |                 |                 |       |

|                               | •                 |                                         |                |                                  |                 |                 |       |

|                               | •<br>001 = Interr | upt is priority 1                       |                |                                  |                 |                 |       |

|                               |                   |                                         |                |                                  |                 |                 |       |

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | ST/   | \<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                 |                 |       |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

#### 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU stops executing instructions

- · The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLK-DIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLK-DIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLK-DIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

| R/W-0      | R/W-0        | R/W-0                               | R/W-0                 | U-0               | U-0            | U-0            | U-0                  |

|------------|--------------|-------------------------------------|-----------------------|-------------------|----------------|----------------|----------------------|

| T9MD       | T8MD         | T7MD                                | T6MD                  |                   |                |                |                      |

| bit 15     | TOMD         | TTND                                | TOND                  |                   | _              | —              | bit                  |

| DIL 15     |              |                                     |                       |                   |                |                | DI                   |

| U-0        | U-0          | U-0                                 | U-0                   | U-0               | U-0            | R/W-0          | R/W-0                |

| _          | _            | _                                   | —                     | _                 | —              | I2C2MD         | AD2MD <sup>(1)</sup> |

| bit 7      |              | •                                   |                       |                   |                |                | bit                  |

|            |              |                                     |                       |                   |                |                |                      |

| Legend:    |              |                                     |                       |                   |                |                |                      |

| R = Reada  | ble bit      | W = Writable                        | bit                   | U = Unimplem      | ented bit, rea | id as '0'      |                      |

| -n = Value | at POR       | '1' = Bit is set                    |                       | '0' = Bit is clea | ired           | x = Bit is unk | nown                 |

|            |              |                                     |                       |                   |                |                |                      |

| bit 15     | T9MD: Timer  | 9 Module Disat                      | ole bit               |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            | 0 = Timer9 m | odule is enable                     | d                     |                   |                |                |                      |

| bit 14     | T8MD: Timer  | 8 Module Disab                      | ole bit               |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            |              | odule is enable                     | -                     |                   |                |                |                      |

| bit 13     |              | 7 Module Disat                      |                       |                   |                |                |                      |

|            |              | odule is disable                    |                       |                   |                |                |                      |

|            |              | odule is enable                     | -                     |                   |                |                |                      |

| bit 12     |              | 6 Module Disat                      |                       |                   |                |                |                      |

|            |              | odule is disable<br>odule is enable |                       |                   |                |                |                      |

| bit 11-2   |              | ited: Read as '                     |                       |                   |                |                |                      |

| bit 1      | -            | 2 Module Disat                      |                       |                   |                |                |                      |

|            |              | z woodle Disat                      | DIE DIL               |                   |                |                |                      |

|            |              | dule is enabled                     |                       |                   |                |                |                      |

| bit 0      |              | 2 Module Disab                      | le bit <sup>(1)</sup> |                   |                |                |                      |

|            |              | ule is disabled                     |                       |                   |                |                |                      |

|            |              | ule is enabled                      |                       |                   |                |                |                      |

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

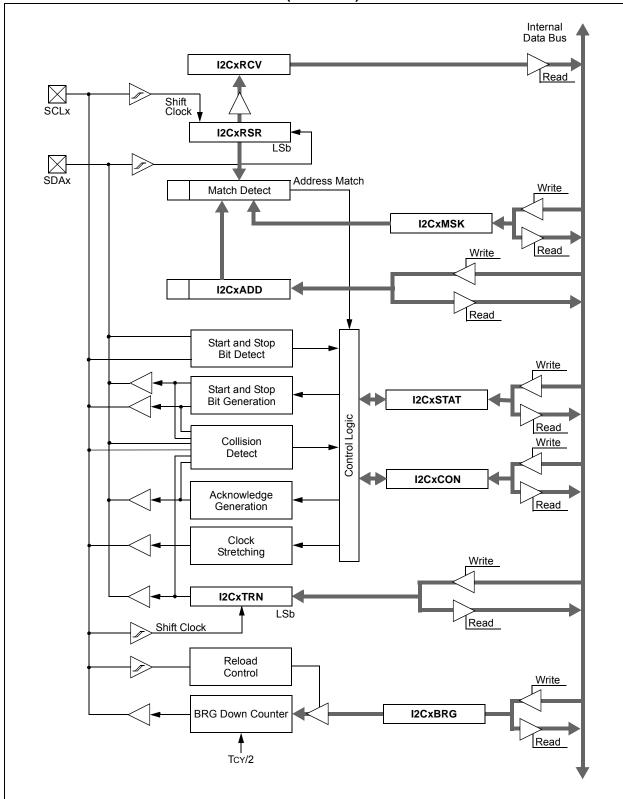

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (X = 1 OR 2)

| U-0           | U-0               | R-0                                   | R-0             | R-0              | R-0              | R-0             | R-0   |

|---------------|-------------------|---------------------------------------|-----------------|------------------|------------------|-----------------|-------|

|               |                   | ТХВО                                  | TXBP            | RXBP             | TXWAR            | RXWAR           | EWARN |

| bit 15        |                   |                                       |                 |                  |                  |                 | bit 8 |

| R/C-0         | R/C-0             | R/C-0                                 | U-0             | R/C-0            | R/C-0            | R/C-0           | R/C-0 |

| IVRIF         | WAKIF             | ERRIF                                 | 0-0             | FIFOIF           | RBOVIF           | RBIF            | TBIF  |

| bit 7         | WAKIF             | ERRIF                                 |                 | FIFUIF           | RBOVIE           | RBIF            | bit   |

|               |                   |                                       |                 |                  |                  |                 | DIL   |

| Legend:       |                   | C = Clear on                          | y bit           |                  |                  |                 |       |

| R = Readable  | e bit             | W = Writable                          | bit             | U = Unimplei     | mented bit, read | d as '0'        |       |

| -n = Value at | POR               | '1' = Bit is set                      |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 15-14     | Unimplemen        | nted: Read as '                       | 0'              |                  |                  |                 |       |

| bit 13        | -                 | smitter in Error                      |                 | bit              |                  |                 |       |

|               |                   | ter is in Bus Of                      |                 |                  |                  |                 |       |

|               | 0 = Transmitt     | ter is not in Bus                     | Off state       |                  |                  |                 |       |

| bit 12        | TXBP: Trans       | mitter in Error                       | State Bus Pas   | sive bit         |                  |                 |       |

|               |                   | ter is in Bus Pa<br>ter is not in Bus |                 | -                |                  |                 |       |

| bit 11        |                   | iver in Error Sta                     |                 |                  |                  |                 |       |

|               |                   | is in Bus Pass                        |                 | vebil            |                  |                 |       |

|               |                   | is not in Bus P                       |                 |                  |                  |                 |       |

| bit 10        | TXWAR: Trai       | nsmitter in Erro                      | r State Warni   | ng bit           |                  |                 |       |

|               |                   | ter is in Error W                     |                 | 5                |                  |                 |       |

|               | 0 = Transmitt     | ter is not in Erro                    | or Warning sta  | ate              |                  |                 |       |

| bit 9         |                   | ceiver in Error                       | •               | bit              |                  |                 |       |

|               |                   | is in Error War                       |                 |                  |                  |                 |       |

| L:1 0         |                   | is not in Error                       |                 |                  | L:4              |                 |       |

| bit 8         |                   | nsmitter or Rec<br>ter or receiver i  |                 |                  | DIT              |                 |       |

|               |                   | ter or receiver i                     |                 | •                |                  |                 |       |

| bit 7         |                   | d Message Rec                         |                 | •                |                  |                 |       |

|               |                   | request has oc                        |                 | 5                |                  |                 |       |

|               | 0 = Interrupt     | request has no                        | t occurred      |                  |                  |                 |       |

| bit 6         |                   | Wake-up Activ                         |                 | ag bit           |                  |                 |       |

|               |                   | request has oc                        |                 |                  |                  |                 |       |

| 6:4 <i>5</i>  | -                 | request has no                        |                 |                  |                  |                 |       |

| bit 5         |                   |                                       |                 | ources in Clin   | F<13:8> regist   | er)             |       |

|               |                   | request has oc<br>request has no      |                 |                  |                  |                 |       |

| bit 4         | -                 | nted: Read as '                       |                 |                  |                  |                 |       |

| bit 3         | -                 | ) Almost Full In                      |                 | it               |                  |                 |       |

|               |                   | request has oc                        |                 |                  |                  |                 |       |

|               |                   | request has no                        |                 |                  |                  |                 |       |

| bit 2         | <b>RBOVIF:</b> RX | Buffer Overflo                        | w Interrupt Fla | ag bit           |                  |                 |       |

|               |                   | request has oc                        |                 |                  |                  |                 |       |

|               |                   | request has no                        |                 |                  |                  |                 |       |

| bit 1         |                   | Iffer Interrupt Fl                    | -               |                  |                  |                 |       |

|               | •                 | request has oc<br>request has no      |                 |                  |                  |                 |       |

|               |                   | i oquest nas nu                       |                 |                  |                  |                 |       |

| hit ()        | TRIF. TY Duf      | ffor Interrupt El                     | aa hit          |                  |                  |                 |       |

| bit 0         |                   | ffer Interrupt Fla<br>request has oc  | -               |                  |                  |                 |       |

#### REGISTER 19-6: CIINTF: ECAN™ INTERRUPT FLAG REGISTER

#### REGISTER 19-14: CIBUFPNT3: ECAN™ FILTER 8-11 BUFFER POINTER REGISTER

| R/W-0         | R/W-0         | R/W-0                                                   | R/W-0          | R/W-0               | R/W-0 | R/W-0           | R/W-0 |

|---------------|---------------|---------------------------------------------------------|----------------|---------------------|-------|-----------------|-------|

|               | F11BP         | <3:0>                                                   |                |                     | F10E  | 3P<3:0>         |       |

| bit 15        |               |                                                         |                |                     |       |                 | bit 8 |

| R/W-0         | R/W-0         | R/W-0                                                   | R/W-0          | R/W-0               | R/W-0 | R/W-0           | R/W-0 |

| R/W-0         | F9BP          |                                                         | R/W-U          | R/W-0               |       | P<3:0>          | R/W-U |

| bit 7         | 1 3 51        | 10.05                                                   |                |                     | 100   | 1 10.05         | bit ( |

|               |               |                                                         |                |                     |       |                 |       |

| Legend:       |               |                                                         |                |                     |       |                 |       |

| R = Readable  |               | W = Writable                                            |                | U = Unimplemer      |       |                 |       |

| -n = Value at | POR           | '1' = Bit is set                                        |                | '0' = Bit is cleare | ed    | x = Bit is unkr | nown  |

| bit 15-12     | F11BP<3:0>:   | : RX Buffer Writ                                        | tten when Filf | ter 11 Hits bits    |       |                 |       |

|               | 1111 = Filter | hits received in                                        | RX FIFO bu     | iffer               |       |                 |       |

|               | 1110 = Filter | hits received in                                        | n RX Buffer 1  | 4                   |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               |               | hits received in hits received in                       |                |                     |       |                 |       |

| bit 11-8      | 1111 = Filter | RX Buffer Wri<br>hits received ir<br>hits received ir   | RX FIFO bu     | iffer               |       |                 |       |

|               | •             |                                                         | Hot Building   | <b>T</b>            |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               |               | hits received in<br>hits received in                    |                |                     |       |                 |       |

| bit 7-4       | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu   | iffer               |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               |               | hits received ir hits received ir                       |                |                     |       |                 |       |

| bit 3-0       | F8BP<3:0>:    | RX Buffer Writt                                         | en when Filte  | er 8 Hits bits      |       |                 |       |

|               |               | hits received ir<br>hits received ir                    |                | -                   |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

|               | •             |                                                         |                |                     |       |                 |       |

| REGISTER 2                      | 1-6: ADxC                            | HS0: ADCx IN                                                               | NPUT CHAN                      | NEL 0 SELE      | CT REGISTE               | R              |         |

|---------------------------------|--------------------------------------|----------------------------------------------------------------------------|--------------------------------|-----------------|--------------------------|----------------|---------|

| R/W-0                           | U-0                                  | U-0                                                                        | R/W-0                          | R/W-0           | R/W-0                    | R/W-0          | R/W-0   |

| CH0NB                           | _                                    | _                                                                          |                                |                 | CH0SB<4:0>(1             | )              |         |

| bit 15                          | ·                                    | ·                                                                          | •                              |                 |                          |                | bit 8   |

| R/W-0                           | U-0                                  | U-0                                                                        | R/W-0                          | R/W-0           | R/W-0                    | R/W-0          | R/W-0   |

| CH0NA                           |                                      |                                                                            | 10,00-0                        | 10.00-0         | CH0SA<4:0>(1             | -              | 10.00-0 |

| bit 7                           |                                      |                                                                            |                                |                 |                          |                | bit (   |

| Legend:                         |                                      |                                                                            |                                |                 |                          |                |         |

| R = Readable                    | bit                                  | W = Writable I                                                             | bit                            | U = Unimple     | mented bit, read         | d as '0'       |         |

| -n = Value at F                 | POR                                  | '1' = Bit is set                                                           |                                | '0' = Bit is cl | eared                    | x = Bit is unk | nown    |

| bit 15<br>bit 14-13<br>bit 12-8 | Same definiti<br><b>Unimpleme</b> r  | nnel 0 Negative<br>ion as bit 7.<br>nted: Read as '(<br>•: Channel 0 Po    | )'                             |                 |                          |                |         |

|                                 | 11111 <b>= Ch</b> a                  | annel 0 positive<br>annel 0 positive                                       | input is AN31                  |                 |                          |                |         |

|                                 | 00001 <b>= Cha</b>                   | annel 0 positive<br>annel 0 positive<br>annel 0 positive                   | input is AN1                   |                 |                          |                |         |

| bit 7                           | CH0NA: Cha<br>1 = Channel            | annel 0 Negative<br>0 negative input<br>0 negative input                   | e Input Select<br>t is AN1     | for Sample A I  | oit                      |                |         |

| bit 6-5                         |                                      | nted: Read as 'd                                                           |                                |                 |                          |                |         |

| bit 4-0                         | 11111 = Cha<br>11110 = Cha<br>•<br>• | <ul> <li>Channel 0 Po<br/>annel 0 positive<br/>annel 0 positive</li> </ul> | input is AN31<br>input is AN30 | elect for Samp  | le A bits <sup>(1)</sup> |                |         |

|                                 | 00001 <b>= Cha</b>                   | annel 0 positive<br>annel 0 positive<br>annel 0 positive                   | input is AN1                   |                 |                          |                |         |

Note 1: ADC2 can only select AN0 through AN15 as positive input.

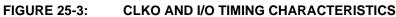

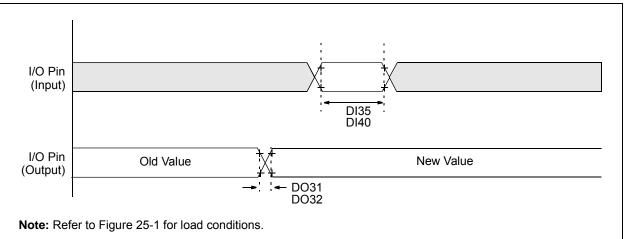

| AC CHARACTERISTICS |        |                                   | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |            |   |

|--------------------|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|---|

| Param<br>No.       | Symbol | Character                         | Min                                                                                                                                                                                                                                                                                    | Typ <sup>(1)</sup> | Max | Units | Conditions |   |

| DO31               | TioR   | Port Output Rise Time             |                                                                                                                                                                                                                                                                                        |                    | 10  | 25    | ns         |   |

| DO32               | TIOF   | Port Output Fall Time             |                                                                                                                                                                                                                                                                                        | _                  | 10  | 25    | ns         | _ |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                                                                                                                                                                                                                                                        | 20                 |     |       | ns         | — |

| DI40               | Trbp   | CNx High or Low Time (input)      |                                                                                                                                                                                                                                                                                        | 2                  |     |       | TCY        | _ |

|  | TABLE 25-20: | <b>I/O TIMING REQUIREMENTS</b> |

|--|--------------|--------------------------------|

|--|--------------|--------------------------------|

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

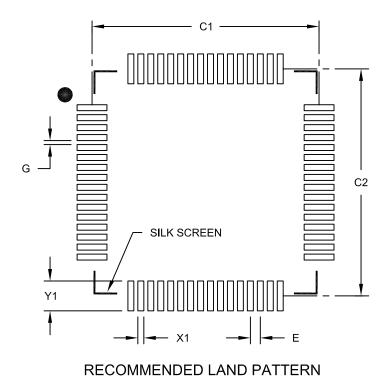

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |      |          |      |

|--------------------------|-------------|------|----------|------|

|                          | MILLIMETERS |      |          |      |

| Dimension Limits         |             | MIN  | NOM      | MAX  |

| Contact Pitch            | E           |      | 0.50 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X64)  | X1          |      |          | 0.30 |

| Contact Pad Length (X64) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

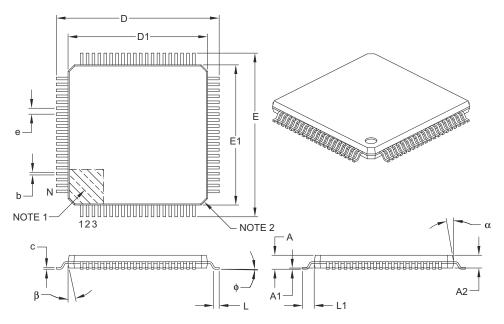

#### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|-----------|----------|-------------|--|--|--|

| ]                        | Dimension Limits | MIN       | NOM      | MAX         |  |  |  |

| Number of Leads          | N                | 80        |          |             |  |  |  |

| Lead Pitch               | е                |           | 0.50 BSC |             |  |  |  |

| Overall Height           | А                | -         | -        | 1.20        |  |  |  |

| Molded Package Thickness | A2               | 0.95      | 1.00     | 1.05        |  |  |  |

| Standoff                 | A1               | 0.05      | -        | 0.15        |  |  |  |

| Foot Length              | L                | 0.45      | 0.60     | 0.75        |  |  |  |

| Footprint                | L1               | 1.00 REF  |          |             |  |  |  |

| Foot Angle               | ¢                | 0°        | 3.5°     | 7°          |  |  |  |

| Overall Width            | E                | 14.00 BSC |          |             |  |  |  |

| Overall Length           | D                | 14.00 BSC |          |             |  |  |  |

| Molded Package Width     | E1               | 12.00 BSC |          |             |  |  |  |

| Molded Package Length    | D1               | 12.00 BSC |          |             |  |  |  |

| Lead Thickness           | С                | 0.09      | -        | 0.20        |  |  |  |

| Lead Width               | b                | 0.17      | 0.22     | 0.27        |  |  |  |

| Mold Draft Angle Top     | α                | 11°       | 12°      | 13°         |  |  |  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°      | 13°         |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

| DMAxPAD    |                                         |

|------------|-----------------------------------------|

| DMAxREQ    |                                         |

| DMAxSTA    |                                         |

| DMAxSTB    |                                         |

| Engine     |                                         |

| Multiplier | 35                                      |

|            | DMAxREQ<br>DMAxSTA<br>DMAxSTB<br>Engine |

#### Е

| ECAN Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CiFMSKSEL2 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ECAN1 Register Map (C1CTRL1.WIN = 0 or 1)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ECAN1 Register Map (C1CTRL1.WIN = 0)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ECAN1 Register Map (C1CTRL1.WIN = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ECAN2 Register Map (C2CTRL1.WIN = 0 or 1)61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ECAN2 Register Map (C2CTRL1.WIN = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Frame Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ECAN Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Filter 15-8 Mask Selection Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (CiFMSKSEL2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Enhanced CAN Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Device Operating Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Errata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Liidid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |