### Intel - EP4CE10E22C8N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 645                                                      |

| Number of Logic Elements/Cells | 10320                                                    |

| Total RAM Bits                 | 423936                                                   |

| Number of I/O                  | 91                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10e22c8n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer / deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

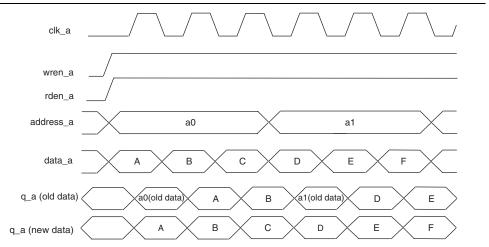

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

Figure 3–7. Cyclone IV Devices Single-Port Mode Timing Waveform

## **Simple Dual-Port Mode**

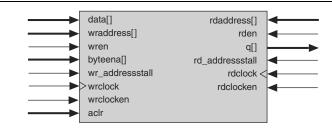

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

Figure 3–8. Cyclone IV Devices Simple Dual-Port Memory (1)

### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

Table 3–3.

Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

(Part 1 of 2)

| Dood Dort | Write Port   |              |              |                   |              |              |          |          |          |  |  |  |

|-----------|--------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|----------|--|--|--|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8 512 × 16 |              | 256 × 32     | 1024 × 9 | 512 × 18 | 256 × 36 |  |  |  |

| 8192 × 1  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$      | $\checkmark$ | $\checkmark$ | _        |          | —        |  |  |  |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$      | $\checkmark$ | $\checkmark$ | -        |          | —        |  |  |  |

| 2048 × 4  | ~            | ~            | $\checkmark$ | $\checkmark$      | ~            | $\checkmark$ | _        | _        | —        |  |  |  |

| 1024 × 8  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$      | $\checkmark$ | $\checkmark$ | _        | _        | —        |  |  |  |

# **18-Bit Multipliers**

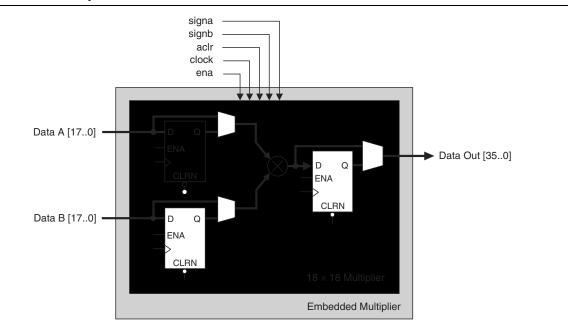

You can configure each embedded multiplier to support a single  $18 \times 18$  multiplier for input widths of 10 to 18 bits.

Figure 4–3 shows the embedded multiplier configured to support an 18-bit multiplier.

Figure 4–3. 18-Bit Multiplier Mode

All 18-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Also, you can dynamically change the signa and signb signals and send these signals through dedicated input registers.

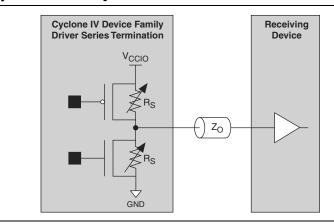

The  $R_S$  shown in Figure 6–2 is the intrinsic impedance of the transistors that make up the I/O buffer.

Figure 6–2. Cyclone IV Devices R<sub>s</sub> OCT with Calibration

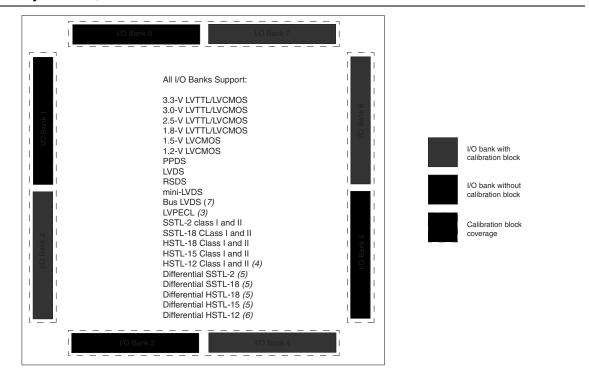

OCT with calibration is achieved using the OCT calibration block circuitry. There is one OCT calibration block in each of I/O banks 2, 4, 5, and 7 for Cyclone IV E devices and I/O banks 4, 5, and 7 for Cyclone IV GX devices. Each calibration block supports each side of the I/O banks. Because there are two I/O banks sharing the same calibration block, both banks must have the same V<sub>CCIO</sub> if both banks enable OCT calibration. If two related banks have different V<sub>CCIO</sub>, only the bank in which the calibration block resides can enable OCT calibration.

Figure 6–10 on page 6–18 shows the top-level view of the OCT calibration blocks placement.

Each calibration block comes with a pair of RUP and RDN pins. When used for calibration, the RUP pin is connected to  $V_{CCIO}$  through an external 25- $\Omega$ ±1% or 50- $\Omega$ ±1% resistor for an  $R_S$  OCT value of 25 $\Omega$  or 50 $\Omega$ , respectively. The RDN pin is connected to GND through an external 25- $\Omega$ ±1% or 50- $\Omega$ ±1% resistor for an  $R_S$  OCT value of 25 $\Omega$  or 50 $\Omega$ , respectively. The RDN pin is connected to GND through an external 25- $\Omega$ ±1% or 50- $\Omega$ ±1% resistor for an  $R_S$  OCT value of 25 $\Omega$  or 50 $\Omega$ , respectively. The external resistors are compared with the internal resistance using comparators. The resultant outputs of the comparators are used by the OCT calibration block to dynamically adjust buffer impedance.

During calibration, the resistance of the RUP and RDN pins varies.

Figure 6–9 shows the overview of Cyclone IV E I/O banks.

Figure 6–9. Cyclone IV E I/O Banks (1), (2)

#### Notes to Figure 6-9:

- (1) This is a top view of the silicon die. This is only a graphical representation. For exact pin locations, refer to the pin list and the Quartus II software.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 1, 2, 5, and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 3, 4, 7, and 8 only.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. Differential SSTL-18, differential HSTL-18, and HSTL-15 I/O standards do not support Class II output.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 3, 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses true LVDS input buffer.

- 3. Click the **Configuration** tab.

- 4. Turn on Generate compressed bitstreams.

- 5. Click OK.

- 6. In the **Settings** dialog box, click **OK**.

You can enable compression when creating programming files from the **Convert Programming Files** dialog box. To enable compression, perform the following steps:

- 1. On the File menu, click Convert Programming Files.

- 2. Under **Output programming file**, select your desired file type from the **Programming file type** list.

- 3. If you select **Programmer Object File (.pof)**, you must specify the configuration device in the **Configuration device** list.

- 4. Under Input files to convert, select SOF Data.

- 5. Click Add File to browse to the Cyclone IV device SRAM object files (.sof).

- 6. In the **Convert Programming Files** dialog box, select the **.pof** you added to **SOF Data** and click **Properties**.

- 7. In the SOF File Properties dialog box, turn on the Compression option.

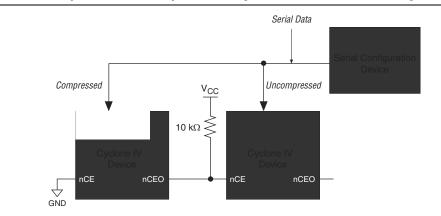

When multiple Cyclone IV devices are cascaded, you can selectively enable the compression feature for each device in the chain. Figure 8–1 shows a chain of two Cyclone IV devices. The first device has compression enabled and receives compressed bitstream from the configuration device. The second device has the compression feature disabled and receives uncompressed data. You can generate programming files for this setup in the **Convert Programming Files** dialog box.

Figure 8–1. Compressed and Uncompressed Configuration Data in the Same Configuration File

## **Configuration Requirement**

This section describes Cyclone IV device configuration requirement and includes the following topics:

- "Power-On Reset (POR) Circuit" on page 8–4

- "Configuration File Size" on page 8–4

- "Power Up" on page 8–6

Table 8–8 provides the configuration time for AS configuration.

| Symbol          | Parameter            | Parameter Cyclone IV E |   | Unit |  |

|-----------------|----------------------|------------------------|---|------|--|

| t <sub>SU</sub> | Setup time           | 10                     | 8 | ns   |  |

| t <sub>H</sub>  | Hold time            | 0                      | 0 | ns   |  |

| t <sub>co</sub> | Clock-to-output time | 4                      | 4 | ns   |  |

Table 8–8. AS Configuration Time for Cyclone IV Devices (1)

Note to Table 8–8:

(1) For the AS configuration timing diagram, refer to the Serial Configuration (EPCS) Devices Datasheet.

Enabling compression reduces the amount of configuration data that is sent to the Cyclone IV device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

## **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash memory-based devices. You can program these devices in-system with the USB-Blaster<sup>™</sup> or ByteBlaster<sup>™</sup> II download cables. Alternatively, you can program them with the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices through the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone IV devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive  $V_{CC}$  and GND, respectively.

To perform in-system programming of a serial configuration device through the AS programming interface, you must place the diodes and capacitors as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V (Figure 8–6).

IF you want to use the setup shown in Figure 8–6 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not require a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

**\*** For more information about implementing the SFL with Cyclone IV devices, refer to *AN 370: Using the Serial FlashLoader with the Quartus II Software.*

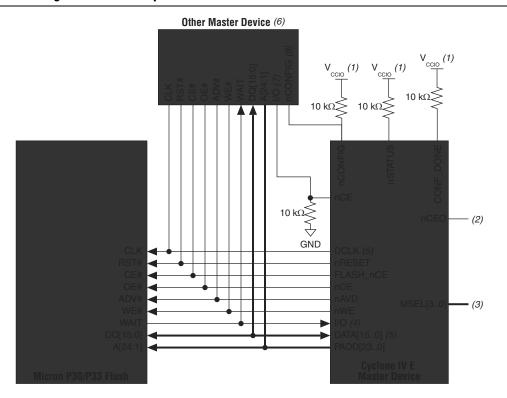

Figure 8–10 shows the AP configuration with multiple bus masters.

Figure 8–10. AP Configuration with Multiple Bus Masters

#### Notes to Figure 8–10:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (5) When cascading Cyclone IV E devices in a multi-device AP configuration, connect the repeater buffers between the master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The other master device must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8-5.

- (7) The other master device can control the AP configuration bus by driving the nCE to high with an output high on the I/O pin.

- (8) The other master device can pulse nCONFIG if it is under system control and not tied to V<sub>CCIO</sub>.

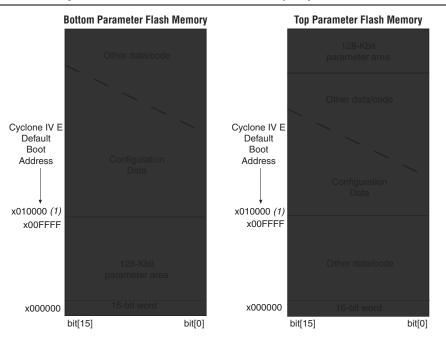

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

#### Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

## **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX<sup>®</sup> II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

**Tor** For more information about the PFL, refer to *AN* 386: Using the Parallel Flash Loader with the Quartus II Software.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

Table 8–21 lists the optional configuration pins. If you do not enable these optional configuration pins in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name  | User Mode                                     | Pin Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is on.                          | Input                | Optional user-supplied clock input synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLRUSK    | I/O if option is off.                         | mput                 | In AS configuration for Cyclone IV GX devices, you can use this pin as an external clock source to generate the DCLK by changing the clock source option in the Quartus II software in the <b>Configuration</b> tab of the <b>Device and Pin Options</b> dialog box.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INIT_DONE | N/A if option is on.<br>I/O if option is off. | Output<br>open-drain | Status pin is used to indicate when the device has initialized and<br>is in user-mode. When nCONFIG is low, the INIT_DONE pin is<br>tri-stated and pulled high due to an external 10-k $\Omega$ pull-up<br>resistor during the beginning of configuration. After the option<br>bit to enable INIT_DONE is programmed into the device (during<br>the first frame of configuration data), the INIT_DONE pin goes<br>low. When initialization is complete, the INIT_DONE pin is<br>released and pulled high and the device enters user mode.<br>Thus, the monitoring circuitry must be able to detect a low-to-<br>high transition. This pin is enabled by turning on the <b>Enable</b><br><b>INIT_DONE output</b> option in the Quartus II software. |

| INIT_DONE |                                               |                      | The functionality of this pin changes if the <b>Enable OCT_DONE</b> option is enabled in the Quartus II software. This option controls whether the INIT_DONE signal is gated by the OCT_DONE signal, which indicates the power-up on-chip termination (OCT) calibration is complete. If this option is turned off, the INIT_DONE signal is not gated by the OCT_DONE signal.                                                                                                                                                                                                                                                                                                                                                                       |

| DEV_OE    | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as programmed. This pin is enabled by turning on the <b>Enable device-wide output enable (DEV_OE)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DEV_CLRn  | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all clears on all device<br>registers. When this pin is driven low, all registers are cleared;<br>when this pin is driven high, all registers behave as<br>programmed. You can enable this pin by turning on the <b>Enable</b><br><b>device-wide reset (DEV_CLRn)</b> option in the Quartus II<br>software.                                                                                                                                                                                                                                                                                                                                                                                               |

Table 8–21. Optional Configuration Pins

### Table 8–28. Document Revision History (Part 2 of 2)

| Date          | Version | Changes                                                                                                                                                                                                                                 |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         | Updated for the Quartus II software 10.0 release:                                                                                                                                                                                       |

| July 2010     | 1.2     | <ul> <li>Updated "Power-On Reset (POR) Circuit", "Configuration and JTAG Pin I/O<br/>Requirements", and "Reset" sections.</li> </ul>                                                                                                    |

| July 2010 1.2 |         | <ul> <li>Updated Figure 8–10.</li> </ul>                                                                                                                                                                                                |

|               |         | ■ Updated Table 8–16 and Table 8–17.                                                                                                                                                                                                    |

| February 2010 |         | Updated for the Quartus II software 9.1 SP1 release:                                                                                                                                                                                    |

|               |         | <ul> <li>Added "Overriding the Internal Oscillator" and "AP Configuration (Supported Flash<br/>Memories)" sections.</li> </ul>                                                                                                          |

|               |         | <ul> <li>Updated "JTAG Instructions" section.</li> </ul>                                                                                                                                                                                |

|               | 1.1     | ■ Added Table 8–6.                                                                                                                                                                                                                      |

|               |         | ■ Updated Table 8–2, Table 8–3, Table 8–4, Table 8–6, Table 8–11, Table 8–13, Table 8–14, Table 8–15, and Table 8–18.                                                                                                                   |

|               |         | <ul> <li>Updated Figure 8–4, Figure 8–5, Figure 8–6, Figure 8–13, Figure 8–14,<br/>Figure 8–15, Figure 8–17, Figure 8–18, Figure 8–23, Figure 8–24, Figure 8–25,<br/>Figure 8–26, Figure 8–27, Figure 8–28, and Figure 8–29.</li> </ul> |

| November 2009 | 1.0     | Initial release.                                                                                                                                                                                                                        |

In user mode, Cyclone IV devices support the CHANGE\_EDREG JTAG instruction, that allows you to write to the 32-bit storage register. You can use Jam<sup>™</sup> STAPL files (.jam) to automate the testing and verification process. You can only execute this instruction when the device is in user mode, and it is a powerful design feature that enables you to dynamically verify the CRC functionality in-system without having to reconfigure the device. You can then use the CRC circuit to check for real errors induced by an SEU.

Table 9–1 describes the CHANGE\_EDREG JTAG instructions.

Table 9–1. CHANGE\_EDREG JTAG Instruction

| JTAG Instruction | Instruction Code | Description                                                                                                                                                                                                                    |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANGE_EDREG     | 00 0001 0101     | This instruction connects the 32-bit CRC storage register between TDI and TDO. Any precomputed CRC is loaded into the CRC storage register to test the operation of the error detection CRC circuitry at the $CRC\_ERROR$ pin. |

After the test completes, Altera recommends that you power cycle the device.

# **Automated SEU Detection**

Cyclone IV devices offer on-chip circuitry for automated checking of SEU detection. Applications that require the device to operate error-free at high elevations or in close proximity to earth's north or south pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy code feature controlled by the **Device and Pin Options** dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Cyclone IV devices, eliminating the need for external logic. The CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration CRAM data is corrupted. You must decide whether to reconfigure the FPGA by strobing the nCONFIG pin low or ignore the error.

# **CRC\_ERROR Pin**

A specific CRC\_ERROR error detection pin is required to monitor the results of the error detection circuitry during user mode. Table 9–2 describes the CRC\_ERROR pin.

Table 9–2. Cyclone IV Device CRC\_ERROR Pin Description

| CRC_ERROR Pin Type       | Description                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| I/O, Output (open-drain) | Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the <b>Error Detection CRC</b> tab of the <b>Device and Pin Options</b> dialog box. |  |  |  |  |  |  |  |

|                          | When using this pin, connect it to an external 10-k $\Omega$ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.                                                                                                                                                       |  |  |  |  |  |  |  |

The CRC\_ERROR pin information for Cyclone IV devices is reported in the Cyclone IV Devices Pin-Outs on the Altera<sup>®</sup> website.

# EXTEST\_PULSE

The instruction code for EXTEST\_PULSE is 0010001111. The EXTEST\_PULSE instruction generates three output transitions:

- Driver drives data on the falling edge of TCK in UPDATE\_IR/DR.

- Driver drives inverted data on the falling edge of TCK after entering the RUN\_TEST/IDLE state.

- Driver drives data on the falling edge of TCK after leaving the RUN\_TEST/IDLE state.

- IF you use DC-coupling on HSSI signals, you must execute the EXTEST instruction. If you use AC-coupling on HSSI signals, you must execute the EXTEST\_PULSE instruction. AC-coupled and DC-coupled HSSI are only supported in post-configuration mode.

## **EXTEST\_TRAIN**

The instruction code for EXTEST\_TRAIN is 0001001111. The EXTEST\_TRAIN instruction behaves the same as the EXTEST\_PULSE instruction with one exception. The output continues to toggle on the TCK falling edge as long as the test access port (TAP) controller is in the RUN\_TEST/IDLE state.

- These two instruction codes are only supported in post-configuration mode for Cyclone IV GX devices.

- When you perform JTAG boundary-scan testing before configuration, the nCONFIG pin must be held low.

# I/O Voltage Support in a JTAG Chain

A Cyclone IV device operating in BST mode uses four required pins: TDI, TDO, TMS, and TCK. The TDO output pin and all JTAG input pins are powered by the  $V_{CCIO}$  power supply of I/O Banks (I/O Bank 9 for Cyclone IV GX devices and I/O Bank 1 for Cyclone IV E devices).

A JTAG chain can contain several different devices. However, you must use caution if the chain contains devices that have different  $V_{CCIO}$  levels. The output voltage level of the TDO pin must meet the specification of the TDI pin it drives. For example, a device with a 3.3-V TDO pin can drive a device with a 5.0-V TDI pin because 3.3 V meets the minimum TTL-level  $V_{IH}$  for the 5.0-V TDI pin.

For multiple devices in a JTAG chain with the 3.0-V/3.3-V I/O standard, you must connect a  $25-\Omega$  series resistor on a TDO pin driving a TDI pin.

You can also interface the TDI and TDO lines of the devices that have different  $V_{CCIO}$  levels by inserting a level shifter between the devices. If possible, the JTAG chain should have a device with a higher  $V_{CCIO}$  level driving a device with an equal or lower  $V_{CCIO}$  level. This way, a level shifter may be required only to shift the TDO level to a level acceptable to the JTAG tester.

| Document Revision History                                                    |                  |

|------------------------------------------------------------------------------|------------------|

| Chapter 3. Cyclone IV Dynamic Reconfiguration                                |                  |

| Glossary of Terms                                                            |                  |

| Dynamic Reconfiguration Controller Architecture                              |                  |

| Dynamic Reconfiguration Controller Port List                                 |                  |

| Offset Cancellation Feature                                                  |                  |

| Functional Simulation of the Offset Cancellation Process                     |                  |

| Dynamic Reconfiguration Modes                                                |                  |

| PMA Controls Reconfiguration Mode                                            |                  |

| Method 1: Using logical_channel_address to Reconfigure Specific Transceive   | er Channels 3–14 |

| Method 2: Writing the Same Control Signals to Control All the Transceiver C  | Channels 3–16    |

| Method 3: Writing Different Control Signals for all the Transceiver Channels | at the Same Time |

| 3–19                                                                         |                  |

| Transceiver Channel Reconfiguration Mode                                     |                  |

| Channel Interface Reconfiguration Mode                                       |                  |

| Data Rate Reconfiguration Mode Using RX Local Divider                        |                  |

| Control and Status Signals for Channel Reconfiguration                       |                  |

| PLL Reconfiguration Mode                                                     |                  |

| Error Indication During Dynamic Reconfiguration                              |                  |

| Functional Simulation of the Dynamic Reconfiguration Process                 |                  |

| Document Revision History                                                    |                  |

|                                                                              |                  |

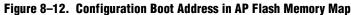

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK[1..0] and REFCLK[5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

|                             | HSSI     |                                                 | Terminatio | VCC_  | CLKIN Level   | I/O Pin Type |         |                    |  |  |

|-----------------------------|----------|-------------------------------------------------|------------|-------|---------------|--------------|---------|--------------------|--|--|

| I/O Standard                | Protocol | Coupling                                        | n          | Input | Output        | Column I/O   | Row I/O | Supported<br>Banks |  |  |

| LVDS                        | ALL      | Differential                                    | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| LVPECL                      | ALL      | AC (Needs<br>off-chip<br>resistor to<br>restore | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL      |                                                 | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

|                             | ALL      |                                                 | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

|                             | ALL      | V <sub>CM</sub> )                               | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| HCSL                        | PCle     | Differential<br>DC                              | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

Table 1–6. REFCLK I/O Standard Support

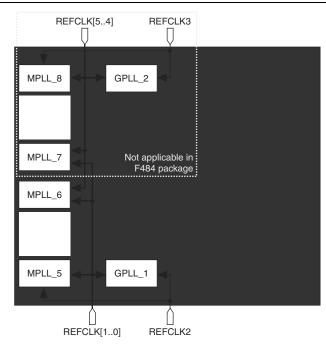

Cyclone IV GX transceivers do not have built-in support for some PCS functions such as auto-negotiation state machine, collision-detect, and carrier-sense. If required, you must implement these functions in a user logic or external circuits.

The 1000 Base-X PHY is defined by IEEE 802.3 standard as an intermediate or transition layer that interfaces various physical media with the media access control (MAC) in a GbE system. The 1000 Base-X PHY, which has a physical interface data rate of 1.25 Gbps consists of the PCS, PMA, and physical media dependent (PMD) layers. Figure 1–54 shows the 1000 Base-X PHY in LAN layers.

### Figure 1–54. 1000 Base-X PHY in a GbE OSI Reference Model

### Notes to Figure 1–54:

- (1) CSMA/CD = Carrier-Sense Multiple Access with Collision Detection

- (2) GMII = gigabit medium independent interface

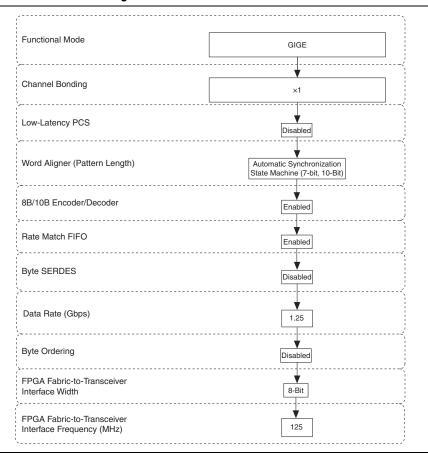

Figure 1–56 shows the transceiver configuration in GIGE mode.

Figure 1–56. Transceiver Configuration in GIGE Mode

When configured in GIGE mode, three encoded comma (/K28.5/) code groups are transmitted automatically after deassertion of tx\_digitalreset and before transmitting user data on the tx\_datain port. This could affect the synchronization state machine behavior at the receiver.

Depending on when you start transmitting the synchronization sequence, there could be an even or odd number of encoded data (/Dx.y/) code groups transmitted between the last of the three automatically sent /K28.5/ code groups and the first /K28.5/ code group of the synchronization sequence. If there is an even number of /Dx.y/ code groups received between these two /K28.5/ code groups, the first /K28.5/ code group of the synchronization sequence begins at an odd code group boundary. An IEEE802.3-compliant GIGE synchronization state machine treats this as an error condition and goes into the Loss-of-Sync state.

| Port Name                                          | Input/<br>Output | Clock Domain        | Description                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|----------------------------------------------------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| fixedclk                                           | Input            | Clock signal        | 125-MHz clock for receiver detect and offset cancellation only in PIPE mode.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                    |                  |                     | Receiver detect or reverse parallel loopback control.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| tx_detectrxloop                                    | Input            | Asynchronous signal | <ul> <li>A high level in the P1 power state and tx_forcelecidle<br/>signal asserted begins the receiver detection operation to determine<br/>if there is a valid receiver downstream. This signal must be<br/>deasserted when the pipephydonestatus signal indicates<br/>receiver detect completion.</li> </ul> |  |  |  |  |  |  |

| tx_forcedisp<br>compliance<br>pipe8b10binvpolarity |                  |                     | <ul> <li>A high level in the P0 power state with the tx_forceelecidle<br/>signal deasserted dynamically configures the channel to support<br/>reverse parallel loopback mode.</li> </ul>                                                                                                                        |  |  |  |  |  |  |

|                                                    |                  |                     | Force the 8B/10B encoder to encode with negative running disparity.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                    | Input            | Asynchronous signal | <ul> <li>Assert only when transmitting the first byte of the PIPE-compliance<br/>pattern to force the 8B/10B encoder with a negative running<br/>disparity.</li> </ul>                                                                                                                                          |  |  |  |  |  |  |

| pipe8b10binvpolarity                               | Input            | Asynchronous signal | Invert the polarity of every bit of the 10-bit input to the 8B/10B decoder                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                    | Input            |                     | PIPE power state control.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                    |                  |                     | <ul> <li>Signal is 2 bits wide and is encoded as follows:</li> </ul>                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| nowordn                                            |                  | Asynchronous signal | <ul> <li>2'b00: P0 (Normal operation)</li> </ul>                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| powerdn                                            |                  | Asynchionous signal | <ul> <li>2'b01: P0s (Low recovery time latency, low power state)</li> </ul>                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                    |                  |                     | <ul> <li>2'b10: P1 (Longer recovery time latency, lower power state)</li> </ul>                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                    |                  |                     | <ul> <li>2'b11: P2 (Lowest power state)</li> </ul>                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| pipedatavalid                                      | Output           | N/A                 | Valid data and control on the rx_dataout and rx_ctrldetect ports indicator.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                    |                  |                     | PHY function completion indicator.                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| pipephydone<br>status Output Asynchronous signal   |                  |                     | <ul> <li>Asserted for one clock cycle to communicate completion of several<br/>PHY functions, such as power state transition and receiver<br/>detection.</li> </ul>                                                                                                                                             |  |  |  |  |  |  |

|                                                    |                  |                     | Electrical idle detected or inferred at the receiver indicator.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| pipeelecidle                                       | Output           | Asynchronous signal | <ul> <li>When electrical idle inference is used, this signal is driven high<br/>when it infers an electrical idle condition</li> </ul>                                                                                                                                                                          |  |  |  |  |  |  |

|                                                    |                  |                     | <ul> <li>When electrical idle inference is not used, the<br/>rx_signaldetect signal is inverted and driven on this port.</li> </ul>                                                                                                                                                                             |  |  |  |  |  |  |

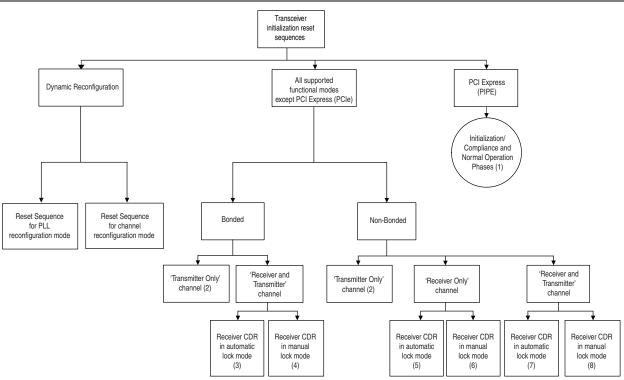

- The busy signal remains low for the first reconfig\_clk clock cycle. It then gets asserted from the second reconfig\_clk clock cycle. Subsequent deassertion of the busy signal indicates the completion of the offset cancellation process. This busy signal is required in transceiver reset sequences except for transmitter only channel configurations. Refer to the reset sequences shown in Figure 2–2 and the associated references listed in the notes for the figure.

- Altera strongly recommends adhering to these reset sequences for proper operation of the Cyclone IV GX transceiver.

Figure 2–2 shows the transceiver reset sequences for Cyclone IV GX devices.

### Notes to Figure 2-2:

- (1) Refer to the Timing Diagram in Figure 2-10.

- (2) Refer to the Timing Diagram in Figure 2–3.

- (3) Refer to the Timing Diagram in Figure 2–4.

- (4) Refer to the Timing Diagram in Figure 2–5.

- (5) Refer to the Timing Diagram in Figure 2–6.

- (6) Refer to the Timing Diagram in Figure 2–7.

- (7) Refer to the Timing Diagram in Figure 2–8.

- (8) Refer to the Timing Diagram in Figure 2–9.

Table 1–23 lists the Cyclone IV GX transceiver block AC specifications.

| Symbol/                                                                 | Ocuditions            | C6     |     |        | C7, I7 |     |        | C8    |     |          |      |

|-------------------------------------------------------------------------|-----------------------|--------|-----|--------|--------|-----|--------|-------|-----|----------|------|

| Description                                                             | Conditions            | Min    | Тур | Max    | Min    | Тур | Max    | Min   | Тур | Max      | Unit |

| PCIe Transmit Jitter Gene                                               | ration <sup>(3)</sup> |        |     | -      |        |     | -      |       |     | <u>.</u> |      |

| Total jitter at 2.5 Gbps<br>(Gen1)                                      | Compliance pattern    | _      | _   | 0.25   | _      | _   | 0.25   | _     | _   | 0.25     | UI   |

| PCIe Receiver Jitter Toler                                              | ance <sup>(3)</sup>   |        |     |        |        |     |        |       |     |          |      |

| Total jitter at 2.5 Gbps<br>(Gen1)                                      | Compliance pattern    | > 0.6  |     |        | > 0.6  |     |        | > 0.6 |     |          | UI   |

| GIGE Transmit Jitter Gene                                               | ration <sup>(4)</sup> |        |     |        | •      |     |        | •     |     |          | •    |

| Deterministic jitter                                                    | Pattern = CRPAT       |        |     | 0.14   |        |     | 0.14   |       |     | 0.14     | UI   |

| (peak-to-peak)                                                          | Fallelli = UNFAT      |        |     | 0.14   | _      | _   | 0.14   |       | _   | 0.14     | 01   |

| Total jitter (peak-to-peak)                                             | Pattern = CRPAT       |        | —   | 0.279  | —      | _   | 0.279  |       | —   | 0.279    | UI   |

| GIGE Receiver Jitter Toler                                              | ance <sup>(4)</sup>   |        |     |        |        |     |        |       |     |          |      |

| Deterministic jitter<br>tolerance (peak-to-peak)                        | Pattern = CJPAT > 0.4 |        | ļ   | > 0.4  |        |     | > 0.4  |       |     | UI       |      |

| Combined deterministic<br>and random jitter<br>tolerance (peak-to-peak) | Pattern = CJPAT       | > 0.66 |     | > 0.66 |        |     | > 0.66 |       |     | UI       |      |

### Table 1–23. Transceiver Block AC Specification for Cyclone IV GX Devices (1), (2)

Notes to Table 1-23:

(1) Dedicated refclk pins were used to drive the input reference clocks.

(2) The jitter numbers specified are valid for the stated conditions only.

(3) The jitter numbers for PIPE are compliant to the PCIe Base Specification 2.0.

(4) The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification.

# **Core Performance Specifications**

The following sections describe the clock tree specifications, PLLs, embedded multiplier, memory block, and configuration specifications for Cyclone IV Devices.

## **Clock Tree Specifications**

Table 1–24 lists the clock tree specifications for Cyclone IV devices.

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 1 of 2)

| Device  | Performance |       |     |                    |                    |       |                    |     | 11   |

|---------|-------------|-------|-----|--------------------|--------------------|-------|--------------------|-----|------|

|         | C6          | C7    | C8  | C8L <sup>(1)</sup> | C9L <sup>(1)</sup> | 17    | 18L <sup>(1)</sup> | A7  | Unit |

| EP4CE6  | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |

| EP4CE10 | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |

| EP4CE15 | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |

| EP4CE22 | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |

| EP4CE30 | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |

| EP4CE40 | 500         | 437.5 | 402 | 362                | 265                | 437.5 | 362                | 402 | MHz  |