# E·XFL

## Intel - EP4CE10E22I7N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| 2012112                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 645                                                      |

| Number of Logic Elements/Cells | 10320                                                    |

| Total RAM Bits                 | 423936                                                   |

| Number of I/O                  | 91                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10e22i7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Manual Clock Switchover                     | 5–30 |

|---------------------------------------------|------|

| Guidelines                                  | 5–30 |

| Programmable Bandwidth                      | 5–32 |

| Phase Shift Implementation                  | 5–32 |

| PLL Cascading                               | 5–33 |

| PLL Reconfiguration                         | 5–34 |

| PLL Reconfiguration Hardware Implementation | 5–34 |

| Post-Scale Counters (C0 to C4)              | 5–36 |

| Scan Chain Description                      | 5–37 |

| Charge Pump and Loop Filter                 | 5–38 |

| Bypassing a PLL Counter                     | 5–39 |

| Dynamic Phase Shifting                      | 5–39 |

| Spread-Spectrum Clocking                    | 5–41 |

| PLL Specifications                          | 5–41 |

| Document Revision History                   | 5–42 |

## Section II. I/O Interfaces

| Chapter 6. I/O Features in Cyclone IV Devi |

|--------------------------------------------|

|--------------------------------------------|

| Cyclone IV I/O Elements                                              |      |

|----------------------------------------------------------------------|------|

| I/O Element Features                                                 |      |

| Programmable Current Strength                                        |      |

| Slew Rate Control                                                    | 6–4  |

| Open-Drain Output                                                    |      |

| Bus Hold                                                             |      |

| Programmable Pull-Up Resistor                                        |      |

| Programmable Delay                                                   | 6–5  |

| PCI-Clamp Diode                                                      |      |

| OCT Support                                                          |      |

| On-Chip Series Termination with Calibration                          |      |

| On-Chip Series Termination Without Calibration                       |      |

| I/O Standards                                                        |      |

| Termination Scheme for I/O Standards                                 |      |

| Voltage-Referenced I/O Standard Termination                          | 6–14 |

| Differential I/O Standard Termination                                |      |

| I/O Banks                                                            |      |

| High-Speed Differential Interfaces                                   |      |

| External Memory Interfacing                                          |      |

| Pad Placement and DC Guidelines                                      |      |

| Pad Placement                                                        |      |

| DC Guidelines                                                        |      |

| Clock Pins Functionality                                             |      |

| High-Speed I/O Interface                                             |      |

| High-Speed I/O Standards Support                                     |      |

| High Speed Serial Interface (HSSI) Input Reference Clock Support     |      |

| LVDS I/O Standard Support in Cyclone IV Devices                      | 6–29 |

| Designing with LVDS                                                  |      |

| BLVDS I/O Standard Support in Cyclone IV Devices                     |      |

| Designing with BLVDS                                                 |      |

| RSDS, Mini-LVDS, and PPDS I/O Standard Support in Cyclone IV Devices |      |

| Designing with RSDS, Mini-LVDS, and PPDS                             |      |

| LVPECL I/O Support in Cyclone IV Devices                             |      |

| Differential SSTL I/O Standard Support in Cyclone IV Devices         |      |

|                                                                      |      |

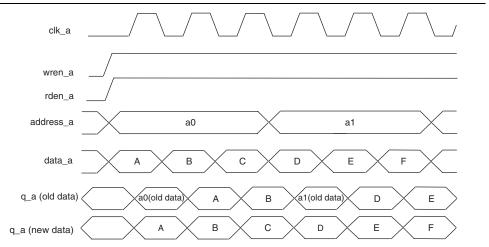

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

Figure 3–7. Cyclone IV Devices Single-Port Mode Timing Waveform

## **Simple Dual-Port Mode**

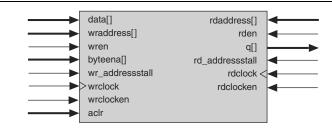

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

Figure 3–8. Cyclone IV Devices Simple Dual-Port Memory (1)

### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

Table 3–3.

Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

(Part 1 of 2)

| Dood Dort |              |              |              |              | Write Port   |              |          |          |          |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|----------|----------|----------|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9 | 512 × 18 | 256 × 36 |

| 8192 × 1  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        |          | —        |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -        |          | —        |

| 2048 × 4  | ~            | ~            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$ | _        | _        | —        |

| 1024 × 8  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        | _        | —        |

## Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup> (Part 4 of 4)

| GCLK Network Clock |   |   |   |   |   |   |   |   |   |   |    |    |    | GC | LK N | etwo | rks |    |    |              |    |    |    |    |    |    |    |    |    |    |

|--------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|------|------|-----|----|----|--------------|----|----|----|----|----|----|----|----|----|----|

| Sources            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15   | 16  | 17 | 18 | 19           | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| DPCLK17            | — | — | — |   | — | — | — | — | — |   | —  | —  | —  | —  | _    |      | —   |    | —  | $\checkmark$ | —  | —  | —  | —  | —  | —  |    | —  |    | —  |

### Notes to Table 5-2:

(1) EP4CGX30 information in this table refers to only EP4CGX30 device in F484 package.

(2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

(3) PLL\_7 and PLL\_8 are not available in EP4CXGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

| GCLK Network Clock              | GCLK Networks |              |              |              |              |              |              |              |              |              |              |              |              |    |              |    |    |              |              |    |

|---------------------------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----|--------------|----|----|--------------|--------------|----|

| Sources                         | 0             | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13 | 14           | 15 | 16 | 17           | 18           | 19 |

| CLK1                            | —             | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —  | —            | —  | —  | —            | —            | —  |

| CLK2/DIFFCLK_1p                 | —             | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK3/DIFFCLK_1n                 | $\checkmark$  |              | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | _            | —            |              | _  |              | —  | _  |              |              | —  |

| CLK4/DIFFCLK_2p                 | —             |              | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK5/DIFFCLK_2n                 | —             |              | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            |              | —  | _            | —  | —  | _            |              | —  |

| CLK6/DIFFCLK_3p                 | —             |              | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | _            | —            |              | _  |              | —  | _  |              |              | —  |

| CLK7/DIFFCLK_3n                 | —             |              | —            | —            | —            | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | —            | —  | —            | —  | —  | —            | _            | —  |

| CLK8/DIFFCLK_5n (2)             | —             |              | —            | _            | _            | —            | —            | —            | —            | _            | $\checkmark$ | —            | $\checkmark$ |    | $\checkmark$ | —  |    | _            |              | —  |

| CLK9/DIFFCLK_5p (2)             | —             |              | —            | _            | _            | —            | —            | —            | —            | _            |              | $\checkmark$ | $\checkmark$ |    | _            | —  |    | _            |              | —  |

| CLK10/DIFFCLK_4n (2)            | _             | _            | _            | _            | _            | _            | —            |              | _            | _            |              | ~            | _            | ~  | ~            | _  |    | _            |              |    |

| CLK11/DIFFCLK_4p<br>(2)         | —             | _            | _            | _            | _            | —            | —            | —            | _            | _            | ~            | _            | —            | ~  | —            | —  | _  | —            |              |    |

| CLK12/DIFFCLK_7n<br><i>(</i> 2) | —             | _            | _            | —            | —            | —            | —            | —            | _            | —            | _            | _            | —            | _  | —            | ~  | _  | ~            |              | ~  |

| CLK13/DIFFCLK_7p<br>(2)         | _             | —            | —            | —            | —            | _            | _            | —            | —            | —            | _            | —            | —            | _  | —            | _  | ~  | $\checkmark$ | _            |    |

| CLK14/DIFFCLK_6n<br><i>(2)</i>  | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | _  | _            | _  | ~  | _            | $\checkmark$ | ~  |

## Table 5-3. GCLK Network Connections for Cyclone IV E Devices (1) (Part 1 of 3)

• For the specific sustaining current for each V<sub>CCIO</sub> voltage level driven through the resistor and for the overdrive current used to identify the next driven input level, refer to the *Cyclone IV Device Datasheet* chapter.

## **Programmable Pull-Up Resistor**

Each Cyclone IV device I/O pin provides an optional programmable pull-up resistor while in user mode. If you enable this feature for an I/O pin, the pull-up resistor holds the output to the  $V_{CCIO}$  level of the output pin's bank.

- IF you enable the programmable pull-up resistor, the device cannot use the bus-hold feature. Programmable pull-up resistors are not supported on the dedicated configuration, JTAG, and dedicated clock pins.

- When the optional DEV\_OE signal drives low, all I/O pins remains tri-stated even with the programmable pull-up option enabled.

## **Programmable Delay**

The Cyclone IV IOE includes programmable delays to ensure zero hold times, minimize setup times, increase clock-to-output times, and delay the clock input signal.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays minimize setup time. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output registers. Each dual-purpose clock input pin provides a programmable delay to the global clock networks.

Table 6–1 shows the programmable delays for Cyclone IV devices.

| Programmable Delay                 | Quartus II Logic Option                                         |

|------------------------------------|-----------------------------------------------------------------|

| Input pin-to-logic array delay     | Input delay from pin to internal cells                          |

| Input pin-to-input register delay  | Input delay from pin to input register                          |

| Output pin delay                   | Delay from output register to output pin                        |

| Dual-purpose clock input pin delay | Input delay from dual-purpose clock pin to fan-out destinations |

Table 6-1. Cyclone IV Devices Programmable Delay Chain

There are two paths in the IOE for an input to reach the logic array. Each of the two paths can have a different delay. This allows you to adjust delays from the pin to the internal logic element (LE) registers that reside in two different areas of the device. You must set the two combinational input delays with the input delay from pin to internal cells logic option in the Quartus II software for each path. If the pin uses the input register, one of the delays is disregarded and the delay is set with the input delay from pin to input register logic option in the Quartus II software.

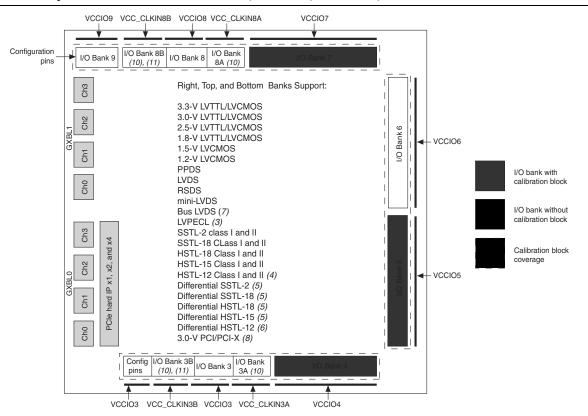

#### Figure 6–11. Cyclone IV GX I/O Banks for EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 <sup>(1), (2), (9)</sup>

#### Notes to Figure 6–11:

- (1) This is a top view of the silicon die. For exact pin locations, refer to the pin list and the Quartus II software.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 5 and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 4, 7, and 8.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses the LVDS input buffer.

- (8) The PCI-X I/O standard does not meet the IV curve requirement at the linear region.

- (9) The OCT block is located in the shaded banks 4, 5, and 7.

- (10) The dedicated clock input I/O banks 3A, 3B, 8A, and 8B can be used either for HSSI input reference clock pins or clock input pins.

- (11) Single-ended clock input support is available for dedicated clock input I/O banks 3B and 8B.

When designing LVTTL/LVCMOS inputs with Cyclone IV devices, refer to the following guidelines:

- All pins accept input voltage (V<sub>I</sub>) up to a maximum limit (3.6 V), as stated in the recommended operating conditions provided in the *Cyclone IV Device Datasheet* chapter.

- Whenever the input level is higher than the bank V<sub>CCIO</sub>, expect higher leakage current.

- The LVTTL/LVCMOS I/O standard input pins can only meet the V<sub>IH</sub> and V<sub>IL</sub> levels according to bank voltage level.

Voltage-referenced standards are supported in an I/O bank using any number of single-ended or differential standards, as long as they use the same V<sub>REF</sub> and V<sub>CCIO</sub> values. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone IV devices, I/O pins using these standards—because they require different V<sub>REF</sub> values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the V<sub>CCIO</sub> set to 2.5 V and the V<sub>REF</sub> set to 1.25 V.

- When using Cyclone IV devices as a receiver in 3.3-, 3.0-, or 2.5-V LVTTL/LVCMOS systems, you are responsible for managing overshoot or undershoot to stay in the absolute maximum ratings and the recommended operating conditions, provided in the *Cyclone IV Device Datasheet* chapter.

- The PCI clamping diode is enabled by default in the Quartus II software for input signals with bank  $V_{CCIO}$  at 2.5, 3.0, or 3.3 V.

## **High-Speed Differential Interfaces**

Cyclone IV devices can send and receive data through LVDS signals. For the LVDS transmitter and receiver, the input and output pins of Cyclone IV devices support serialization and deserialization through internal logic.

The BLVDS extends the benefits of LVDS to multipoint applications such as bidirectional backplanes. The loading effect and the need to terminate the bus at both ends for multipoint applications require BLVDS to drive out a higher current than LVDS to produce a comparable voltage swing. All the I/O banks of Cyclone IV devices support BLVDS for user I/O pins.

The RSDS and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI).

The PPDS standard is the next generation of the RSDS standard introduced by National Semiconductor Corporation. Cyclone IV devices meet the National Semiconductor Corporation PPDS Interface Specification and support the PPDS standard for outputs only. All the I/O banks of Cyclone IV devices support the PPDS standard for output pins only.

The LVDS standard does not require an input reference voltage, but it does require a 100- $\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side for the top and bottom I/O banks.

- "FPP Configuration" on page 8–40

- "JTAG Configuration" on page 8–45

- "Device Configuration Pins" on page 8–62

## **Configuration Features**

Table 8–1 lists the configuration methods you can use in each configuration scheme.

Table 8–1. Configuration Features in Cyclone IV Devices

| <b>Configuration Scheme</b> | Configuration Method                  | Decompression | Remote System Upgrade <sup>(1)</sup> |

|-----------------------------|---------------------------------------|---------------|--------------------------------------|

| AS                          | Serial Configuration Device           | $\checkmark$  | $\checkmark$                         |

| AP                          | Supported Flash Memory <sup>(2)</sup> | —             | $\checkmark$                         |

| PS                          | External Host with Flash Memory       | $\checkmark$  | ✓ (3)                                |

|                             | Download Cable                        | $\checkmark$  | _                                    |

| FPP                         | External Host with Flash Memory       | —             | ✓ <sup>(3)</sup>                     |

| ITAC based configuration    | External Host with Flash Memory       | —             | —                                    |

| JTAG based configuration    | Download Cable                        | —             | _                                    |

### Notes to Table 8-1:

(1) Remote update mode is supported when you use the Remote System Upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus® II software.

(2) For more information about the supported device families for the Micron commodity parallel flash, refer to Table 8–10 on page 8–22.

(3) Remote update mode is supported externally using the Parallel Flash Loader (PFL) with the Quartus II software.

## **Configuration Data Decompression**

Cyclone IV devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and send the compressed bitstream to Cyclone IV devices. During configuration, Cyclone IV devices decompress the bitstream in real time and program the SRAM cells.

Compression may reduce the configuration bitstream size by 35 to 55%.

When you enable compression, the Quartus II software generates configuration files with compressed configuration data. This compressed file reduces the storage requirements in the configuration device or flash memory and decreases the time required to send the bitstream to the Cyclone IV device. The time required by a Cyclone IV device to decompress a configuration file is less than the time required to send the configuration data to the device. There are two methods for enabling compression for the Cyclone IV device bitstreams in the Quartus II software:

- Before design compilation (through the Compiler Settings menu)

- After design compilation (through the **Convert Programming Files** dialog box)

To enable compression in the compiler settings of the project in the Quartus II software, perform the following steps:

- 1. On the Assignments menu, click **Device**. The **Settings** dialog box appears.

- 2. Click Device and Pin Options. The Device and Pin Options dialog box appears.

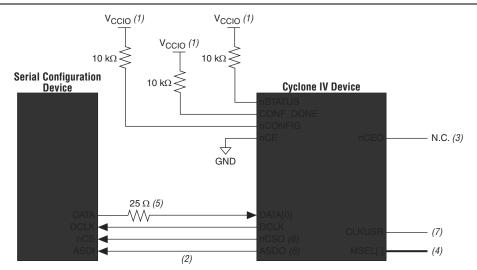

This four-pin interface connects to Cyclone IV device pins, as shown in Figure 8-2.

Figure 8–2. Single-Device AS Configuration

### Notes to Figure 8-2:

(1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Cyclone IV devices use the ASDO-to-ASDI path to control the configuration device.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as the DATA [1] pin in AP and FPP modes.

- (7) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- To tri-state the configuration bus for AS configuration schemes, you must tie nCE high and nCONFIG low.

- The 25-Ω resistor at the near end of the serial configuration device for DATA[0] works to minimize the driver impedance mismatch with the board trace and reduce the overshoot seen at the Cyclone IV device DATA[0] input pin.

In the single-device AS configuration, the maximum board loading and board trace length between the supported serial configuration device and the Cyclone IV device must follow the recommendations in Table 8–7 on page 8–18.

The DCLK generated by the Cyclone IV device controls the entire configuration cycle and provides timing for the serial interface. Cyclone IV devices use an internal oscillator or an external clock source to generate the DCLK. For Cyclone IV E devices, you can use a 40-MHz internal oscillator to generate the DCLK and for Cyclone IV GX devices you can use a slow clock (20 MHz maximum) or a fast clock (40 MHz maximum) from the internal oscillator or an external clock from CLKUSR to generate the DCLK. There are some variations in the internal oscillator frequency because of the process, voltage, and temperature (PVT) conditions in Cyclone IV

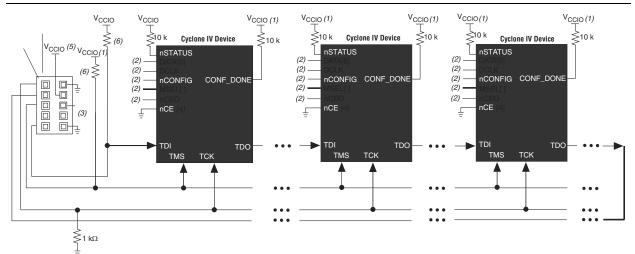

## Figure 8–26. JTAG Configuration of Multiple Devices Using a Download Cable (1.2, 1.5, and 1.8-V V<sub>CCIO</sub> Powering the JTAG Pins)

### Notes to Figure 8-26:

- (1) Connect these pull-up resistors to the V<sub>CCIO</sub> supply of the bank in which the pin resides.

- (2) Connect the nCONFIG and MSEL pins to support a non-JTAG configuration scheme. If you only use a JTAG configuration, connect the nCONFIG pin to logic-high and the MSEL pins to GND. In addition, pull DCLK and DATA[0] to either high or low, whichever is convenient on your board.

- (3) In the USB-Blaster and ByteBlaster II cable, this pin is connected to nCE when it is used for AS programming, otherwise it is a no connect.

- (4) You must connect the nCE pin to GND or driven low for successful JTAG configuration.

- (5) Power up the V<sub>CC</sub> of the ByteBlaster II or USB-Blaster cable with supply from V<sub>CCI0</sub>. The ByteBlaster II and USB-Blaster cables do not support a target supply voltage of 1.2 V. For the target supply voltage value, refer to the ByteBlaster II Download Cable User Guide and the USB-Blaster Download Cable User Guide.

- (6) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ .

- IF a non-Cyclone IV device is cascaded in the JTAG-chain, TDO of the non-Cyclone IV device driving into TDI of the Cyclone IV device must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

The CONF\_DONE and nSTATUS signals are shared in multi-device AS, AP, PS, and FPP configuration chains to ensure that the devices enter user mode at the same time after configuration is complete. When the CONF\_DONE and nSTATUS signals are shared among all the devices, you must configure every device when JTAG configuration is performed.

If you only use JTAG configuration, Altera recommends that you connect the circuitry as shown in Figure 8–25 or Figure 8–26, in which each of the CONF\_DONE and nSTATUS signals are isolated so that each device can enter user mode individually.

After the first device completes configuration in a multi-device configuration chain, its nCEO pin drives low to activate the nCE pin of the second device, which prompts the second device to begin configuration. Therefore, if these devices are also in a JTAG chain, ensure that the nCE pins are connected to GND during JTAG configuration or that the devices are JTAG configured in the same order as the configuration chain. As long as the devices are JTAG configured in the same order as the multi-device configuration chain, the nCEO of the previous device drives the nCE pin of the next device low when it has successfully been JTAG configured. You can place other Altera devices that have JTAG support in the same JTAG chain for device programming and configuration.

Table 8–21 lists the optional configuration pins. If you do not enable these optional configuration pins in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name  | User Mode                                     | Pin Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is on.                          | Input                | Optional user-supplied clock input synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLRUSK    | I/O if option is off.                         | mput                 | In AS configuration for Cyclone IV GX devices, you can use this pin as an external clock source to generate the DCLK by changing the clock source option in the Quartus II software in the <b>Configuration</b> tab of the <b>Device and Pin Options</b> dialog box.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INIT_DONE | N/A if option is on.<br>I/O if option is off. | Output<br>open-drain | Status pin is used to indicate when the device has initialized and<br>is in user-mode. When nCONFIG is low, the INIT_DONE pin is<br>tri-stated and pulled high due to an external 10-k $\Omega$ pull-up<br>resistor during the beginning of configuration. After the option<br>bit to enable INIT_DONE is programmed into the device (during<br>the first frame of configuration data), the INIT_DONE pin goes<br>low. When initialization is complete, the INIT_DONE pin is<br>released and pulled high and the device enters user mode.<br>Thus, the monitoring circuitry must be able to detect a low-to-<br>high transition. This pin is enabled by turning on the <b>Enable</b><br><b>INIT_DONE output</b> option in the Quartus II software. |

|           |                                               |                      | The functionality of this pin changes if the <b>Enable OCT_DONE</b> option is enabled in the Quartus II software. This option controls whether the INIT_DONE signal is gated by the OCT_DONE signal, which indicates the power-up on-chip termination (OCT) calibration is complete. If this option is turned off, the INIT_DONE signal is not gated by the OCT_DONE signal.                                                                                                                                                                                                                                                                                                                                                                       |

| DEV_OE    | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as programmed. This pin is enabled by turning on the <b>Enable device-wide output enable (DEV_OE)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DEV_CLRn  | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all clears on all device<br>registers. When this pin is driven low, all registers are cleared;<br>when this pin is driven high, all registers behave as<br>programmed. You can enable this pin by turning on the <b>Enable</b><br><b>device-wide reset (DEV_CLRn)</b> option in the Quartus II<br>software.                                                                                                                                                                                                                                                                                                                                                                                               |

Table 8–21. Optional Configuration Pins

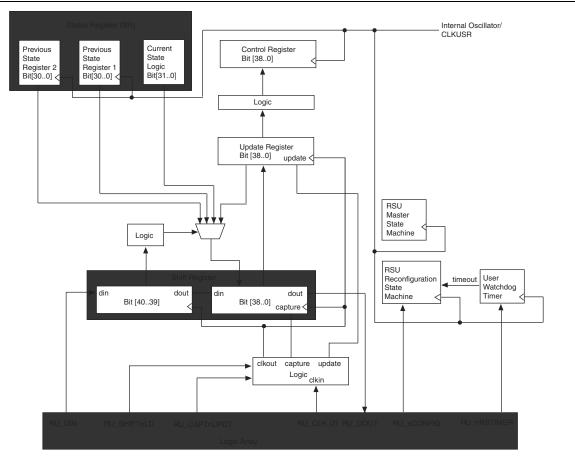

## **Dedicated Remote System Upgrade Circuitry**

This section describes the implementation of the Cyclone IV device remote system upgrade dedicated circuitry. The remote system upgrade circuitry is implemented in hard logic. This dedicated circuitry interfaces with the user-defined factory application configurations implemented in the Cyclone IV device logic array to provide the complete remote configuration solution. The remote system upgrade circuitry contains the remote system upgrade registers, a watchdog timer, and state machines that control those components. Figure 8–33 shows the data path of the remote system upgrade block.

Figure 8–33. Remote System Upgrade Circuit Data Path (1)

### Notes to Figure 8-33:

- (1) The RU\_DOUT, RU\_SHIFTnLD, RU\_CAPTNUPDT, RU\_CLK, RU\_DIN, RU\_nCONFIG, and RU\_nRSTIMER signals are internally controlled by the ALTREMOTE\_UPDATE megafunction.

- (2) The RU\_CLK refers to the ALTREMOTE\_UPDATE megafunction block "clock" input. For more information, refer to the *Remote Update Circuitry* (ALTREMOTE\_UPDATE) Megafunction User Guide.

## **Remote System Upgrade Registers**

The remote system upgrade block contains a series of registers that stores the configuration addresses, watchdog timer settings, and status information. Table 8–22 lists these registers.

Table 8–22.

Remote System Upgrade Registers

| Register            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift<br>register   | This register is accessible by the logic array and allows the update, status, and control registers to be written<br>and sampled by user logic. Write access is enabled in remote update mode for factory configurations to allow<br>writing to the update register. Write access is disabled for all application configurations in remote update<br>mode.                                                                                                        |

| Control<br>register | This register contains the current configuration address, the user watchdog timer settings, one option bit for checking early CONF_DONE, and one option bit for selecting the internal oscillator as the startup state machine clock. During a read operation in an application configuration, this register is read into the shift register. When a reconfiguration cycle is started, the contents of the update register are written into the control register. |

| Update<br>register  | This register contains data similar to that in the control register. However, it can only be updated by the factory configuration by shifting data into the shift register and issuing an update operation. When a reconfiguration cycle is triggered by the factory configuration, the control register is updated with the contents of the update register. During a read in a factory configuration, this register is read into the shift register.            |

| Status<br>register  | This register is written by the remote system upgrade circuitry on every reconfiguration to record the cause of the reconfiguration. This information is used by the factory configuration to determine the appropriate action following a reconfiguration. During a capture cycle, this register is read into the shift register.                                                                                                                                |

The control and status registers of the remote system upgrade are clocked by the 10-MHz internal oscillator (the same oscillator that controls the user watchdog timer) or the CLKUSR. However, the shift and update registers of the remote system upgrade are clocked by the maximum frequency of 40-MHz user clock input (RU\_CLK). There is no minimum frequency for RU\_CLK.

## **Remote System Upgrade Control Register**

The remote system upgrade control register stores the application configuration address, the user watchdog timer settings, and option bits for a application configuration. In remote update mode for the AS configuration scheme, the control register address bits are set to all zeros (24'b0) at power up to load the AS factory configuration. In remote update mode for the AP configuration scheme, the control register address bits are set to 24'h010000 (24'b1 0000 0000 0000) at power up to load the AP default factory configuration. However, for the AP configuration scheme, you can change the default factory configuration address to any desired address using the APFC\_BOOT\_ADDR JTAG instruction. Additionally, a factory configuration in remote update mode has write access to this register.

- The divisor value divides the frequency of the configuration oscillator output clock. This output clock is used as the clock source for the error detection process.

- 8. Click OK.

Figure 9–2. Enabling the Error Detection CRC Feature in the Quartus II Software

## **Accessing Error Detection Block Through User Logic**

The error detection circuit stores the computed 32-bit CRC signature in a 32-bit register, which is read out by user logic from the core. The cycloneiv\_crcblock primitive is a WYSIWYG component used to establish the interface from the user logic to the error detection circuit. The cycloneiv\_crcblock primitive atom contains the input and output ports that must be included in the atom. To access the logic array, the cycloneiv\_crcblock WYSIWYG atom must be inserted into your design.

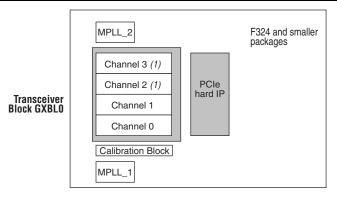

The Cyclone IV GX device includes a hard intellectual property (IP) implementation of the PCIe MegaCore<sup>®</sup> functions, supporting Gen1 ×1, ×2, and ×4 initial lane widths configured in the root port or endpoint mode. For more information, refer to "PCI-Express Hard IP Block" on page 1–46.

## **Transceiver Architecture**

Cyclone IV GX devices offer either one or two transceiver blocks per device, depending on the package. Each block consists of four full-duplex (transmitter and receiver) channels, located on the left side of the device (in a die-top view). Figure 1–1 and Figure 1–2 show the die-top view of the transceiver block and related resource locations in Cyclone IV GX devices.

### Note to Figure 1–1:

(1) Channel 2 and Channel 3 are not available in the F169 and smaller packages.

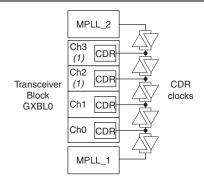

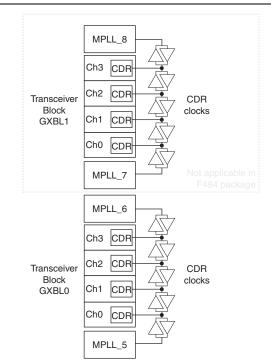

The CDR unit in each receiver channel gets the CDR clocks from one of the two multipurpose PLLs directly adjacent to the transceiver block. The CDR clocks distribution network is segmented by bidirectional tri-state buffers as shown in Figure 1–29 and Figure 1–30. This requires the CDR clocks from either one of the two multipurpose PLLs to drive a number of contiguous segmented paths to reach the intended receiver channel. Interleaving the CDR clocks from the two multipurpose PLLs is not supported.

For example, based on Figure 1–29, a combination of MPLL\_1 driving receiver channels 0, 1, and 3, while MPLL\_2 driving receiver channel 2 is not supported. In this case, only one multipurpose PLL can be used for the receiver channels.

### Figure 1–29. CDR Clocking for Transceiver Channels in F324 and Smaller Packages

### Note to Figure 1-29:

(1) Transceiver channels 2 and 3 are not available for devices in F169 and smaller packages.

### Figure 1–30. CDR Clocking for Transceiver Channels in F484 and Larger Packages

- Channel alignment is acquired if three additional aligned ||A|| columns are observed at the output of the deskew FIFOs of the four channels after alignment of the first ||A|| column.

- Channel alignment is indicated by the assertion of rx\_channelaligned signal.

- After acquiring channel alignment, if four misaligned ||A|| columns are seen at the output of the deskew FIFOs in all four channels with no aligned ||A|| columns in between, the rx\_channelaligned signal is deasserted, indicating loss of channel alignment.

Figure 1–65 shows lane skew at the receiver input and how the deskew FIFO uses the /A/ code group to align the channels.

Lane 0 Κ Κ R Κ R R Κ Κ R κ R Lane 1 Κ Κ R Κ R R Κ Κ R Κ R Lanes skew at receiver input Lane 2 Κ Κ R Κ R R Κ Κ R Κ R κ Κ R κ R R Κ κ R Κ R Lane 3 Lane 0 Κ Κ R Κ R R Κ Κ R Κ R Lane 1 Κ Κ R Κ R R κ Κ R Κ R Lanes are deskewed by lining up the "Align"/A/ code groups R κ R R κ к R R Lane 2 Κ Κ Κ R κ R R Κ Κ R R Κ Κ Κ Lane 3 /A/ column

## Figure 1-65. Deskew FIFO-Lane Skew at the Receiver Input

## **Lane Synchronization**

In XAUI mode, the word aligner is configured in automatic synchronization state machine mode that is compliant to the PCS synchronization state diagram specified in clause 48 of the IEEE P802.3ae specification. Table 1–23 lists the synchronization state machine parameters that implements the lane synchronization in XAUI mode.

Table 1–23. Synchronization State Machine Parameters <sup>(1)</sup>

| Parameter                                                                                 | Value |

|-------------------------------------------------------------------------------------------|-------|

| Number of valid synchronization (/K28.5/) code groups received to achieve synchronization | 4     |

| Number of erroneous code groups received to lose synchronization                          | 4     |

| Number of continuous good code groups received to reduce the error count by one           | 4     |

### Note to Table 1–23:

(1) The word aligner supports 7-bit and 10-bit pattern lengths in XAUI mode.

Figure 1–67 shows the transceiver configuration in Deterministic Latency mode.

| Functional Mode                                                       |               |                   | Deterministic Latency |                |                 |                |               |                |

|-----------------------------------------------------------------------|---------------|-------------------|-----------------------|----------------|-----------------|----------------|---------------|----------------|

| Channel Bonding                                                       |               |                   | ▼                     |                |                 |                |               |                |

|                                                                       |               |                   | ×1, ×4                |                |                 |                |               |                |

| Low-Latency PCS                                                       | Disabled      |                   |                       |                |                 |                |               |                |

|                                                                       |               |                   | Alignment<br>D-Bit)   |                | Bit SI<br>(10-B |                |               |                |

| 8B/10B Encoder/Decoder                                                | Enabled       |                   | Disabled              |                | Enabled         |                | Disabled      |                |

| Rate Match FIFO                                                       | Disabled      |                   | Disabled              |                | Disabled        |                | Disabled      |                |

| Byte SERDES                                                           | Enabled       | Disabled          | Enabled               | Disabled       | Enabled         | Disabled       | Enabled       | Disabled       |

| Data Rate (Gbps)                                                      | 0.6-<br>3.125 | 0.6-<br>1.5625    | 0.6-<br>3.125         | 0.6-<br>1.5625 | 0.6-<br>3.125   | 0.6-<br>1.5625 | 0.6-<br>3.125 | 0.6-<br>1.5625 |

| Byte Ordering                                                         | Disabled      | Disabled          | Disabled              | Disabled       | Disabled        | Disabled       | Disabled      | Disabled       |

| FPGA Fabric-to-Transceiver<br>Interface Width                         | 16-Bit        | 8-Bit             | 20-Bit                | 10-Bit         | 16-Bit          | 8-Bit          | 20-Bit        | 10-Bit         |

| FPGA Fabric-to-Transceiver<br>Interface Frequency (MHz)               | 60-<br>156.25 | 30-<br>156.25     | 60-<br>156.25         | 30-<br>156.25  | 60-<br>156.25   | 30-<br>156.25  | 60-<br>156.25 | 30-<br>156.25  |

| TX PCS Latency (FPGA<br>Fabric-Transceiver Interface<br>Clock Cycles) | 2.5 - 3.5     | <b>▼</b><br>4 - 5 | 2.5 - 3.5             | 4 - 5          | 2.5 - 3         | 4              | 2.5 - 3       | 4              |

| RX PCS Latency (FPGA<br>Fabric-Transceiver Interface<br>Clock Cycles) | 5-6           | 8-9               | 5-6                   | 8-9            | 5-6             | 8-9            | 5-6           | 8-9            |

Figure 1–67. Transceiver Configuration in Deterministic Latency Mode

Both CPRI and OBSAI protocols define the serial interface connecting the base station component (specifically channel cards) and remote radio heads (specifically radio frequency cards) in a radio base station system with fiber optics. The protocols require the accuracy of round trip delay measurement for single-hop and multi-hop connections to be within  $\pm$  16.276 ns. The Cyclone IV GX transceivers support the following CPRI and OBSAI line rates using Deterministic Latency mode:

- CPRI —614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps, and 3.072 Gbps

- OBSAI—768 Mbps, 1.536 Gbps, and 3.072 Gbps

• For more information about deterministic latency implementation, refer to *AN 610: Implementing Deterministic Latency for CPRI and OBSAI Protocols in Stratix IV, HardCopy IV, Arria II GX, and Cyclone IV Devices.*

## **Registered Mode Phase Compensation FIFO**

In Deterministic Latency mode, the RX phase compensation FIFO is set to registered mode while the TX phase compensation FIFO supports optional registered mode. When set into registered mode, the phase compensation FIFO acts as a register and eliminates the latency uncertainty through the FIFOs.

| Port Name                       | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                             |                                                                                                                           |  |  |  |  |

|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| logical_channel_<br>address[n0] | Input            | Enabled by the ALTGX_RECONFIG MegaWizard Plug-In Manager when you enable the Use 'logical_channel_address' port for Analog controls reconfiguration option in the Analog controls screen.                                                                                                                                               |                                                                                                                           |  |  |  |  |

|                                 |                  | The width of the logical_channel_address port depends on the value you set in the What is the number of channels controlled by the reconfig controller? option in the Reconfiguration settings screen. This port can be enabled only when the number of channels controlled by the dynamic reconfiguration controller is more than one. |                                                                                                                           |  |  |  |  |

|                                 |                  | Number of channels controlled<br>by the reconfiguration controller                                                                                                                                                                                                                                                                      | logical_channel_address input port width                                                                                  |  |  |  |  |

|                                 |                  | 2<br>3–4<br>5–8<br>9–16                                                                                                                                                                                                                                                                                                                 | <pre>logical_channel_address[0] logical_channel_address[10] logical_channel_address[20] logical_channel_address[30]</pre> |  |  |  |  |

| rx_tx_duplex_sel<br>[10]        | Input            | This is a 2-bit wide signal. You can select this in the <b>Error checks</b> screen.                                                                                                                                                                                                                                                     |                                                                                                                           |  |  |  |  |

|                                 |                  | The advantage of using this optional port is that it allows you to reconfigure only the transmitter portion of a channel, even if the channel configuration is duplex.                                                                                                                                                                  |                                                                                                                           |  |  |  |  |

|                                 |                  | For a setting of:                                                                                                                                                                                                                                                                                                                       |                                                                                                                           |  |  |  |  |

|                                 |                  | <pre>rx_tx_duplex_sel[1:0] = 2'b00—the transmitter and receiver portion of the<br/>channel is reconfigured.</pre>                                                                                                                                                                                                                       |                                                                                                                           |  |  |  |  |

|                                 |                  | <pre>rx_tx_duplex_sel[1:0] = 2'b01—the receiver portion of the channel is<br/>reconfigured.</pre>                                                                                                                                                                                                                                       |                                                                                                                           |  |  |  |  |

|                                 |                  | <pre>rx_tx_duplex_sel[1:0] = 2'b10- reconfigured.</pre>                                                                                                                                                                                                                                                                                 | -the transmitter portion of the channel is                                                                                |  |  |  |  |

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 3 of 7)

Example 1–1 shows how to calculate the change of 50- $\Omega$  I/O impedance from 25°C at 3.0 V to 85°C at 3.15 V.

Example 1–1. Impedance Change

$$\begin{split} \Delta R_V &= (3.15-3) \times 1000 \times -0.026 = -3.83 \\ \Delta R_T &= (85-25) \times 0.262 = 15.72 \\ \text{Because } \Delta R_V \text{ is negative,} \\ MF_V &= 1 \ / \ (3.83/100 + 1) = 0.963 \\ \text{Because } \Delta R_T \text{ is positive,} \\ MF_T &= 15.72/100 + 1 = 1.157 \\ MF &= 0.963 \times 1.157 = 1.114 \\ R_{\text{final}} &= 50 \times 1.114 = 55.71 \ \Omega \end{split}$$

## **Pin Capacitance**

Table 1–11 lists the pin capacitance for Cyclone IV devices.

| Symbol                     | Parameter                                                                                                            | Typical –<br>Quad Flat<br>Pack<br>(QFP) | Typical –<br>Quad Flat<br>No Leads<br>(QFN) | Typical –<br>Ball-Grid<br>Array<br>(BGA) | Unit |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------|------------------------------------------|------|

| CIOTB                      | Input capacitance on top and bottom I/O pins                                                                         | 7                                       | 7                                           | 6                                        | рF   |

| CIOLR                      | Input capacitance on right I/O pins                                                                                  | 7                                       | 7                                           | 5                                        | pF   |

| $C_{LVDSLR}$               | Input capacitance on right I/O pins with dedicated LVDS output                                                       | 8                                       | 8                                           | 7                                        | рF   |

| C <sub>VREFLR</sub><br>(2) | Input capacitance on right dual-purpose $\mathtt{VREF}$ pin when used as $V_{REF}$ or user I/O pin                   | 21                                      | 21                                          | 21                                       | pF   |

| C <sub>VREFTB</sub>        | Input capacitance on top and bottom dual-purpose $\mathtt{VREF}$ pin when used as $V_{\textrm{REF}}$ or user I/O pin | 23 <i>(3)</i>                           | 23                                          | 23                                       | pF   |

| C <sub>CLKTB</sub>         | Input capacitance on top and bottom dedicated clock input pins                                                       | 7                                       | 7                                           | 6                                        | pF   |

| C <sub>CLKLR</sub>         | Input capacitance on right dedicated clock input pins                                                                | 6                                       | 6                                           | 5                                        | pF   |

Notes to Table 1-11:

(1) The pin capacitance applies to FBGA, UBGA, and MBGA packages.

(2) When you use the vref pin as a regular input or output, you can expect a reduced performance of toggle rate and  $t_{CO}$  because of higher pin capacitance.

(3)  $C_{VREFTB}$  for the EP4CE22 device is 30 pF.