#### Intel - EP4CE10F17C6N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 645                                                      |

| Number of Logic Elements/Cells | 10320                                                    |

| Total RAM Bits                 | 423936                                                   |

| Number of I/O                  | 179                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10f17c6n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter Revision Dates  | ix     |

|-------------------------|--------|

| Additional Information  |        |

| How to Contact Altera   |        |

| Typographic Conventions | Info–1 |

# Section I. Device Core

### Chapter 1. Cyclone IV FPGA Device Family Overview

| Cyclone IV Device Family Features                    | 1–1  |

|------------------------------------------------------|------|

| Device Resources                                     | 1–3  |

| Package Matrix                                       | 1–5  |

| Cyclone IV Device Family Speed Grades                | 1–7  |

| Cyclone IV Device Family Architecture                | 1–8  |

| FPGA Core Fabric                                     |      |

| I/O Features                                         |      |

| Clock Management                                     | 1–9  |

| External Memory Interfaces                           | 1–9  |

| Configuration                                        | 1–10 |

| High-Speed Transceivers (Cyclone IV GX Devices Only) | 1–10 |

| Hard IP for PCI Express (Cyclone IV GX Devices Only) | 1–11 |

| Reference and Ordering Information                   | 1–12 |

| Document Revision History                            | 1–13 |

### Chapter 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

| Logic Elements            | . 2–1 |

|---------------------------|-------|

| LE Features               | . 2–2 |

| LE Operating Modes        | . 2–3 |

| Normal Mode               | . 2–3 |

| Arithmetic Mode           | . 2–4 |

| Logic Array Blocks        | . 2–5 |

| Topology                  | . 2–5 |

| LAB Interconnects         | . 2–6 |

| LAB Control Signals       | . 2–6 |

| Document Revision History | . 2–7 |

### Chapter 3. Memory Blocks in Cyclone IV Devices

| Overview                     | 3–1 |

|------------------------------|-----|

| Control Signals              | 3–3 |

| Parity Bit Support           | 3–3 |

| Byte Enable Support          | 3–3 |

| Packed Mode Support          | 3–4 |

| Address Clock Enable Support |     |

| Mixed-Width Support          | 3–6 |

| Asynchronous Clear           | 3–7 |

| Memory Modes                 | 3–7 |

| Single-Port Mode             | 3–8 |

| Simple Dual-Port Mode        | 3–9 |

|                              |     |

# **Section I. Device Core**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device family, which is the most architecturally advanced, high-performance, low-power FPGA in the marketplace. This section includes the following chapters:

- Chapter 1, Cyclone IV FPGA Device Family Overview

- Chapter 2, Logic Elements and Logic Array Blocks in Cyclone IV Devices

- Chapter 3, Memory Blocks in Cyclone IV Devices

- Chapter 4, Embedded Multipliers in Cyclone IV Devices

- Chapter 5, Clock Networks and PLLs in Cyclone IV Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Table 1–2 lists Cyclone IV GX device resources.

| Resources                            | EP4CGX15 | EP4CGX22         | EP4CGX30 | EP4CGX30<br>(2)   | EP4CGX50          | EP4CGX75          | EP4CGX110         | EP4CGX150     |

|--------------------------------------|----------|------------------|----------|-------------------|-------------------|-------------------|-------------------|---------------|

| Logic elements (LEs)                 | 14,400   | 21,280           | 29,440   | 29,440            | 49,888            | 73,920            | 109,424           | 149,760       |

| Embedded memory (Kbits)              | 540      | 756              | 1,080    | 1,080             | 2,502             | 4,158             | 5,490             | 6,480         |

| Embedded 18 × 18 multipliers         | 0        | 40               | 80       | 80                | 140               | 198               | 280               | 360           |

| General purpose PLLs                 | 1        | 2                | 2        | 4 (4)             | 4 (4)             | 4 (4)             | 4 (4)             | 4 <i>(4)</i>  |

| Multipurpose PLLs                    | 2 (5)    | 2 <sup>(5)</sup> | 2 (5)    | 2 <sup>(5)</sup>  | 4 (5)             | 4 (5)             | 4 (5)             | 4 (5)         |

| Global clock networks                | 20       | 20               | 20       | 30                | 30                | 30                | 30                | 30            |

| High-speed transceivers (6)          | 2        | 4                | 4        | 4                 | 8                 | 8                 | 8                 | 8             |

| Transceiver maximum data rate (Gbps) | 2.5      | 2.5              | 2.5      | 3.125             | 3.125             | 3.125             | 3.125             | 3.125         |

| PCIe (PIPE) hard IP blocks           | 1        | 1                | 1        | 1                 | 1                 | 1                 | 1                 | 1             |

| User I/O banks                       | g (7)    | g (7)            | g (7)    | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <i>(8)</i> |

| Maximum user I/O <sup>(9)</sup>      | 72       | 150              | 150      | 290               | 310               | 310               | 475               | 475           |

Table 1–2. Resources for the Cyclone IV GX Device Family

Notes to Table 1-2:

(1) Applicable for the F169 and F324 packages.

(2) Applicable for the F484 package.

(3) Only two multipurpose PLLs for F484 package.

(4) Two of the general purpose PLLs are able to support transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(5) You can use the multipurpose PLLs for general purpose clocking when they are not used to clock the transceivers. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(6) If PCIe ×1, you can use the remaining transceivers in a quad for other protocols at the same or different data rates.

(7) Including one configuration I/O bank and two dedicated clock input I/O banks for HSSI reference clock input.

(8) Including one configuration I/O bank and four dedicated clock input I/O banks for HSSI reference clock input.

(9) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

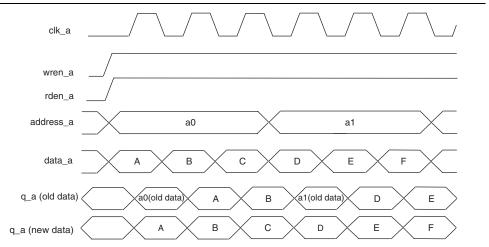

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

Figure 3–7. Cyclone IV Devices Single-Port Mode Timing Waveform

### **Simple Dual-Port Mode**

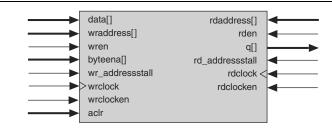

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

Figure 3–8. Cyclone IV Devices Simple Dual-Port Memory (1)

#### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

Table 3–3.

Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

(Part 1 of 2)

| Dood Dort | Write Port   |              |              |              |              |              |          |          |          |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|----------|----------|----------|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9 | 512 × 18 | 256 × 36 |

| 8192 × 1  | ~            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        |          | —        |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -        |          | —        |

| 2048 × 4  | ~            | ~            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$ | _        | _        | —        |

| 1024 × 8  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _        | _        | —        |

# **Power-Up Conditions and Memory Initialization**

The M9K memory block outputs of Cyclone IV devices power up to zero (cleared) regardless of whether the output registers are used or bypassed. All M9K memory blocks support initialization using a **.mif**. You can create **.mif**s in the Quartus II software and specify their use using the RAM MegaWizard Plug-In Manager when instantiating memory in your design. Even if memory is pre-initialized (for example, using a **.mif**), it still powers up with its outputs cleared. Only the subsequent read after power up outputs the pre-initialized values.

**To** For more information about **.mif**s, refer to the *RAM Megafunction User Guide* and the *Quartus II Handbook*.

### **Power Management**

The M9K memory block clock enables of Cyclone IV devices allow you to control clocking of each M9K memory block to reduce AC power consumption. Use the rden signal to ensure that read operations only occur when necessary. If your design does not require read-during-write, reduce power consumption by deasserting the rden signal during write operations or any period when there are no memory operations. The Quartus II software automatically powers down any unused M9K memory blocks to save static power.

# **Document Revision History**

Table 3–6 shows the revision history for this chapter.

| Table 3-6. | Document | Revision | History |

|------------|----------|----------|---------|

|------------|----------|----------|---------|

| Date          | Version | Changes                                    |

|---------------|---------|--------------------------------------------|

| November 2011 | 1.1     | Updated the "Byte Enable Support" section. |

| November 2009 | 1.0     | Initial release.                           |

When designing LVTTL/LVCMOS inputs with Cyclone IV devices, refer to the following guidelines:

- All pins accept input voltage (V<sub>I</sub>) up to a maximum limit (3.6 V), as stated in the recommended operating conditions provided in the *Cyclone IV Device Datasheet* chapter.

- Whenever the input level is higher than the bank V<sub>CCIO</sub>, expect higher leakage current.

- The LVTTL/LVCMOS I/O standard input pins can only meet the V<sub>IH</sub> and V<sub>IL</sub> levels according to bank voltage level.

Voltage-referenced standards are supported in an I/O bank using any number of single-ended or differential standards, as long as they use the same V<sub>REF</sub> and V<sub>CCIO</sub> values. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone IV devices, I/O pins using these standards—because they require different V<sub>REF</sub> values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the V<sub>CCIO</sub> set to 2.5 V and the V<sub>REF</sub> set to 1.25 V.

- When using Cyclone IV devices as a receiver in 3.3-, 3.0-, or 2.5-V LVTTL/LVCMOS systems, you are responsible for managing overshoot or undershoot to stay in the absolute maximum ratings and the recommended operating conditions, provided in the *Cyclone IV Device Datasheet* chapter.

- The PCI clamping diode is enabled by default in the Quartus II software for input signals with bank  $V_{CCIO}$  at 2.5, 3.0, or 3.3 V.

### **High-Speed Differential Interfaces**

Cyclone IV devices can send and receive data through LVDS signals. For the LVDS transmitter and receiver, the input and output pins of Cyclone IV devices support serialization and deserialization through internal logic.

The BLVDS extends the benefits of LVDS to multipoint applications such as bidirectional backplanes. The loading effect and the need to terminate the bus at both ends for multipoint applications require BLVDS to drive out a higher current than LVDS to produce a comparable voltage swing. All the I/O banks of Cyclone IV devices support BLVDS for user I/O pins.

The RSDS and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI).

The PPDS standard is the next generation of the RSDS standard introduced by National Semiconductor Corporation. Cyclone IV devices meet the National Semiconductor Corporation PPDS Interface Specification and support the PPDS standard for outputs only. All the I/O banks of Cyclone IV devices support the PPDS standard for output pins only.

The LVDS standard does not require an input reference voltage, but it does require a 100- $\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side for the top and bottom I/O banks.

### **Board Design Considerations**

This section explains how to achieve the optimal performance from a Cyclone IV I/O interface and ensure first-time success in implementing a functional design with optimal signal quality. You must consider the critical issues of controlled impedance of traces and connectors, differential routing, and termination techniques to get the best performance from Cyclone IV devices.

Use the following general guidelines to improve signal quality:

- Base board designs on controlled differential impedance. Calculate and compare all parameters, such as trace width, trace thickness, and the distance between two differential traces.

- Maintain equal distance between traces in differential I/O standard pairs as much as possible. Routing the pair of traces close to each other maximizes the common-mode rejection ratio (CMRR).

- Longer traces have more inductance and capacitance. These traces must be as short as possible to limit signal integrity issues.

- Place termination resistors as close to receiver input pins as possible.

- Use surface mount components.

- Avoid 90° corners on board traces.

- Use high-performance connectors.

- Design backplane and card traces so that trace impedance matches the impedance of the connector and termination.

- Keep an equal number of vias for both signal traces.

- Create equal trace lengths to avoid skew between signals. Unequal trace lengths result in misplaced crossing points and decrease system margins as the TCCS value increases.

- Limit vias because they cause discontinuities.

- Keep switching transistor-to-transistor logic (TTL) signals away from differential signals to avoid possible noise coupling.

- Do not route TTL clock signals to areas under or above the differential signals.

- Analyze system-level signals.

- **To** For PCB layout guidelines, refer to *AN* 224: *High-Speed Board Layout Guidelines* and *AN* 315: *Guidelines for Designing High-Speed FPGA PCBs*.

### **Software Overview**

Cyclone IV devices high-speed I/O system interfaces are created in core logic by a Quartus II software megafunction because they do not have a dedicated circuit for the SERDES. Cyclone IV devices use the I/O registers and LE registers to improve the timing performance and support the SERDES. The Quartus II software allows you to design your high-speed interfaces using ALTLVDS megafunction. This megafunction

For more information about the operation of the Micron P30 Parallel NOR and P33 Parallel NOR flash memories, search for the keyword "P30" or "P33" on the Micron website (www.micron.com) to obtain the P30 or P33 family datasheet.

### **Single-Device AP Configuration**

The following groups of interface pins are supported in Micron P30 and P33 flash memories:

- Control pins

- Address pins

- Data pins

The following control signals are from the supported parallel flash memories:

- CLK

- active-low reset (RST#)

- active-low chip enable (CE#)

- active-low output enable (OE#)

- active-low address valid (ADV#)

- active-low write enable (WE#)

The supported parallel flash memories output a control signal (WAIT) to Cyclone IV E devices to indicate when synchronous data is ready on the data bus. Cyclone IV E devices have a 24-bit address bus connecting to the address bus (A[24:1]) of the flash memory. A 16-bit bidirectional data bus (DATA[15..0]) provides data transfer between the Cyclone IV E device and the flash memory.

The following control signals are from the Cyclone IV E device to flash memory:

- DCLK

- active-low hard rest (nRESET)

- active-low chip enable (FLASH\_nCE)

- active-low output enable for the DATA [15..0] bus and WAIT pin (nOE)

- active-low address valid signal and is used to write data into the flash (nAVD)

- active-low write enable and is used to write data into the flash (nWE)

- The **.rbf** used by the JRunner software driver cannot be a compressed **.rbf** because the JRunner software driver uses JTAG-based configuration. During JTAG-based configuration, the real-time decompression feature is not available.

- **C** For more information about the JRunner software driver, refer to *AN* 414: JRunner *Software Driver: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera website at (www.altera.com).

### **Combining JTAG and AS Configuration Schemes**

You can combine the AS configuration scheme with the JTAG-based configuration (Figure 8–28). This setup uses two 10-pin download cable headers on the board. One download cable is used in JTAG mode to configure the Cyclone IV device directly through the JTAG interface. The other download cable is used in AS mode to program the serial configuration device in-system through the AS programming interface. If you try configuring the device using both schemes simultaneously, JTAG configuration takes precedence and AS configuration terminates.

# 11. Power Requirements for Cyclone IV Devices

#### CYIV-51011-1.3

This chapter describes information about external power supply requirements, hot-socketing specifications, power-on reset (POR) requirements, and their implementation in Cyclone IV devices.

This chapter includes the following sections:

- "External Power Supply Requirements" on page 11–1

- "Hot-Socketing Specifications" on page 11–2

- "Hot-socketing Feature Implementation" on page 11–3

- "Power-On Reset Circuitry" on page 11–3

# **External Power Supply Requirements**

This section describes the different external power supplies required to power Cyclone IV devices. Table 11–1 and Table 11–2 list the descriptions of external power supply pins for Cyclone IV GX and Cyclone IV E devices, respectively.

**To** For power supply pin connection guidelines and power regulator sharing, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

| Power Supply Pin   | Nominal Voltage Level (V)    | Description                                                                                                 |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|

| VCCINT             | 1.2                          | Core voltage, PCI Express (PCIe) hard IP block, and transceiver physical coding sublayer (PCS) power supply |

| VCCA (1)           | 2.5                          | PLL analog power supply                                                                                     |

| VCCD_PLL           | 1.2                          | PLL digital power supply                                                                                    |

| VCCIO (2)          | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply                                                                                      |

| VCC_CLKIN (3), (4) | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | Differential clock input pins power supply                                                                  |

| VCCH_GXB           | 2.5                          | Transceiver output (TX) buffer power supply                                                                 |

| VCCA_GXB           | 2.5                          | Transceiver physical medium attachment (PMA) and auxiliary power supply                                     |

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Actual lock time depends on the transition density of the incoming data and the ppm difference between the receiver input reference clock and the upstream transmitter reference clock.

Transition from the LTD state to the LTR state occurs when either of the following conditions is met:

- Signal detection circuitry indicates the absence of valid signal levels at the receiver input buffer. This condition is valid for PCI Express (PIPE) mode only. CDR transitions are not dependent on signal detection circuitry in other modes.

- The recovered clock is not within the configured ppm frequency threshold setting with respect to CDR clocks from multipurpose PLLs.

In automatic lock mode, the switch from LTR to LTD states is indicated by the assertion of the rx\_freqlocked signal and the switch from LTD to LTR states indicated by the de-assertion of the rx\_freqlocked signal.

### **Manual Lock Mode**

State transitions are controlled manually by using rx\_locktorefclk and rx\_locktodata ports. The LTR/LTD controller sets the CDR state depending on the logic level on the rx\_locktorefclk and rx\_locktodata ports. This mode provides the flexibility to control the CDR for a reduced lock time compared to the automatic lock mode. In automatic lock mode, the LTR/LTD controller relies on the ppm detector and the phase relationship detector to set the CDR in LTR or LTD mode. The ppm detector and phase relationship detector reaction times can be too long for some applications that require faster CDR lock time.

In manual lock mode, the rx\_freqlocked signal is asserted when the CDR is in LTD state and de-asserted when CDR is in LTR state. For descriptions of rx\_locktorefclk and rx\_locktodata port controls, refer to Table 1–27 on page 1–87.

IF you do not enable the optional rx\_locktorefclk and rx\_locktodata ports, the Quartus II software automatically configures the LTR/LTD controller in automatic lock mode.

The recommended transceiver reset sequence varies depending on the CDR lock mode. For more information about the reset sequence recommendations, refer to the *Reset Control and Power Down for Cyclone IV GX Devices* chapter.

### Deserializer

The deserializer converts received serial data from the receiver input buffer to parallel 8- or 10-bit data. Serial data is assumed to be received from the LSB to the MSB. The deserializer operates with the high-speed recovered clock from the CDR with the frequency at half of the serial data rate.

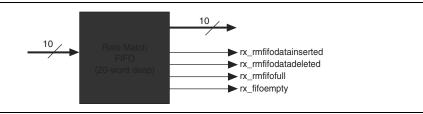

### **Rate Match FIFO**

In asynchronous systems, the upstream transmitter and local receiver can be clocked with independent reference clocks. Frequency differences in the order of a few hundred ppm can corrupt the data when latching from the recovered clock domain (the same clock domain as the upstream transmitter reference clock) to the local receiver reference clock domain. Figure 1–21 shows the rate match FIFO block diagram.

Figure 1–21. Rate Match FIFO Block Diagram

The rate match FIFO compensates for small clock frequency differences of up to  $\pm 300$  ppm (600 ppm total) between the upstream transmitter and the local receiver clocks by performing the following functions:

- Insert skip symbols when the local receiver reference clock frequency is greater than the upstream transmitter reference clock frequency

- Delete skip symbols when the local receiver reference clock frequency is less than the upstream transmitter reference clock frequency

The 20-word deep rate match FIFO and logics control insertion and deletion of skip symbols, depending on the ppm difference. The operation begins after the word aligner synchronization status (rx\_syncstatus) is asserted.

P

Rate match FIFO is only supported with 8B/10B encoded data and the word aligner in automatic synchronization state machine mode.

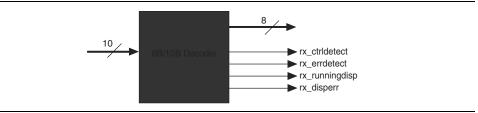

### **8B/10B Decoder**

The 8B/10B decoder receives 10-bit data and decodes it into an 8-bit data and a 1-bit control identifier. The decoder is compliant with Clause 36 of the IEEE 802.3 specification.

Figure 1–22 shows the 8B/10B decoder block diagram.

#### Figure 1–22. 8B/10B Decoder Block Diagram

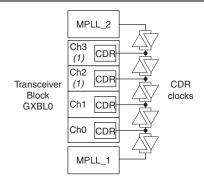

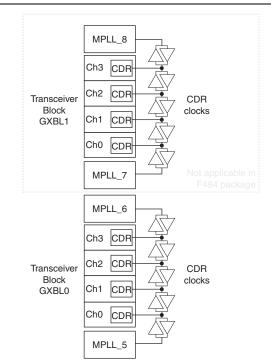

The CDR unit in each receiver channel gets the CDR clocks from one of the two multipurpose PLLs directly adjacent to the transceiver block. The CDR clocks distribution network is segmented by bidirectional tri-state buffers as shown in Figure 1–29 and Figure 1–30. This requires the CDR clocks from either one of the two multipurpose PLLs to drive a number of contiguous segmented paths to reach the intended receiver channel. Interleaving the CDR clocks from the two multipurpose PLLs is not supported.

For example, based on Figure 1–29, a combination of MPLL\_1 driving receiver channels 0, 1, and 3, while MPLL\_2 driving receiver channel 2 is not supported. In this case, only one multipurpose PLL can be used for the receiver channels.

#### Figure 1–29. CDR Clocking for Transceiver Channels in F324 and Smaller Packages

#### Note to Figure 1-29:

(1) Transceiver channels 2 and 3 are not available for devices in F169 and smaller packages.

#### Figure 1–30. CDR Clocking for Transceiver Channels in F484 and Larger Packages

Serial loopback mode can only be dynamically enabled or disabled during user mode by performing a dynamic channel reconfiguration.

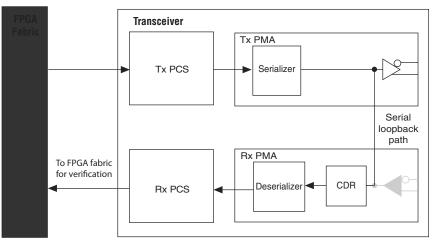

Figure 1–71. Serial Loopback Path<sup>(1)</sup>

Note to Figure 1–71:

(1) Grayed-Out Blocks are Not Active in this mode.

### **Reverse Serial Loopback**

The reverse serial loopback mode is available for all functional modes except for XAUI mode. The two reverse serial loopback options from the receiver to the transmitter are:

- Pre-CDR mode where data received through the RX input buffer is looped back to the TX output buffer using the **Reverse serial loopback (pre-CDR)** option

- Post-CDR mode where retimed data through the receiver CDR from the RX input buffer is looped back to the TX output buffer using the Reverse serial loopback option

The received data is also available to the FPGA logic. In the transmitter channel, only the transmitter buffer is active.

- The transmitter pre-emphasis feature is not available in reverse serial loopback (pre-CDR) mode.

- Reverse serial loopback modes can only be dynamically enabled or disabled during user mode by performing a dynamic channel reconfiguration.

| Block                 | Port Name          | Input/<br>Output    | Clock Domain                                                                                                                                                                                        | Description                                                                                                                                                                                                               |

|-----------------------|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                    |                     |                                                                                                                                                                                                     | Transceiver block power down.                                                                                                                                                                                             |

|                       | gxb_powerdown      | Input               | Asynchronous signal                                                                                                                                                                                 | <ul> <li>When asserted, all digital and analog circuitry in the PCS,<br/>HSSI, CDR, and PCIe modules are powered down.</li> </ul>                                                                                         |

|                       |                    |                     |                                                                                                                                                                                                     | <ul> <li>Asserting the gxb_powerdown signal does not power<br/>down the refclk buffers.</li> </ul>                                                                                                                        |

| Reset & Power<br>Down | tx_digitalreset    | Input               | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles.                                                                                                                 | Transmitter PCS reset. <ul> <li>When asserted, the transmitter PCS blocks are reset.</li> </ul>                                                                                                                           |

|                       | rx_analogreset     | Input               | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles.                                                                                                                 | <ul> <li>Receiver PMA reset.</li> <li>When asserted, analog circuitry in the receiver PMA block is reset.</li> </ul>                                                                                                      |

|                       | rx_digitalreset    | Input               | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles.                                                                                                                 | Receiver PCS reset. <ul> <li>When asserted, the receiver PCS blocks are reset.</li> </ul>                                                                                                                                 |

|                       |                    | Input               | Clock signal                                                                                                                                                                                        | Dynamic reconfiguration clock.                                                                                                                                                                                            |

|                       | reconfig_clk Input |                     |                                                                                                                                                                                                     | <ul> <li>Also used for offset cancellation except in PIPE mode.</li> </ul>                                                                                                                                                |

| Reconfiguration       |                    | mput                | olook olghai                                                                                                                                                                                        | <ul> <li>For the supported frequency range for this clock, refer to<br/>the Cyclone IV Device Data Sheet chapter.</li> </ul>                                                                                              |

|                       | reconfig_togxb     | Input               | Asynchronous signal                                                                                                                                                                                 | From the dynamic reconfiguration controller.                                                                                                                                                                              |

|                       | reconfig_fromgxb   | Output              | Asynchronous signal                                                                                                                                                                                 | To the dynamic reconfiguration controller.                                                                                                                                                                                |

| Calibration Block     | cal_blk_clk        | Input               | Clock signal                                                                                                                                                                                        | Clock for the transceiver calibration block.                                                                                                                                                                              |

| Galipiation Diock     | cal_blk_powerdown  | Input               | Asynchronous signal                                                                                                                                                                                 | Calibration block power down control.                                                                                                                                                                                     |

|                       |                    |                     |                                                                                                                                                                                                     | BIST or PRBS test completion indicator.                                                                                                                                                                                   |

|                       | rx_bistdone        | rx_bistdone Output  | Asynchronous signal                                                                                                                                                                                 | <ul> <li>A high level during BIST test mode indicates the verifier<br/>either receives complete pattern cycle or detects an error<br/>and stays asserted until being reset using the<br/>rx_digitalreset port.</li> </ul> |

| Test Mode             |                    |                     |                                                                                                                                                                                                     | <ul> <li>A high level during PRBS test mode indicates the verifier<br/>receives complete pattern cycle and stays asserted until<br/>being reset using the rx_digitalreset port.</li> </ul>                                |

|                       |                    |                     |                                                                                                                                                                                                     | BIST or PRBS verifier error indicator                                                                                                                                                                                     |

| r                     | rx_bisterr Output  | Asynchronous signal | <ul> <li>In BIST test mode, the signal stays asserted upon detecting<br/>an error until being reset using the rx_digitalreset<br/>port.</li> </ul>                                                  |                                                                                                                                                                                                                           |

|                       |                    |                     | <ul> <li>In PRBS test mode, the signal asserts for a minimum of 3<br/>rx_clkout clock cycles upon detecting an error and<br/>deasserts if the following PRBS sequence contains no error.</li> </ul> |                                                                                                                                                                                                                           |

# Table 1–29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for Cyclone IV GX (Part 2 of 2)

# **Document Revision History**

Table 1–30 lists the revision history for this chapter.

| Table 1-30. | Document | Revision   | History  |

|-------------|----------|------------|----------|

|             | Dooumont | 1101131011 | 11131019 |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|               |         | ■ Updated the GiGE row in Table 1–14.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| February 2015 | 3.7     | <ul> <li>Updated the "GIGE Mode" section.</li> </ul>                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|               |         | <ul> <li>Updated the note in the "Clock Frequency Compensation" section.</li> </ul>                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| October 2013  | 3.6     | Updated Figure 1–15 and Table 1–4.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| May 2013      | 3.5     | Updated Table 1–27 by setting "rx_locktodata" and "rx_locktorefclk" to "Input"                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|               |         | <ul> <li>Updated the data rate for the V-by-one protocol and the F324 package support in<br/>HD-SDI in Table 1–1.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |  |  |

| October 2012  | 3.4     | ■ Updated note (1) to Figure 1–27.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|               |         | <ul> <li>Added latency information to Figure 1–67.</li> </ul>                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| November 2011 | 3.3     | <ul> <li>Updated "Word Aligner" and "Basic Mode" sections.</li> </ul>                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| November 2011 | 3.3     | ■ Updated Figure 1–37.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|               |         | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| December 2010 |         | ■ Updated Table 1–1, Table 1–5, Table 1–11, Table 1–14, Table 1–24, Table 1–25, Table 1–26, Table 1–27, Table 1–28, and Table 1–29.                                                                                                                                                                                                                                               |  |  |  |  |  |

|               | 3.2     | <ul> <li>Updated "8B/10B Encoder", "Transmitter Output Buffer", "Receiver Input Buffer",<br/>"Clock Data Recovery", "Miscellaneous Transmitter PCS Features", "Miscellaneous<br/>Receiver PCS Feature", "Input Reference Clocking", "PCI Express (PIPE) Mode",<br/>"Channel Deskewing", "Lane Synchronization", "Serial Loopback", and "Self Test<br/>Modes" sections.</li> </ul> |  |  |  |  |  |

|               |         | ■ Added Figure 1–9, Figure 1–10, Figure 1–19, Figure 1–20, and Figure 1–43.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               |         | ■ Updated Figure 1–53, Figure 1–55, Figure 1–59, Figure 1–60, Figure 1–69, Figure 1–70, Figure 1–71, Figure 1–72, Figure 1–73, and Figure 1–74.                                                                                                                                                                                                                                   |  |  |  |  |  |

| November 2010 | 3.1     | Updated Introductory information.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|               |         | <ul> <li>Updated information for the Quartus II software version 10.0 release.</li> </ul>                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| July 2010     | 3.0     | <ul> <li>Reset control, power down, and dynamic reconfiguration information moved to<br/>new Cyclone IV Reset Control and Power Down and Cyclone IV Dynamic<br/>Reconfiguration chapters.</li> </ul>                                                                                                                                                                              |  |  |  |  |  |

| Chapter Revision Dates  | v      |

|-------------------------|--------|

| Additional Information  |        |

| How to Contact Altera   | Info-1 |

| Typographic Conventions | Info–1 |

# Section I. Device Datasheet

### Chapter 1. Cyclone IV Device Datasheet

| Operating Conditions                              | 1–1  |

|---------------------------------------------------|------|

| Absolute Maximum Ratings                          | 1–2  |

| Maximum Allowed Overshoot or Undershoot Voltage   |      |

| Recommended Operating Conditions                  |      |

| ESD Performance                                   |      |

| DC Characteristics                                | 1–7  |

| Supply Current                                    |      |

| Bus Hold                                          | 1–7  |

| OCT Specifications                                | 1–8  |

| Pin Capacitance                                   |      |

| Internal Weak Pull-Up and Weak Pull-Down Resistor | 1–11 |

| Hot-Socketing                                     | 1–11 |

| Schmitt Trigger Input                             |      |

| I/O Standard Specifications                       | 1–12 |

| Power Consumption                                 |      |

| Switching Characteristics                         | 1–16 |

| Transceiver Performance Specifications            | 1–17 |

| Core Performance Specifications                   | 1–23 |

| Clock Tree Specifications                         |      |

| PLL Specifications                                | 1–24 |

| Embedded Multiplier Specifications                | 1–26 |

| Memory Block Specifications                       | 1–26 |

| Configuration and JTAG Specifications             | 1–26 |

| Periphery Performance                             |      |

| High-Speed I/O Specifications                     |      |

| External Memory Interface Specifications          | 1–32 |

| Duty Cycle Distortion Specifications              |      |

| OCT Calibration Timing Specification              |      |

| IOE Programmable Delay                            | 1–34 |

| I/O Timing                                        | 1–37 |

| Glossary                                          |      |

| Document Revision History                         | 1–42 |

- **\*** For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interfaces Handbook*.

- Actual achievable frequency depends on design- and system-specific factors. Perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

### **High-Speed I/O Specifications**

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices. For definitions of high-speed timing specifications, refer to "Glossary" on page 1–37.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

| 0 milest                                             |                                          | C6  |     | C7, I7 |     |     | C8, A7 |     |     | C8L, I8L |     |     | C9L   |     |     |       |      |

|------------------------------------------------------|------------------------------------------|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-------|-----|-----|-------|------|

| Symbol Modes                                         |                                          | Min | Тур | Max    | Min | Тур | Max    | Min | Тур | Max      | Min | Тур | Max   | Min | Тур | Max   | Unit |

|                                                      | ×10                                      | 5   |     | 180    | 5   |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

|                                                      | ×8                                       | 5   |     | 180    | 5   | —   | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   | —   | 132.5 | MHz  |

| f <sub>HSCLK</sub><br>(input clock                   | ×7                                       | 5   |     | 180    | 5   |     | 155.5  | 5   | _   | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

| (input clock frequency)                              | ×4                                       | 5   |     | 180    | 5   |     | 155.5  | 5   | _   | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

| 1 37                                                 | ×2                                       | 5   |     | 180    | 5   |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

|                                                      | ×1                                       | 5   |     | 360    | 5   |     | 311    | 5   | _   | 311      | 5   |     | 311   | 5   |     | 265   | MHz  |

|                                                      | ×10                                      | 100 |     | 360    | 100 |     | 311    | 100 | _   | 311      | 100 |     | 311   | 100 |     | 265   | Mbps |

|                                                      | ×8                                       | 80  |     | 360    | 80  |     | 311    | 80  |     | 311      | 80  |     | 311   | 80  |     | 265   | Mbps |

| Device<br>operation in                               | ×7                                       | 70  | —   | 360    | 70  | —   | 311    | 70  |     | 311      | 70  | —   | 311   | 70  | —   | 265   | Mbps |

| Mbps                                                 | ×4                                       | 40  | —   | 360    | 40  | —   | 311    | 40  |     | 311      | 40  | —   | 311   | 40  | —   | 265   | Mbps |

|                                                      | ×2                                       | 20  |     | 360    | 20  |     | 311    | 20  | _   | 311      | 20  |     | 311   | 20  |     | 265   | Mbps |

|                                                      | ×1                                       | 10  | —   | 360    | 10  | —   | 311    | 10  |     | 311      | 10  | —   | 311   | 10  | —   | 265   | Mbps |

| t <sub>DUTY</sub>                                    | —                                        | 45  |     | 55     | 45  |     | 55     | 45  | _   | 55       | 45  |     | 55    | 45  |     | 55    | %    |

| Transmitter<br>channel-to-<br>channel skew<br>(TCCS) | _                                        | _   | _   | 200    | _   | _   | 200    | _   | _   | 200      | _   | _   | 200   | _   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)                      | _                                        | _   | _   | 500    | _   | _   | 500    | _   | _   | 550      | _   | _   | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                                    | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500 | _      | _   | 500 |          | _   | 500 |       | _   | 500 |       | ps   |

| t <sub>FALL</sub>                                    | 20 – 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _      | _   | 500 | _      | _   | 500 | _        | _   | 500 |       | _   | 500 |       | ps   |

### Table 1-46. Glossary (Part 3 of 5)

| Letter | Term                                                   | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|--------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|        | R <sub>L</sub>                                         | Receiver differential input discrete resistor (external to Cyclone IV devices).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| R      | Receiver Input<br>Waveform                             | Receiver input waveform for LVDS and LVPECL differential standards:<br>Single-Ended Waveform<br>Positive Channel (p) = V <sub>IH</sub><br>Negative Channel (n) = V <sub>IL</sub><br>Ground<br>Differential Waveform (Mathematical Function of Positive & Negative Channel)<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$ |  |  |  |  |  |  |  |

|        | Receiver input<br>skew margin<br>(RSKM)                | High-speed I/O block: The total margin left after accounting for the sampling window and TCCS.<br>RSKM = (TUI – SW – TCCS) / 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| S      | Single-ended<br>voltage-<br>referenced I/O<br>Standard | VCCIO         VOH         VIH(DC)         VIH(DC)         VIH(DC)         VIL(QC)         VIL(QC)         VIL(QC)         VIL(QC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         VIL(AC)         Values. The AC values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. After the receiver input crosses the AC value, the receiver changes to the new logic state. The new logic state is then maintained as long as the input stays beyond the DC threshold. This approach is intended to provide predictable receiver timing in the presence of input waveform <i>ringing</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|        | SW (Sampling<br>Window)                                | High-speed I/O block: The period of time during which the data must be valid to capture it correctly. The setup and hold times determine the ideal strobe position in the sampling window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

### Table 1-46. Glossary (Part 5 of 5)

| Letter | Term                    | Definitions                                                                                                                                                                                    |

|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | V <sub>CM(DC)</sub>     | DC common mode input voltage.                                                                                                                                                                  |

|        | V <sub>DIF(AC)</sub>    | AC differential input voltage: The minimum AC input differential voltage required for switching.                                                                                               |

|        | V <sub>DIF(DC)</sub>    | DC differential input voltage: The minimum DC input differential voltage required for switching.                                                                                               |

|        | V <sub>ICM</sub>        | Input common mode voltage: The common mode of the differential signal at the receiver.                                                                                                         |

|        | V <sub>ID</sub>         | Input differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                  |

|        | V <sub>IH</sub>         | Voltage input high: The minimum positive voltage applied to the input that is accepted by the device as a logic high.                                                                          |

|        | V <sub>IH(AC)</sub>     | High-level AC input voltage.                                                                                                                                                                   |

|        | V <sub>IH(DC)</sub>     | High-level DC input voltage.                                                                                                                                                                   |

|        | V <sub>IL</sub>         | Voltage input low: The maximum positive voltage applied to the input that is accepted by the device as a logic low.                                                                            |

|        | V <sub>IL (AC)</sub>    | Low-level AC input voltage.                                                                                                                                                                    |

|        | V <sub>IL (DC)</sub>    | Low-level DC input voltage.                                                                                                                                                                    |

|        | V <sub>IN</sub>         | DC input voltage.                                                                                                                                                                              |

|        | V <sub>OCM</sub>        | Output common mode voltage: The common mode of the differential signal at the transmitter.                                                                                                     |

| V      | V <sub>OD</sub>         | Output differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. $V_{OD} = V_{OH} - V_{OL}$ . |