### Intel - EP4CE10F17C7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 645                                                      |

| Number of Logic Elements/Cells | 10320                                                    |

| Total RAM Bits                 | 423936                                                   |

| Number of I/O                  | 179                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10f17c7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Chapter Revision Dates**

The chapters in this document, Cyclone IV Device Handbook,, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

- Chapter 1. Cyclone IV FPGA Device Family Overview Revised: March 2016 Part Number: CYIV-51001-2.0

- Chapter 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices Revised: *November* 2009 Part Number: *CYIV-51002-1.0*

- Chapter 3. Memory Blocks in Cyclone IV Devices Revised: *November* 2011 Part Number: *CYIV-51003-1.1*

- Chapter 4. Embedded Multipliers in Cyclone IV Devices Revised: *February* 2010 Part Number: *CYIV-51004-1.1*

- Chapter 5. Clock Networks and PLLs in Cyclone IV Devices Revised: October 2012 Part Number: CYIV-51005-2.4

- Chapter 6. I/O Features in Cyclone IV Devices Revised: March 2016 Part Number: CYIV-51006-2.7

- Chapter 7. External Memory Interfaces in Cyclone IV Devices Revised: March 2016 Part Number: CYIV-51007-2.6

- Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices Revised: *May 2013* Part Number: *CYIV-51008-1.7*

- Chapter 9. SEU Mitigation in Cyclone IV Devices Revised: May 2013 Part Number: CYIV-51009-1.3

- Chapter 10. JTAG Boundary-Scan Testing for Cyclone IV Devices Revised: December 2013 Part Number: CYIV-51010-1.3

- Chapter 11. Power Requirements for Cyclone IV Devices Revised: May 2013 Part Number: CYIV-51011-1.3

Table 1–2 lists Cyclone IV GX device resources.

| Resources                            | EP4CGX15 | EP4CGX22         | EP4CGX30 | EP4CGX30<br>(2)   | EP4CGX50          | EP4CGX75          | EP4CGX110         | EP4CGX150     |

|--------------------------------------|----------|------------------|----------|-------------------|-------------------|-------------------|-------------------|---------------|

| Logic elements (LEs)                 | 14,400   | 21,280           | 29,440   | 29,440            | 49,888            | 73,920            | 109,424           | 149,760       |

| Embedded memory (Kbits)              | 540      | 756              | 1,080    | 1,080             | 2,502             | 4,158             | 5,490             | 6,480         |

| Embedded 18 × 18 multipliers         | 0        | 40               | 80       | 80                | 140               | 198               | 280               | 360           |

| General purpose PLLs                 | 1        | 2                | 2        | 4 (4)             | 4 (4)             | 4 (4)             | 4 (4)             | 4 <i>(4)</i>  |

| Multipurpose PLLs                    | 2 (5)    | 2 <sup>(5)</sup> | 2 (5)    | 2 <sup>(5)</sup>  | 4 (5)             | 4 (5)             | 4 (5)             | 4 (5)         |

| Global clock networks                | 20       | 20               | 20       | 30                | 30                | 30                | 30                | 30            |

| High-speed transceivers (6)          | 2        | 4                | 4        | 4                 | 8                 | 8                 | 8                 | 8             |

| Transceiver maximum data rate (Gbps) | 2.5      | 2.5              | 2.5      | 3.125             | 3.125             | 3.125             | 3.125             | 3.125         |

| PCIe (PIPE) hard IP blocks           | 1        | 1                | 1        | 1                 | 1                 | 1                 | 1                 | 1             |

| User I/O banks                       | g (7)    | g (7)            | g (7)    | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <i>(8)</i> |

| Maximum user I/O <sup>(9)</sup>      | 72       | 150              | 150      | 290               | 310               | 310               | 475               | 475           |

Table 1–2. Resources for the Cyclone IV GX Device Family

Notes to Table 1-2:

(1) Applicable for the F169 and F324 packages.

(2) Applicable for the F484 package.

(3) Only two multipurpose PLLs for F484 package.

(4) Two of the general purpose PLLs are able to support transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(5) You can use the multipurpose PLLs for general purpose clocking when they are not used to clock the transceivers. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(6) If PCIe ×1, you can use the remaining transceivers in a quad for other protocols at the same or different data rates.

(7) Including one configuration I/O bank and two dedicated clock input I/O banks for HSSI reference clock input.

(8) Including one configuration I/O bank and four dedicated clock input I/O banks for HSSI reference clock input.

(9) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

# **Address Clock Enable Support**

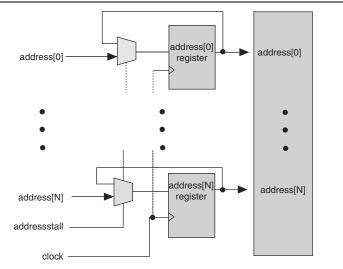

Cyclone IV devices M9K memory blocks support an active-low address clock enable, which holds the previous address value for as long as the addressstall signal is high (addressstall = '1'). When you configure M9K memory blocks in dual-port mode, each port has its own independent address clock enable.

Figure 3–2 shows an address clock enable block diagram. The address register output feeds back to its input using a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal.

$\label{eq:Figure 3-2. Cyclone IV Devices Address Clock Enable Block Diagram$

The address clock enable is typically used to improve the effectiveness of cache memory applications during a cache-miss. The default value for the address clock enable signals is low.

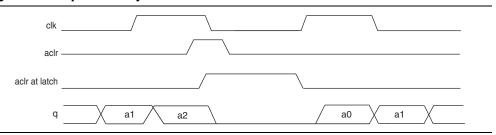

## **Asynchronous Clear**

Cyclone IV devices support asynchronous clears for read address registers, output registers, and output latches only. Input registers other than read address registers are not supported. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are immediately seen. If your RAM does not use output registers, you can still clear the RAM outputs using the output latch asynchronous clear feature.

Asserting asynchronous clear to the read address register during a read operation may corrupt the memory content.

Figure 3–5 shows the functional waveform for the asynchronous clear feature.

Figure 3–5. Output Latch Asynchronous Clear Waveform

You can selectively enable asynchronous clears per logical memory using the Quartus II RAM MegaWizard<sup>™</sup> Plug-In Manager.

**For more information, refer to the** *RAM Megafunction User Guide*.

There are three ways to reset registers in the M9K blocks:

- Power up the device

- Use the aclr signal for output register only

- Assert the device-wide reset signal using the DEV\_CLRn option

### **Memory Modes**

Cyclone IV devices M9K memory blocks allow you to implement fully-synchronous SRAM memory in multiple modes of operation. Cyclone IV devices M9K memory blocks do not support asynchronous (unregistered) memory inputs.

M9K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port

- Shift-register

- ROM

- FIFO

3–7

# **Document Revision History**

Table 4–3 lists the revision history for this chapter.

### Table 4–3. Document Revision History

| Date          | Version | Changes                                                                                      |

|---------------|---------|----------------------------------------------------------------------------------------------|

| February 2010 | 1.1     | Added Cyclone IV E devices in Table 4–1 for the Quartus II software version 9.1 SP1 release. |

| November 2009 | 1.0     | Initial release.                                                                             |

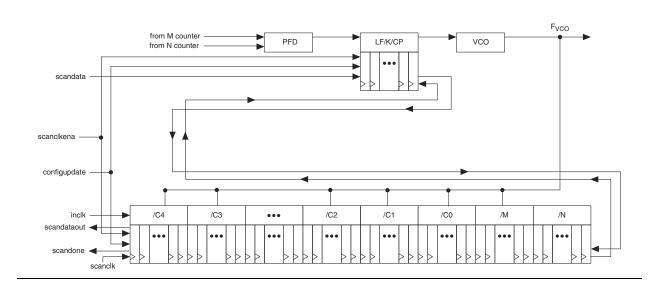

Figure 5–22 shows how to adjust PLL counter settings dynamically by shifting their new settings into a serial shift register chain or scan chain. Serial data shifts to the scan chain via the scandataport, and shift registers are clocked by scanclk. The maximum scanclk frequency is 100 MHz. After shifting the last bit of data, asserting the configupdate signal for at least one scanclk clock cycle synchronously updates the PLL configuration bits with the data in the scan registers.

The counter settings are updated synchronously to the clock frequency of the individual counters. Therefore, not all counters update simultaneously.

To reconfigure the PLL counters, perform the following steps:

- 1. The scanclkena signal is asserted at least one scanclk cycle prior to shifting in the first bit of scandata (D0).

- 2. Serial data (scandata) is shifted into the scan chain on the second rising edge of scanclk.

- 3. After all 144 bits have been scanned into the scan chain, the scanclkena signal is de-asserted to prevent inadvertent shifting of bits in the scan chain.

- 4. The configupdate signal is asserted for one scanclk cycle to update the PLL counters with the contents of the scan chain.

- 5. The scandone signal goes high indicating that the PLL is being reconfigured. A falling edge indicates that the PLL counters have been updated with new settings.

- 6. Reset the PLL using the areset signal if you make any changes to the M, N, post-scale output C counters, or the I<sub>CP</sub>, R, C settings.

- 7. You can repeat steps 1 through 5 to reconfigure the PLL any number of times.

Table 6–2 on page 6–7 shows the possible settings for I/O standards with current strength control. These programmable current strength settings are a valuable tool in helping decrease the effects of simultaneously switching outputs (SSO) in conjunction with reducing system noise. The supported settings ensure that the device driver meets the specifications for IOH and IOL of the corresponding I/O standard.

$\square$  When you use programmable current strength, on-chip series termination (R<sub>S</sub> OCT) is not available.

## **Slew Rate Control**

The output buffer for each Cyclone IV I/O pin provides optional programmable output slew-rate control. Table 6–2 on page 6–7 shows the possible slew rate option and the Quartus II default slew rate setting. However, these fast transitions may introduce noise transients in the system. A slower slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Because each I/O pin has an individual slew-rate control, you can specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges. Slew rate control is available for single-ended I/O standards with current strength of 8 mA or higher.

- You cannot use the programmable slew rate feature when using OCT with calibration.

- You cannot use the programmable slew rate feature when using the 3.0-V PCI, 3.0-V PCI-X, 3.3-V LVTTL, or 3.3-V LVCMOS I/O standards. Only the fast slew rate (default) setting is available.

## **Open-Drain Output**

Cyclone IV devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (for example, interrupt and write enable signals) that are asserted by multiple devices in your system.

### **Bus Hold**

Each Cyclone IV device user I/O pin provides an optional bus-hold feature. The bus-hold circuitry holds the signal on an I/O pin at its last-driven state. Because the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage in which noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals.

IF you enable the bus-hold feature, the device cannot use the programmable pull-up option. Disable the bus-hold feature when the I/O pin is configured for differential signals. Bus-hold circuitry is not available on dedicated clock pins.

Bus-hold circuitry is only active after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

The IOE registers in each I/O block share the same source for the preset or clear features. You can program preset or clear for each individual IOE, but you cannot use both features simultaneously. You can also program the registers to power-up high or low after configuration is complete. If programmed to power-up low, an asynchronous clear can control the registers. If programmed to power-up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of the active-low input of another device upon power-up. If one register in an IOE uses a preset or clear signal, all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

**\*** For more information about the input and output pin delay settings, refer to the *Area and Timing Optimization* chapter in volume 2 of the *Quartus II Handbook*.

### **PCI-Clamp Diode**

Cyclone IV devices provide an optional PCI-clamp diode enabled input and output for each I/O pin. Dual-purpose configuration pins support the diode in user mode if the specific pins are not used as configuration pins for the selected configuration scheme. For example, if you are using the active serial (AS) configuration scheme, you cannot use the clamp diode on the ASDO and nCSO pins in user mode. Dedicated configuration pins do not support the on-chip diode.

The PCI-clamp diode is available for the following I/O standards:

- 3.3-V LVTTL

- 3.3-V LVCMOS

- 3.0-V LVTTL

- 3.0-V LVCMOS

- 2.5-V LVTTL/LVCMOS

- PCI

- PCI-X

If the input I/O standard is one of the listed standards, the PCI-clamp diode is enabled by default in the Quartus II software.

# **OCT Support**

Cyclone IV devices feature OCT to provide I/O impedance matching and termination capabilities. OCT helps prevent reflections and maintain signal integrity while minimizing the need for external resistors in high pin-count ball grid array (BGA) packages. Cyclone IV devices provide I/O driver on-chip impedance matching and R<sub>S</sub> OCT for single-ended outputs and bidirectional pins.

When using R<sub>S</sub> OCT, programmable current strength is not available.

There are two ways to implement OCT in Cyclone IV devices:

- OCT with calibration

- OCT without calibration

| ] | Chapter 6:<br>I/O Banks        |

|---|--------------------------------|

|   | I/O Fe                         |

|   | atures                         |

|   | I/O Features in Cyclone IV Dev |

| ] | ne IV Dev                      |

ices

#### Table 6-4. Number of VREF Pins Per I/O Bank for Cyclone IV E Devices (Part 2 of 2)

| Device             |          | EP4CE6   |          |          | EP4CE10  |          |          | EP4CE15  |          |          | P4CE1    |          |          | EP4CE22  |          |          | EP4CE30  |          |          |          | 2<br>2<br>2<br>2<br>2 |          |          | EP4CE55  |          |          | EP4CE75  |          | EDAFE11E | 1446     |

|--------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| l/O<br>Bank<br>(1) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA              | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| 8                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2        | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4                     | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3        | 3        |

#### Note to Table 6-4:

(1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

| Table 6-5. | Number of VREF | <sup>:</sup> Pins Per I/O Bank | k for Cyclone IV GX Devices |

|------------|----------------|--------------------------------|-----------------------------|

|------------|----------------|--------------------------------|-----------------------------|

| Device                 | 4CGX15   | 4CG      | i <b>X22</b> |          | 4CGX30   |          | 400      | 4CGX50   |          | 4CGX75   |          | 4CGX110  |          |          | 4CGX150  |          |  |

|------------------------|----------|----------|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| <b>I/O Bank</b><br>(1) | 169-FBGA | 169-FBGA | 324-FBGA     | 169-FBGA | 324-FBGA | 484-FBGA | 484-FBGA | 672-FBGA | 484-FBGA | 672-FBGA | 484-FBGA | 672-FBGA | 896-FBGA | 484-FBGA | 672-FBGA | 896-FBGA |  |

| 3                      | 1        | -        | 1            |          | 1        | 3        | :        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |  |

| 4                      | 1        |          | 1            |          | 1        | 3        | :        | 3        | 3        | 3        |          | 3        |          |          | 3        |          |  |

| 5                      | 1        | -        | 1            |          | 1        | 3        | 3        |          | 3        |          | 3        |          |          | 3        |          |          |  |

| 6                      | 1        | -        | 1            |          | 1        |          | 3        |          | 3        |          | 3        |          |          | 3        |          |          |  |

| 7                      | 1        |          | 1            |          | 1        | 3        | 3        |          | 3        |          | 3        |          |          | 3        |          |          |  |

| 8 <i>(2)</i>           | 1        |          | 1            |          | 1        | 3        |          | 3        | 3        | }        |          | 3        |          |          | 3        |          |  |

### Notes to Table 6–5:

(1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

(2) Bank 9 does not have VREF pin. If input pins with VREF I/O standards are used in bank 9 during user mode, it shares the VREF pin in bank 8.

Each Cyclone IV I/O bank has its own VCCIO pins. Each I/O bank can support only one  $V_{CCIO}$  setting from among 1.2, 1.5, 1.8, 2.5, 3.0, or 3.3 V. Any number of supported single-ended or differential standards can be simultaneously supported in a single I/O bank, as long as they use the same  $V_{CCIO}$  levels for input and output pins.

In Cyclone IV devices, DQS is used only during write mode in DDR2 and DDR SDRAM interfaces. Cyclone IV devices ignore DQS as the read-data strobe because the PHY internally generates the read capture clock for read mode. However, you must connect the DQS pin to the DQS signal in DDR2 and DDR SDRAM interfaces, or to the CQ signal in QDR II SRAM interfaces.

- Cyclone IV devices do not support differential strobe pins, which is an optional feature in the DDR2 SDRAM device.

- When you use the Altera Memory Controller MegaCore<sup>®</sup> function, the PHY is instantiated for you. For more information about the memory interface data path, refer to the *External Memory Interface Handbook*.

- ALTMEMPHY is a self-calibrating megafunction, enhanced to simplify the implementation of the read-data path in different memory interfaces. The auto-calibration feature of ALTMEMPHY provides ease-of-use by optimizing clock phases and frequencies across process, voltage, and temperature (PVT) variations. You can save on the global clock resources in Cyclone IV devices through the ALTMEMPHY megafunction because you are not required to route the DQS signals on the global clock buses (because DQS is ignored for read capture). Resynchronization issues do not arise because no transfer occurs from the memory domain clock (DQS) to the system domain for capturing data DQ.

All I/O banks in Cyclone IV devices can support DQ and DQS signals with DQ-bus modes of ×8, ×9, ×16, ×18, ×32, and ×36 except Cyclone IV GX devices that do not support left I/O bank interface. DDR2 and DDR SDRAM interfaces use ×8 mode DQS group regardless of the interface width. For a wider interface, you can use multiple ×8 DQ groups to achieve the desired width requirement.

In the ×9, ×18, and ×36 modes, a pair of complementary DQS pins (CQ and CQ#) drives up to 9, 18, or 36 DQ pins, respectively, in the group, to support one, two, or four parity bits and the corresponding data bits. The ×9, ×18, and ×36 modes support the QDR II memory interface. CQ# is the inverted read-clock signal that is connected to the complementary data strobe (DQS or CQ#) pin. You can use any unused DQ pins as regular user I/O pins if they are not used as memory interface signals.

For more information about unsupported DQS and DQ groups of the Cyclone IV transceivers that run at ≥2.97 Gbps data rate, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

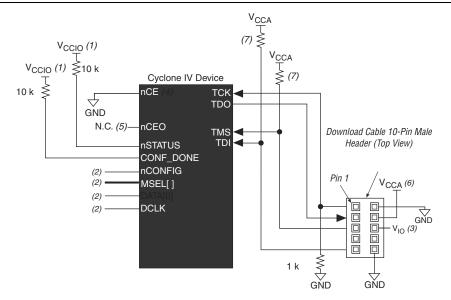

For device using V<sub>CCIO</sub> of 2.5, 3.0, and 3.3 V, refer to Figure 8–23. All I/O inputs must maintain a maximum AC voltage of 4.1 V because JTAG pins do not have the internal PCI clamping diodes to prevent voltage overshoot when using V<sub>CCIO</sub> of 2.5, 3.0, and 3.3 V. You must power up the V<sub>CC</sub> of the download cable with a 2.5-V supply from V<sub>CCA</sub>. For device using V<sub>CCIO</sub> of 1.2, 1.5, and 1.8 V, refer to Figure 8–24. You can power up the V<sub>CC</sub> of the download cable with the supply from V<sub>CCIO</sub>.

#### Notes to Figure 8-23:

- (1) Connect these pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) Connect the nCONFIG and MSEL pins to support a non-JTAG configuration scheme. If you only use JTAG configuration, connect the nCONFIG pin to logic-high and the MSEL pins to GND. In addition, pull DCLK and DATA[0] to either high or low, whichever is convenient on your board.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the device's V<sub>CCA</sub>. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*. When using the USB-Blaster, ByteBlaster II, ByteBlasterMV, and EthernetBlaster cables, this pin is a no connect.

- (4) The nCE pin must be connected to GND or driven low for successful JTAG configuration.

- (5) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (6) Power up the  $V_{CC}$  of the EthernetBlaster, ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from  $V_{CCA}$ . Third-party programmers must switch to 2.5 V. Pin 4 of the header is a  $V_{CC}$  power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the *MasterBlaster Serial/USB Communications Cable User Guide*.

- (7) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ ..

Table 9–7 lists the input and output ports that you must include in the atom.

Table 9–7. CRC Block Input and Output Ports

| Port                                                             | Input/Output | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <crcblock_name></crcblock_name>                                  | Input        | Unique identifier for the CRC block, and represents any identifier name that is legal for the given description language (for example, Verilog HDL, VHDL, and AHDL). This field is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .clk(< <i>clock source</i> >                                     | Input        | This signal designates the clock input of this cell. All operations of this cell are with respect to the rising edge of the clock. Whether it is the loading of the data into the cell or data out of the cell, it always occurs on the rising edge. This port is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <pre>.shiftnld (<shiftnld source="">)</shiftnld></pre>           | Input        | This signal is an input into the error detection block. If shiftnld=1, the data is shifted from the internal shift register to the regout at each rising edge of clk. If shiftnld=0, the shift register parallel loads either the pre-calculated CRC value or the update register contents, depending on the ldsrc port input. To do this, the shiftnld must be driven low for at least two clock cycles. This port is required.                                                                                                                                                                                                                                                                                                                                                                                     |

| .ldsrc (< <i>ldsrc</i><br><i>source</i> >)                       | Input        | This signal is an input into the error detection block. If ldsrc=0, the pre-computed CRC register is selected for loading into the 32-bit shift register at the rising edge of clk when shiftnld=0. If ldsrc=1, the signature register (result of the CRC calculation) is selected for loading into the shift register at the rising edge of clk when shiftnld=0. This port is ignored when shiftnld=1. This port is required.                                                                                                                                                                                                                                                                                                                                                                                       |

| .crcerror ( <crcerror<br>indicator<br/>output&gt;)</crcerror<br> | Output       | This signal is the output of the cell that is synchronized to the internal oscillator of the device (80-MHz internal oscillator) and not to the clk port. It asserts high if the error block detects that a SRAM bit has flipped and the internal CRC computation has shown a difference with respect to the pre-computed value. You must connect this signal either to an output pin or a bidirectional pin. If it is connected to an output pin, you can only monitor the CRC_ERROR pin (the core cannot access this output). If the CRC_ERROR signal is used by core logic to read error detection logic, you must connect this signal to a BIDIR pin. The signal is fed to the core indirectly by feeding a BIDIR pin that has its output enable port connected to V <sub>CC</sub> (see Figure 9–3 on page 9–8). |

| .regout ( <registered<br>output&gt;)</registered<br>             | Output       | This signal is the output of the error detection shift register synchronized to the $clk$ port to be read by core logic. It shifts one bit at each cycle, so you should clock the $clk$ signal 31 cycles to read out the 32 bits of the shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Recovering from CRC Errors**

The system that the Altera FPGA resides in must control device reconfiguration. After detecting an error on the CRC\_ERROR pin, strobing the nCONFIG low directs the system to perform the reconfiguration at a time when it is safe for the system to reconfigure the FPGA.

When the data bit is rewritten with the correct value by reconfiguring the device, the device functions correctly.

While soft errors are uncommon in Altera devices, certain high-reliability applications might require a design to account for these errors.

The user I/O pins and dual-purpose I/O pins have weak pull-up resistors, which are always enabled (after POR) before and during configuration. The weak pull up resistors are not enabled prior to POR.

A possible concern for semiconductor devices in general regarding hot socketing is the potential for latch up. Latch up can occur when electrical subsystems are hot socketed into an active system. During hot socketing, the signal pins may be connected and driven by the active system before the power supply can provide current to the  $V_{CC}$  of the device and ground planes. This condition can lead to latch up and cause a low-impedance path from  $V_{CC}$  to GND in the device. As a result, the device extends a large amount of current, possibly causing electrical damage.

The design of the I/O buffers and hot-socketing circuitry ensures that Cyclone IV devices are immune to latch up during hot-socketing.

# **Hot-socketing Feature Implementation**

The hot-socketing circuit does not include the CONF\_DONE, nCEO, and nSTATUS pins to ensure that they are able to operate during configuration. The expected behavior for these pins is to drive out during power-up and power-down sequences.

Altera uses GND as reference for hot-socketing operation and I/O buffer designs. To ensure proper operation, Altera recommends connecting the GND between boards before connecting the power supplies. This prevents the GND on your board from being pulled up inadvertently by a path to power through other components on your board. A pulled up GND can otherwise cause an out-of-specification I/O voltage or current condition with the Altera device.

# **Power-On Reset Circuitry**

Cyclone IV devices contain POR circuitry to keep the device in a reset state until the power supply voltage levels have stabilized during power up. During POR, all user I/O pins are tri-stated until the power supplies reach the recommended operating levels. In addition, the POR circuitry also ensures the V<sub>CCIO</sub> level of I/O banks that contain configuration pins reach an acceptable level before configuration is triggered.

The POR circuit of the Cyclone IV device monitors the V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> that contain configuration pins during power-on. You can power up or power down the V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> pins in any sequence. The V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> must have a monotonic rise to their steady state levels. All V<sub>CCA</sub> pins must be powered to 2.5V (even when PLLs are not used), and must be powered up and powered down at the same time.

After the Cyclone IV device enters the user mode, the POR circuit continues to monitor the  $V_{CCINT}$  and  $V_{CCA}$  pins so that a brown-out condition during user mode is detected. If the  $V_{CCINT}$  or  $V_{CCA}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. If the  $V_{CCIO}$  voltage sags during user mode, the POR circuit does not reset the device.

<sup>•</sup> For more information about the hot-socketing specification, refer to the *Cyclone IV Device Datasheet* chapter and the *Hot-Socketing and Power-Sequencing Feature and Testing for Altera Devices* white paper.

- Channel alignment is acquired if three additional aligned ||A|| columns are observed at the output of the deskew FIFOs of the four channels after alignment of the first ||A|| column.

- Channel alignment is indicated by the assertion of rx\_channelaligned signal.

- After acquiring channel alignment, if four misaligned ||A|| columns are seen at the output of the deskew FIFOs in all four channels with no aligned ||A|| columns in between, the rx\_channelaligned signal is deasserted, indicating loss of channel alignment.

Figure 1–65 shows lane skew at the receiver input and how the deskew FIFO uses the /A/ code group to align the channels.

Lane 0 Κ Κ R Κ R R Κ Κ R κ R Lane 1 Κ Κ R Κ R R Κ Κ R Κ R Lanes skew at receiver input Lane 2 Κ Κ R Κ R R Κ Κ R Κ R κ Κ R κ R R Κ κ R Κ R Lane 3 Lane 0 Κ Κ R Κ R R Κ Κ R Κ R Lane 1 Κ Κ R Κ R R κ Κ R Κ R Lanes are deskewed by lining up the "Align"/A/ code groups R κ R R κ к R R Lane 2 Κ Κ Κ R κ R R Κ Κ R R Κ Κ Κ Lane 3 /A/ column

### Figure 1-65. Deskew FIFO-Lane Skew at the Receiver Input

### **Lane Synchronization**

In XAUI mode, the word aligner is configured in automatic synchronization state machine mode that is compliant to the PCS synchronization state diagram specified in clause 48 of the IEEE P802.3ae specification. Table 1–23 lists the synchronization state machine parameters that implements the lane synchronization in XAUI mode.

Table 1–23. Synchronization State Machine Parameters <sup>(1)</sup>

| Parameter                                                                                 | Value |

|-------------------------------------------------------------------------------------------|-------|

| Number of valid synchronization (/K28.5/) code groups received to achieve synchronization | 4     |

| Number of erroneous code groups received to lose synchronization                          | 4     |

| Number of continuous good code groups received to reduce the error count by one           | 4     |

#### Note to Table 1–23:

(1) The word aligner supports 7-bit and 10-bit pattern lengths in XAUI mode.

| Port Name                  | Input/<br>Output | Clock Domain        | Description                                                                                                                                                                                                                                                                                                     |

|----------------------------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fixedclk                   | Input            | Clock signal        | 125-MHz clock for receiver detect and offset cancellation only in PIPE mode.                                                                                                                                                                                                                                    |

|                            |                  |                     | Receiver detect or reverse parallel loopback control.                                                                                                                                                                                                                                                           |

| tx_detectrxloop            | Input            | Asynchronous signal | <ul> <li>A high level in the P1 power state and tx_forcelecidle<br/>signal asserted begins the receiver detection operation to determine<br/>if there is a valid receiver downstream. This signal must be<br/>deasserted when the pipephydonestatus signal indicates<br/>receiver detect completion.</li> </ul> |

|                            |                  |                     | <ul> <li>A high level in the P0 power state with the tx_forceelecidle<br/>signal deasserted dynamically configures the channel to support<br/>reverse parallel loopback mode.</li> </ul>                                                                                                                        |

|                            |                  |                     | Force the 8B/10B encoder to encode with negative running disparity.                                                                                                                                                                                                                                             |

| tx_forcedisp<br>compliance | Input            | Asynchronous signal | <ul> <li>Assert only when transmitting the first byte of the PIPE-compliance<br/>pattern to force the 8B/10B encoder with a negative running<br/>disparity.</li> </ul>                                                                                                                                          |

| pipe8b10binvpolarity       | Input            | Asynchronous signal | Invert the polarity of every bit of the 10-bit input to the 8B/10B decoder                                                                                                                                                                                                                                      |

|                            |                  |                     | PIPE power state control.                                                                                                                                                                                                                                                                                       |

|                            |                  |                     | <ul> <li>Signal is 2 bits wide and is encoded as follows:</li> </ul>                                                                                                                                                                                                                                            |

| powerdn                    | Input            | Asynchronous signal | <ul> <li>2'b00: P0 (Normal operation)</li> </ul>                                                                                                                                                                                                                                                                |

| powerun                    | mput             | Asynchionous signal | <ul> <li>2'b01: P0s (Low recovery time latency, low power state)</li> </ul>                                                                                                                                                                                                                                     |

|                            |                  |                     | <ul> <li>2'b10: P1 (Longer recovery time latency, lower power state)</li> </ul>                                                                                                                                                                                                                                 |

|                            |                  |                     | <ul> <li>2'b11: P2 (Lowest power state)</li> </ul>                                                                                                                                                                                                                                                              |

| pipedatavalid              | Output           | N/A                 | Valid data and control on the rx_dataout and rx_ctrldetect ports indicator.                                                                                                                                                                                                                                     |

|                            |                  |                     | PHY function completion indicator.                                                                                                                                                                                                                                                                              |

| pipephydone<br>status      | Output           | Asynchronous signal | <ul> <li>Asserted for one clock cycle to communicate completion of several<br/>PHY functions, such as power state transition and receiver<br/>detection.</li> </ul>                                                                                                                                             |

|                            |                  |                     | Electrical idle detected or inferred at the receiver indicator.                                                                                                                                                                                                                                                 |

| pipeelecidle               | Output           | Asynchronous signal | <ul> <li>When electrical idle inference is used, this signal is driven high<br/>when it infers an electrical idle condition</li> </ul>                                                                                                                                                                          |

|                            |                  |                     | <ul> <li>When electrical idle inference is not used, the<br/>rx_signaldetect signal is inverted and driven on this port.</li> </ul>                                                                                                                                                                             |

cancellation process on the receiver channel.

The deassertion of the busy signal indicates proper completion of the offset

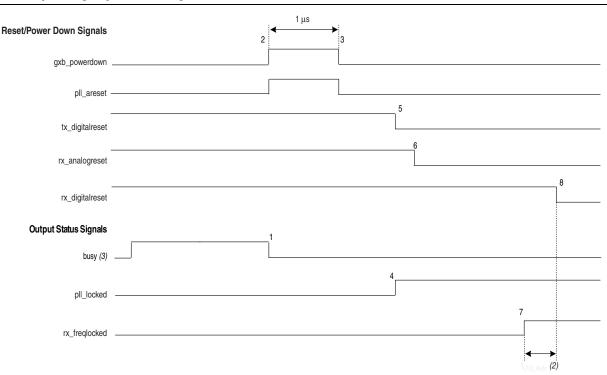

# Figure 2–13. Sample Reset Sequence of a Receiver and Transmitter Channels-Receiver CDR in Automatic Lock Mode with the Optional gxb\_powerdown Signal <sup>(1)</sup>

#### Notes to Figure 2-13:

- (1) The  $gxb\_powerdown$  signal must not be asserted during the offset cancellation sequence.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

# **Simulation Requirements**

The following are simulation requirements:

- The gxb\_powerdown port is optional. In simulation, if the gxb\_powerdown port is not instantiated, you must assert the tx\_digitalreset, rx\_digitalreset, and rx\_analogreset signals appropriately for correct simulation behavior.

- If the gxb\_powerdown port is instantiated, and the other reset signals are not used, you must assert the gxb\_powerdown signal for at least 1 µs for correct simulation behavior.

- You can deassert the rx\_digitalreset signal immediately after the rx\_freqlocked signal goes high to reduce the simulation run time. It is not necessary to wait for t<sub>LTD\_Auto</sub> (as suggested in the actual reset sequence).

- The busy signal is deasserted after about 20 parallel reconfig\_clk clock cycles in order to reduce simulation run time. For silicon behavior in hardware, you can follow the reset sequences described in the previous pages.

# Method 3: Writing Different Control Signals for all the Transceiver Channels at the Same Time

If you disable the **Use the same control signal for all the channels** option, the PMA control ports for a write transaction are separate for each channel. If you disable this option, the width of the PMA control ports are fixed as follows:

### **PMA Control Ports Used in a Write Transaction**

- tx\_vodctrl is 3 bits per channel

- tx\_preemp are 5 bits per channel

- rx\_eqdcgain is 2 bits per channel

- rx\_eqctrl is 4 bits per channel

For example, if you have two channels, the tx\_vodctrl is 6 bits wide (tx\_vodctrl [2:0] corresponds to channel 1 and tx\_vodctrl [5:3] corresponds to channel 2).

### **PMA Control Ports Used in a Read Transaction**

The width of the PMA control ports for a read transaction are always separate for each channel as explained in "Method 2: Writing the Same Control Signals to Control All the Transceiver Channels" on page 3–16.

#### Write Transaction

Because the PMA controls of all the channels are written, if you want to reconfigure a specific channel connected to the ALTGX\_RECONFIG instance, set the new value at the corresponding PMA control port of the channel under consideration and retain the previously stored values in the other active channels with a read transaction prior to this write transaction.

For example, if the number of channels controlled by the ALTGX\_RECONFIG instance is two, the tx\_vodctrl signal in this case would be 6 bits wide. The tx\_vodctrl[2:0] signal corresponds to channel 1 and the tx\_vodctrl[5:3] signal corresponds to channel 2.

- To dynamically reconfigure the PMA controls of only channel 2 with a new value, first perform a read transaction to retrieve the existing PMA control values from tx\_vodctrl\_out[5:0]. Use the tx\_vodctrl\_out[2:0] value for tx\_vodctrl[2:0] to write in channel 1. By doing so, channel 1 is overwritten with the same value.

- Perform a write transaction. This ensures that the new values are written only to channel 2 while channel 1 remains unchanged.

### **Clocking/Interface Options**

The following describes the **Clocking/Interface** options available in Cyclone IV GX devices. The core clocking setup describes the transceiver core clocks that are the write and read clocks of the Transmit Phase Compensation FIFO and the Receive Phase Compensation FIFO, respectively. Core clocking is classified as transmitter core clocking and receiver core clocking.

Table 3–6 lists the supported clocking interface settings for channel reconfiguration mode in Cyclone IV GX devices.

| mout                                       |                                                            |  |  |  |  |  |  |

|--------------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|

| ALTGX Setting                              | Description                                                |  |  |  |  |  |  |

| Dynamic Reconfiguration Channe             | el Internal and Interface Settings                         |  |  |  |  |  |  |

|                                            | Select one of the available options:                       |  |  |  |  |  |  |

| How should the receivers be                | Share a single transmitter core clock between receivers    |  |  |  |  |  |  |

| clocked?                                   | Use the respective channel transmitter core clocks         |  |  |  |  |  |  |

|                                            | Use the respective channel receiver core clocks            |  |  |  |  |  |  |

|                                            | Select one of the available options:                       |  |  |  |  |  |  |

| How should the transmitters be<br>clocked? | Share a single transmitter core clock between transmitters |  |  |  |  |  |  |

|                                            | Use the respective channel transmitter core clocks         |  |  |  |  |  |  |

Table 3–6. Dynamic Reconfiguration Clocking Interface Settings in Channel Reconfiguration

Mode

Transmitter core clocking refers to the clock that is used to write the parallel data from the FPGA fabric into the Transmit Phase Compensation FIFO. You can use one of the following clocks to write into the Transmit Phase Compensation FIFO:

- tx\_coreclk—you can use a clock of the same frequency as tx\_clkout from the FPGA fabric to provide the write clock to the Transmit Phase Compensation FIFO. If you use tx\_coreclk, it overrides the tx\_clkout options in the ALTGX MegaWizard Plug-In Manager.

- tx\_clkout—the Quartus II software automatically routes tx\_clkout to the FPGA fabric and back into the Transmit Phase Compensation FIFO.

| Symbol                       | Modes | C6  |     |     | C7, I7 |     |     | C8, A7 |     |     | C8L, I8L |     |     | C9L |     |     | Unit |

|------------------------------|-------|-----|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-----|-----|-----|------|

|                              |       | Min | Тур | Max | Min    | Тур | Max | Min    | Тур | Max | Min      | Тур | Max | Min | Тур | Max | UIII |

| t <sub>LOCK</sub> <i>(3)</i> |       |     |     | 1   |        |     | 1   |        | _   | 1   |          | —   | 1   |     |     | 1   | ms   |

#### Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 2 of 2)

Notes to Table 1-31:

(1) Applicable for true RSDS and emulated RSDS\_E\_3R transmitter.

(2) Cyclone IV E devices—true RSDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated RSDS transmitter is supported at the output pin of all I/O Banks. Cyclone IV GX devices—true RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated RSDS transmitter is only supported at the

pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(3) t<sub>LOCK</sub> is the time required for the PLL to lock from the end-of-device configuration.

(4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                                           | Modes                       | C6  |     |     | C7, I7 |     |     | C8, A7 |     |     | C8L, 18L |     |     | C9L |     |      | 11   |

|--------------------------------------------------|-----------------------------|-----|-----|-----|--------|-----|-----|--------|-----|-----|----------|-----|-----|-----|-----|------|------|

|                                                  |                             | Min | Тур | Max | Min    | Тур | Max | Min    | Тур | Max | Min      | Тур | Max | Min | Тур | Max  | Unit |

| f <sub>HSCLK</sub> (input<br>clock<br>frequency) | ×10                         | 5   | —   | 85  | 5      | —   | 85  | 5      | _   | 85  | 5        | _   | 85  | 5   | —   | 72.5 | MHz  |

|                                                  | ×8                          | 5   |     | 85  | 5      |     | 85  | 5      |     | 85  | 5        | _   | 85  | 5   | _   | 72.5 | MHz  |

|                                                  | ×7                          | 5   | _   | 85  | 5      | _   | 85  | 5      | _   | 85  | 5        | _   | 85  | 5   | —   | 72.5 | MHz  |

|                                                  | ×4                          | 5   |     | 85  | 5      |     | 85  | 5      | _   | 85  | 5        | _   | 85  | 5   | —   | 72.5 | MHz  |

|                                                  | ×2                          | 5   |     | 85  | 5      |     | 85  | 5      |     | 85  | 5        |     | 85  | 5   | _   | 72.5 | MHz  |

|                                                  | ×1                          | 5   | _   | 170 | 5      | _   | 170 | 5      | _   | 170 | 5        | _   | 170 | 5   | —   | 145  | MHz  |

| Device<br>operation in<br>Mbps                   | ×10                         | 100 | _   | 170 | 100    | _   | 170 | 100    | _   | 170 | 100      | _   | 170 | 100 | —   | 145  | Mbps |

|                                                  | ×8                          | 80  | _   | 170 | 80     | _   | 170 | 80     | _   | 170 | 80       | _   | 170 | 80  | —   | 145  | Mbps |

|                                                  | ×7                          | 70  | _   | 170 | 70     | _   | 170 | 70     | _   | 170 | 70       | _   | 170 | 70  | —   | 145  | Mbps |

|                                                  | ×4                          | 40  |     | 170 | 40     |     | 170 | 40     | _   | 170 | 40       | _   | 170 | 40  | —   | 145  | Mbps |

|                                                  | ×2                          | 20  | _   | 170 | 20     | _   | 170 | 20     | _   | 170 | 20       | _   | 170 | 20  | —   | 145  | Mbps |

|                                                  | ×1                          | 10  | _   | 170 | 10     | _   | 170 | 10     | _   | 170 | 10       | _   | 170 | 10  | —   | 145  | Mbps |

| t <sub>DUTY</sub>                                | —                           | 45  | _   | 55  | 45     | _   | 55  | 45     | _   | 55  | 45       | _   | 55  | 45  | —   | 55   | %    |

| TCCS                                             | —                           | —   | _   | 200 | _      | _   | 200 |        |     | 200 |          |     | 200 |     | _   | 200  | ps   |

| Output jitter<br>(peak to peak)                  | _                           | _   | _   | 500 | _      | _   | 500 | _      | _   | 550 | _        | _   | 600 | _   |     | 700  | ps   |

| t <sub>RISE</sub>                                | 20-80%,                     |     |     |     |        |     |     |        |     |     |          |     |     |     |     |      |      |

|                                                  | C <sub>LOAD</sub> =<br>5 pF | -   | 500 | —   | —      | 500 | —   | —      | 500 | _   | —        | 500 | _   | —   | 500 | —    | ps   |

| t <sub>FALL</sub>                                | 20-80%,                     |     |     |     |        |     |     |        |     |     |          |     |     |     |     |      |      |

|                                                  | C <sub>LOAD</sub> =<br>5 pF | -   | 500 |     |        | 500 |     | _      | 500 |     | —        | 500 |     | —   | 500 | —    | ps   |

Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 1 of 2)