Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 645                                                     |

| Number of Logic Elements/Cells | 10320                                                   |

| Total RAM Bits                 | 423936                                                  |

| Number of I/O                  | 179                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10f17i7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Manual Clock Switchover                                                   |      |

|---------------------------------------------------------------------------|------|

| Guidelines                                                                |      |

| Programmable Bandwidth                                                    |      |

| Phase Shift Implementation                                                |      |

| PLL Cascading                                                             | 5–33 |

| PLL Reconfiguration                                                       |      |

| PLL Reconfiguration Hardware Implementation                               | 5–34 |

| Post-Scale Counters (C0 to C4)                                            | 5–36 |

| Scan Chain Description                                                    | 5–37 |

| Charge Pump and Loop Filter                                               | 5–38 |

| Bypassing a PLL Counter                                                   | 5–39 |

| Dynamic Phase Shifting                                                    |      |

| Spread-Spectrum Clocking                                                  |      |

| PLL Specifications                                                        |      |

| Document Revision History                                                 |      |

| Section II. I/O Interfaces  Chapter 6. I/O Features in Cyclone IV Devices |      |

| Cyclone IV I/O Elements                                                   | 6.2  |

| I/O Element Features                                                      |      |

| Programmable Current Strength                                             |      |

| Slew Rate Control                                                         |      |

|                                                                           |      |

| Open-Drain Output                                                         |      |

| Bus Hold                                                                  |      |

| Programmable Pull-Up Resistor                                             |      |

| Programmable Delay                                                        |      |

| PCI-Clamp Diode                                                           |      |

| OCT Support                                                               |      |

| On-Chip Series Termination with Calibration                               |      |

| On-Chip Series Termination Without Calibration                            |      |

| I/O Standards                                                             |      |

| Termination Scheme for I/O Standards                                      |      |

| Voltage-Referenced I/O Standard Termination                               |      |

| Differential I/O Standard Termination                                     |      |

| I/O Banks                                                                 |      |

| High-Speed Differential Interfaces                                        |      |

| External Memory Interfacing                                               |      |

| Pad Placement and DC Guidelines                                           |      |

| Pad Placement                                                             |      |

| DC Guidelines                                                             |      |

| Clock Pins Functionality                                                  |      |

| High-Speed I/O Interface                                                  |      |

| High-Speed I/O Standards Support                                          |      |

| High Speed Serial Interface (HSSI) Input Reference Clock Support          |      |

| LVDS I/O Standard Support in Cyclone IV Devices                           | 6–29 |

| Designing with LVDS                                                       |      |

| BLVDS I/O Standard Support in Cyclone IV Devices                          |      |

| Designing with BLVDS                                                      |      |

| RSDS, Mini-LVDS, and PPDS I/O Standard Support in Cyclone IV Devices      |      |

| Designing with RSDS, Mini-LVDS, and PPDS                                  |      |

| LVPECL I/O Support in Cyclone IV Devices                                  |      |

| Differential SSTL I/O Standard Support in Cyclone IV Devices              | 6–35 |

viii Contents

# Chapter 11. Power Requirements for Cyclone IV DevicesExternal Power Supply Requirements11–1Hot-Socketing Specifications11–2Devices Driven Before Power-Up11–2I/O Pins Remain Tri-stated During Power-Up11–2Hot-socketing Feature Implementation11–3Power-On Reset Circuitry11–3Document Revision History11–4

# **Document Revision History**

Table 1–10 lists the revision history for this chapter.

Table 1-10. Document Revision History

| Date          | Version | Changes                                                                                                                  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------|

| March 2016    | 2.0     | ■ Updated Table 1–4 and Table 1–5 to remove support for the N148 package.                                                |

| IVIAICII 2016 | 2.0     | ■ Updated Figure 1–2 to remove support for the N148 package.                                                             |

| April 2014    | 1.9     | Updated "Packaging Ordering Information for the Cyclone IV E Device".                                                    |

| May 2013      | 1.8     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                      |

| February 2013 | 1.7     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                      |

| October 2012  | 1.6     | Updated Table 1–3 and Table 1–4.                                                                                         |

| November 2011 | 1.5     | ■ Updated "Cyclone IV Device Family Features" section.                                                                   |

| November 2011 | 1.5     | ■ Updated Figure 1–2 and Figure 1–3.                                                                                     |

|               |         | ■ Updated for the Quartus II software version 10.1 release.                                                              |

|               |         | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                                   |

| December 2010 | 1.4     | ■ Updated Table 1–1, Table 1–2, Table 1–3, Table 1–5, and Table 1–6.                                                     |

|               |         | ■ Updated Figure 1–3.                                                                                                    |

|               |         | ■ Minor text edits.                                                                                                      |

| July 2010     | 1.3     | Updated Table 1–2 to include F484 package information.                                                                   |

|               |         | ■ Updated Table 1–3 and Table 1–6.                                                                                       |

| March 2010    | 1.2     | ■ Updated Figure 1–3.                                                                                                    |

|               |         | ■ Minor text edits.                                                                                                      |

|               |         | ■ Added Cyclone IV E devices in Table 1–1, Table 1–3, and Table 1–6 for the Quartus II software version 9.1 SP1 release. |

|               |         | Added the "Cyclone IV Device Family Speed Grades" and "Configuration" sections.                                          |

| February 2010 | 1.1     | ■ Added Figure 1–3 to include Cyclone IV E Device Packaging Ordering Information.                                        |

|               |         | ■ Updated Table 1–2, Table 1–4, and Table 1–5 for Cyclone IV GX devices.                                                 |

|               |         | ■ Minor text edits.                                                                                                      |

| November 2009 | 1.0     | Initial release.                                                                                                         |

Table 5-2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices (1), (2) (Part 4 of 4)

| GCLK Network Clock GCLK Netwo |   |   |   |   |   |   | Networks |   |   |   |    |    |    |    |    |    |    |    |    |          |    |    |    |    |    |    |    |    |    |    |

|-------------------------------|---|---|---|---|---|---|----------|---|---|---|----|----|----|----|----|----|----|----|----|----------|----|----|----|----|----|----|----|----|----|----|

| Sources                       | 0 | 1 | 2 | 3 | 4 | 5 | 6        | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19       | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| DPCLK17                       |   | _ | _ | _ | _ | _ | _        | _ | _ | _ | _  | _  | _  | _  |    |    |    |    |    | <b>\</b> | _  |    |    |    | _  | _  |    |    |    | _  |

#### Notes to Table 5-2:

October 2012

Altera Corporation

- (1) EP4CGX30 information in this table refers to only EP4CGX30 device in F484 package.

- (2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

- (3) PLL\_7 and PLL\_8 are not available in EP4CXGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

Table 5-3. GCLK Network Connections for Cyclone IV E Devices (1) (Part 1 of 3)

| GCLK Network Clock   |          |   |   |          |   |          |          |          | GC       | LK N     | etwo     | rks      |    |          |          |          |          |          |    |    |

|----------------------|----------|---|---|----------|---|----------|----------|----------|----------|----------|----------|----------|----|----------|----------|----------|----------|----------|----|----|

| Sources              | 0        | 1 | 2 | 3        | 4 | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12 | 13       | 14       | 15       | 16       | 17       | 18 | 19 |

| CLK1                 | _        | ✓ | ✓ | _        | _ | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK2/DIFFCLK_1p      | _        | ✓ | _ | ✓        | ✓ | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _        | _        | _        | _  | _  |

| CLK3/DIFFCLK_1n      | <b>✓</b> | _ | _ | <b>✓</b> | _ | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK4/DIFFCLK_2p      | _        | _ | _ | _        | _ | <b>✓</b> | _        | <b>✓</b> | _        | <b>✓</b> | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK5/DIFFCLK_2n      | _        | _ | _ | _        | _ | _        | ✓        | ✓        | _        | _        | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK6/DIFFCLK_3p      | _        | _ | _ | _        | _ | _        | <b>✓</b> | _        | <b>✓</b> | <b>✓</b> | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK7/DIFFCLK_3n      | _        | _ | _ | _        | _ | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | _  | _        | _        | _        | _        |          | _  | _  |

| CLK8/DIFFCLK_5n (2)  | _        | _ | _ | _        | _ | _        | _        | _        | _        | _        | <b>✓</b> | _        | ✓  | _        | <b>✓</b> | _        | _        |          | _  | _  |

| CLK9/DIFFCLK_5p (2)  | _        | _ | _ | _        | _ | _        | _        | _        | _        | _        | _        | <b>✓</b> | ✓  | _        | _        | _        | _        |          | _  | _  |

| CLK10/DIFFCLK_4n (2) | _        |   | _ | _        | _ | _        | _        | _        | _        | _        | _        | ~        | _  | <b>✓</b> | ~        | _        | —        | _        | _  |    |

| CLK11/DIFFCLK_4p     | _        | _ | _ | _        | _ | _        | _        | _        | _        | _        | ~        | _        | _  | <b>~</b> | _        | _        | _        |          | _  | _  |

| CLK12/DIFFCLK_7n (2) | _        | _ | _ | _        | _ | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | <b>✓</b> | _        | <b>✓</b> | _  | ~  |

| CLK13/DIFFCLK_7p     | _        | — | — | —        | _ | —        | _        | _        | —        | _        | —        | —        | _  | _        | —        | _        | ~        | <b>✓</b> | _  | _  |

| CLK14/DIFFCLK_6n     | _        | _ | _ | _        | _ | _        | _        | _        | _        | _        | _        | _        | _  | _        | _        | _        | <b>✓</b> | _        | ~  | ~  |

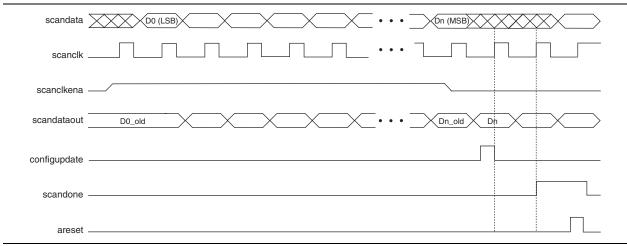

Figure 5–23 shows a functional simulation of the PLL reconfiguration feature.

Figure 5-23. PLL Reconfiguration Scan Chain

When reconfiguring the counter clock frequency, the corresponding counter phase shift settings cannot be reconfigured using the same interface. You can reconfigure phase shifts in real time using the dynamic phase shift reconfiguration interface. If you reconfigure the counter frequency, but wish to keep the same non-zero phase shift setting (for example, 90°) on the clock output, you must reconfigure the phase shift after reconfiguring the counter clock frequency.

#### Post-Scale Counters (CO to C4)

You can configure multiply or divide values and duty cycle of post-scale counters in real time. Each counter has an 8-bit high time setting and an 8-bit low time setting. The duty cycle is the ratio of output high or low time to the total cycle time, that is the sum of the two. Additionally, these counters have two control bits, rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

When the rbypass bit is set to 1, it bypasses the counter, resulting in a divide by one. When this bit is set to 0, the PLL computes the effective division of the VCO output frequency based on the high and low time counters. For example, if the post-scale divide factor is 10, the high and low count values are set to 5 and 5, to achieve a 50–50% duty cycle. The PLL implements this duty cycle by transitioning the output clock from high-to-low on the rising edge of the VCO output clock. However, a 4 and 6 setting for the high and low count values, respectively, would produce an output clock with a 40–60% duty cycle.

The rselodd bit indicates an odd divide factor for the VCO output frequency with a 50% duty cycle. For example, if the post-scale divide factor is three, the high and low time count values are 2 and 1, respectively, to achieve this division. This implies a 67%–33% duty cycle. If you need a 50%–50% duty cycle, you must set the rselodd control bit to 1 to achieve this duty cycle despite an odd division factor. The PLL implements this duty cycle by transitioning the output clock from high-to-low on a falling edge of the VCO output clock. When you set rselodd = 1, subtract 0.5 cycles from the high time and add 0.5 cycles to the low time.

For example:

■ High time count = 2 cycles

Table 6–2 lists the I/O standards that support impedance matching and series termination.

Table 6–2. Cyclone IV Device I/O Features Support (Part 1 of 2)

| I/O Standard                                 |                      | ent Strength<br>mA) <sup>(1)</sup> , <sup>(9)</sup> | R <sub>S</sub> OC<br>Calib<br>Setting, | T with<br>ration<br>Ohm (Ω) | Calib         | Without<br>ration<br>Ohm (Ω) | Cyclone<br>IV E I/O<br>Banks | Cyclone<br>IV GX I/O<br>Banks | Slew<br>Rate<br>Option | PCI-<br>clamp<br>Diode |

|----------------------------------------------|----------------------|-----------------------------------------------------|----------------------------------------|-----------------------------|---------------|------------------------------|------------------------------|-------------------------------|------------------------|------------------------|

|                                              | Column I/O           | Row I/O                                             | Column<br>I/O                          | Row<br>I/O <sup>(8)</sup>   | Column<br>I/O | Row<br>I/O <sup>(8)</sup>    | Support                      | Support                       | (6)                    | Support                |

| 3.3-V LVTTL                                  | 4,8                  | 4,8                                                 | _                                      | _                           | _             | _                            |                              |                               | _                      | <b>✓</b>               |

| 3.3-V LVCMOS                                 | 2                    | 2                                                   | _                                      | _                           | _             | _                            |                              |                               | _                      | ✓                      |

| 3.0-V LVTTL                                  | 4,8,12,16            | 4,8,12,16                                           | 50,25                                  | 50,25                       | 50,25         | 50,25                        |                              |                               | 0,1,2                  | <b>✓</b>               |

| 3.0-V LVCMOS                                 | 4,8,12,16            | 4,8,12,16                                           | 50,25                                  | 50,25                       | 50,25         | 50,25                        |                              |                               | 0,1,2                  | ✓                      |

| 3.0-V PCI/PCI-X                              | _                    | _                                                   | _                                      | _                           | _             | _                            |                              | 3,4,5,6,                      | _                      | <b>✓</b>               |

| 2.5-V<br>LVTTL/LVCMOS                        | 4,8,12,16            | 4,8,12,16                                           | 50,25                                  | 50,25                       | 50,25         | 50,25                        |                              | 7,8,9                         |                        | <b>✓</b>               |

| 1.8-V<br>LVTTL/LVCMOS                        | 2,4,6,8,10,12,1<br>6 | 2,4,6,8,10,12,1<br>6                                | 50,25                                  | 50,25                       | 50,25         | 50,25                        |                              |                               |                        | _                      |

| 1.5-V LVCMOS                                 | 2,4,6,8,10,12,1<br>6 | 2,4,6,8,10,12,1<br>6                                | 50,25                                  | 50,25                       | 50,25         | 50,25                        |                              |                               |                        | _                      |

| 1.2-V LVCMOS                                 | 2,4,6,8,10,12        | 2,4,6,8,10                                          | 50,25                                  | 50                          | 50,25         | 50                           | 1,2,3,4,<br>5,6,7,8          | 4,5,6,7,<br>8                 |                        | _                      |

| SSTL-2 Class I                               | 8,12                 | 8,12                                                | 50                                     | 50                          | 50            | 50                           |                              |                               |                        |                        |

| SSTL-2 Class II                              | 16                   | 16                                                  | 25                                     | 25                          | 25            | 25                           |                              |                               | 0,1, <b>2</b>          | _                      |

| SSTL-18 Class I                              | 8,10,12              | 8,10,12                                             | 50                                     | 50                          | 50            | 50                           |                              |                               | 0,1,2                  | _                      |

| SSTL-18 Class II                             | 12,16                | 12,16                                               | 25                                     | 25                          | 25            | 25                           |                              | 3,4,5,6,                      |                        | _                      |

| HSTL-18 Class I                              | 8,10,12              | 8,10,12                                             | 50                                     | 50                          | 50            | 50                           |                              | 7,8,9                         |                        | _                      |

| HSTL-18 Class II                             | 16                   | 16                                                  | 25                                     | 25                          | 25            | 25                           |                              |                               |                        | _                      |

| HSTL-15 Class I                              | 8,10,12              | 8,10,12                                             | 50                                     | 50                          | 50            | 50                           |                              |                               |                        |                        |

| HSTL-15 Class II                             | 16                   | 16                                                  | 25                                     | 25                          | 25            | 25                           |                              |                               |                        |                        |

| HSTL-12 Class I                              | 8,10,12              | 8,10                                                | 50                                     | 50                          | 50            | 50                           |                              | 4,5,6,7,<br>8                 |                        | _                      |

| HSTL-12 Class II                             | 14                   | _                                                   | 25                                     | _                           | 25            | _                            | 3,4,7,8                      | 4,7,8                         |                        | _                      |

| Differential SSTL-2<br>Class   (2), (7)      | 8,12                 | 8,12                                                | 50                                     | 50                          | 50            | 50                           |                              |                               |                        | _                      |

| Differential SSTL-2<br>Class II (2), (7)     | 16                   | 16                                                  | 25                                     | 25                          | 25            | 25                           |                              |                               |                        | _                      |

| Differential SSTL-<br>18 <sup>(2), (7)</sup> | 8,10,12              | _                                                   | 50                                     | _                           | 50            | _                            | 1,2,3,4,<br>5,6,7,8          | 3,4,5,6,<br>7,8               | 0,1, <b>2</b>          | _                      |

| Differential HSTL-<br>18 <sup>(2), (7)</sup> | 8,10,12              | _                                                   | 50                                     | _                           | 50            | _                            |                              |                               |                        | _                      |

| Differential HSTL-<br>15 <sup>(2), (7)</sup> | 8,10,12              | _                                                   | 50                                     | _                           | 50            | _                            |                              |                               |                        | _                      |

| Differential HSTL-<br>12 (2), (7)            | 8,10,12              | _                                                   | 50                                     | _                           | 50            | _                            | 3,4,7,8                      | 4,7,8                         |                        | _                      |

Figure 8–34 shows the control register bit positions. Table 8–23 defines the control register bit contents. The numbers in Figure 8–34 show the bit position of a setting in a register. For example, bit number 35 is the enable bit for the watchdog timer.

Figure 8-34. Remote System Upgrade Control Register

| 38   | 37       | 36      | 35    | 34   | 33         | 12    | 11           | 0  |

|------|----------|---------|-------|------|------------|-------|--------------|----|

| Rsv2 | Cd_early | Osc_int | Wd_en | Rsv1 | Ru_address | [210] | Wd_timer[110 | 0] |

Table 8-23. Remote System Upgrade Control Register Contents

| Control Register Bit | Value                                   | Definition                                                                                                                 |

|----------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Wd_timer[110]        | 12'b00000000000                         | User watchdog time-out value (most significant 12 bits of 29-bit count value: {Wd_timer[110],17'b1000})                    |

| Ru_address[210]      | 22'b00000000000000000000000000000000000 | Configuration address (most significant 22 bits of 24-bit boot address value: boot_address[23:0] = {Ru_address[210],2'b0}) |

| Rsv1                 | 1'b0                                    | Reserved bit                                                                                                               |

| Wd_en                | 1'b1                                    | User watchdog timer enable bit                                                                                             |

| Osc_int (1)          | 1'b1                                    | Internal oscillator as startup state machine clock enable bit                                                              |

| Cd_early (1)         | 1'b1                                    | Early CONF_DONE check                                                                                                      |

| Rsv2                 | 1'b1                                    | Reserved bit                                                                                                               |

#### Note to Table 8-23:

(1) Option bit for the application configuration.

When enabled, the early CONF\_DONE check (Cd\_early) option bit ensures that there is a valid configuration at the boot address specified by the factory configuration and that it is of the proper size. If an invalid configuration is detected or the CONF\_DONE pin is asserted too early, the device resets and then reconfigures the factory configuration image. The internal oscillator (as the startup state machine clock [Osc\_int] option bit) ensures a functional startup clock to eliminate the hanging of startup. When all option bits are turned on, they provide complete coverage for the programming and startup portions of the application configuration. Altera recommends turning on both the Cd\_early and Osc\_int option bits.

The Cd\_early and Osc\_int option bits for the application configuration must be turned on by the factory configuration.

#### **Remote System Upgrade Status Register**

The remote system upgrade status register specifies the reconfiguration trigger condition. The various trigger and error conditions include:

- Cyclical redundancy check (CRC) error during application configuration

- nSTATUS assertion by an external device due to an error

- Cyclone IV device logic array triggers a reconfiguration cycle, possibly after downloading a new application configuration image

# 11. Power Requirements for Cyclone IV Devices

#### CYIV-51011-1.3

This chapter describes information about external power supply requirements, hot-socketing specifications, power-on reset (POR) requirements, and their implementation in Cyclone IV devices.

This chapter includes the following sections:

- "External Power Supply Requirements" on page 11–1

- "Hot-Socketing Specifications" on page 11–2

- "Hot-socketing Feature Implementation" on page 11–3

- "Power-On Reset Circuitry" on page 11–3

### **External Power Supply Requirements**

This section describes the different external power supplies required to power Cyclone IV devices. Table 11–1 and Table 11–2 list the descriptions of external power supply pins for Cyclone IV GX and Cyclone IV E devices, respectively.

- For each Altera recommended power supply's operating conditions, refer to the *Cyclone IV Device Datasheet* chapter.

- For power supply pin connection guidelines and power regulator sharing, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

Table 11–1. Power Supply Descriptions for the Cyclone IV GX Devices (Part 1 of 2)

| Power Supply Pin   | Nominal Voltage Level (V)    | Description                                                                                                 |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|

| VCCINT             | 1.2                          | Core voltage, PCI Express (PCIe) hard IP block, and transceiver physical coding sublayer (PCS) power supply |

| VCCA (1)           | 2.5                          | PLL analog power supply                                                                                     |

| VCCD_PLL           | 1.2                          | PLL digital power supply                                                                                    |

| VCCIO (2)          | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply                                                                                      |

| VCC_CLKIN (3), (4) | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | Differential clock input pins power supply                                                                  |

| VCCH_GXB           | 2.5                          | Transceiver output (TX) buffer power supply                                                                 |

| VCCA_GXB           | 2.5                          | Transceiver physical medium attachment (PMA) and auxiliary power supply                                     |

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

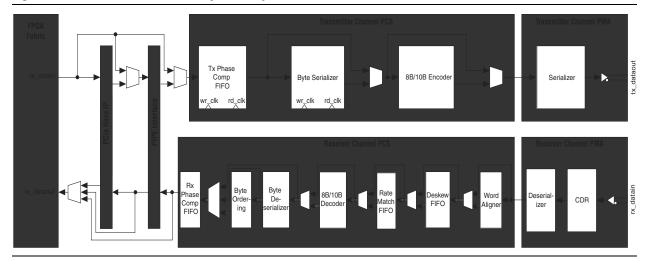

## **Architectural Overview**

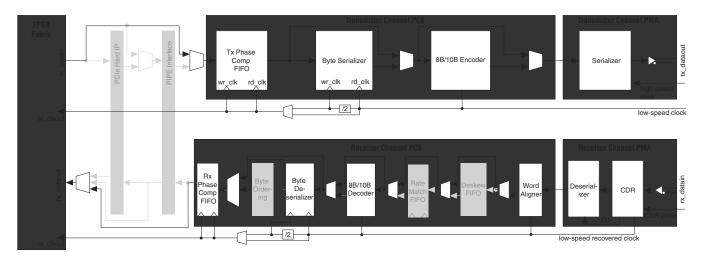

Figure 1–3 shows the Cyclone IV GX transceiver channel datapath.

Figure 1–3. Transceiver Channel Datapath for Cyclone IV GX Devices

Each transceiver channel consists of a transmitter and a receiver datapath. Each datapath is further structured into the following:

- Physical media attachment (PMA)—includes analog circuitry for I/O buffers, clock data recovery (CDR), serializer/deserializer (SERDES), and programmable pre-emphasis and equalization to optimize serial data channel performance.

- Physical coding sublayer (PCS)—includes hard logic implementation of digital functionality within the transceiver that is compliant with supported protocols.

Outbound parallel data from the FPGA fabric flows through the transmitter PCS and PMA, is transmitted as serial data. Received inbound serial data flows through the receiver PMA and PCS into the FPGA fabric. The transceiver supports the following interface widths:

- FPGA fabric-transceiver PCS—8, 10, 16, or 20 bits

- PMA-PCS—8 or 10 bits

- The transceiver channel interfaces through the PIPE when configured for PCIe protocol implementation. The PIPE is compliant with version 2.00 of the PHY Interface for the PCI Express Architecture specification.

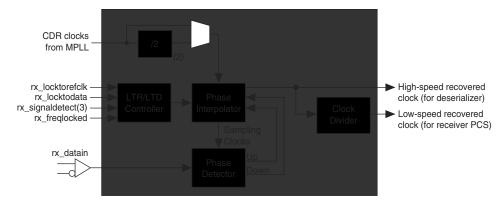

#### **Clock Data Recovery**

Each receiver channel has an independent CDR unit to recover the clock from the incoming serial data stream. The high-speed recovered clock is used to clock the deserializer for serial-to-parallel conversion of the received input data, and low-speed recovered clock to clock the receiver PCS blocks. Figure 1–15 illustrates the CDR unit block diagram.

Figure 1-15. CDR Unit Block Diagram

#### Notes to Figure 1-15:

- (1) Optional RX local divider for CDR clocks from multipurpose PLL is only available in each CDR unit for EP4CGX30 (F484 package), EP4CGX50, and EP4CGX75 devices. This block is used with the transceiver dynamic reconfiguration feature. For more information, refer to the Cyclone IV Dynamic Reconfiguration chapter and AN 609: Implementing Dynamic Reconfiguration in Cyclone IV GX Devices.

- (2) CDR state transition in automatic lock mode is not dependent on rx\_signaldetect signal, except when configured in PCI Express (PIPE) mode only.

Each CDR unit gets the reference clock from one of the two multipurpose phase-locked loops (PLLs) adjacent to the transceiver block. The CDR works by tracking the incoming data with a phase detector and finding the optimum sampling clock phase from the phase interpolator unit. The CDR operations are controlled by the LTR/LTD controller block, where the CDR may operate in the following states:

- Lock-to-reference (LTR) state—phase detector disabled and CDR ignores incoming data

- Lock-to-data (LTD) state—phase detector enabled and CDR tracks incoming data to find the optimum sampling clock phase

State transitions are supported with automatic lock mode and manual lock mode.

#### **Automatic Lock Mode**

Upon receiver power-up and reset cycle, the CDR is put into LTR state. Transition to the LTD state is performed automatically when both of the following conditions are met:

- Signal detection circuitry indicates the presence of valid signal levels at the receiver input buffer. This condition is valid for PCI Express (PIPE) mode only.

CDR transitions are not dependent on signal detection circuitry in other modes.

- The recovered clock is within the configured part per million (ppm) frequency threshold setting with respect to the CDR clocks from multipurpose PLL.

For Transmitter and Receiver operation in bonded channel configuration, the receiver PCS supports configuration with rate match FIFO, and configuration without rate match FIFO. Figure 1–39 shows the datapath clocking in Transmitter and Receiver operation with rate match FIFO in ×2 and ×4 bonded channel configurations. For Transmitter and Receiver operation in bonded channel configuration without rate match FIFO, the datapath clocking is identical to Figure 1–38 for the bonded transmitter channels, and Figure 1–34 on page 1–35 for the receiver channels.

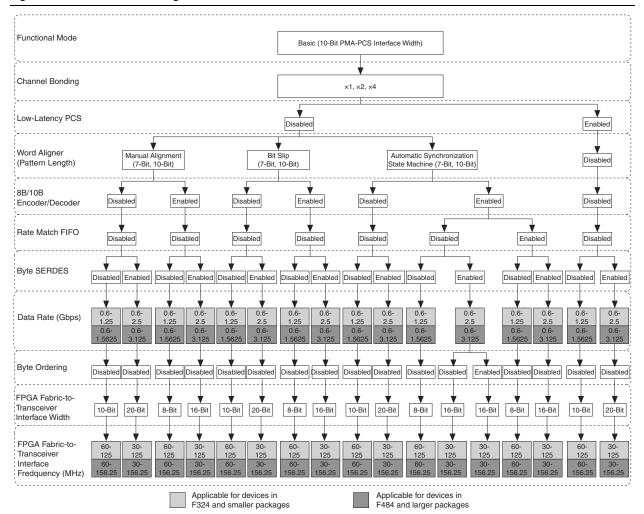

Figure 1–46. Transceiver Configurations in Basic Mode with a 10-Bit Wide PMA-to-PCS Interface

#### **Rate Match FIFO Operation in Basic Mode**

In Basic mode, the rate match FIFO performs the following operations:

- Deletes a maximum of four skip patterns from a cluster, if there is one skip pattern left in the cluster after deletion

- Insert a maximum of four skip patterns in a cluster, if there are less than five skip patterns in the cluster after deletion

- Automatically deletes the data byte that causes the FIFO to go full and asserts the rx rmfifofull flag synchronous to the subsequent data byte

- Automatically inserts /K30.7/ (9'h1FE) after the data byte that causes the FIFO to go empty and asserts the rx-fifoempty flag synchronous to the inserted /K30.7/ (9'h1FE)

#### **Additional Options in Basic Mode**

In Basic mode, the transceiver supports the following additional options:

■ low-latency PCS operation

Figure 1–66 shows the transceiver channel datapath and clocking when configured in deterministic latency mode.

Figure 1-66. Transceiver Channel Datapath and Clocking when Configured in Deterministic Latency Mode

#### Note to Figure 1-66:

(1) High-speed recovered clock.

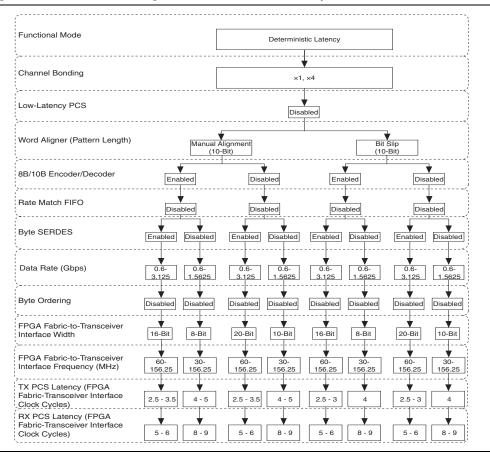

Figure 1–67 shows the transceiver configuration in Deterministic Latency mode.

Figure 1-67. Transceiver Configuration in Deterministic Latency Mode

Both CPRI and OBSAI protocols define the serial interface connecting the base station component (specifically channel cards) and remote radio heads (specifically radio frequency cards) in a radio base station system with fiber optics. The protocols require the accuracy of round trip delay measurement for single-hop and multi-hop connections to be within  $\pm$  16.276 ns. The Cyclone IV GX transceivers support the following CPRI and OBSAI line rates using Deterministic Latency mode:

- CPRI —614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps, and 3.072 Gbps

- OBSAI—768 Mbps, 1.536 Gbps, and 3.072 Gbps

- For more information about deterministic latency implementation, refer to AN 610: Implementing Deterministic Latency for CPRI and OBSAI Protocols in Stratix IV, HardCopy IV, Arria II GX, and Cyclone IV Devices.

#### **Registered Mode Phase Compensation FIFO**

In Deterministic Latency mode, the RX phase compensation FIFO is set to registered mode while the TX phase compensation FIFO supports optional registered mode. When set into registered mode, the phase compensation FIFO acts as a register and eliminates the latency uncertainty through the FIFOs.

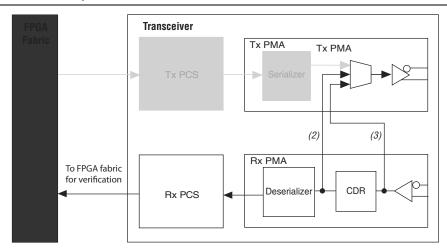

Figure 1–72 shows the two paths in reverse serial loopback mode.

Figure 1–72. Reverse Serial Loopback (1)

#### Notes to Figure 1-72:

- (1) Grayed-Out Blocks are Not Active in this mode.

- (2) Post-CDR reverse serial loopback path.

- (3) Pre-CDR reverse serial loopback path.

#### **Self Test Modes**

Each transceiver channel in the Cyclone IV GX device contains modules for pattern generator and verifier. Using these built-in features, you can verify the functionality of the functional blocks in the transceiver channel without requiring user logic. The self test functionality is provided as an optional mechanism for debugging transceiver channels.

There are three types of supported pattern generators and verifiers:

- Built-in self test (BIST) incremental data generator and verifier—test the complete transmitter PCS and receiver PCS datapaths for bit errors with parallel loopback before the PMA blocks.

- Pseudo-random binary sequence (PRBS) generator and verifier—the PRBS generator and verifier interface with the serializer and deserializer in the PMA blocks. The advantage of using a PRBS data stream is that the randomness yields an environment that stresses the transmission medium. In the data stream, you can observe both random jitter and deterministic jitter using a time interval analyzer, bit error rate tester, or oscilloscope.

- High frequency and low frequency pattern generator—the high frequency patterns generate alternate ones and zeros and the low frequency patterns generate five ones and five zeroes. These patterns do not have a corresponding verifier.

- The self-test features are only supported in Basic mode.

Table 3-5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 2 of 3)

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA Fabric-Transceiver Channel Interface Widths)                                         |  |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                          | Two 8-bit unencoded Data (rx_dataout)                                                                                                                  |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[7:0] - rx_dataout (LSByte) and                                                                                                          |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[23:16]-rx_dataout (MSByte)                                                                                                              |  |  |  |  |  |  |

|                                                          | The following signals are used in 16-bit 8B/10B modes:                                                                                                 |  |  |  |  |  |  |

|                                                          | Two Control Bits                                                                                                                                       |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[8] - rx_ctrldetect (LSB) and                                                                                                            |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[24]-rx_ctrldetect (MSB)                                                                                                                 |  |  |  |  |  |  |

|                                                          | Two Receiver Error Detect Bits                                                                                                                         |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[9] - rx_errdetect (LSB) and                                                                                                             |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[25]-rx_errdetect(MSB)                                                                                                                   |  |  |  |  |  |  |

|                                                          | Two Receiver Sync Status Bits                                                                                                                          |  |  |  |  |  |  |

|                                                          | rx_dataoutfull [10] - rx_syncstatus (LSB) and                                                                                                          |  |  |  |  |  |  |

| 16-bit FPGA fabric-Transceiver                           | rx_dataoutfull[26] -rx_syncstatus (MSB)                                                                                                                |  |  |  |  |  |  |

| Channel Interface with PCS-PMA set to 8/10 bits          | Two Receiver Disparity Error Bits                                                                                                                      |  |  |  |  |  |  |

| SEL IO O/ TO DIES                                        | rx_dataoutfull [11] - rx_disperr (LSB) and                                                                                                             |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[27] - rx_disperr (MSB)                                                                                                                  |  |  |  |  |  |  |

|                                                          | Two Receiver Pattern Detect Bits                                                                                                                       |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[12] - rx_patterndetect (LSB) and                                                                                                        |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[28]-rx_patterndetect (MSB)                                                                                                              |  |  |  |  |  |  |

|                                                          | rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion status indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes |  |  |  |  |  |  |

|                                                          |                                                                                                                                                        |  |  |  |  |  |  |

|                                                          | Two 2-bit PCI Express (PIPE) Functional Mode Status Bits                                                                                               |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[14:13] - rx_pipestatus (LSB) and rx_dataoutfull[30:29] rx_pipestatus (MSB)</pre>                                                   |  |  |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                              |  |  |  |  |  |  |

For more information about receiver input and transmitter output waveforms, and for other differential I/O standards, refer to the I/O Features in Cyclone IV Devices chapter.

Table 1–18. Differential SSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       |      | <sub>I(DC)</sub> (V) | V <sub>x(</sub> ,            | V <sub>Swir</sub> | ng(AC)<br><b>/</b> )            | V <sub>OX(AC)</sub> (V) |                  |                                 |     |                                 |

|------------------------|-------|-----------------------|-------|------|----------------------|------------------------------|-------------------|---------------------------------|-------------------------|------------------|---------------------------------|-----|---------------------------------|

|                        | Min   | Тур                   | Max   | Min  | Max                  | Min                          | Тур               | Max                             | Min                     | Max              | Min                             | Тур | Max                             |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 0.36 | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.2   | _                 | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.7                     | V <sub>CCI</sub> | V <sub>CCIO</sub> /2 -<br>0.125 | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

| SSTL-18<br>Class I, II | 1.7   | 1.8                   | 1.90  | 0.25 | V <sub>CCIO</sub>    | V <sub>CCIO</sub> /2 - 0.175 | _                 | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                     | V <sub>CCI</sub> | V <sub>CCIO</sub> /2 - 0.125    | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

#### Note to Table 1-18:

Table 1–19. Differential HSTL I/O Standard Specifications for Cyclone IV Devices (1)

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>DIF(DC)</sub> (V) |                   | V <sub>X(AC)</sub> (V)   |     |                             | V <sub>CM(DC)</sub> (V)     |     |                             |         | V <sub>DIF(AC)</sub> (V)    |  |

|------------------------|-----------------------|-----|-------|--------------------------|-------------------|--------------------------|-----|-----------------------------|-----------------------------|-----|-----------------------------|---------|-----------------------------|--|

|                        | Min                   | Тур | Max   | Min                      | Мах               | Min                      | Тур | Max                         | Min                         | Тур | Max                         | Mi<br>n | Max                         |  |

| HSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.2                      | _                 | 0.85                     | _   | 0.95                        | 0.85                        | _   | 0.95                        | 0.4     | _                           |  |

| HSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | 0.2                      | _                 | 0.71                     | _   | 0.79                        | 0.71                        | _   | 0.79                        | 0.4     | _                           |  |

| HSTL-12<br>Class I, II | 1.14                  | 1.2 | 1.26  | 0.16                     | V <sub>CCIO</sub> | 0.48 x V <sub>CCIO</sub> |     | 0.52 x<br>V <sub>CCIO</sub> | 0.48 x<br>V <sub>CCIO</sub> |     | 0.52 x<br>V <sub>CCIO</sub> | 0.3     | 0.48 x<br>V <sub>CCIO</sub> |  |

#### Note to Table 1-19:

Table 1–20. Differential I/O Standard Specifications for Cyclone IV Devices (1) (Part 1 of 2)

| I/O Standard                   | V <sub>CCIO</sub> (V) |                         |       | V <sub>ID</sub> (mV) |     | V <sub>IcM</sub> (V) <sup>(2)</sup> |                                                                                                     |      | V <sub>OD</sub> (mV) <sup>(3)</sup> |     |     | V <sub>os</sub> (V) <sup>(3)</sup> |      |       |

|--------------------------------|-----------------------|-------------------------|-------|----------------------|-----|-------------------------------------|-----------------------------------------------------------------------------------------------------|------|-------------------------------------|-----|-----|------------------------------------|------|-------|

|                                | Min                   | Min Typ Max Min Max Min |       | Condition            | Max | Min                                 | Тур                                                                                                 | Max  | Min                                 | Тур | Max |                                    |      |       |

| LVDEOL                         |                       |                         |       |                      |     | 0.05                                | $D_{MAX} \leq 500 \; Mbps$                                                                          | 1.80 |                                     |     |     |                                    |      |       |

| LVPECL<br>(Row I/Os)           | 2.375                 | 2.5                     | 2.625 | 100                  |     | 0.55                                | $\begin{array}{l} 500 \; \text{Mbps} \leq  D_{\text{MAX}} \\ \leq  700 \; \text{Mbps} \end{array}$  | 1.80 |                                     | _   |     | _                                  | _    | _     |

|                                |                       |                         |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |                                     |     |     |                                    |      |       |

| LVPECL<br>(Column<br>I/Os) (6) | 2.375                 | 2.5                     | 2.625 | 100                  | _   | 0.05                                | $D_{MAX} \leq 500 \text{ Mbps}$                                                                     | 1.80 |                                     | _   | _   | _                                  |      |       |

|                                |                       |                         |       |                      |     | 0.55                                | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$    | 1.80 | _                                   |     |     |                                    |      |       |

| 1,700)                         |                       |                         |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |                                     |     |     |                                    |      |       |

|                                |                       |                         |       |                      |     | 0.05                                | $D_{MAX} \leq 500 \; Mbps$                                                                          | 1.80 |                                     |     |     |                                    |      |       |

| LVDS (Row<br>I/Os)             | 2.375                 | 2.5                     | 2.625 | 100                  | _   | 0.55                                | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq \; 700 \; \text{Mbps} \end{array}$ | 1.80 | 247                                 | _   | 600 | 1.125                              | 1.25 | 1.375 |

|                                |                       |                         |       |                      |     | 1.05                                | D <sub>MAX</sub> > 700 Mbps                                                                         | 1.55 |                                     |     |     |                                    |      |       |

<sup>(1)</sup> Differential SSTL requires a  $V_{\text{REF}}$  input.

<sup>(1)</sup> Differential HSTL requires a  $V_{\text{REF}}$  input.

Table 1–25. PLL Specifications for Cyclone IV Devices (1), (2) (Part 2 of 2)

| Symbol                                    | Parameter                                                                                                                      | Min | Тур     | Max  | Unit           |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|----------------|

| t <sub>DLOCK</sub>                        | Time required to lock dynamically (after switchover, reconfiguring any non-post-scale counters/delays or areset is deasserted) | _   | _       | 1    | ms             |

| toutjitter_period_dedclk (6)              | Dedicated clock output period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                             | _   | _       | 300  | ps             |

|                                           | F <sub>OUT</sub> < 100 MHz                                                                                                     | _   | _       | 30   | mUI            |

| toutjitter_ccj_dedclk (6)                 | Dedicated clock output cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                     | _   | _       | 300  | ps             |

|                                           | F <sub>OUT</sub> < 100 MHz                                                                                                     | _   | _       | 30   | mUI            |

| t <sub>outjitter_period_io</sub> (6)      | Regular I/O period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                        | _   | _       | 650  | ps             |

|                                           | F <sub>OUT</sub> < 100 MHz                                                                                                     | _   | _       | 75   | mUI            |

| t <sub>OUTJITTER_CCJ_IO</sub> (6)         | Regular I/O cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                | _   | _       | 650  | ps             |

|                                           | F <sub>OUT</sub> < 100 MHz                                                                                                     | _   | _       | 75   | mUI            |

| t <sub>PLL_PSERR</sub>                    | Accuracy of PLL phase shift                                                                                                    | _   | _       | ±50  | ps             |

| t <sub>ARESET</sub>                       | Minimum pulse width on areset signal.                                                                                          | 10  | _       | _    | ns             |

| t <sub>CONFIGPLL</sub>                    | Time required to reconfigure scan chains for PLLs                                                                              | _   | 3.5 (7) | _    | SCANCLK cycles |

| f <sub>SCANCLK</sub>                      | scanclk frequency                                                                                                              | _   | _       | 100  | MHz            |

| t <sub>CASC_OUTJITTER_PERIOD_DEDCLK</sub> | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT} \ge 100 \text{ MHz}$ )                                    | _   | _       | 425  | ps             |

| (8), (9)                                  | Period jitter for dedicated clock output in cascaded PLLs (F <sub>OUT</sub> < 100 MHz)                                         |     |         | 42.5 | mUI            |

#### Notes to Table 1-25:

- (1) This table is applicable for general purpose PLLs and multipurpose PLLs.

- (2) You must connect  $V_{CCD\ PLL}$  to  $V_{CCINT}$  through the decoupling capacitor and ferrite bead.

- (3) This parameter is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (4) The  $V_{CO}$  frequency reported by the Quartus II software in the PLL Summary section of the compilation report takes into consideration the  $V_{CO}$  post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

- (5) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source that is less than 200 ps.

- (6) Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.9999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL when an input jitter of 30 ps is applied.

- (7) With 100-MHz scanclk frequency.

- $(8) \quad \text{The cascaded PLLs specification is applicable only with the following conditions:} \\$

- Upstream PLL—0.59 MHz ≤ Upstream PLL bandwidth < 1 MHz

- Downstream PLL—Downstream PLL bandwidth > 2 MHz

- (9) PLL cascading is not supported for transceiver applications.