### Intel - EP4CE10F17I7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 645                                                      |

| Number of Logic Elements/Cells | 10320                                                    |

| Total RAM Bits                 | 423936                                                   |

| Number of I/O                  | 179                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 256-LBGA                                                 |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce10f17i7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter Revision Dates    | ix     |

|---------------------------|--------|

| Additional Information    |        |

| How to Contact Altera I   | info–1 |

| Typographic Conventions I | info–1 |

| Section I. Device Core    |        |

| Chapter 1. Cyclone IV FPGA Device Family Overview    |  |

|------------------------------------------------------|--|

| Cyclone IV Device Family Features                    |  |

| Device Resources                                     |  |

| Package Matrix                                       |  |

| Cyclone IV Device Family Speed Grades                |  |

| Cyclone IV Device Family Architecture                |  |

| FPGA Core Fabric                                     |  |

| I/O Features                                         |  |

| Clock Management                                     |  |

| External Memory Interfaces                           |  |

| Configuration                                        |  |

| High-Speed Transceivers (Cyclone IV GX Devices Only) |  |

| Hard IP for PCI Express (Cyclone IV GX Devices Only) |  |

| Reference and Ordering Information                   |  |

| Document Revision History                            |  |

### Chapter 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

| Logic Elements            | 2–1 |

|---------------------------|-----|

| LE Features               | 2–2 |

| LE Operating Modes        | 2–3 |

| Normal Mode               | 2–3 |

| Arithmetic Mode           | 2–4 |

| Logic Array Blocks        | 2–5 |

| Topology                  | 2–5 |

| LAB Interconnects         | 2–6 |

| LAB Control Signals       | 2–6 |

| Document Revision History | 2–7 |

### Chapter 3. Memory Blocks in Cyclone IV Devices

| Overview                     | 3–1 |

|------------------------------|-----|

| Control Signals              | 3–3 |

| Parity Bit Support           | 3–3 |

| Byte Enable Support          | 3–3 |

| Packed Mode Support          |     |

| Address Clock Enable Support | 3–5 |

| Mixed-Width Support          |     |

| Asynchronous Clear           |     |

| Memory Modes                 | 3–7 |

| Single-Port Mode             |     |

| Simple Dual-Port Mode        |     |

# **Cyclone IV Device Family Speed Grades**

Table 1–5 lists the Cyclone IV GX devices speed grades.

| Device    | F169           | F324                         | F484                    | F672                    | F896       |            |  |

|-----------|----------------|------------------------------|-------------------------|-------------------------|------------|------------|--|

| EP4CGX15  | C6, C7, C8, I7 | —                            | —                       | —                       | —          |            |  |

| EP4CGX22  | C6, C7, C8, I7 | C6, C7, C8, I7               | —                       | —                       | —          |            |  |

| EP4CGX30  | C6, C7, C8, I7 | 6, C7, C8, I7 C6, C7, C8, I7 |                         | C6, C7, C8, I7 —        |            |            |  |

| EP4CGX50  | —              |                              |                         | C6, C7, C8, I7          | —          |            |  |

| EP4CGX75  | 24CGX75 —      |                              | C6, C7, C8, I7          | C6, C7, C8, I7          | —          |            |  |

| EP4CGX110 | —              | —                            | – C7, C8, I7 C7, C8, I7 |                         | C7, C8, I7 |            |  |

| EP4CGX150 | —              |                              |                         | — C7, C8, I7 C7, C8, I7 |            | C7, C8, I7 |  |

Table 1–5. Speed Grades for the Cyclone IV GX Device Family

Table 1–6 lists the Cyclone IV E devices speed grades.

| Table 1-6. | Speed Grades for the C | yclone IV E Device Family | (1), (2) |

|------------|------------------------|---------------------------|----------|

|------------|------------------------|---------------------------|----------|

| Device   | E144                                   | M164 | M256     | U256 | F256                                   | F324  | U484                                   | F484                                   | F780                            |

|----------|----------------------------------------|------|----------|------|----------------------------------------|-------|----------------------------------------|----------------------------------------|---------------------------------|

| EP4CE6   | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |      |          | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |       |                                        |                                        |                                 |

| EP4CE10  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _     | _                                      | _                                      | _                               |

| EP4CE15  | C8L, C9L, I8L<br>C6, C7, C8, I7        | I7N  | C7N, 17N | I7N  |                                        |       | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _                                      |                                 |

| EP4CE22  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _     | _                                      | _                                      | _                               |

| EP4CE30  | _                                      | _    | _        | _    | _                                      | A7N — |                                        | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE40  | _                                      | _    | _        | _    | _                                      | A7N   | I7N                                    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE55  | —                                      | _    | _        | _    | _                                      | _     | 17N                                    | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE75  | —                                      | _    | _        | _    | _                                      | _     | 17N                                    | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE115 | _                                      |      | _        | _    | _                                      |       |                                        | C8L, C9L, I8L<br>C7, C8, I7            | C8L, C9L, I8L<br>C7, C8, I7     |

#### Notes to Table 1-6:

(1) C8L, C9L, and I8L speed grades are applicable for the 1.0-V core voltage.

(2) C6, C7, C8, I7, and A7 speed grades are applicable for the 1.2-V core voltage.

# **Reference and Ordering Information**

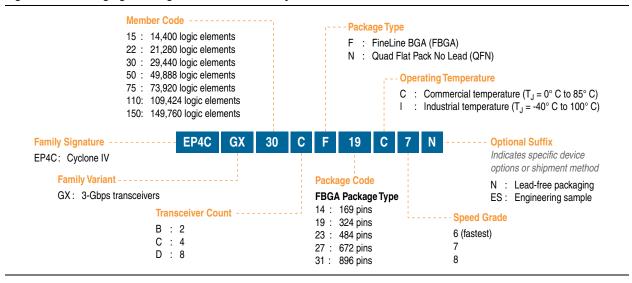

Figure 1-2 shows the ordering codes for Cyclone IV GX devices.

#### Figure 1–2. Packaging Ordering Information for the Cyclone IV GX Device

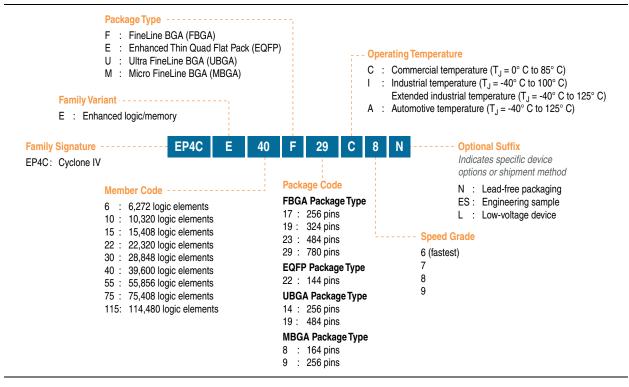

Figure 1–3 shows the ordering codes for Cyclone IV E devices.

In true dual-port mode, you can access any memory location at any time from either port A or port B. However, when accessing the same memory location from both ports, you must avoid possible write conflicts. When you attempt to write to the same address location from both ports at the same time, a write conflict happens. This results in unknown data being stored to that address location. There is no conflict resolution circuitry built into the Cyclone IV devices M9K memory blocks. You must handle address conflicts external to the RAM block.

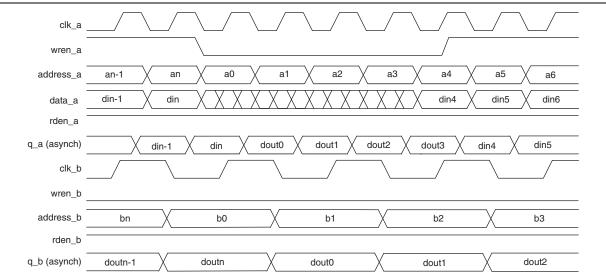

Figure 3–11 shows true dual-port timing waveforms for the write operation at port A and read operation at port B. Registering the outputs of the RAM simply delays the q outputs by one clock cycle.

Figure 3–11. Cyclone IV Devices True Dual-Port Timing Waveform

### **Shift Register Mode**

Cyclone IV devices M9K memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flipflops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

The size of a ( $w \times m \times n$ ) shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 9,216 bits. In addition, the size of ( $w \times n$ ) must be less than or equal to the maximum width of the block, which is 36 bits. If you need a larger shift register, you can cascade the M9K memory blocks.

# 4. Embedded Multipliers in Cyclone IV Devices

CYIV-51004-1.1

Cyclone<sup>®</sup> IV devices include a combination of on-chip resources and external interfaces that help increase performance, reduce system cost, and lower the power consumption of digital signal processing (DSP) systems. Cyclone IV devices, either alone or as DSP device co-processors, are used to improve price-to-performance ratios of DSP systems. Particular focus is placed on optimizing Cyclone IV devices for applications that benefit from an abundance of parallel processing resources, which include video and image processing, intermediate frequency (IF) modems used in wireless communications systems, and multi-channel communications and video systems.

This chapter contains the following sections:

- "Embedded Multiplier Block Overview" on page 4–1

- "Architecture" on page 4–2

- "Operational Modes" on page 4–4

# **Embedded Multiplier Block Overview**

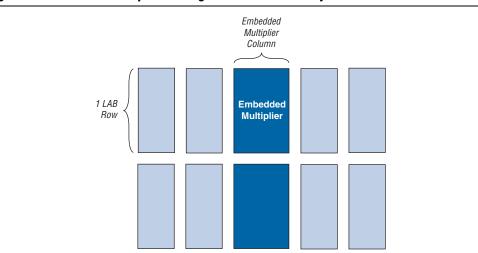

Figure 4–1 shows one of the embedded multiplier columns with the surrounding logic array blocks (LABs). The embedded multiplier is configured as either one  $18 \times 18$  multiplier or two  $9 \times 9$  multipliers. For multiplications greater than  $18 \times 18$ , the Quartus<sup>®</sup> II software cascades multiple embedded multiplier blocks together. There are no restrictions on the data width of the multiplier, but the greater the data width, the slower the multiplication process.

#### Figure 4–1. Embedded Multipliers Arranged in Columns with Adjacent LABs

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Cyclone IV Device Handbook, Volume 1 February 2010

For more information about the number of GCLK networks in each device density, refer to the *Cyclone IV FPGA Device Family Overview* chapter.

### **GCLK Network**

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks) can use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables and clears fed by an external pin. Internal logic can also drive GCLKs for internally generated GCLKs and asynchronous clears, clock enables, or other control signals with high fan-out.

Table 5–1, Table 5–2 on page 5–4, and Table 5–3 on page 5–7 list the connectivity of the clock sources to the GCLK networks.

Table 5-1. GCLK Network Connections for EP4CGX15, EP4CGX22, and EP4CGX30<sup>(1), (2)</sup> (Part 1 of 2)

| GCLK Network Clock            | GCLK Networks |              |              |              |              |              |              |              |   |              |              |              |              |              |              |              |              |              |              |              |

|-------------------------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Sources                       | 0             | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8 | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19           |

| CLK4/DIFFCLK_2n               |               | —            |              | _            | —            | $\checkmark$ | —            | $\checkmark$ | — | $\checkmark$ | —            | —            | —            | _            | —            | —            | —            | —            | —            | —            |

| CLK5/DIFFCLK_2p               | —             | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | _ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |

| CLK6/DIFFCLK_3n               |               | —            | —            |              | —            | —            | $\checkmark$ |              | > | $\checkmark$ | —            | —            | —            |              | —            | —            | —            | —            | —            | —            |

| CLK7/DIFFCLK_3p               | —             | —            |              | —            | —            | $\checkmark$ | —            | —            | > | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            |

| CLK8/DIFFCLK_5n               |               | —            |              |              | —            | —            |              |              |   | —            | $\checkmark$ | —            | $\checkmark$ |              | $\checkmark$ | —            |              |              | —            | —            |

| CLK9/DIFFCLK_5p               |               | —            |              |              | —            | —            | —            |              |   | —            | —            | $\checkmark$ | $\checkmark$ |              | —            | —            | —            | —            | —            | —            |

| CLK10/DIFFCLK_4n/RE<br>FCLK1n | _             | _            | _            | _            | _            | _            | _            | _            | _ | _            | _            | ~            | _            | ~            | ~            | _            | _            | _            | _            |              |

| CLK11/DIFFCLK_4p/RE<br>FCLK1p | _             | _            | _            | _            | _            | _            | _            | _            | _ | _            | ~            | _            |              | ~            |              | _            | _            | _            | _            | —            |

| CLK12/DIFFCLK_7p/RE<br>FCLK0p | _             | _            | —            | _            | _            | _            | _            | _            | _ | _            | _            | _            | _            | _            |              | ~            | _            | ~            | _            | ~            |

| CLK13/DIFFCLK_7n/RE<br>FCLK0n | _             | _            | —            | _            | _            | _            | _            | _            | _ | _            | _            | _            | _            | _            |              | —            | ~            | ~            | _            |              |

| CLK14/DIFFCLK_6p              | _             | —            | _            | _            | —            | _            | _            | _            |   | -            | -            | —            | —            | _            | -            |              | ~            | _            | <            | <            |

| CLK15/DIFFCLK_6n              |               |              | _            |              |              | _            |              |              |   | _            | _            | _            | _            |              | _            | >            |              |              | >            | —            |

| PLL_1_C0                      | $\checkmark$  |              |              | $\checkmark$ |              | —            |              |              |   | —            | —            | —            |              |              | —            | >            |              |              | $\checkmark$ | —            |

| PLL_1_C1                      | —             | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | — | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —            | $\checkmark$ |

| PLL_1_C2                      | $\checkmark$  |              | $\checkmark$ |              |              | —            |              |              |   | —            | —            | —            |              |              | —            | >            |              | $\checkmark$ | —            | —            |

| PLL_1_C3                      |               | $\checkmark$ |              | $\checkmark$ | —            | —            |              |              |   | —            | —            | —            | —            |              | —            | —            | $\checkmark$ |              | $\checkmark$ | —            |

| PLL_1_C4                      |               |              | $\checkmark$ |              | $\checkmark$ | —            |              |              |   | —            | —            | —            |              |              | —            |              |              | $\checkmark$ | —            | $\checkmark$ |

| PLL_2_C0                      | $\checkmark$  | —            | —            | $\checkmark$ | —            | —            | —            | —            | — | —            | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            |

| PLL_2_C1                      | —             | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | — | —            | —            | $\checkmark$ | —            | —            | $\checkmark$ | —            | —            | —            | —            | —            |

| PLL_2_C2                      | <b>&gt;</b>   |              | $\checkmark$ |              |              | —            |              |              |   | —            | $\checkmark$ | —            | $\checkmark$ |              | —            |              |              |              | —            | —            |

| PLL_2_C3                      | —             | <b>~</b>     | —            | >            | —            | —            | —            | —            | — | —            | —            | ~            | —            | >            | —            | —            | —            | —            | —            | _            |

| PLL_2_C4                      | —             | —            | <b>&gt;</b>  | —            | >            | —            | —            | —            | — | —            | —            | —            | >            | —            | >            | —            | —            | —            | —            | -            |

| PLL_3_C0                      | —             | —            | —            | —            | —            | >            | —            | —            | > | _            | _            | —            | —            | —            | _            | $\checkmark$ | —            | —            | >            | -            |

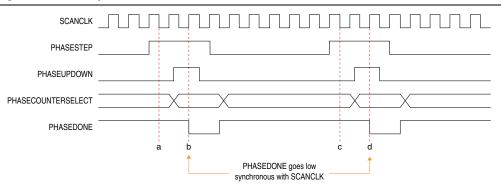

Figure 5–26 shows the dynamic phase shifting waveform.

The PHASESTEP signal is latched on the negative edge of SCANCLK (a,c) and must remain asserted for at least two SCANCLK cycles. Deassert PHASESTEP after PHASEDONE goes low. On the second SCANCLK rising edge (b,d) after PHASESTEP is latched, the values of PHASEUPDOWN and PHASECOUNTERSELECT are latched and the PLL starts dynamic phase-shifting for the specified counters, and in the indicated direction. PHASEDONE is deasserted synchronous to SCANCLK at the second rising edge (b,d) and remains low until the PLL finishes dynamic phase-shifting. Depending on the VCO and SCANCLK frequencies, PHASEDONE low time may be greater than or less than one SCANCLK cycle.

You can perform another dynamic phase-shift after the PHASEDONE signal goes from low to high. Each PHASESTEP pulse enables one phase shift. PHASESTEP pulses must be at least one SCANCLK cycle apart.

For information about the ALTPLL\_RECONFIG MegaWizard<sup>™</sup> Plug-In Manager, refer to the *ALTPLL\_RECONFIG Megafunction User Guide*.

## Spread-Spectrum Clocking

Cyclone IV devices can accept a spread-spectrum input with typical modulation frequencies. However, the device cannot automatically detect that the input is a spread-spectrum signal. Instead, the input signal looks like deterministic jitter at the input of the PLL. PLLs of Cyclone IV devices can track a spread-spectrum input clock as long as it is in the input jitter tolerance specifications and the modulation frequency of the input clock is below the PLL bandwidth, that is specified in the fitter report. Cyclone IV devices cannot generate spread-spectrum signals internally.

# **PLL Specifications**

For information about PLL specifications, refer to the Cyclone IV Device Datasheet chapter. The IOE registers in each I/O block share the same source for the preset or clear features. You can program preset or clear for each individual IOE, but you cannot use both features simultaneously. You can also program the registers to power-up high or low after configuration is complete. If programmed to power-up low, an asynchronous clear can control the registers. If programmed to power-up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of the active-low input of another device upon power-up. If one register in an IOE uses a preset or clear signal, all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

**For more information about the input and output pin delay settings, refer to the** *Area and Timing Optimization* chapter in volume 2 of the *Quartus II Handbook*.

### **PCI-Clamp Diode**

Cyclone IV devices provide an optional PCI-clamp diode enabled input and output for each I/O pin. Dual-purpose configuration pins support the diode in user mode if the specific pins are not used as configuration pins for the selected configuration scheme. For example, if you are using the active serial (AS) configuration scheme, you cannot use the clamp diode on the ASDO and nCSO pins in user mode. Dedicated configuration pins do not support the on-chip diode.

The PCI-clamp diode is available for the following I/O standards:

- 3.3-V LVTTL

- 3.3-V LVCMOS

- 3.0-V LVTTL

- 3.0-V LVCMOS

- 2.5-V LVTTL/LVCMOS

- PCI

- PCI-X

If the input I/O standard is one of the listed standards, the PCI-clamp diode is enabled by default in the Quartus II software.

### **OCT Support**

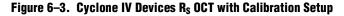

Cyclone IV devices feature OCT to provide I/O impedance matching and termination capabilities. OCT helps prevent reflections and maintain signal integrity while minimizing the need for external resistors in high pin-count ball grid array (BGA) packages. Cyclone IV devices provide I/O driver on-chip impedance matching and R<sub>S</sub> OCT for single-ended outputs and bidirectional pins.

$\mathbb{L}$  When using R<sub>S</sub> OCT, programmable current strength is not available.

There are two ways to implement OCT in Cyclone IV devices:

- OCT with calibration

- OCT without calibration

Figure 6–3 shows the external calibration resistors setup on the RUP and RDN pins and the associated OCT calibration circuitry.

RUP and RDN pins go to a tri-state condition when calibration is completed or not running. These two pins are dual-purpose I/Os and function as regular I/Os if you do not use the calibration circuit.

### **On-Chip Series Termination Without Calibration**

Cyclone IV devices support driver impedance matching to match the impedance of the transmission line, which is typically 25 or 50  $\Omega$ . When used with the output drivers, OCT sets the output driver impedance to 25 or 50  $\Omega$ . Cyclone IV devices also support I/O driver series termination (R<sub>S</sub> = 50  $\Omega$ ) for SSTL-2 and SSTL-18.

Table 6–6 and Table 6–7 summarize which I/O banks support these I/O standards in the Cyclone IV device family.

| Differential I/O Standards                           | I/O Bank Location | External Resistor<br>Network at Transmitter | Transmitter (TX)      | Receiver (RX) |  |

|------------------------------------------------------|-------------------|---------------------------------------------|-----------------------|---------------|--|

| LVDS                                                 | 1,2,5,6           | Not Required                                | <ul> <li>✓</li> </ul> | $\checkmark$  |  |

|                                                      | All               | Three Resistors                             | ▼                     | ~             |  |

|                                                      | 1,2,5,6           | Not Required                                |                       |               |  |

| RSDS                                                 | 3,4,7,8           | Three Resistors                             | ~                     | —             |  |

|                                                      | All               | Single Resistor                             | -                     |               |  |

| mini-LVDS                                            | 1,2,5,6           | Not Required                                | <ul> <li>✓</li> </ul> |               |  |

| IIIIII-LVD3                                          | All               | Three Resistors                             | ~                     |               |  |

| PPDS                                                 | 1,2,5,6           | Not Required                                | <ul> <li>✓</li> </ul> |               |  |

| FFD3                                                 | All               | Three Resistors                             | ~                     | —             |  |

| BLVDS (1)                                            | All               | Single Resistor                             | $\checkmark$          | $\checkmark$  |  |

| LVPECL (2)                                           | All               | —                                           | —                     | $\checkmark$  |  |

| Differential SSTL-2 (3)                              | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential SSTL-18 (3)                             | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-18 (3)                             | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-15 (3)                             | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

| Differential HSTL-12 <sup>(3)</sup> , <sup>(4)</sup> | All               | —                                           | $\checkmark$          | $\checkmark$  |  |

Table 6-6. Differential I/O Standards Supported in Cyclone IV E I/O Banks

#### Notes to Table 6-6:

(1) Transmitter and Receiver  $f_{\text{MAX}}$  depend on system topology and performance requirement.

(2) The LVPECL I/O standard is only supported on dedicated clock input pins.

(3) The differential SSTL-2, SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards are only supported on clock input pins and PLL output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-15, and HSTL-12 I/O standards.

(4) Differential HSTL-12 Class II is supported only in column I/O banks.

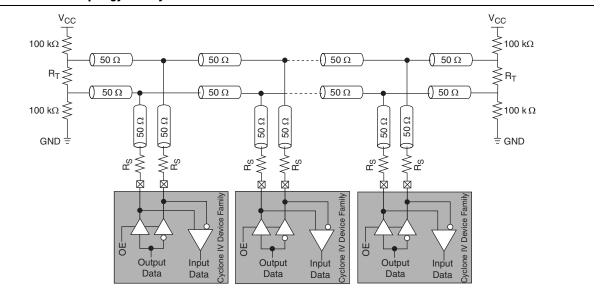

Figure 6–14 shows a typical BLVDS topology with multiple transmitter and receiver pairs.

The BLVDS I/O standard is supported on the top, bottom, and right I/O banks of Cyclone IV devices. The BLVDS transmitter uses two single-ended output buffers with the second output buffer programmed as inverted, while the BLVDS receiver uses a true LVDS input buffer. The transmitter and receiver share the same pins. An output-enabled (OE) signal is required to tristate the output buffers when the LVDS input buffer receives a signal.

For more information, refer to the *Cyclone IV Device Datasheet* chapter.

### **Designing with BLVDS**

The BLVDS bidirectional communication requires termination at both ends of the bus in BLVDS. The termination resistor ( $R_T$ ) must match the bus differential impedance, which in turn depends on the loading on the bus. Increasing the load decreases the bus differential impedance. With termination at both ends of the bus, termination is not required between the two signals at the input buffer. A single series resistor ( $R_S$ ) is required at the output buffer to match the output buffer impedance to the transmission line impedance. However, this series resistor affects the voltage swing at the input buffer. The maximum data rate achievable depends on many factors.

Altera recommends that you perform simulation using the IBIS model while considering factors such as bus loading, termination values, and output and input buffer location on the bus to ensure that the required performance is achieved.

**For more information about BLVDS interface support in Altera devices, refer to** *AN 522: Implementing Bus LVDS Interface in Supported Altera Device Families.*

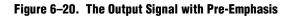

before the next edge; this may lead to pattern-dependent jitter. With pre-emphasis, the output current is momentarily boosted during switching to increase the output slew rate. The overshoot produced by this extra switching current is different from the overshoot caused by signal reflection. This overshoot happens only during switching, and does not produce ringing.

The Quartus II software allows two settings for programmable pre-emphasis control—0 and 1, in which 0 is pre-emphasis off and 1 is pre-emphasis on. The default setting is 1. The amount of pre-emphasis needed depends on the amplification of the high-frequency components along the transmission line. You must adjust the setting to suit your designs, as pre-emphasis decreases the amplitude of the low-frequency component of the output signal.

Figure 6–20 shows the differential output signal with pre-emphasis.

# **High-Speed I/O Timing**

This section discusses the timing budget, waveforms, and specifications for source-synchronous signaling in Cyclone IV devices. Timing for source-synchronous signaling is based on skew between the data and clock signals.

High-speed differential data transmission requires timing parameters provided by IC vendors and requires you to consider the board skew, cable skew, and clock jitter. This section provides information about high-speed I/O standards timing parameters in Cyclone IV devices.

Table 6–11 defines the parameters of the timing diagram shown in Figure 6–21.

Table 6–11. High-Speed I/O Timing Definitions (Part 1 of 2)

| Parameter                                          | Symbol | Description                                                                                                                                                                                                                       |

|----------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter channel-to-channel skew <sup>(1)</sup> | TCCS   | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.                                                                   |

| Sampling window                                    | sw     | The period of time during which the data must be valid in order for you to capture it correctly. The setup and hold times determine the ideal strobe position in the sampling window.<br>$T_{SW} = T_{SU} + T_{hd} + PLL$ jitter. |

| Time unit interval                                 | TUI    | The TUI is the data-bit timing budget allowed for skew, propagation delays, and data sampling window.                                                                                                                             |

| Receiver input skew margin                         | RSKM   | RSKM is defined by the total margin left after accounting for the sampling window and TCCS. The RSKM equation is:<br>$SKM = \frac{(TUI - SW - TCCS)}{2}$                                                                          |

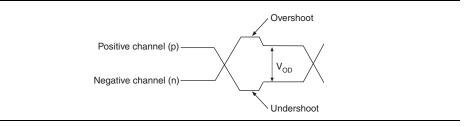

### **DDR Output Registers**

A dedicated write DDIO block is implemented in the DDR output and output enable paths.

Figure 7–8 shows how a Cyclone IV dedicated write DDIO block is implemented in the I/O element (IOE) registers.

Figure 7–8. Cyclone IV Dedicated Write DDIO

The two DDR output registers are located in the I/O element (IOE) block. Two serial data streams routed through datain\_l and datain\_h, are fed into two registers, output register Ao and output register Bo, respectively, on the same clock edge. The output from output register Ao is captured on the falling edge of the clock, while the output from output register Bo is captured on the rising edge of the clock. The registered outputs are multiplexed by the common clock to drive the DDR output pin at twice the data rate.

The DDR output enable path has a similar structure to the DDR output path in the IOE block. The second output enable register provides the write preamble for the DQS strobe in DDR external memory interfaces. This active-low output enable register extends the high-impedance state of the pin by half a clock cycle to provide the external memory's DQS write preamble time specification.

For more information about Cyclone IV IOE registers, refer to the *Cyclone IV Device I/O Features* chapter.

# Table 8–4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 2 of 2)

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------|

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   | _         | —                                           |

#### Notes to Table 8-4:

(1) Configuration voltage standard applied to the V<sub>CCIO</sub> supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

> Smaller Cyclone IV E devices or package options (E144 and F256 packages) do not have the MSEL[3] pin. The AS Fast POR configuration scheme at 3.0- or 2.5-V configuration voltage standard and the AP configuration scheme are not supported in Cyclone IV E devices without the MSEL[3] pin. To configure these devices with other supported configuration schemes, select MSEL[2..0] pins according to the MSEL settings in Table 8–5.

| Configuration Scheme         | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-------|-----------|---------------------------------------------------|

| AS                           | 1     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 0     | 0     | Fast      | 3.0, 2.5                                          |

|                              | 0     | 0     | 1     | 0     | Standard  | 3.3                                               |

|                              | 0     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

| AP                           | 0     | 1     | 0     | 1     | Fast      | 3.3                                               |

|                              | 0     | 1     | 1     | 0     | Fast      | 1.8                                               |

|                              | 0     | 1     | 1     | 1     | Standard  | 3.3                                               |

|                              | 1     | 0     | 1     | 1     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | 0     | Standard  | 1.8                                               |

| PS                           | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

|                              | 0     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| FPP                          | 1     | 1     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

|                              | 1     | 1     | 1     | 1     | Fast      | 1.8, 1.5                                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | (3)   |           | —                                                 |

Table 8–5. Configuration Schemes for Cyclone IV E Devices

#### Notes to Table 8-5:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration. Table 8–21 lists the optional configuration pins. If you do not enable these optional configuration pins in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

| Pin Name   | Pin Name User Mode                            |                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLKUSR I/O | N/A if option is on.                          | Input                | Optional user-supplied clock input synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|            | I/O if option is off.                         |                      | In AS configuration for Cyclone IV GX devices, you can use this pin as an external clock source to generate the DCLK by changing the clock source option in the Quartus II software in the <b>Configuration</b> tab of the <b>Device and Pin Options</b> dialog box.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| INIT_DONE  | N/A if option is on.<br>I/O if option is off. | Output<br>open-drain | Status pin is used to indicate when the device has initialized and<br>is in user-mode. When nCONFIG is low, the INIT_DONE pin is<br>tri-stated and pulled high due to an external 10-k $\Omega$ pull-up<br>resistor during the beginning of configuration. After the option<br>bit to enable INIT_DONE is programmed into the device (during<br>the first frame of configuration data), the INIT_DONE pin goes<br>low. When initialization is complete, the INIT_DONE pin is<br>released and pulled high and the device enters user mode.<br>Thus, the monitoring circuitry must be able to detect a low-to-<br>high transition. This pin is enabled by turning on the <b>Enable</b><br><b>INIT_DONE output</b> option in the Quartus II software. |  |  |

|            |                                               |                      | The functionality of this pin changes if the <b>Enable OCT_DONE</b> option is enabled in the Quartus II software. This option controls whether the INIT_DONE signal is gated by the OCT_DONE signal, which indicates the power-up on-chip termination (OCT) calibration is complete. If this option is turned off, the INIT_DONE signal is not gated by the OCT_DONE signal.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| DEV_OE     | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as programmed. This pin is enabled by turning on the <b>Enable device-wide output enable (DEV_OE)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| DEV_CLRn   | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all clears on all device<br>registers. When this pin is driven low, all registers are cleared;<br>when this pin is driven high, all registers behave as<br>programmed. You can enable this pin by turning on the <b>Enable</b><br><b>device-wide reset (DEV_CLRn)</b> option in the Quartus II<br>software.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Table 8–21. Optional Configuration Pins

Table 2–2 lists the power-down signals available for each transceiver block.

Table 2–2. Transceiver Block Power-Down Signals

| Signal        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | Resets the transceiver PLL. The pll_areset signal is asserted in two conditions:                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| pll_areset    | <ul> <li>During reset sequence, the signal is asserted to reset the transceiver PLL. This signal is<br/>controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |  |  |

|               | <ul> <li>After the transceiver PLL is reconfigured, the signal is asserted high by the<br/>ALTPLL_RECONFIG controller. This signal is not controlled by the user.</li> </ul>                                                                                                                                                                                                                                                                                                                          |  |  |

| gxb_powerdown | Powers down the entire transceiver block. When this signal is asserted, this signal powers down the PCS and PMA in all the transceiver channels.                                                                                                                                                                                                                                                                                                                                                      |  |  |

|               | This signal operates independently from the other reset signals. This signal is common to the transceiver block.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| pll_locked    | A status signal. Indicates the status of the transmitter multipurpose PLLs or general purpose PLLs.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|               | <ul> <li>A high level—indicates the multipurpose PLL or general purpose PLL is locked to the<br/>incoming reference clock frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |  |  |

|               | A status signal. Indicates the status of the receiver CDR lock mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| rx_freqlocked | A high level—the receiver is in lock-to-data mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|               | A low level—the receiver CDR is in lock-to-reference mode.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| busy          | A status signal. An output from the ALTGX_RECONFIG block indicates the status of the dynamic reconfiguration controller. This signal remains low for the first reconfig_cll clock cycle after power up. It then gets asserted from the second reconfig_clk clock cycle. Assertion on this signal indicates that the offset cancellation process is being executed on the receiver buffer as well as the receiver CDR. When this signal is deassert it indicates that offset cancellation is complete. |  |  |

|               | This busy signal is also used to indicate the dynamic reconfiguration duration such as in analog reconfiguration mode and channel reconfiguration mode.                                                                                                                                                                                                                                                                                                                                               |  |  |

- For more information about offset cancellation, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

- If none of the channels is instantiated in a transceiver block, the Quartus<sup>®</sup> II software automatically powers down the entire transceiver block.

### **Blocks Affected by the Reset and Power-Down Signals**

Table 2–3 lists the blocks that are affected by specific reset and power-down signals.

| Table 2–3. Blocks Affected by Reset and Power-Down Signals | (Part 1 of 2) |

|------------------------------------------------------------|---------------|

|------------------------------------------------------------|---------------|

| Transceiver Block                          | rx_digitalreset | rx_analogreset | tx_digitalreset | pll_areset   | gxb_powerdown |

|--------------------------------------------|-----------------|----------------|-----------------|--------------|---------------|

| multipurpose PLLs and general purpose PLLs | —               | _              | _               | $\checkmark$ | _             |

| Transmitter Phase<br>Compensation FIFO     | _               | _              | ~               | _            | ~             |

| Byte Serializer                            | _               |                | $\checkmark$    | _            | $\checkmark$  |

| 8B/10B Encoder                             | —               | —              | ~               |              | $\checkmark$  |

September 2014 Altera Corporation

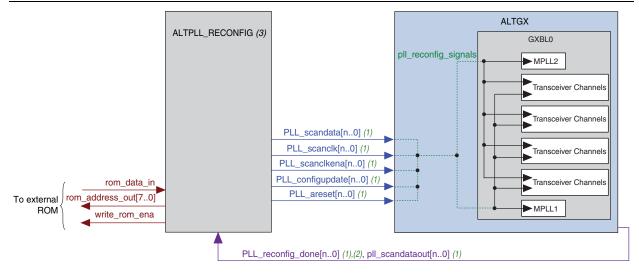

The .**mif** files carries the reconfiguration information that will be used to reconfigure the multipurpose PLL or general purpose PLL dynamically. The .**mif** contents is generated automatically when you select the **Enable PLL Reconfiguration** option in the **Reconfiguration Setting** in ALTGX instances. The .**mif** files will be generated based on the data rate and input reference clock setting in the ALTGX MegaWizard. You must use the external ROM and feed its content to the ALTPLL\_RECONFIG megafunction to reconfigure the multipurpose PLL setting.

Figure 3–16 shows the connection for PLL reconfiguration mode.

#### Notes to Figure 3–16:

- (1)  $\langle n \rangle =$  (number of transceiver PLLs configured in the ALTGX MegaWizard) 1.

- (2) You must connect the pll\_reconfig\_done signal from the ALTGX to the pll\_scandone port from ALTPLL\_RECONFIG.

(3) You need two ALTPLL\_RECONFIG controllers if you have two separate ALTGX instances with transceiver PLL instantiated in each ALTGX instance.

For more information about connecting the ALTPLL\_RECONFIG and ALTGX instances, refer to the AN 609: Implementing Dynamic Reconfiguration in Cyclone IV GX Devices.