Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 7155                                                       |

| Number of Logic Elements/Cells | 114480                                                     |

| Total RAM Bits                 | 3981312                                                    |

| Number of I/O                  | 280                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.97V ~ 1.03V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 484-BGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f23c8ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 5-5. Cyclone IV GX PLL Features (Part 2 of 2)

|                                                                      |                                       |                    |                          |                          | Availa | Availability |          |   |       |  |  |  |

|----------------------------------------------------------------------|---------------------------------------|--------------------|--------------------------|--------------------------|--------|--------------|----------|---|-------|--|--|--|

| Features                                                             | General Purpose PLLs Multipurpose PLL |                    |                          | S                        |        |              |          |   |       |  |  |  |

|                                                                      | PLL_1<br>(1), (10)                    | PLL_2<br>(1), (10) | PLL_<br>3 <sup>(2)</sup> | PLL_<br>4 <sup>(3)</sup> |        |              |          |   | PLL_8 |  |  |  |

| Input clock switchover                                               | <b>√</b>                              |                    |                          |                          |        |              |          |   |       |  |  |  |

| User mode reconfiguration                                            |                                       |                    |                          |                          | •      | /            |          |   |       |  |  |  |

| Loss of lock detection                                               | ✓                                     |                    |                          |                          |        |              |          |   |       |  |  |  |

| PLL drives TX Serial Clock, TX Load<br>Enable, and TX Parallel Clock | ✓                                     |                    |                          |                          |        |              |          |   |       |  |  |  |

| VCO output drives RX clock data recovery (CDR) clock                 |                                       |                    |                          |                          |        |              |          |   |       |  |  |  |

| PLL drives FREF for ppm detect                                       | ✓                                     | <b>✓</b>           |                          |                          |        |              | <b>~</b> | / |       |  |  |  |

#### Notes to Table 5-5:

- (1) This is only applicable to EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F672 and F896 package.

- (2) This is applicable to all Cyclone IV devices.

- (3) This is applicable to all Cyclone IV devices except EP4CGX15 devices in all packages, EP4CGX22, and EP4CGX30 devices in F169 package.

- (4) This is only applicable to EP4CGX15, EP4CGX22, and all EP4CGX30 devices except EP4CGX30 in the F484 package..

- (5) C counters range from 1 through 512 if the output clock uses a 50% duty cycle. For any output clocks using a non-50% duty cycle, the post-scale counters range from 1 through 256.

- (6) These clock pins can access the GCLK networks.

- (7) These clock pins are only available in EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices and cannot access the GCLK networks. CLK [17, 19, 20, 21] p can be used as single-ended clock input pins.

- (8) Only applicable if the input clock jitter is in the input jitter tolerance specifications.

- (9) The smallest phase shift is determined by the voltage-controlled oscillator (VCO) period divided by eight. For degree increments, Cyclone IV GX devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (10) This is applicable to the EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

Table 5–6 lists the features available in Cyclone IV E PLLs.

Table 5-6. Cyclone IV E PLL Features (Part 1 of 2)

| Hardware Features                    | Availability                                                                           |

|--------------------------------------|----------------------------------------------------------------------------------------|

| C (output counters)                  | 5                                                                                      |

| M, N, C counter sizes                | 1 to 512 <sup>(1)</sup>                                                                |

| Dedicated clock outputs              | 1 single-ended or 1 differential pair                                                  |

| Clock input pins                     | 4 single-ended or 2 differential pairs                                                 |

| Spread-spectrum input clock tracking | ✓ (2)                                                                                  |

| PLL cascading                        | Through GCLK                                                                           |

| Compensation modes                   | Source-Synchronous Mode, No Compensation Mode, Normal Mode, and Zero Delay Buffer Mode |

| Phase shift resolution               | Down to 96-ps increments <sup>(3)</sup>                                                |

| Programmable duty cycle              | <b>✓</b>                                                                               |

| Output counter cascading             | <b>✓</b>                                                                               |

| Input clock switchover               | <b>✓</b>                                                                               |

| User mode reconfiguration            | ~                                                                                      |

Table 5-6. Cyclone IV E PLL Features (Part 2 of 2)

| Hardware Features      | Availability |

|------------------------|--------------|

| Loss of lock detection | ✓            |

#### Notes to Table 5-6:

- C counters range from 1 through 512 if the output clock uses a 50% duty cycle. For any output clocks using a non-50% duty cycle, the post-scale counters range from 1 through 256.

- (2) Only applicable if the input clock jitter is in the input jitter tolerance specifications.

- (3) The smallest phase shift is determined by the VCO period divided by eight. For degree increments, Cyclone IV E devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

# **Cyclone IV PLL Hardware Overview**

This section gives a hardware overview of the Cyclone IV PLL.

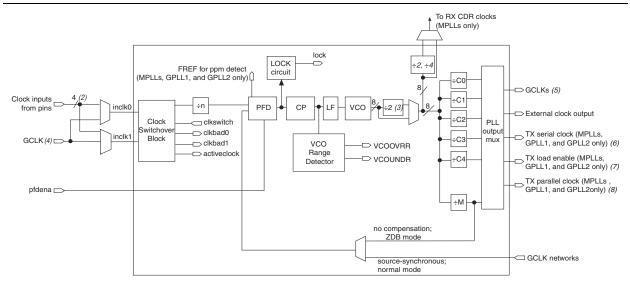

Figure 5–9 shows a simplified block diagram of the major components of the PLL of Cyclone IV GX devices.

Figure 5–9. Cyclone IV GX PLL Block Diagram (1)

### Notes to Figure 5-9:

- (1) Each clock source can come from any of the four clock pins located on the same side of the device as the PLL.

- (2) There are additional 4 pairs of dedicated differential clock inputs in EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices that can only drive general purpose PLLs and multipurpose PLLs on the left side of the device. CLK[19..16] can access PLL \_2, PLL \_6, PLL \_7, and PLL \_8 while CLK[23..20] can access PLL \_1, PLL \_5, PLL \_6, and PLL \_7. For the location of these clock input pins, refer to Figure 5–3 on page 5–13.

- (3) This is the VCO post-scale counter K.

- (4) This input port is fed by a pin-driven dedicated GCLK, or through a clock control block if the clock control block is fed by an output from another PLL or a pin-driven dedicated GCLK. An internally generated global signal cannot drive the PLL.

- (5) For the general purpose PLL and multipurpose PLL counter outputs connectivity to the GCLKs, refer to Table 5–1 on page 5–2 and Table 5–2 on page 5–4

- (6) Only the CI output counter can drive the TX serial clock.

- (7) Only the C2 output counter can drive the TX load enable.

- (8) Only the C3 output counter can drive the TX parallel clock.

# **Configuration Scheme**

A configuration scheme with different configuration voltage standards is selected by driving the MSEL pins either high or low, as shown in Table 8–3, Table 8–4, and Table 8–5.

Hardwire the MSEL pins to  $V_{CCA}$  or GND without pull-up or pull-down resistors to avoid problems detecting an incorrect configuration scheme. Do not drive the MSEL pins with a microprocessor or another device.

Table 8–3. Configuration Schemes for Cyclone IV GX Devices (EP4CGX15, EP4CGX22, and EP4CGX30 [except for F484 Package])

| Configuration Scheme         | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|------------------------------|-------|-------|-------|-----------|---------------------------------------------------|

|                              | 1     | 0     | 1     | Fast      | 3.3                                               |

| AS                           | 0     | 1     | 1     | Fast      | 3.0, 2.5                                          |

| AO                           | 0     | 0     | 1     | Standard  | 3.3                                               |

|                              | 0     | 1     | 0     | Standard  | 3.0, 2.5                                          |

|                              | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                                     |

| PS                           | 1     | 1     | 0     | Fast      | 1.8, 1.5                                          |

|                              | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                                     |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | _         | _                                                 |

#### Notes to Table 8-3:

- (1) Configuration voltage standard applied to the  $V_{\text{CCIO}}$  supply of the bank in which the configuration pins reside.

- (2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

- (3) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

Table 8-4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 1 of 2)

| Configuration Scheme | MSEL3 | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) (1) |

|----------------------|-------|-------|-------|-------|-----------|----------------------------------------|

|                      | 1     | 1     | 0     | 1     | Fast      | 3.3                                    |

| AS                   | 1     | 0     | 1     | 1     | Fast      | 3.0, 2.5                               |

| AS                   | 1     | 0     | 0     | 1     | Standard  | 3.3                                    |

|                      | 1     | 0     | 1     | 0     | Standard  | 3.0, 2.5                               |

|                      | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                          |

| PS                   | 1     | 1     | 1     | 0     | Fast      | 1.8, 1.5                               |

| F3                   | 1     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                          |

|                      | 0     | 0     | 0     | 0     | Standard  | 1.8, 1.5                               |

|                      | 0     | 0     | 1     | 1     | Fast      | 3.3, 3.0, 2.5                          |

| FPP                  | 0     | 1     | 0     | 0     | Fast      | 1.8, 1.5                               |

| ree<br>              | 0     | 0     | 0     | 1     | Standard  | 3.3, 3.0, 2.5                          |

|                      | 0     | 0     | 1     | 0     | Standard  | 1.8, 1.5                               |

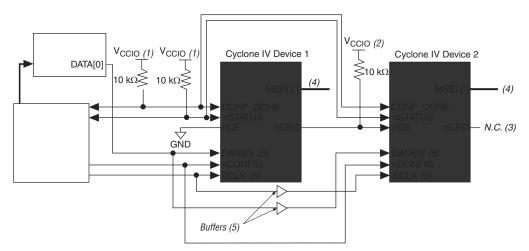

To ensure DCLK and DATA [0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA [0] pin is available as a user I/O pin after configuration. In the PS scheme, the DATA [0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

Figure 8–14 shows how to configure multiple devices using an external host device. This circuit is similar to the PS configuration circuit for a single device, except that Cyclone IV devices are cascaded for multi-device configuration.

Figure 8-14. Multi-Device PS Configuration Using an External Host

### Notes to Figure 8-14:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain. V<sub>CC</sub> must be high enough to meet the V<sub>IH</sub> specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

# **FPP Configuration**

The FPP configuration in Cyclone IV devices is designed to meet the increasing demand for faster configuration time. Cyclone IV devices are designed with the capability of receiving byte-wide configuration data per clock cycle.

You can perform FPP configuration of Cyclone IV devices with an intelligent host, such as a MAX II device or microprocessor with flash memory. If your system already contains a CFI flash memory, you can use it for the Cyclone IV device configuration storage as well. The MAX II PFL feature in MAX II devices provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control configuration from the flash memory device to the Cyclone IV device.

- For more information about the PFL, refer to AN 386: Using the Parallel Flash Loader with the Quartus II Software.

- FPP configuration is supported in EP4CGX30 (only for F484 package), EP4CGX50, EP4CGX75, EP4CGX110, EP4CGX150, and all Cyclone IV E devices.

- The FPP configuration is not supported in E144 package of Cyclone IV E devices.

- Cyclone IV devices do not support enhanced configuration devices for FPP configuration.

## **FPP Configuration Using an External Host**

FPP configuration using an external host provides a fast method to configure Cyclone IV devices. In the FPP configuration scheme, you can use an external host device to control the transfer of configuration data from a storage device, such as flash memory, to the target Cyclone IV device. You can store configuration data in an .rbf, .hex, or .ttf format. When using the external host, a design that controls the configuration process, such as fetching the data from flash memory and sending it to

Figure 8–31 shows the block diagrams to implement remote system upgrade in Cyclone IV devices.

Figure 8-31. Remote System Upgrade Block Diagrams for AS and AP Configuration Schemes

The MSEL pin setting in the remote system upgrade mode is the same as the standard configuration mode. Standard configuration mode refers to normal Cyclone IV device configuration mode with no support for remote system upgrades (the remote system upgrade circuitry is disabled). When using remote system upgrade in Cyclone IV devices, you must enable the remote update mode option setting in the Quartus II software.

# **Enabling Remote Update**

You can enable or disable remote update for Cyclone IV devices in the Quartus II software before design compilation (in the Compiler Settings menu). To enable remote update in the compiler settings of the project, perform the following steps:

- 1. On the Assignments menu, click **Device**. The **Settings** dialog box appears.

- 2. Click **Device and Pin Options**. The **Device and Pin Options** dialog box appears.

- 3. Click the **Configuration** tab.

- 4. From the **Configuration Mode** list, select **Remote**.

- 5. Click OK.

- 6. In the **Settings** dialog box, click **OK**.

### **Configuration Image Types**

When using remote system upgrade, Cyclone IV device configuration bitstreams are classified as factory configuration images or application configuration images. An image, also referred to as a configuration, is a design loaded into the device that performs certain user-defined functions. Each device in your system requires one factory image or with addition of one or more application images. The factory image is a user-defined fall-back or safe configuration and is responsible for administering remote updates with the dedicated circuitry. Application images implement user-defined functionality in the target Cyclone IV device. You can include the default application image functionality in the factory image.

# **Architectural Overview**

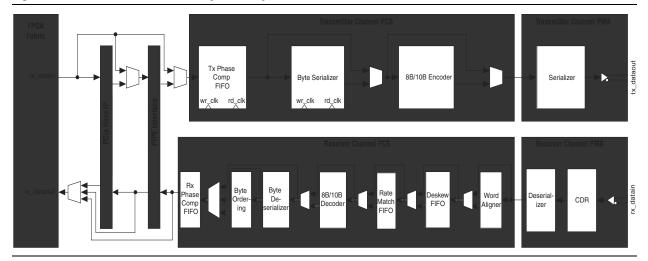

Figure 1–3 shows the Cyclone IV GX transceiver channel datapath.

Figure 1–3. Transceiver Channel Datapath for Cyclone IV GX Devices

Each transceiver channel consists of a transmitter and a receiver datapath. Each datapath is further structured into the following:

- Physical media attachment (PMA)—includes analog circuitry for I/O buffers, clock data recovery (CDR), serializer/deserializer (SERDES), and programmable pre-emphasis and equalization to optimize serial data channel performance.

- Physical coding sublayer (PCS)—includes hard logic implementation of digital functionality within the transceiver that is compliant with supported protocols.

Outbound parallel data from the FPGA fabric flows through the transmitter PCS and PMA, is transmitted as serial data. Received inbound serial data flows through the receiver PMA and PCS into the FPGA fabric. The transceiver supports the following interface widths:

- FPGA fabric-transceiver PCS—8, 10, 16, or 20 bits

- PMA-PCS—8 or 10 bits

- The transceiver channel interfaces through the PIPE when configured for PCIe protocol implementation. The PIPE is compliant with version 2.00 of the PHY Interface for the PCI Express Architecture specification.

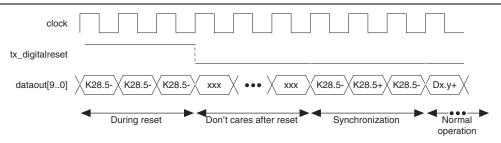

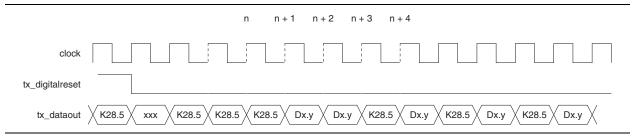

The following describes the 8B/10B encoder behavior in reset condition (as shown in Figure 1–7):

- During reset, the 8B/10B encoder ignores the inputs (tx\_datain and tx\_ctrlenable ports) from the FPGA fabric and outputs the K28.5 pattern from the RD- column continuously until the tx\_digitalreset port is deasserted.

- Upon deassertion of the tx\_digitalreset port, the 8B/10B encoder starts with a negative disparity and transmits three K28.5 code groups for synchronization before it starts encoding and transmitting data on its output.

- Due to some pipelining of the transmitter PCS, some "don't cares" (10'hxxx) are sent before the three synchronizing K28.5 code groups.

Figure 1-7. 8B/10B Encoder Behavior in Reset Condition

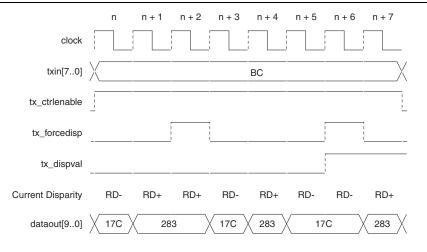

The encoder supports forcing the running disparity to either positive or negative disparity with tx\_forcedisp and tx\_dispval ports. Figure 1–8 shows an example of tx\_forcedisp and tx\_dispval port use, where data is shown in hexadecimal radix.

Figure 1–8. Force Running Disparity Operation

In this example, a series of K28.5 code groups are continuously sent. The stream alternates between a positive disparity K28.5 (RD+) and a negative disparity K28.5 (RD-) to maintain a neutral overall disparity. The current running disparity at time n+1 indicates that the K28.5 in time n+2 should be encoded with a negative disparity. Because tx forcedisp is high at time n+2, and tx disparit is low, the K28.5

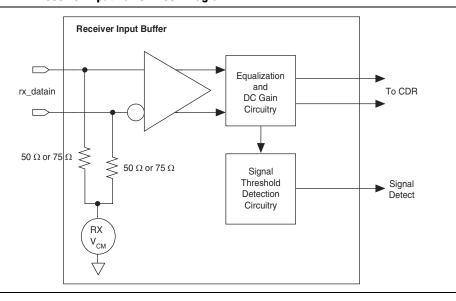

In a DC-coupled link, the transmitter DC common mode voltage is seen unblocked at the receiver input buffer as shown in Figure 1–13. The link common mode voltage depends on the transmitter common mode voltage and the receiver common mode voltage. When using the receiver OCT and on-chip biasing circuitry in a DC coupled link, you must ensure the transmitter common mode voltage is compatible with the receiver common mode requirements. If you disable the OCT, you must terminate and bias the receiver externally and ensure compatibility between the transmitter and the receiver common mode voltage.

Transmitter

Physical Medium

Receiver

Physical Medium

RX Termination

RX Termination

Figure 1–13. DC-Coupled Link with OCT

Figure 1–14 shows the receiver input buffer block diagram.

Figure 1-14. Receiver Input Buffer Block Diagram

The receiver input buffers support the following features:

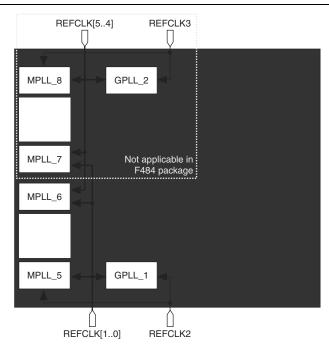

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK [1..0] and REFCLK [5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the Clock Networks and PLLs in Cyclone IV Devices chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

Table 1–6. REFCLK I/O Standard Support

|                             | HSSI     |                         | Terminatio | VCC_  | C_CLKIN Level |            | I/O Pin Type |                    |  |  |

|-----------------------------|----------|-------------------------|------------|-------|---------------|------------|--------------|--------------------|--|--|

| I/O Standard                | Protocol | Coupling                | n          | Input | Output        | Column I/O | Row I/O      | Supported<br>Banks |  |  |

| LVDS                        | ALL      | Differential            | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

| LVPECL                      | ALL      | AC (Needs               | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

| 404454                      | ALL      | off-chip<br>resistor to | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL      | restore                 | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

| 0.0 1 1 02                  | ALL      | V <sub>CM</sub> )       | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

| HCSL                        | PCle     | Differential<br>DC      | Off-chip   | 2.5 V | Not Supported | Yes        | No           | 3A, 3B, 8A, 8B     |  |  |

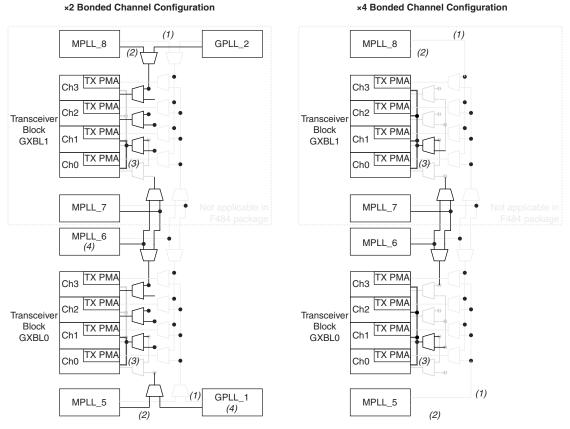

Figure 1–37. Clock Distribution in Bonded (×2 and ×4) Channel Configuration for Transceivers in F484 and Larger Packages

### Notes to Figure 1-37:

- (1) High-speed clock.

- (2) Low-speed clock.

- (3) Bonded common low-speed clock path.

- (4) These PLLs have restricted clock driving capability and may not reach all connected channels. For details, refer to Table 1-10.

The channel datapath clocking is similar between bonded channels in ×2 and ×4 configurations.

Figure 1–38 shows the datapath clocking in Transmitter Only operation for ×2 and ×4 bonded configurations. In these configurations, each bonded channel selects the high-speed clock from one the supported PLLs. The high-speed clock in each bonded channel feeds the respective serializer for parallel to serial operation. The common bonded low-speed clock feeds to each bonded channel that is used for the following blocks in each transmitter PCS channel:

- 8B/10B encoder

- read clock of byte serializer

- read clock of TX phase compensation FIFO

/2 8B/10B Encode **4**(₹ Tx Phase Comp FIFO 8B/10B Encode /2 low-speed clock **◆** Tx Phase Comp FIFO

Figure 1-39. Transmitter and Receiver Datapath Clocking with Rate Match FIFO in Bonded Channel Configuration

### Notes to Figure 1–39:

- (1) Low-speed recovered clock.

- (2) High-speed recovered clock.

Figure 1–57 shows an example of even numbers of /Dx.y/ between the last automatically sent /K28.5/ and the first user-sent /K28.5/. The first user-sent /K28.5/ code group received at an odd code group boundary in cycle n+3 takes the receiver synchronization state machine in Loss-of-Sync state. The first synchronization ordered-set /K28.5/Dx.y/ in cycles n+3 and n+4 is discounted and three additional ordered sets are required for successful synchronization.

Figure 1-57. Example of Reset Condition in GIGE Mode

# **Running Disparity Preservation with Idle Ordered Set**

During idle ordered sets transmission in GIGE mode, the transmitter ensures a negative running disparity at the end of an idle ordered set. Any /Dx.y/, except for /D21.5/ (part of /C1/ ordered set) or /D2.2/ (part of /C2/ ordered set) following a /K28.5/ is automatically replaced with either of the following:

- A /D5.6/ (/I1/ ordered set) if the running disparity before /K28.5/ is positive

- A /D16.2/ (/I2/ ordered set) if the running disparity before /K28.5/ is negative

# **Lane Synchronization**

In GIGE mode, the word aligner is configured in automatic synchronization state machine mode that complies with the IEEE P802.3ae standard. A synchronization ordered set is a /K28.5/ code group followed by an odd number of valid /Dx.y/ code groups. Table 1–19 lists the synchronization state machine parameters that implements the GbE-compliant synchronization.

Table 1–19. Synchronization State Machine Parameters (1)

| Parameter                                                                        | Value |

|----------------------------------------------------------------------------------|-------|

| Number of valid synchronization ordered sets received to achieve synchronization | 3     |

| Number of erroneous code groups received to lose synchronization                 | 4     |

| Number of continuous good code groups received to reduce the error count by one  | 4     |

#### Note to Table 1-19:

(1) The word aligner supports 7-bit and 10-bit pattern lengths in GIGE mode.

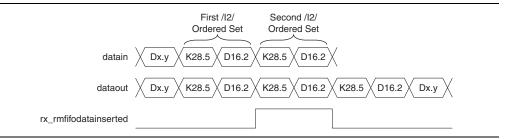

Figure 1–59 shows an example of rate match FIFO insertion in the case where one symbol must be inserted. Because the rate match FIFO can only insert /I2/ ordered sets, it inserts one /I2/ ordered set (two symbols inserted).

Figure 1-59. Example of Rate Match FIFO Insertion in GIGE Mode

The rate match FIFO does not insert or delete code groups automatically to overcome FIFO empty or full conditions. In this case, the rate match FIFO asserts the rx\_rmfifofull and rx\_rmfifoempty flags for at least two recovered clock cycles to indicate rate match FIFO full and empty conditions, respectively. You must then assert the rx\_digitalreset signal to reset the receiver PCS blocks.

# **Serial RapidIO Mode**

Serial RapidIO mode provides the non-bonded (×1) transceiver channel datapath configuration for SRIO protocol implementation. The Cyclone IV GX transceiver provides the PMA and the following PCS functions:

- 8B/10B encoding and decoding

- lane synchronization state machine

Cyclone IV GX transceivers do not have built-in support for some PCS functions such as pseudo-random idle sequence generation and lane alignment in ×4 bonded channel configuration. If required, you must implement these functions in a user logics or external circuits.

The RapidIO Trade Association defines a high-performance, packet-switched interconnect standard to pass data and control information between microprocessors, digital signals, communications, network processes, system memories, and peripheral devices. The SRIO physical layer specification defines serial protocol running at 1.25 Gbps, 2.5 Gbps, and 3.125 Gbps in either single-lane (×1) or bonded four-lane (×4) at each line rate. Cyclone IV GX transceivers support single-lane (×1) configuration at all three line rates. Four ×1 channels configured in Serial RapidIO mode can be instantiated to achieve one non-bonded ×4 SRIO link. When implementing four ×1 SRIO channels, the receivers do not have lane alignment or deskew capability.

### **Transmitter Only Channel**

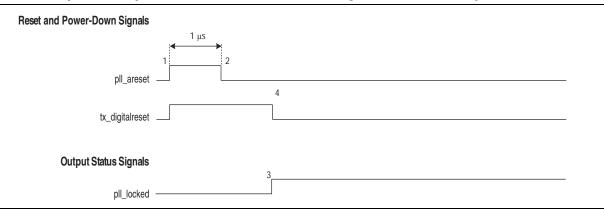

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager in Basic ×4 functional mode, use the reset sequence shown in Figure 2–3.

Figure 2-3. Sample Reset Sequence for Bonded and Non-Bonded Configuration Transmitter Only Channels

As shown in Figure 2–3, perform the following reset procedure for the **Transmitter Only** channel configuration:

- 1. After power up, assert pll\_areset for a minimum period of 1  $\mu$ s (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset signal asserted during this time period. After you de-assert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. When the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert the tx\_digitalreset signal (marker 4). At this point, the transmitter is ready for transmitting data.

#### Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

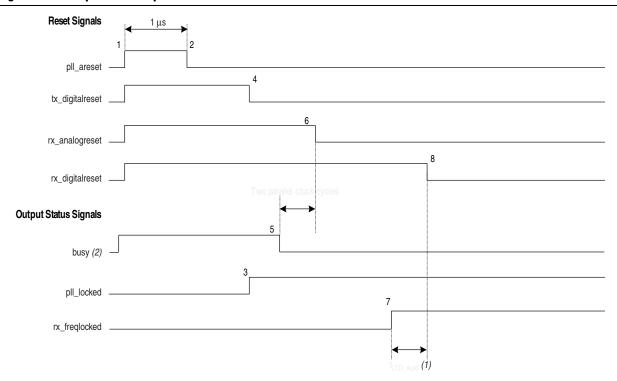

This configuration contains both a transmitter and a receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–8.

Figure 2–8. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 2-8:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–8, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, assert pl1\_areset for a minimum period of 1  $\mu$ s (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you deassert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. After the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), deassert tx\_digitalreset. For receiver operation, after deassertion of busy signal, wait for two parallel clock cycles to deassert the rx analogreset signal.

- 4. Wait for the rx freqlocked signal to go high (marker 7).

- 5. After the  $rx\_freqlocked$  signal goes high, wait for at least  $t_{LTD\_Auto}$ , then deassert the  $rx\_digitalreset$  signal (marker 8). At this point, the transmitter and receiver are ready for data traffic.

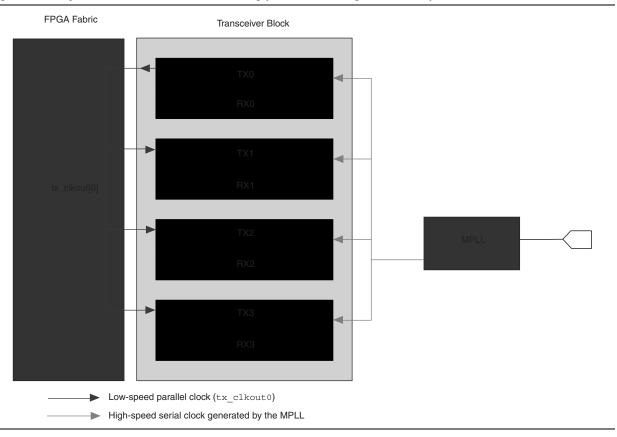

### **Option 1: Share a Single Transmitter Core Clock Between Transmitters**

- Enable this option if you want tx\_clkout of the first channel (channel 0) of the transceiver block to provide the write clock to the Transmitter Phase Compensation FIFOs of the remaining channels in the transceiver block.

- This option is typically enabled when all the channels of a transceiver block have the same functional mode and data rate and are reconfigured to the identical functional mode and data rate.

Figure 3–11 shows the sharing of channel 0's tx\_clkout between all four regular channels of a transceiver block.

Figure 3-11. Option 1 for Transmitter Core Clocking (Channel Reconfiguration Mode)

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

| Programming Mode         | DCLK Range | Typical DCLK | Unit |

|--------------------------|------------|--------------|------|

| Active Parallel (AP) (1) | 20 to 40   | 33           | MHz  |

| Active Serial (AS)       | 20 to 40   | 33           | MHz  |

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1–30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                         | Min | Max | Unit |

|-----------------------|---------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                  | 40  | _   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                               | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                      | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                      | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                               | 10  | _   | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output (2), (3)                | _   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output (2), (3) |     | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance (2), (3) | _   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                       | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                        | 10  | _   | ns   |

| t <sub>JSCO</sub>     | Update register clock to output                   |     | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output    | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance    | _   | 25  | ns   |

### Notes to Table 1-30:

- (1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

# **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

Table 1-46. Glossary (Part 4 of 5)

| ter | Term                                  | Definitions                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|     | t <sub>C</sub>                        | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                |  |  |  |  |  |  |

|     | Channel-to-<br>channel-skew<br>(TCCS) | High-speed I/O block: The timing difference between the fastest and slowest output edges, including $t_{\text{CO}}$ variation and clock skew. The clock is included in the TCCS measurement.                                                      |  |  |  |  |  |  |

|     | t <sub>cin</sub>                      | Delay from the clock pad to the I/O input register.                                                                                                                                                                                               |  |  |  |  |  |  |

|     | t <sub>CO</sub>                       | Delay from the clock pad to the I/O output.                                                                                                                                                                                                       |  |  |  |  |  |  |

|     | t <sub>cout</sub>                     | Delay from the clock pad to the I/O output register.                                                                                                                                                                                              |  |  |  |  |  |  |

|     | t <sub>DUTY</sub>                     | High-speed I/O block: Duty cycle on high-speed transmitter output clock.                                                                                                                                                                          |  |  |  |  |  |  |

|     | t <sub>FALL</sub>                     | Signal high-to-low transition time (80–20%).                                                                                                                                                                                                      |  |  |  |  |  |  |

|     | t <sub>H</sub>                        | Input register hold time.                                                                                                                                                                                                                         |  |  |  |  |  |  |

|     | Timing Unit<br>Interval (TUI)         | High-speed I/O block: The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(Receiver Input Clock Frequency Multiplication Factor) = t_C/w).$                                                               |  |  |  |  |  |  |

|     | t <sub>INJITTER</sub>                 | Period jitter on the PLL clock input.                                                                                                                                                                                                             |  |  |  |  |  |  |

|     | t <sub>OUTJITTER_DEDCLK</sub>         | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                      |  |  |  |  |  |  |

|     | t <sub>OUTJITTER_IO</sub>             | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                         |  |  |  |  |  |  |

|     | t <sub>pllcin</sub>                   | Delay from the PLL inclk pad to the I/O input register.                                                                                                                                                                                           |  |  |  |  |  |  |

| -   | t <sub>plicout</sub>                  | Delay from the PLL inclk pad to the I/O output register.                                                                                                                                                                                          |  |  |  |  |  |  |

|     | Transmitter<br>Output<br>Waveform     | Standards:  Single-Ended Waveform  Positive Channel (p) = V <sub>OH</sub> Negative Channel (n) = V <sub>OL</sub> Ground  Differential Waveform (Mathematical Function of Positive & Negative Channel)  V <sub>OD</sub> 0 V  V <sub>OD</sub> p - n |  |  |  |  |  |  |

|     | t <sub>RISE</sub>                     | Signal low-to-high transition time (20–80%).                                                                                                                                                                                                      |  |  |  |  |  |  |

|     | t <sub>SU</sub>                       | Input register setup time.                                                                                                                                                                                                                        |  |  |  |  |  |  |

| J   | -ou                                   |                                                                                                                                                                                                                                                   |  |  |  |  |  |  |