Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 7155                                                       |

| Number of Logic Elements/Cells | 114480                                                     |

| Total RAM Bits                 | 3981312                                                    |

| Number of I/O                  | 280                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.97V ~ 1.03V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 484-BGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f23c9ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

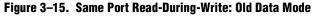

### **Same-Port Read-During-Write Mode**

This mode applies to a single-port RAM or the same port of a true dual-port RAM. In the same port read-during-write mode, there are two output choices: **New Data** mode (or flow-through) and **Old Data** mode. In **New Data** mode, new data is available on the rising edge of the same clock cycle on which it was written. In **Old Data** mode, the RAM outputs reflect the old data at that address before the write operation proceeds.

When using **New Data** mode together with byteena, you can control the output of the RAM. When byteena is high, the data written into the memory passes to the output (flow-through). When byteena is low, the masked-off data is not written into the memory and the old data in the memory appears on the outputs. Therefore, the output can be a combination of new and old data determined by byteena.

Figure 3–14 and Figure 3–15 show sample functional waveforms of same port read-during-write behavior with both **New Data** and **Old Data** modes, respectively.

clk\_a

wren\_a

rden\_a

address\_a

address\_a

A

B

C

D

E

F

q\_a (asynch)

A

B

C

D

E

F

Figure 3-14. Same Port Read-During Write: New Data Mode

### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

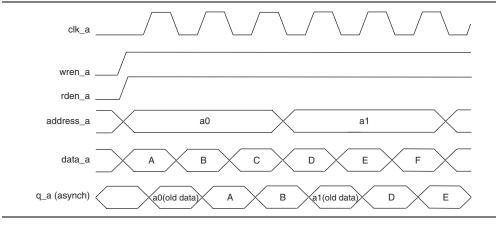

Figure 5–3. Clock Networks and Clock Control Block Locations in EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices (1), (2)

### Notes to Figure 5-3:

- (1) The clock networks and clock control block locations in this figure apply to only the EP4CGX30 device in F484 package and all EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices.

- (2) PLL 1, PLL 2, PLL 3, and PLL 4 are general purpose PLLs while PLL 5, PLL 6, PLL 7, and PLL 8 are multipurpose PLLs.

- (3) There are 6 clock control blocks on the top, right and bottom sides of the device and 12 clock control blocks on the left side of the device.

- (4) REFCLK[0,1]p/n and REFCLK[4,5]p/n can only drive the general purpose PLLs and multipurpose PLLs on the left side of the device. These clock pins do not have access to the clock control blocks and GCLK networks. The REFCLK[4,5]p/n pins are not available in devices in F484 nackage.

- (5) Not available for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

- Low time count = 1 cycle

- rselodd = 1 effectively equals:

- High time count = 1.5 cycles

- Low time count = 1.5 cycles

- Duty cycle = (1.5/3)% high time count and (1.5/3)% low time count

### **Scan Chain Description**

Cyclone IV PLLs have a 144-bit scan chain.

Table 5–7 lists the number of bits for each component of the PLL.

Table 5-7. Cyclone IV PLL Reprogramming Bits

| Die als Name               | Number of Bits |       |       |  |  |  |  |  |

|----------------------------|----------------|-------|-------|--|--|--|--|--|

| Block Name                 | Counter        | Other | Total |  |  |  |  |  |

| C4 <sup>(1)</sup>          | 16             | 2 (2) | 18    |  |  |  |  |  |

| C3                         | 16             | 2 (2) | 18    |  |  |  |  |  |

| C2                         | 16             | 2 (2) | 18    |  |  |  |  |  |

| C1                         | 16             | 2 (2) | 18    |  |  |  |  |  |

| CO                         | 16             | 2 (2) | 18    |  |  |  |  |  |

| M                          | 16             | 2 (2) | 18    |  |  |  |  |  |

| N                          | 16             | 2 (2) | 18    |  |  |  |  |  |

| Charge Pump                | 9              | 0     | 9     |  |  |  |  |  |

| Loop Filter <sup>(3)</sup> | 9              | 0     | 9     |  |  |  |  |  |

| Total number of bits:      |                | •     | 144   |  |  |  |  |  |

### Notes to Table 5-7:

- (1) LSB bit for C4 low-count value is the first bit shifted into the scan chain.

- (2) These two control bits include rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

- (3) MSB bit for loop filter is the last bit shifted into the scan chain.

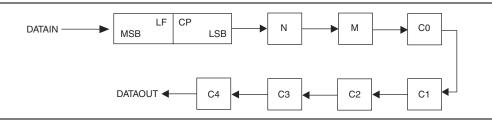

Figure 5–24 shows the scan chain order of the PLL components.

Figure 5-24. PLL Component Scan Chain Order

# **Section II. I/O Interfaces**

This section provides information about Cyclone $^{\otimes}$  IV device family I/O features and high-speed differential and external memory interfaces.

This section includes the following chapters:

- Chapter 6, I/O Features in Cyclone IV Devices

- Chapter 7, External Memory Interfaces in Cyclone IV Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

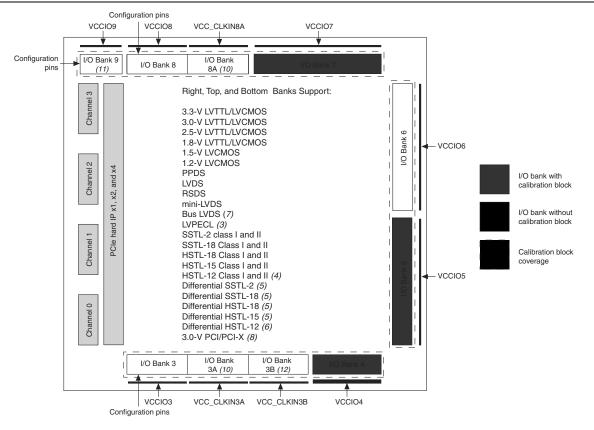

Figure 6–10 and Figure 6–11 show the overview of Cyclone IV GX I/O banks.

Figure 6-10. Cyclone IV GX I/O Banks for EP4CGX15, EP4CGX22, and EP4CGX30 (1), (2), (9)

### Notes to Figure 6-10:

- (1) This is a top view of the silicon die. For exact pin locations, refer to the pin list and the Quartus II software. Channels 2 and 3 are not available in EP4CGX15 and F169 package type in EP4CGX22 and EP4CGX30 devices.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 5 and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 4, 7, and 8.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses the LVDS input buffer.

- (8) The PCI-X I/O standard does not meet the IV curve requirement at the linear region.

- (9) The OCT block is located in the shaded banks 4, 5, and 7.

- (10) There are two dedicated clock input I/O banks (I/O bank 3A and I/O bank 8A) that can be used for either high-speed serial interface (HSSI) input reference clock pins or clock input pins.

- (11) There are dual-purpose I/O pins in bank 9. If input pins with VREF I/O standards are used on these dual-purpose I/O pins during user mode, they share the VREF pin in bank 8. These dual-purpose IO pins in bank 9 when used in user mode also support R<sub>S</sub> OCT without calibration and they share the OCT block with bank 8.

- (12) There are four dedicated clock input in I/O bank 3B for the EP4CGX30F484 device that can be used for either HSSI input reference clock pins or clock input pins.

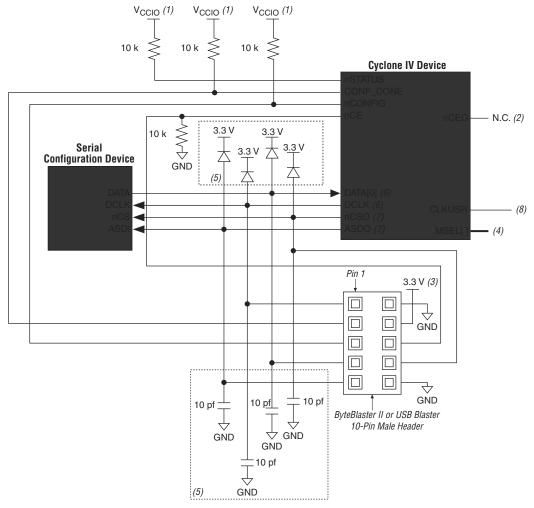

For more information about the USB-Blaster download cable, refer to the *USB-Blaster Download Cable User Guide*. For more information about the ByteBlaster II download cable, refer to the *ByteBlaster II Download Cable User Guide*.

Figure 8–6 shows the download cable connections to the serial configuration device.

Figure 8-6. In-System Programming of Serial Configuration Devices

#### Notes to Figure 8-6:

- (1) Connect these pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (3) Power up the V<sub>CC</sub> of the ByteBlaster II or USB-Blaster download cable with the 3.3-V supply.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The diodes and capacitors must be placed as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V. The external diodes and capacitors are required to prevent damage to the Cyclone IV device AS configuration input pins due to possible overshoot when programming the serial configuration device with a download cable. Altera recommends using the Schottky diode, which has a relatively lower forward diode voltage (VF) than the switching and Zener diodes, for effective voltage clamping.

- (6) When cascading Cyclone IV devices in a multi-device AS configuration, connect the repeater buffers between the master and slave devices for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (8) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

VCCIO (1) VCCIO (2)

VCCIO (3)

Refers (6)

Refers (6)

VCCIO (1)

Figure 8-9. Word-Wide Multi-Device AP Configuration

### Notes to Figure 8-9:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AP mode and the slave devices in FPP mode. To connect MSEL [3..0] for the master device in AP mode and the slave devices in FPP mode, refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O pin to monitor the WAIT signal from the Micron P30 or P33 flash.

- (6) Connect the repeater buffers between the Cyclone IV E master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

In a multi-device AP configuration, the board trace length between the parallel flash and the master device must follow the recommendations listed in Table 8–11.

DQ[15..8]

You can perform JTAG testing on Cyclone IV devices before, during, and after configuration. Cyclone IV devices support the BYPASS, IDCODE, and SAMPLE instructions during configuration without interrupting configuration. All other JTAG instructions can only be issued by first interrupting configuration and reprogramming I/O pins with the ACTIVE DISENGAGE and CONFIG IO instructions.

The CONFIG\_IO instruction allows you to configure the I/O buffers through the JTAG port and interrupts configuration when issued after the ACTIVE\_DISENGAGE instruction. This instruction allows you to perform board-level testing prior to configuring the Cyclone IV device or waiting for a configuration device to complete configuration. Prior to issuing the CONFIG\_IO instruction, you must issue the ACTIVE\_DISENGAGE instruction. This is because in Cyclone IV devices, the CONFIG\_IO instruction does not hold nSTATUS low until reconfiguration, so you must disengage the active configuration mode controller when active configuration is interrupted. The ACTIVE\_DISENGAGE instruction places the active configuration mode controllers in an idle state prior to JTAG programming. Additionally, the ACTIVE\_ENGAGE instruction allows you to re-engage a disengaged active configuration mode controller.

You must follow a specific flow when executing the ACTIVE\_DISENGAGE, CONFIG\_IO, and ACTIVE ENGAGE JTAG instructions in Cyclone IV devices.

The chip-wide reset (DEV\_CLRn) and chip-wide output enable (DEV\_OE) pins in Cyclone IV devices do not affect JTAG boundary-scan or programming operations. Toggling these pins do not affect JTAG operations (other than the usual boundary-scan operation).

When designing a board for JTAG configuration of Cyclone IV devices, consider the dedicated configuration pins. Table 8–15 describes how you must connect these pins during JTAG configuration.

Table 8-15. Dedicated Configuration Pin Connections During JTAG Configuration

| Signal    | Description                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nCE       | On all Cyclone IV devices in the chain, nce must be driven low by connecting it to GND, pulling it low through a resistor, or driving it by some control circuitry. For devices that are also in multi-device AS, AP, PS, or FPP configuration chains, you must connect the nce pins to GND during JTAG configuration or JTAG configured in the same order as the configuration chain. |

| nCEO      | On all Cyclone IV devices in the chain, nceo is left floating or connected to the nce of the next device.                                                                                                                                                                                                                                                                              |

| MSEL      | These pins must not be left floating. These pins support whichever non-JTAG configuration that you used in production. If you only use JTAG configuration, tie these pins to GND.                                                                                                                                                                                                      |

| nCONFIG   | Driven high by connecting to the $V_{\text{CCIO}}$ supply of the bank in which the pin resides and pulling up through a resistor or driven high by some control circuitry.                                                                                                                                                                                                             |

| nSTATUS   | Pull to the $V_{CCIO}$ supply of the bank in which the pin resides through a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each <code>nstatus</code> pin must be pulled up to the $V_{CCIO}$ individually.                                                                                                                                         |

| CONF_DONE | Pull to the $V_{CCIO}$ supply of the bank in which the pin resides through a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin must be pulled up to $V_{CCIO}$ supply of the bank in which the pin resides individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.                  |

| DCLK      | Must not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                              |

Use the ACTIVE\_DISENGAGE instruction with the CONFIG\_IO instruction to interrupt configuration. Table 8–16 lists the sequence of instructions to use for various CONFIG\_IO usage scenarios.

Table 8–16. JTAG CONFIG\_IO (without JTAG\_PROGRAM) Instruction Flows (1)

|                                                         | Configuration Scheme and Current State of the Cyclone IV Device |     |       |       |           |     |       |       |          |     |    |    |

|---------------------------------------------------------|-----------------------------------------------------------------|-----|-------|-------|-----------|-----|-------|-------|----------|-----|----|----|

| JTAG Instruction                                        | Prior to User Mode<br>(Interrupting Configuration)              |     |       |       | User Mode |     |       |       | Power Up |     |    |    |

|                                                         | PS                                                              | FPP | AS    | AP    | PS        | FPP | AS    | AP    | PS       | FPP | AS | AP |

| ACTIVE_DISENGAGE                                        | 0                                                               | 0   | 0     | 0     | 0         | 0   | 0     | 0     | _        | _   | _  | _  |

| CONFIG_IO                                               | R                                                               | R   | R     | R     | R         | R   | R     | R     | NA       | NA  | NA | NA |

| JTAG Boundary Scan<br>Instructions (no<br>JTAG_PROGRAM) | 0                                                               | 0   | 0     | 0     | 0         | 0   | 0     | 0     | _        | _   | _  | _  |

| ACTIVE_ENGAGE                                           |                                                                 |     | R (2) | R (2) |           |     | R (2) | R (2) | _        | _   | _  | _  |

| PULSE_NCONFIG                                           | Α                                                               | Α   | A (3) | A (3) | Α         | Α   | 0     | 0     | _        | _   | _  | _  |

| Pulse nCONFIG pin                                       |                                                                 |     | A (3) | A (3) |           |     | 0     | 0     | _        | _   | _  | _  |

| JTAG TAP Reset                                          | R                                                               | R   | R     | R     | R         | R   | R     | R     | _        | _   | _  | _  |

#### Notes to Table 8-16:

- (1) You must execute "R" indicates that the instruction before the next instruction, "O" indicates the optional instruction, "A" indicates that the instruction must be executed, and "NA" indicates that the instruction is not allowed in this mode.

- (2) Required if you use ACTIVE DISENGAGE.

- (3) Neither of the instruction is required if you use ACTIVE\_ENGAGE.

The CONFIG\_IO instruction does not hold nSTATUS low until reconfiguration. You must disengage the AS or AP configuration controller by issuing the ACTIVE\_DISENGAGE and ACTIVE\_ENGAGE instructions when active configuration is interrupted. You must issue the ACTIVE\_DISENGAGE instruction alone or prior to the CONFIG\_IO instruction if the JTAG\_PROGRAM instruction is to be issued later (Table 8–17). This puts the active configuration controllers into the idle state. The active configuration controller is reengaged after user mode is reached through JTAG programming (Table 8–17).

While executing the CONFIG IO instruction, all user I/Os are tri-stated.

If reconfiguration after interruption is performed using configuration modes (rather than using JTAG\_PROGRAM), it is not necessary to issue the ACTIVE\_DISENGAGE instruction prior to CONFIG\_IO. You can start reconfiguration by either pulling nCONFIG low for at least 500 ns or issuing the PULSE\_NCONFIG instruction. If the ACTIVE\_DISENGAGE instruction was issued and the JTAG\_PROGRAM instruction fails to enter user mode, you must issue the ACTIVE\_ENGAGE instruction to reactivate the active configuration controller. Issuing the ACTIVE\_ENGAGE instruction also triggers reconfiguration in configuration modes; therefore, it is not necessary to pull nCONFIG low or issue the PULSE\_NCONFIG instruction.

Figure 8–34 shows the control register bit positions. Table 8–23 defines the control register bit contents. The numbers in Figure 8–34 show the bit position of a setting in a register. For example, bit number 35 is the enable bit for the watchdog timer.

Figure 8-34. Remote System Upgrade Control Register

| 38   | 37       | 36      | 35    | 34   | 33         | 12    | 11           | 0  |

|------|----------|---------|-------|------|------------|-------|--------------|----|

| Rsv2 | Cd_early | Osc_int | Wd_en | Rsv1 | Ru_address | [210] | Wd_timer[110 | 0] |

Table 8-23. Remote System Upgrade Control Register Contents

| Control Register Bit | Value                                   | Definition                                                                                                                 |

|----------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Wd_timer[110]        | 12'b00000000000                         | User watchdog time-out value (most significant 12 bits of 29-bit count value: {Wd_timer[110],17'b1000})                    |

| Ru_address[210]      | 22'b00000000000000000000000000000000000 | Configuration address (most significant 22 bits of 24-bit boot address value: boot_address[23:0] = {Ru_address[210],2'b0}) |

| Rsv1                 | 1'b0                                    | Reserved bit                                                                                                               |

| Wd_en                | 1'b1                                    | User watchdog timer enable bit                                                                                             |

| Osc_int (1)          | 1'b1                                    | Internal oscillator as startup state machine clock enable bit                                                              |

| Cd_early (1)         | 1'b1                                    | Early CONF_DONE check                                                                                                      |

| Rsv2                 | 1'b1                                    | Reserved bit                                                                                                               |

### Note to Table 8-23:

(1) Option bit for the application configuration.

When enabled, the early CONF\_DONE check (Cd\_early) option bit ensures that there is a valid configuration at the boot address specified by the factory configuration and that it is of the proper size. If an invalid configuration is detected or the CONF\_DONE pin is asserted too early, the device resets and then reconfigures the factory configuration image. The internal oscillator (as the startup state machine clock [Osc\_int] option bit) ensures a functional startup clock to eliminate the hanging of startup. When all option bits are turned on, they provide complete coverage for the programming and startup portions of the application configuration. Altera recommends turning on both the Cd\_early and Osc\_int option bits.

The Cd\_early and Osc\_int option bits for the application configuration must be turned on by the factory configuration.

#### **Remote System Upgrade Status Register**

The remote system upgrade status register specifies the reconfiguration trigger condition. The various trigger and error conditions include:

- Cyclical redundancy check (CRC) error during application configuration

- nSTATUS assertion by an external device due to an error

- Cyclone IV device logic array triggers a reconfiguration cycle, possibly after downloading a new application configuration image

Table 8–25 lists the contents of previous state register 1 and previous state register 2 in the status register. The status register bit in Table 8–25 shows the bit positions in a 3-bit register. The previous state register 1 and previous state register 2 have the same bit definitions. The previous state register 1 reflects the current application configuration and the previous state register 2 reflects the previous application configuration.

Table 8–25. Remote System Upgrade Previous State Register 1 and Previous State Register 2 Contents in Status Register

| Status Register Bit | Definition                           | Description                                                                                                                                |  |  |  |  |

|---------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 30                  | nCONFIG Source                       | One-hot, active-high field that describes the reconfiguration source                                                                       |  |  |  |  |

| 29                  | CRC error source                     | that caused the Cyclone IV device to leave the previous application                                                                        |  |  |  |  |

| 28                  | nSTATUS Source                       | configuration. If there is a tie, the higher bit order indicates                                                                           |  |  |  |  |

| 27                  | User watchdog timer source           | precedence. For example, if nCONFIG and remote system upgrade nCONFIG reach the reconfiguration state machine at the same time,            |  |  |  |  |

| 26                  | Remote system upgrade nCONFIG source | the nconfig precedes the remote system upgrade nconfig.                                                                                    |  |  |  |  |

| 25:24               | Master state machine current state   | The state of the master state machine during reconfiguration causes the Cyclone IV device to leave the previous application configuration. |  |  |  |  |

| 23:0                | Boot address                         | The address used by the configuration scheme to load the previous application configuration.                                               |  |  |  |  |

If a capture is inappropriately done while capturing a previous state before the system has entered remote update application configuration for the first time, a value outputs from the shift register to indicate that the capture is incorrectly called.

### **Remote System Upgrade State Machine**

The remote system upgrade control and update registers have identical bit definitions, but serve different roles (Table 8–22 on page 8–75). While both registers can only be updated when the device is loaded with a factory configuration image, the update register writes are controlled by the user logic, and the control register writes are controlled by the remote system upgrade state machine.

In factory configurations, the user logic should send the option bits (Cd\_early and Osc\_int), the configuration address, and watchdog timer settings for the next application configuration bit to the update register. When the logic array configuration reset (RU\_nCONFIG) goes high, the remote system upgrade state machine updates the control register with the contents of the update register and starts system reconfiguration from the new application page.

To ensure the successful reconfiguration between the pages, assert the RU\_nCONFIG signal for a minimum of 250 ns. This is equivalent to strobing the reconfig input of the ALTREMOTE\_UPDATE megafunction high for a minimum of 250 ns.

If there is an error or reconfiguration trigger condition, the remote system upgrade state machine directs the system to load a factory or application configuration (based on mode and error condition) by setting the control register accordingly.

Table 8–26 lists the contents of the control register after such an event occurs for all possible error or trigger conditions.

The user watchdog timer is disabled in factory configurations and during the configuration cycle of the application configuration. It is enabled after the application configuration enters user mode.

### **Quartus II Software Support**

Implementation in your design requires a remote system upgrade interface between the Cyclone IV device logic array and remote system upgrade circuitry. You must also generate configuration files for production and remote programming of the system configuration memory. The Quartus II software provides these features.

The two implementation options, ALTREMOTE\_UPDATE megafunction and remote system upgrade atom, are for the interface between the remote system upgrade circuitry and the device logic array interface. Using the megafunction block instead of creating your own logic saves design time and offers more efficient logic synthesis and device implementation.

For more information about the ALTREMOTE\_UPDATE megafunction, refer to the Remote Update Circuitry (ALTREMOTE\_UPDATE) Megafunction User Guide.

# **Document Revision History**

Table 8–28 lists the revision history for this chapter.

Table 8-28. Document Revision History (Part 1 of 2)

| Date          | Version | Changes                                                                                                                                                             |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         | ■ Added Table 8–6.                                                                                                                                                  |

|               |         | ■ Updated Table 8–9 to add new device options and packages.                                                                                                         |

| May 2013      | 1.7     | ■ Updated Figure 8–16 and Figure 8–22 to include user mode.                                                                                                         |

|               |         | ■ Updated the "Dedicated" column for DATA[0] and DCLK in Table 8–19.                                                                                                |

|               |         | ■ Updated the "User Mode" and "Pin Type" columns for DCLK in Table 8–20.                                                                                            |

| February 2013 | 1.6     | Updated Table 8–9 to add new device options and packages.                                                                                                           |

|               |         | <ul> <li>Updated "AP Configuration Supported Flash Memories", "Configuration Data<br/>Decompression", and "Overriding the Internal Oscillator" sections.</li> </ul> |

| October 2012  | 1.5     | ■ Updated Figure 8–3, Figure 8–4, Figure 8–5, Figure 8–7, Figure 8–8, Figure 8–9, Figure 8–10, and Figure 8–11.                                                     |

|               |         | ■ Updated Table 8–2, Table 8–8, Table 8–12, Table 8–13, Table 8–18, and Table 8–19.                                                                                 |

|               |         | Added information about how to gain control of EPCS pins.                                                                                                           |

|               |         | Updated "Reset", "Single-Device AS Configuration", "Single-Device AP<br>Configuration", and "Overriding the Internal Oscillator" sections.                          |

| November 2011 | 1.4     | ■ Added Table 8–7.                                                                                                                                                  |

|               |         | ■ Updated Table 8–6 and Table 8–19.                                                                                                                                 |

|               |         | ■ Updated Figure 8–3, Figure 8–4, and Figure 8–5.                                                                                                                   |

|               |         | ■ Updated for the Quartus II software version 10.1 release.                                                                                                         |

| December 2010 | 1.3     | Added Cyclone IV E new device package information.                                                                                                                  |

| December 2010 | 1.0     | ■ Updated Table 8–7, Table 8–10, and Table 8–11.                                                                                                                    |

|               |         | ■ Minor text edits.                                                                                                                                                 |

WYSIWYG is an optimization technique that performs optimization on a VQM (Verilog Quartus Mapping) netlist in the Quartus II software.

### **Error Detection Block**

Table 9–3 lists the types of CRC detection to check the configuration bits.

Table 9-3. Types of CRC Detection to Check the Configuration Bits

| First Type of CRC Detection                                                | Second Type of CRC Detection                                                                                                                                     |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ CRAM error checking ability (32-bit CRC)                                 | ■ 16-bit CRC embedded in every configuration data frame.                                                                                                         |

| during user mode, for use by the CRC_ERROR pin.                            | ■ During configuration, after a frame of data is loaded into the device, the pre-computed CRC is shifted into the CRC circuitry.                                 |

| ■ There is only one 32-bit CRC value. This value covers all the CRAM data. | ■ Simultaneously, the CRC value for the data frame shifted-in is calculated. If the pre-computed CRC and calculated CRC values do not match, nSTATUS is set low. |

|                                                                            | Every data frame has a 16-bit CRC. Therefore, there are many 16-bit CRC values for the whole configuration bit stream.                                           |

|                                                                            | Every device has a different length of configuration data frame.                                                                                                 |

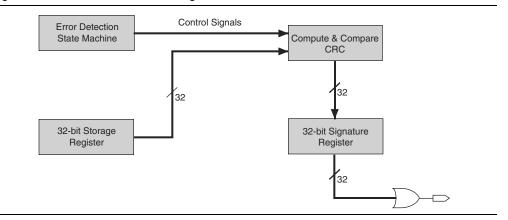

This section focuses on the first type—the 32-bit CRC when the device is in user mode.

## **Error Detection Registers**

There are two sets of 32-bit registers in the error detection circuitry that store the computed CRC signature and pre-calculated CRC value. A non-zero value on the signature register causes the CRC ERROR pin to set high.

Figure 9-1 shows the block diagram of the error detection block and the two related 32-bit registers: the signature register and the storage register.

Figure 9-1. Error Detection Block Diagram

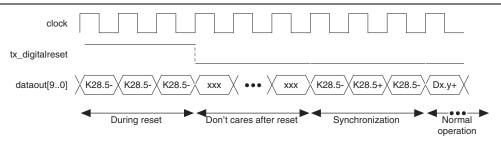

The following describes the 8B/10B encoder behavior in reset condition (as shown in Figure 1–7):

- During reset, the 8B/10B encoder ignores the inputs (tx\_datain and tx\_ctrlenable ports) from the FPGA fabric and outputs the K28.5 pattern from the RD- column continuously until the tx\_digitalreset port is deasserted.

- Upon deassertion of the tx\_digitalreset port, the 8B/10B encoder starts with a negative disparity and transmits three K28.5 code groups for synchronization before it starts encoding and transmitting data on its output.

- Due to some pipelining of the transmitter PCS, some "don't cares" (10'hxxx) are sent before the three synchronizing K28.5 code groups.

Figure 1-7. 8B/10B Encoder Behavior in Reset Condition

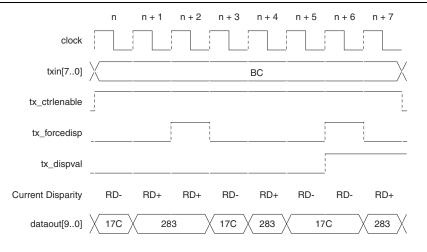

The encoder supports forcing the running disparity to either positive or negative disparity with tx\_forcedisp and tx\_dispval ports. Figure 1–8 shows an example of tx\_forcedisp and tx\_dispval port use, where data is shown in hexadecimal radix.

Figure 1–8. Force Running Disparity Operation

In this example, a series of K28.5 code groups are continuously sent. The stream alternates between a positive disparity K28.5 (RD+) and a negative disparity K28.5 (RD-) to maintain a neutral overall disparity. The current running disparity at time n+1 indicates that the K28.5 in time n+2 should be encoded with a negative disparity. Because tx forcedisp is high at time n+2, and tx disparit is low, the K28.5

# **Transceiver Clocking Architecture**

The multipurpose PLLs and general-purpose PLLs located on the left side of the device generate the clocks required for the transceiver operation. The following sections describe the Cyclone IV GX transceiver clocking architecture:

- "Input Reference Clocking" on page 1–27

- "Transceiver Channel Datapath Clocking" on page 1–29

- "FPGA Fabric-Transceiver Interface Clocking" on page 1–43

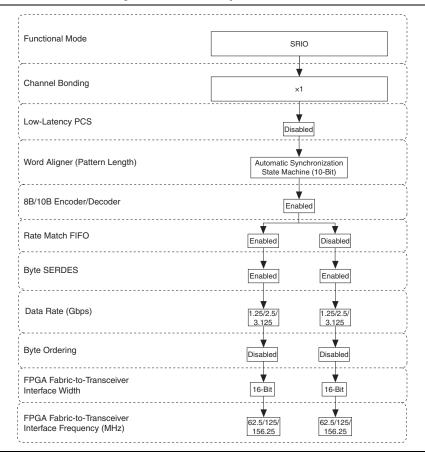

Figure 1–61 shows the transceiver configuration in Serial RapidIO mode.

Figure 1-61. Transceiver Configuration in Serial RapidIO Mode

### **Lane Synchronization**

In Serial RapidIO mode, the word aligner is compliant to the SRIO Specification 1.3 and is configured in automatic synchronization state machine mode with the parameter settings as listed in Table 1–20.

Table 1–20. Synchronization State Machine Parameters (1)

| Parameter                                                                                 | Value |

|-------------------------------------------------------------------------------------------|-------|

| Number of valid synchronization (/K28.5/) code groups received to achieve synchronization | 127   |

| Number of erroneous code groups received to lose synchronization                          | 3     |

| Number of continuous good code groups received to reduce the error count by one           | 255   |

### Note to Table 1-20:

(1) The word aligner supports 10-bit pattern lengths in SRIO mode.

### **Transmitter Only Channel**

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager, use the same reset sequence shown in Figure 2–3 on page 2–7.

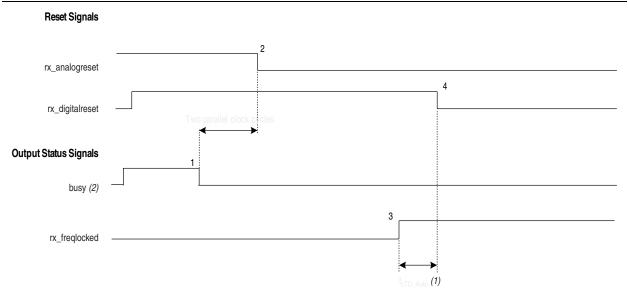

### Receiver Only Channel—Receiver CDR in Automatic Lock Mode

This configuration contains only a receiver channel. If you create a **Receiver Only** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–6.

Figure 2–6. Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 2-6:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–6, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, wait for the busy signal to be deasserted.

- 2. Keep the rx\_digitalreset and rx\_analogreset signals asserted during this time period.

- 3. After the busy signal is deasserted, wait for another two parallel clock cycles, then deassert the rx\_analogreset signal.

- 4. Wait for the rx freqlocked signal to go high.

- 5. When rx\_freqlocked goes high (marker 3), from that point onwards, wait for at least t<sub>LTD\_Auto</sub>, then de-assert the rx\_digitalreset signal (marker 4). At this point, the receiver is ready to receive data.

#### **PMA Control Ports Used in a Read Transaction**

- tx vodctrl out is 3 bits per channel

- tx\_preemp\_out is 5 bits per channel

- rx eqdcgain out is 2 bits per channel

- rx eqctrl out is 4 bits per channel

For example, assume the number of channels controlled by the dynamic reconfiguration controller is two, tx\_vodctrl\_out is 6 bits wide.

### **Write Transaction**

The value you set at the selected PMA control ports is written to all the transceiver channels connected to the ALTGX\_RECONFIG instance.

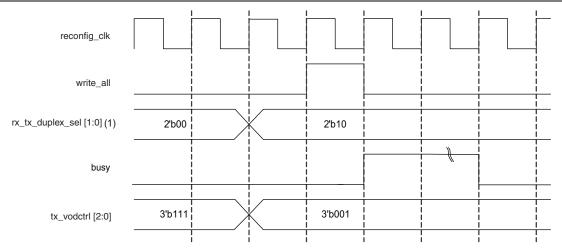

For example, assume you have enabled  $tx\_vodctrl$  in the ALTGX\_RECONFIG MegaWizard Plug-In Manager to reconfigure the  $V_{OD}$  of the transceiver channels. To complete a write transaction to reconfigure the  $V_{OD}$ , perform the following steps:

- 1. Before you initiate a write transaction, set the selected PMA control ports to the desired settings (for example, tx vodctrl = 3'b001).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are written to the transceiver channel.

- 3. Ensure that the busy signal is low before you start a write transaction.

- Assert the write\_all signal for one reconfig\_clk clock cycle. This initiates the write transaction.

- 5. The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy writing the PMA control values. When the write transaction has completed, the busy signal goes low.

Figure 3–6 shows the write transaction for Method 2.

Figure 3-6. Write Transaction Waveform—Use the same control signal for all the channels Option

#### Note to Figure 3-6:

(1) In this waveform example, you want to write to only the transmitter portion of the channel.

For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to *Section III: System Performance Specifications* of the *External Memory Interface Handbook*.

Table 1–37 lists the memory output clock jitter specifications for Cyclone IV devices.

Table 1–37. Memory Output Clock Jitter Specifications for Cyclone IV Devices (1), (2)

| Parameter                    | Symbol                 | Min  | Max | Unit |

|------------------------------|------------------------|------|-----|------|

| Clock period jitter          | t <sub>JIT(per)</sub>  | -125 | 125 | ps   |

| Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -200 | 200 | ps   |

| Duty cycle jitter            | t <sub>JIT(duty)</sub> | -150 | 150 | ps   |

#### Notes to Table 1-37:

- (1) Memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2 standard.

- (2) The clock jitter specification applies to memory output clock pins generated using DDIO circuits clocked by a PLL output routed on a global clock (GCLK) network.

### **Duty Cycle Distortion Specifications**

Table 1–38 lists the worst case duty cycle distortion for Cyclone IV devices.

Table 1–38. Duty Cycle Distortion on Cyclone IV Devices I/O Pins (1), (2), (3)

| Symbol            | C6  |     | C7, I7 |     | C8, I8L, A7 |     | C9L |     | Unit  |

|-------------------|-----|-----|--------|-----|-------------|-----|-----|-----|-------|

|                   | Min | Max | Min    | Max | Min         | Max | Min | Max | UIIIT |

| Output Duty Cycle | 45  | 55  | 45     | 55  | 45          | 55  | 45  | 55  | %     |

### Notes to Table 1-38:

- (1) The duty cycle distortion specification applies to clock outputs from the PLLs, global clock tree, and IOE driving the dedicated and general purpose I/O pins.

- (2) Cyclone IV devices meet the specified duty cycle distortion at the maximum output toggle rate for each combination of I/O standard and current strength.

- (3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

### **OCT Calibration Timing Specification**

Table 1–39 lists the duration of calibration for series OCT with calibration at device power-up for Cyclone IV devices.

Table 1–39. Timing Specification for Series OCT with Calibration at Device Power-Up for Cyclone IV Devices  $^{(1)}$

| Symbol              | Description                                                | Maximum | Units |

|---------------------|------------------------------------------------------------|---------|-------|

| t <sub>OCTCAL</sub> | Duration of series OCT with calibration at device power-up | 20      | μs    |

### Note to Table 1-39:

(1) OCT calibration takes place after device configuration and before entering user mode.