Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 7155                                                     |

| Number of Logic Elements/Cells | 114480                                                   |

| Total RAM Bits                 | 3981312                                                  |

| Number of I/O                  | 280                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f23i7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

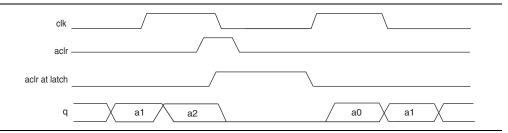

## **Asynchronous Clear**

Cyclone IV devices support asynchronous clears for read address registers, output registers, and output latches only. Input registers other than read address registers are not supported. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are immediately seen. If your RAM does not use output registers, you can still clear the RAM outputs using the output latch asynchronous clear feature.

Asserting asynchronous clear to the read address register during a read operation may corrupt the memory content.

Figure 3–5 shows the functional waveform for the asynchronous clear feature.

Figure 3-5. Output Latch Asynchronous Clear Waveform

You can selectively enable asynchronous clears per logical memory using the Quartus II RAM MegaWizard™ Plug-In Manager.

For more information, refer to the RAM Megafunction User Guide.

There are three ways to reset registers in the M9K blocks:

- Power up the device

- Use the aclr signal for output register only

- Assert the device-wide reset signal using the DEV\_CLRn option

## **Memory Modes**

Cyclone IV devices M9K memory blocks allow you to implement fully-synchronous SRAM memory in multiple modes of operation. Cyclone IV devices M9K memory blocks do not support asynchronous (unregistered) memory inputs.

M9K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port

- Shift-register

- **ROM**

- **FIFO**

### **Read or Write Clock Mode**

Cyclone IV devices M9K memory blocks can implement read or write clock mode for FIFO and simple dual-port memories. In this mode, a write clock controls the data inputs, write address, and wren registers. Similarly, a read clock controls the data outputs, read address, and rden registers. M9K memory blocks support independent clock enables for both the read and write clocks.

When using read or write mode, if you perform a simultaneous read or write to the same address location, the output read data is unknown. If you require the output data to be a known value, use either single-clock mode, input clock mode, or output clock mode and choose the appropriate read-during-write behavior in the MegaWizard Plug-In Manager.

## **Single-Clock Mode**

Cyclone IV devices M9K memory blocks can implement single-clock mode for FIFO, ROM, true dual-port, simple dual-port, and single-port memories. In this mode, you can control all registers of the M9K memory block with a single clock together with clock enable.

## **Design Considerations**

This section describes designing with M9K memory blocks.

## **Read-During-Write Operations**

"Same-Port Read-During-Write Mode" on page 3–16 and "Mixed-Port Read-During-Write Mode" on page 3–16 describe the functionality of the various RAM configurations when reading from an address during a write operation at that same address.

There are two read-during-write data flows: same-port and mixed-port. Figure 3–13 shows the difference between these flows.

Port A data in

Port B data in

Mixed-port data flow

---- Same-port data flow

Port B data out

Figure 3-13. Cyclone IV Devices Read-During-Write Data Flow

Chapter 5: Clock Networks and PLLs in Cyclone IV Devices

Clock Networks

Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices (1), (2) (Part 1 of 4)

| GCLK Network Clock              | GCLK Networks |          |   |   |   |   |   |          |          |   |    |          |    |          |    |    |          |    |    |          |          |    |          |          |          |          |          |    |    |          |

|---------------------------------|---------------|----------|---|---|---|---|---|----------|----------|---|----|----------|----|----------|----|----|----------|----|----|----------|----------|----|----------|----------|----------|----------|----------|----|----|----------|

| Sources                         | 0             | 1        | 2 | 3 | 4 | 5 | 6 | 7        | 8        | 9 | 10 | 11       | 12 | 13       | 14 | 15 | 16       | 17 | 18 | 19       | 20       | 21 | 22       | 23       | 24       | 25       | 26       | 27 | 28 | 29       |

| CLKIO4/DIFFCLK_2n               | —             | _        | _ | — | _ | — | _ | _        | _        | _ | _  | _        | ✓  | _        | ✓  | —  | <b>✓</b> | _  | —  | _        | _        | —  | _        | _        | —        | _        | _        | —  |    | <u> </u> |

| CLKIO5/DIFFCLK_2p               | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | ~        | ~  | _  | _        | ~  | _  | _        | _        | _  | _        | _        | _        | _        | _        | _  | _  | _        |

| CLKIO6/DIFFCLK_3n               | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | <b>✓</b> | _  | ~  | ~        | _  | _  | _        | _        | _  | _        | _        |          | _        | _        | _  | _  | _        |

| CLKIO7/DIFFCLK_3p               | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | ~  | _        | _  | ~  | _        | ~  | _  | _        | _        | _  | _        | _        |          | _        | _        | _  | _  | _        |

| CLKIO8/DIFFCLK_5n               | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | ~  | _        | ~        | _  | ~        | _        |          | _        | _        | _  | _  | _        |

| CLKIO9/DIFFCLK_5p               | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | <b>✓</b> | <b>✓</b> | _  | _        | ~        | _        | _        | _        | _  | _  | _        |

| CLKIO10/DIFFCLK_4n/RE<br>FCLK3n | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | ~        | _        | ~  | ~        |          | _        | _        | _        | _  | _  | _        |

| CLKIO11/DIFFCLK_4p/RE<br>FCLK3p | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | ~  | _        | _        | ~  | _        | ~        | _        | _        | _        | _  | _  | _        |

| CLKIO12/DIFFCLK_7p/RE<br>FCLK2p | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | _        | _        | _  | _        | _        | <b>✓</b> | _        | ~        | _  | ~  | _        |

| CLKIO13/DIFFCLK_7n/RE<br>FCLK2n | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | _        | _        | _  | _        | _        | _        | <b>✓</b> | <b>✓</b> | _  | _  | ~        |

| CLKIO14/DIFFCLK_6p              | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | _        | _        | _  | _        | _        | _        | ~        | _        | ~  | ~  | _        |

| CLKIO15/DIFFCLK_6n              | _             | _        | _ | _ | _ | _ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | _        | _        | _  | _        | _        | ✓        | _        | _        | ~  | _  | ~        |

| PLL_1_C0                        | ~             | _        | _ | ~ | _ | ~ | _ | _        | _        | _ | _  | _        | _  | _        |    | _  | _        |    | _  | _        |          | _  | _        | _        | ~        |          | _        | ~  | _  | ~        |

| PLL_1_C1                        | —             | <b>✓</b> | — | — | ~ | — |   | —        | _        |   | —  | —        | —  | _        |    | _  | _        |    | _  | _        |          | _  | _        | —        | —        | ~        |          | —  | ~  | _        |

| PLL_1_C2                        | <b>✓</b>      | —        | ~ | — |   | — |   | —        | _        |   | —  | —        | —  | _        |    | _  | _        |    | _  | _        |          | _  | _        | —        | <b>✓</b> |          | ~        | —  | _  | _        |

| PLL_1_C3                        |               | <b>✓</b> | _ | ~ | _ | _ |   |          | _        |   |    | _        | _  | _        |    | _  | _        |    | _  | _        |          | _  | _        |          |          | ~        | _        | ~  | _  | _        |

| PLL_1_C4                        | _             | —        | ~ | _ | ~ | ~ | _ | _        | _        | _ | _  | _        | _  | _        | _  | _  | _        | _  | _  | _        | _        | _  | _        | _        | —        | _        | ~        | _  | ~  | ~        |

| PLL_2_C0                        |               |          | _ |   | _ | _ | ~ |          | _        | ~ |    | ~        | _  | _        |    | _  | _        |    | ~  | _        |          | ~  | _        | ~        |          |          | _        |    | _  | _        |

| PLL_2_C1                        |               |          | _ |   | _ | _ |   | <b>✓</b> |          |   | ~  | _        | _  |          |    |    | _        |    |    | ~        |          |    | ~        | _        |          |          |          |    |    |          |

| PLL_2_C2                        |               |          | _ |   | _ | _ | ~ | _        | ~        |   |    | _        | _  | _        |    | _  |          |    | ~  |          | ~        | _  |          | _        |          |          | _        |    | _  |          |

| PLL_2_C3                        |               | —        | _ |   | _ | _ |   | <b>✓</b> | _        | ✓ |    | _        | _  |          |    | _  | _        |    | _  | ✓        |          | ~  | _        | _        |          |          | _        |    | _  | _        |

| PLL_2_C4                        | _             |          | _ | _ | _ | _ | _ | _        | <b>✓</b> | _ | ✓  | <b>✓</b> | _  | _        | _  | _  | _        | _  | _  | _        | <b>✓</b> | _  | <b>✓</b> | <b>✓</b> |          | _        | _        | _  | _  | _        |

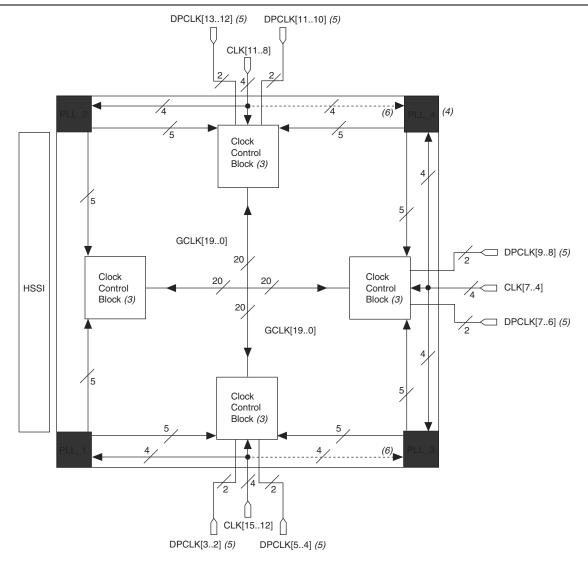

## **GCLK Network Clock Source Generation**

Figure 5–2, Figure 5–3, and Figure 5–4 on page 5–14 show the Cyclone IV PLLs, clock inputs, and clock control block location for different Cyclone IV device densities.

Figure 5-2. Clock Networks and Clock Control Block Locations in EP4CGX15, EP4CGX22, and EP4CGX30 Devices (1), (2)

#### Notes to Figure 5-2:

- (1) The clock networks and clock control block locations apply to all EP4CGX15, EP4CGX22, and EP4CGX30 devices except EP4CGX30 device in F484 package.

- (2) PLL 1 and PLL 2 are multipurpose PLLs while PLL 3 and PLL 4 are general purpose PLLs.

- (3) There are five clock control blocks on each side.

- (4) PLL 4 is only available in EP4CGX22 and EP4CGX30 devices in F324 package.

- (5) The EP4CGX15 device has two DPCLK pins on three sides of the device: DPCLK2 and DPCLK5 on bottom side, DPCLK7 and DPCLK8 on the right side, DPCLK10 and DPCLK13 on the top side of device.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

# **Document Revision History**

Table 5–14 lists the revision history for this chapter.

Table 5-14. Document Revision History

| Date          | Version | Changes                                                                                                         |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------|

| October 2012  | 2.4     | ■ Updated "Manual Override" and "PLL Cascading" sections.                                                       |

| October 2012  | 2.4     | ■ Updated Figure 5–9.                                                                                           |

| November 2011 | 2.3     | ■ Updated the "Dynamic Phase Shifting" section.                                                                 |

| November 2011 | 2.3     | ■ Updated Figure 5–26.                                                                                          |

|               |         | ■ Updated for the Quartus II software version 10.1 release.                                                     |

| December 2010 |         | ■ Updated Figure 5–3 and Figure 5–10.                                                                           |

|               | 2.2     | ■ Updated "GCLK Network Clock Source Generation", "PLLs in Cyclone IV Devices", and "Manual Override" sections. |

|               |         | Minor text edits.                                                                                               |

|               |         | ■ Updated Figure 5–2, Figure 5–3, Figure 5–4, and Figure 5–10.                                                  |

| July 2010     | 2.1     | ■ Updated Table 5–1, Table 5–2, and Table 5–5.                                                                  |

|               |         | Updated "Clock Feedback Modes" section.                                                                         |

|               |         | ■ Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1 release.                   |

|               |         | Updated "Clock Networks" section.                                                                               |

| February 2010 | 2.0     | ■ Updated Table 5–1 and Table 5–2.                                                                              |

|               |         | ■ Added Table 5–3.                                                                                              |

|               |         | ■ Updated Figure 5–2, Figure 5–3, and Figure 5–9.                                                               |

|               |         | ■ Added Figure 5–4 and Figure 5–10.                                                                             |

| November 2009 | 1.0     | Initial release.                                                                                                |

## **Section II. I/O Interfaces**

This section provides information about Cyclone $^{\otimes}$  IV device family I/O features and high-speed differential and external memory interfaces.

This section includes the following chapters:

- Chapter 6, I/O Features in Cyclone IV Devices

- Chapter 7, External Memory Interfaces in Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

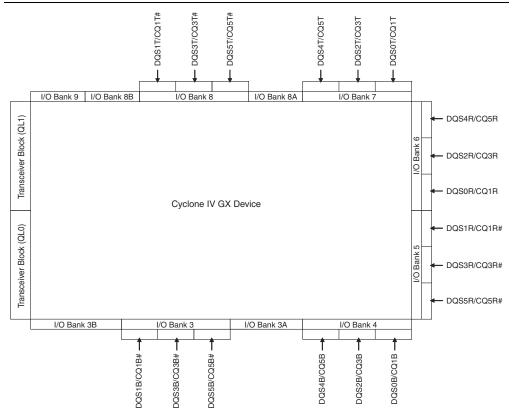

Figure 7–2 shows the location and numbering of the DQS, DQ, or CQ# pins in the Cyclone IV GX I/O banks.

Figure 7–2. DQS, CQ, or CQ# Pins in Cyclone IV GX I/O Banks (1)

### Note to Figure 7–2:

(1) The DQS, CQ, or CQ# pin locations in this diagram apply to all packages in Cyclone IV GX devices except devices in 169-pin FBGA and 324-pin FBGA.

During device configuration, Cyclone IV E devices read configuration data using the parallel interface and configure their SRAM cells. This scheme is referred to as the AP configuration scheme because the device controls the configuration interface. This scheme contrasts with the FPP configuration scheme, where an external host controls the interface.

### **AP Configuration Supported Flash Memories**

The AP configuration controller in Cyclone IV E devices is designed to interface with two industry-standard flash families—the Micron P30 Parallel NOR flash family and the Micron P33 Parallel NOR flash family. Unlike serial configuration devices, both of the flash families supported in AP configuration scheme are designed to interface with microprocessors. By configuring from an industry standard microprocessor flash which allows access to the flash after entering user mode, the AP configuration scheme allows you to combine configuration data and user data (microprocessor boot code) on the same flash memory.

The Micron P30 flash family and the P33 flash family support a continuous synchronous burst read mode at 40 MHz DCLK frequency for reading data from the flash. Additionally, the Micron P30 and P33 flash families have identical pin-out and adopt similar protocols for data access.

Cyclone IV E devices use a 40-MHz oscillator for the AP configuration scheme. The oscillator is the same oscillator used in the Cyclone IV E AS configuration scheme.

Table 8–10 lists the supported families of the commodity parallel flash for the AP configuration scheme.

Table 8–10. Supported Commodity Flash for AP Configuration Scheme for Cyclone IV E Devices  $^{(1)}$

| Flash Memory Density | Micron P30 Flash Family (2) | Micron P33 Flash Family <sup>(3)</sup> |  |  |

|----------------------|-----------------------------|----------------------------------------|--|--|

| 64 Mbit              | ✓                           | ✓                                      |  |  |

| 128 Mbit             | ✓                           | ✓                                      |  |  |

| 256 Mbit             | ✓                           | ✓                                      |  |  |

#### Notes to Table 8-10:

- (1) The AP configuration scheme only supports flash memory speed grades of 40 MHz and above.

- (2) 3.3-, 3.0-, 2.5-, and 1.8-V I/O options are supported for the Micron P30 flash family.

- (3) 3.3-, 3.0- and 2.5-V I/O options are supported for the Micron P33 flash family.

Configuring Cyclone IV E devices from the Micron P30 and P33 family 512-Mbit flash memory is possible, but you must properly drive the extra address and FLASH\_nCE pins as required by these flash memories.

To check for supported speed grades and package options, refer to the respective flash datasheets.

The AP configuration scheme in Cyclone IV E devices supports flash speed grades of 40 MHz and above. However, AP configuration for all these speed grades must be capped at 40 MHz. The advantage of faster speed grades is realized when your design in the Cyclone IV E devices accesses flash memory in user mode.

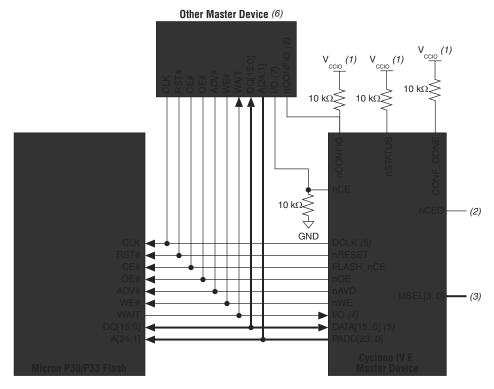

Figure 8–10 shows the AP configuration with multiple bus masters.

Figure 8-10. AP Configuration with Multiple Bus Masters

### Notes to Figure 8-10:

- (1) Connect the pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (5) When cascading Cyclone IV E devices in a multi-device AP configuration, connect the repeater buffers between the master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The other master device must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8-5.

- (7) The other master device can control the AP configuration bus by driving the nCE to high with an output high on the I/O pin.

- (8) The other master device can pulse nCONFIG if it is under system control and not tied to  $V_{CCIO}$ .

Use the ACTIVE\_DISENGAGE instruction with the CONFIG\_IO instruction to interrupt configuration. Table 8–16 lists the sequence of instructions to use for various CONFIG\_IO usage scenarios.

Table 8–16. JTAG CONFIG\_IO (without JTAG\_PROGRAM) Instruction Flows (1)

|                                                         | Configuration Scheme and Current State of the Cyclone IV Device |           |       |       |    |          |       |       |    |     |    |    |

|---------------------------------------------------------|-----------------------------------------------------------------|-----------|-------|-------|----|----------|-------|-------|----|-----|----|----|

| JTAG Instruction                                        | (Inte                                                           | User Mode |       |       |    | Power Up |       |       |    |     |    |    |

|                                                         | PS                                                              | FPP       | AS    | AP    | PS | FPP      | AS    | AP    | PS | FPP | AS | AP |

| ACTIVE_DISENGAGE                                        | 0                                                               | 0         | 0     | 0     | 0  | 0        | 0     | 0     | _  | _   | _  | _  |

| CONFIG_IO                                               | R                                                               | R         | R     | R     | R  | R        | R     | R     | NA | NA  | NA | NA |

| JTAG Boundary Scan<br>Instructions (no<br>JTAG_PROGRAM) | 0                                                               | 0         | 0     | 0     | 0  | 0        | 0     | 0     | _  | _   | _  | _  |

| ACTIVE_ENGAGE                                           |                                                                 |           | R (2) | R (2) |    |          | R (2) | R (2) | _  | _   | _  | _  |

| PULSE_NCONFIG                                           | Α                                                               | Α         | A (3) | A (3) | Α  | Α        | 0     | 0     | _  | _   | _  | _  |

| Pulse nCONFIG pin                                       |                                                                 |           | A (3) | A (3) |    |          | 0     | 0     | _  | _   | _  | _  |

| JTAG TAP Reset                                          | R                                                               | R         | R     | R     | R  | R        | R     | R     | _  | _   | _  | _  |

#### Notes to Table 8-16:

- (1) You must execute "R" indicates that the instruction before the next instruction, "O" indicates the optional instruction, "A" indicates that the instruction must be executed, and "NA" indicates that the instruction is not allowed in this mode.

- (2) Required if you use ACTIVE DISENGAGE.

- (3) Neither of the instruction is required if you use ACTIVE\_ENGAGE.

The CONFIG\_IO instruction does not hold nSTATUS low until reconfiguration. You must disengage the AS or AP configuration controller by issuing the ACTIVE\_DISENGAGE and ACTIVE\_ENGAGE instructions when active configuration is interrupted. You must issue the ACTIVE\_DISENGAGE instruction alone or prior to the CONFIG\_IO instruction if the JTAG\_PROGRAM instruction is to be issued later (Table 8–17). This puts the active configuration controllers into the idle state. The active configuration controller is reengaged after user mode is reached through JTAG programming (Table 8–17).

While executing the CONFIG IO instruction, all user I/Os are tri-stated.

If reconfiguration after interruption is performed using configuration modes (rather than using JTAG\_PROGRAM), it is not necessary to issue the ACTIVE\_DISENGAGE instruction prior to CONFIG\_IO. You can start reconfiguration by either pulling nCONFIG low for at least 500 ns or issuing the PULSE\_NCONFIG instruction. If the ACTIVE\_DISENGAGE instruction was issued and the JTAG\_PROGRAM instruction fails to enter user mode, you must issue the ACTIVE\_ENGAGE instruction to reactivate the active configuration controller. Issuing the ACTIVE\_ENGAGE instruction also triggers reconfiguration in configuration modes; therefore, it is not necessary to pull nCONFIG low or issue the PULSE\_NCONFIG instruction.

Table 8–19. Configuration Pin Summary for Cyclone IV E Devices (Part 3 of 3)

| Bank | Description | Input/Output | Dedicated | Powered By        | Configuration Mode |

|------|-------------|--------------|-----------|-------------------|--------------------|

| 5    | DEV_CLRn    | Input        | 1         | V <sub>CCIO</sub> | Optional, AP       |

#### Notes to Table 8-19:

- (1) To tri-state AS configuration pins in the AS configuration scheme, turn-on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

- (2) To tri-state AP configuration pins in the AP configuration scheme, turn-on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, Data[0..15], FLASH\_nCE, and other AP pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

- (3) The CRC\_ERROR pin is not available in Cyclone IV E devices with 1.0-V core voltage.

- (4) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

Table 8–20 describes the dedicated configuration pins. You must properly connect these pins on your board for successful configuration. You may not need some of these pins for your configuration schemes.

Table 8-20. Dedicated Configuration Pins on the Cyclone IV Device (Part 1 of 4)

| Pin Name | User Mode | Configuration<br>Scheme | Pin Type                 | Description                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|-------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSEL     | N/A       | All                     | Input                    | Configuration input that sets the Cyclone IV device configuration scheme. You must hardwire these pins to $V_{CCA}$ or GND. The MSEL pins have internal 9-k $\Omega$ pull-down resistors that are always active.                                                                                                                                                                         |

| nCONFIG  | N/A       | All                     | Input                    | Configuration control input. Pulling this pin low with external circuitry during user mode causes the Cyclone IV device to lose its configuration data, enter a reset state, and tri-state all I/O pins. Returning this pin to a logic-high level starts a reconfiguration.                                                                                                              |

|          |           | All                     |                          | The Cyclone IV device drives nstatus low immediately after power-up and releases it after the POR time.  Status output—if an error occurs during configuration, nstatus is pulled low by the target device.                                                                                                                                                                              |

| nSTATUS  | N/A       |                         | Bidirectional open-drain | ■ Status input—if an external source (for example, another Cyclone IV device) drives the nstatus pin low during configuration or initialization, the target device enters an error state.                                                                                                                                                                                                |

| IISTATOS |           |                         | ·                        | Driving nSTATUS low after configuration and initialization does not affect the configured device. If you use a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the device, but because the device ignores transitions on nSTATUS in user mode, the device does not reconfigure. To start a reconfiguration, you must pull nCONFIG low. |

Table 8–25 lists the contents of previous state register 1 and previous state register 2 in the status register. The status register bit in Table 8–25 shows the bit positions in a 3-bit register. The previous state register 1 and previous state register 2 have the same bit definitions. The previous state register 1 reflects the current application configuration and the previous state register 2 reflects the previous application configuration.

Table 8–25. Remote System Upgrade Previous State Register 1 and Previous State Register 2 Contents in Status Register

| Status Register Bit | Definition                           | Description                                                                                                                                |  |  |  |  |  |

|---------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 30                  | nCONFIG Source                       | One-hot, active-high field that describes the reconfiguration source that caused the Cyclone IV device to leave the previous application   |  |  |  |  |  |

| 29                  | CRC error source                     |                                                                                                                                            |  |  |  |  |  |

| 28                  | nSTATUS Source                       | configuration. If there is a tie, the higher bit order indicates                                                                           |  |  |  |  |  |

| 27                  | User watchdog timer source           | precedence. For example, if nCONFIG and remote system upgrade nCONFIG reach the reconfiguration state machine at the same time             |  |  |  |  |  |

| 26                  | Remote system upgrade nCONFIG source | the nconfig precedes the remote system upgrade nconfig.                                                                                    |  |  |  |  |  |

| 25:24               | Master state machine current state   | The state of the master state machine during reconfiguration causes the Cyclone IV device to leave the previous application configuration. |  |  |  |  |  |

| 23:0                | Boot address                         | The address used by the configuration scheme to load the previous application configuration.                                               |  |  |  |  |  |

If a capture is inappropriately done while capturing a previous state before the system has entered remote update application configuration for the first time, a value outputs from the shift register to indicate that the capture is incorrectly called.

### **Remote System Upgrade State Machine**

The remote system upgrade control and update registers have identical bit definitions, but serve different roles (Table 8–22 on page 8–75). While both registers can only be updated when the device is loaded with a factory configuration image, the update register writes are controlled by the user logic, and the control register writes are controlled by the remote system upgrade state machine.

In factory configurations, the user logic should send the option bits (Cd\_early and Osc\_int), the configuration address, and watchdog timer settings for the next application configuration bit to the update register. When the logic array configuration reset (RU\_nCONFIG) goes high, the remote system upgrade state machine updates the control register with the contents of the update register and starts system reconfiguration from the new application page.

To ensure the successful reconfiguration between the pages, assert the RU\_nCONFIG signal for a minimum of 250 ns. This is equivalent to strobing the reconfig input of the ALTREMOTE\_UPDATE megafunction high for a minimum of 250 ns.

If there is an error or reconfiguration trigger condition, the remote system upgrade state machine directs the system to load a factory or application configuration (based on mode and error condition) by setting the control register accordingly.

Table 8–26 lists the contents of the control register after such an event occurs for all possible error or trigger conditions.

This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Cyclone® IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                    | Contact Method | Address                   |  |  |

|--------------------------------|----------------|---------------------------|--|--|

| Technical support              | Website        | www.altera.com/support    |  |  |

| Technical training             | Website        | www.altera.com/training   |  |  |

| 160mmoar training              | Email          | custrain@altera.com       |  |  |

| Product literature             | Website        | www.altera.com/literature |  |  |

| Nontechnical support (general) | Email          | nacomp@altera.com         |  |  |

| (software licensing)           | Email          | authorization@altera.com  |  |  |

### Note to Table:

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                    |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                             |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example,     \text{qdesigns}  \text{directory, D: drive, and chiptrip.gdf} file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                       |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <file name=""> and <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre></file>                                       |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                   |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                |

<sup>(1)</sup> You can also contact your local Altera sales office or sales representative.

| Table 1–14. | <b>Transceiver</b> | <b>Functional Mode</b> | s for Protocol Im | plementation | (Part 2 of 2) |

|-------------|--------------------|------------------------|-------------------|--------------|---------------|

|             |                    |                        |                   |              |               |

| Functional Mode          | Protocol                    | Key Feature                                                                               | Reference                                    |

|--------------------------|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|

| Deterministic<br>Latency | Proprietary, CPRI,<br>OBSAI | TX PLL phase frequency detector (PFD) feedback, registered mode FIFO, TX bit-slip control | "Deterministic Latency<br>Mode" on page 1–73 |

| SDI                      | SDI                         | High-speed SERDES, CDR                                                                    | "SDI Mode" on<br>page 1–76                   |

## **Basic Mode**

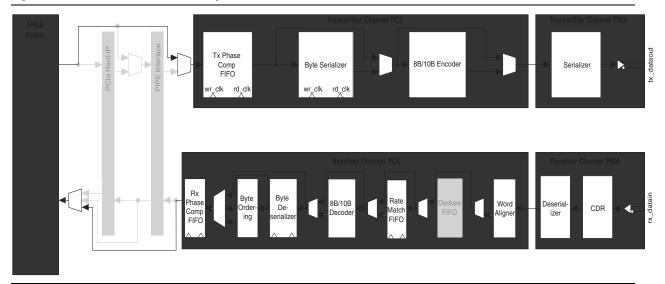

The Cyclone IV GX transceiver channel datapath is highly flexible in Basic mode to implement proprietary protocols. SATA, V-by-One, and Display Port protocol implementations in Cyclone IV GX transceiver are supported with Basic mode. Figure 1–44 shows the transceiver channel datapath supported in Basic mode.

Figure 1-44. Transceiver Channel Datapath in Basic Mode

#### **PIPE Interface**

The PIPE interface provides a standard interface between the PCIe-compliant PHY and MAC layer as defined by the version 2.00 of the PIPE Architecture specification for Gen1 (2.5 Gbps) signaling rate. Any core or IP implementing the PHY MAC, data link, and transaction layers that supports PIPE 2.00 can be connected to the Cyclone IV GX transceiver configured in PIPE mode. Table 1–15 lists the PIPE-specific ports available from the Cyclone IV GX transceiver configured in PIPE mode and the corresponding port names in the PIPE 2.00 specification.

Table 1–15. Transceiver-FPGA Fabric Interface Ports in PIPE Mode

| Transceiver Port Name          | PIPE 2.00 Port Name |  |  |  |  |

|--------------------------------|---------------------|--|--|--|--|

| tx_datain[150] <sup>(1)</sup>  | TxData[150]         |  |  |  |  |

| tx_ctrlenable[10] (1)          | TxDataK[10]         |  |  |  |  |

| rx_dataout[150] <sup>(1)</sup> | RxData[150]         |  |  |  |  |

| rx_ctrldetect[10] (1)          | RxDataK[10]         |  |  |  |  |

| tx_detectrxloop                | TxDetectRx/Loopback |  |  |  |  |

| tx_forceelecidle               | TxElecIdle          |  |  |  |  |

| tx_forcedispcompliance         | TxCompliance        |  |  |  |  |

| pipe8b10binvpolarity           | RxPolarity          |  |  |  |  |

| powerdn[10] (2)                | PowerDown[10]       |  |  |  |  |

| pipedatavalid                  | RxValid             |  |  |  |  |

| pipephydonestatus              | PhyStatus           |  |  |  |  |

| pipeelecidle                   | RxElecIdle          |  |  |  |  |

| pipestatus                     | RxStatus[20]        |  |  |  |  |

#### Notes to Table 1-15:

- (1) When used with PCIe hard IP block, the byte SERDES is not used. In this case, the data ports are 8 bits wide and control identifier is 1 bit wide.

- (2) Cyclone IV GX transceivers do not implement power saving measures in lower power states (P0s, P1, and P2), except when putting the transmitter buffer in electrical idle in the lower power states.

### **Receiver Detection Circuitry**

In PIPE mode, the transmitter supports receiver detection function with a built-in circuitry in the transmitter PMA. The PCIe protocol requires the transmitter to detect if a receiver is present at the far end of each lane as part of the link training and synchronization state machine sequence. This feature requires the following conditions:

- transmitter output buffer to be tri-stated

- have OCT utilization

- 125 MHz clock on the fixedclk port

The circuit works by sending a pulse on the common mode of the transmitter. If an active PCIe receiver is present at the far end, the time constant of the step voltage on the trace is higher compared to when the receiver is not present. The circuitry monitors the time constant of the step signal seen on the trace to decide if a receiver was detected.

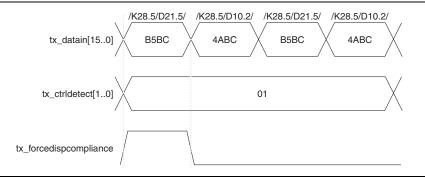

The compliance pattern is a repeating sequence of the four code groups: /K28.5/; /D21.5/; /K28.5/; /D10.2/. Figure 1–53 shows the compliance pattern transmission where the  $tx_forcedispcompliance$  port must be asserted in the same parallel clock cycle as /K28.5/D21.5/ of the compliance pattern on  $tx_datain[15..0]$  port.

Figure 1-53. Compliance Pattern Transmission Support in PCI Express (PIPE) Mode

## **Reset Requirement**

Cyclone IV GX devices meets the PCIe reset time requirement from device power up to the link active state with the configuration schemes listed in Table 1–17.

Table 1–18. Electrical Idle Inference Conditions

| Device       | Configuration Scheme        | <b>Configuration Time (ms)</b> |

|--------------|-----------------------------|--------------------------------|

| EP4CGX15     | Passive serial (PS)         | 51                             |

| EP4CGX22     | PS                          | 92                             |

| EP4CGX30 (1) | PS                          | 92                             |

| EP4CGX50     | Fast passive parallel (FPP) | 41                             |

| EP4CGX75     | FPP                         | 41                             |

| EP4CGX110    | FPP                         | 70                             |

| EP4CGX150    | FPP                         | 70                             |

#### Note to Table 1-18:

### **GIGE Mode**

GIGE mode provides the transceiver channel datapath configuration for GbE (specifically the 1000 Base-X physical layer device (PHY) standard) protocol implementation. The Cyclone IV GX transceiver provides the PMA and the following PCS functions as defined in the IEEE 802.3 specification for 1000 Base-X PHY:

- 8B/10B encoding and decoding

- synchronization

If you enabled the auto-negotiation state machine in the FPGA core with the rate match FIFO, refer to "Clock Frequency Compensation" on page 1–63.

<sup>(1)</sup> EP4CGX30 device in F484 package fulfills the PCIe reset time requirement using FPP configuration scheme with configuration time of 41 ms.

2.5

3.125

| iable 1–25. Pr | 103, nigii allu | LOW Frequ                        | ency Pattern                 | s, and Gham                                                           | ner securiys                                                         | (Part 2 UI                        | 2)                           |                                                                       |                                                                      |  |

|----------------|-----------------|----------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|--|

|                |                 | 8-bit Channel Width              |                              |                                                                       |                                                                      | 10-bit Channel Width              |                              |                                                                       |                                                                      |  |

| Patterns       | Polynomial      | Channel<br>Width<br>of<br>8 bits | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages | Channel<br>Width<br>of<br>10-bits | Word<br>Alignment<br>Pattern | Maximum<br>Data Rate<br>(Gbps) for<br>F324 and<br>Smaller<br>Packages | Maximum<br>Data Rate<br>(Gbps) for<br>F484 and<br>Larger<br>Packages |  |

|                |                 |                                  |                              |                                                                       |                                                                      |                                   |                              |                                                                       | 1                                                                    |  |

Table 1–25. PRBS. High and Low Frequency Patterns, and Channel Settings (Part 2 of 2)

#### Notes to Table 1-25:

Frequency

1111100000

- (1) Channel width refers to the **What is the channel width?** option in the **General** screen of the ALTGX MegaWizard Plug-In Manager. Based on the selection, an 8 or 10 bits wide pattern is generated as indicated by a **Yes (Y)** or **No (N)**.

- (2) A verifier and associated rx bistdone and rx bisterr signals are not available for the specified patterns.

You can enable the serial loopback option to loop the generated PRBS patterns to the receiver channel for verifier to check the PRBS patterns. When the PRBS pattern is received, the rx\_bisterr and rx\_bistdone signals indicate the status of the verifier. After the word aligner restores the word boundary, the rx\_bistdone signal is driven high when the verifier receives a complete pattern cycle and remains asserted until it is reset using the rx\_digitalreset port. After the assertion of rx\_bistdone, the rx\_bisterr signal is asserted for a minimum of three rx\_clkout cycles when errors are detected in the data and deasserts if the following PRBS sequence contains no error. You can reset the PRBS pattern generator and verifier by asserting the tx\_digitalreset and rx\_digitalreset ports, respectively.

#### **Transmitter Only Channel**

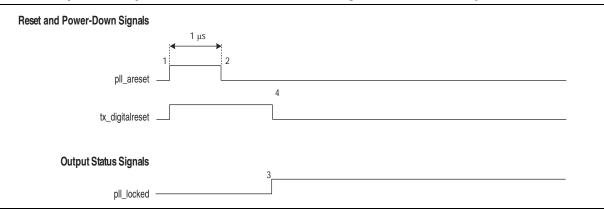

This configuration contains only a transmitter channel. If you create a **Transmitter Only** instance in the ALTGX MegaWizard Plug-In Manager in Basic ×4 functional mode, use the reset sequence shown in Figure 2–3.

Figure 2-3. Sample Reset Sequence for Bonded and Non-Bonded Configuration Transmitter Only Channels

As shown in Figure 2–3, perform the following reset procedure for the **Transmitter Only** channel configuration:

- 1. After power up, assert pll\_areset for a minimum period of 1  $\mu$ s (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset signal asserted during this time period. After you de-assert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. When the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), de-assert the tx\_digitalreset signal (marker 4). At this point, the transmitter is ready for transmitting data.

As shown in Figure 2–12, perform the following reset procedure when using the dynamic reconfiguration controller to change the configuration of the transceiver channel:

- 1. After power up and establishing that the transceiver is operating as desired, write the desired new value in the appropriate registers (including reconfig\_mode\_sel[2:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- For more information, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

- 2. Assert the  $tx\_digitalreset$ ,  $rx\_analogreset$ , and  $rx\_digitalreset$  signals.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. Wait for the assertion of the channel\_reconfig\_done signal (marker 4) that indicates the completion of dynamic reconfiguration in this mode.

- 5. Deassert the tx\_digitalreset signal (marker 5). This signal must be deasserted after assertion of the channel\_reconfig\_done signal (marker 4) and before the deassertion of the rx\_analogreset signal (marker 6).

- 6. Wait for at least five parallel clock cycles after assertion of the channel\_reconfig\_done signal (marker 4) to deassert the rx\_analogreset signal (marker 6).

- 7. Lastly, wait for the rx\_freqlocked signal to go high. After rx\_freqlocked goes high (marker 7), wait for t<sub>LTD\_Auto</sub> to deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

## **Power Down**

The Quartus II software automatically selects the power-down channel feature, which takes effect when you configure the Cyclone IV GX device. All unused transceiver channels and blocks are powered down to reduce overall power consumption. The gxb\_powerdown signal is an optional transceiver block signal. It powers down all transceiver channels and all functional blocks in the transceiver block. The minimum pulse width for this signal is 1  $\mu$ s. After power up, if you use the gxb\_powerdown signal, wait for deassertion of the busy signal, then assert the gxb\_powerdown signal for a minimum of 1  $\mu$ s. Lastly, follow the sequence shown in Figure 2–13.

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 4 of 4)

| Symbol/<br>Description                           | Conditions | C6                                 |     |        | C7, I7 |     |        | C8  |     |        | Unit  |

|--------------------------------------------------|------------|------------------------------------|-----|--------|--------|-----|--------|-----|-----|--------|-------|

|                                                  |            | Min                                | Тур | Max    | Min    | Тур | Max    | Min | Тур | Max    | Ullit |

| PLD-Transceiver Interface                        |            |                                    |     |        |        |     |        |     |     |        |       |

| Interface speed<br>(F324 and smaller<br>package) | _          | 25                                 | _   | 125    | 25     | _   | 125    | 25  | _   | 125    | MHz   |

| Interface speed<br>(F484 and larger<br>package)  | _          | 25                                 | _   | 156.25 | 25     | _   | 156.25 | 25  | _   | 156.25 | MHz   |

| Digital reset pulse width                        | _          | Minimum is 2 parallel clock cycles |     |        |        |     |        |     |     |        |       |

#### Notes to Table 1-21:

- (1) This specification is valid for transmitter output jitter specification with a maximum total jitter value of 112 ps, typically for 3.125 Gbps SRIO and XAUI protocols.

- (2) The minimum reconfig\_clk frequency is 2.5 MHz if the transceiver channel is configured in **Transmitter Only** mode. The minimum reconfig\_clk frequency is 37.5 MHz if the transceiver channel is configured in **Receiver Only** or **Receiver and Transmitter** mode.

- (3) The device cannot tolerate prolonged operation at this absolute maximum.

- (4) The rate matcher supports only up to ±300 parts per million (ppm).

- (5) Supported for the F169 and F324 device packages only.

- (6) Supported for the F484, F672, and F896 device packages only. Pending device characterization.

- (7) To support CDR ppm tolerance greater than ±300 ppm, implement ppm detector in user logic and configure CDR to Manual Lock Mode.

- (8) Asynchronous spread-spectrum clocking is not supported.

- (9) For the EP4CGX30 (F484 package only), EP4CGX50, and EP4CGX75 devices, the CDR ppl tolerance is ±200 ppm.

- (10) Time taken until pll locked goes high after pll powerdown deasserts.

- (11) Time that the CDR must be kept in lock-to-reference mode after rx analogreset deasserts and before rx locktodata is asserted in manual mode.

- (12) Time taken to recover valid data after the rx\_locktodata signal is asserted in manual mode (Figure 1–2), or after rx\_freqlocked signal goes high in automatic mode (Figure 1–3).

- (13) Time taken to recover valid data after the  $rx\_locktodata$  signal is asserted in manual mode.

- (14) Time taken to recover valid data after the  ${\tt rx\_freqlocked}$  signal goes high in automatic mode.

- (15) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.