Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 7155                                                     |

| Number of Logic Elements/Cells | 114480                                                   |

| Total RAM Bits                 | 3981312                                                  |

| Number of I/O                  | 528                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

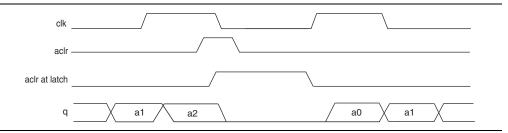

## **Asynchronous Clear**

Cyclone IV devices support asynchronous clears for read address registers, output registers, and output latches only. Input registers other than read address registers are not supported. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are immediately seen. If your RAM does not use output registers, you can still clear the RAM outputs using the output latch asynchronous clear feature.

Asserting asynchronous clear to the read address register during a read operation may corrupt the memory content.

Figure 3–5 shows the functional waveform for the asynchronous clear feature.

Figure 3-5. Output Latch Asynchronous Clear Waveform

You can selectively enable asynchronous clears per logical memory using the Quartus II RAM MegaWizard™ Plug-In Manager.

For more information, refer to the RAM Megafunction User Guide.

There are three ways to reset registers in the M9K blocks:

- Power up the device

- Use the aclr signal for output register only

- Assert the device-wide reset signal using the DEV\_CLRn option

# **Memory Modes**

Cyclone IV devices M9K memory blocks allow you to implement fully-synchronous SRAM memory in multiple modes of operation. Cyclone IV devices M9K memory blocks do not support asynchronous (unregistered) memory inputs.

M9K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port

- Shift-register

- **ROM**

- **FIFO**

Violating the setup or hold time on the M9K memory block input registers may corrupt memory contents. This applies to both read and write operations.

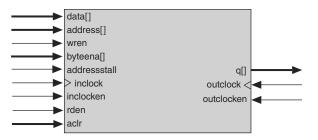

## Single-Port Mode

Single-port mode supports non-simultaneous read and write operations from a single address. Figure 3–6 shows the single-port memory configuration for Cyclone IV devices M9K memory blocks.

Figure 3–6. Single-Port Memory (1), (2)

#### Notes to Figure 3-6:

- (1) You can implement two single-port memory blocks in a single M9K block.

- (2) For more information, refer to "Packed Mode Support" on page 3-4.

During a write operation, the behavior of the RAM outputs is configurable. If you activate rden during a write operation, the RAM outputs show either the new data being written or the old data at that address. If you perform a write operation with rden deactivated, the RAM outputs retain the values they held during the most recent active rden signal.

To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about read-during-write mode, refer to "Read-During-Write Operations" on page 3–15.

The port width configurations for M9K blocks in single-port mode are as follow:

- 8192 × 1

- 4096 × 2

- 2048 × 4

- 1024 × 8

- 1024 × 9

- 512 × 16

- 512 × 18

- 256 × 32

- 256 × 36

# 4. Embedded Multipliers in Cyclone IV Devices

CYIV-51004-1.1

Cyclone® IV devices include a combination of on-chip resources and external interfaces that help increase performance, reduce system cost, and lower the power consumption of digital signal processing (DSP) systems. Cyclone IV devices, either alone or as DSP device co-processors, are used to improve price-to-performance ratios of DSP systems. Particular focus is placed on optimizing Cyclone IV devices for applications that benefit from an abundance of parallel processing resources, which include video and image processing, intermediate frequency (IF) modems used in wireless communications systems, and multi-channel communications and video systems.

This chapter contains the following sections:

- "Embedded Multiplier Block Overview" on page 4–1

- "Architecture" on page 4–2

- "Operational Modes" on page 4–4

# **Embedded Multiplier Block Overview**

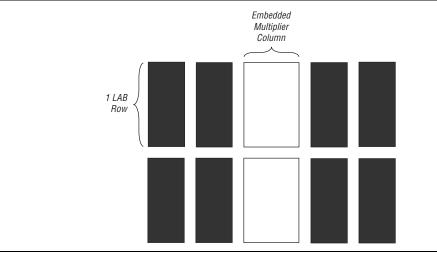

Figure 4–1 shows one of the embedded multiplier columns with the surrounding logic array blocks (LABs). The embedded multiplier is configured as either one  $18\times18$  multiplier or two  $9\times9$  multipliers. For multiplications greater than  $18\times18$ , the Quartus II software cascades multiple embedded multiplier blocks together. There are no restrictions on the data width of the multiplier, but the greater the data width, the slower the multiplication process.

Figure 4–1. Embedded Multipliers Arranged in Columns with Adjacent LABs

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Figure 6–16. RSDS, Mini-LVDS, or PPDS Interface with External Resistor Network on the Top and Bottom I/O Banks  $^{(1)}$

#### Note to Figure 6-16:

(1) R<sub>S</sub> and R<sub>P</sub> values are pending characterization.

A resistor network is required to attenuate the output voltage swing to meet RSDS, mini-LVDS, and PPDS specifications when using emulated transmitters. You can modify the resistor network values to reduce power or improve the noise margin.

The resistor values chosen must satisfy Equation 6–1.

#### Equation 6-1. Resistor Network

$$\frac{R_S \times \frac{R_P}{2}}{R_S + \frac{R_P}{2}} = 50 \Omega$$

Altera recommends that you perform simulations using Cyclone IV devices IBIS models to validate that custom resistor values meet the RSDS, mini-LVDS, or PPDS requirements.

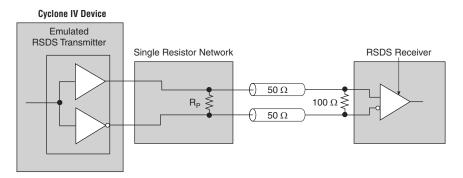

It is possible to use a single external resistor instead of using three resistors in the resistor network for an RSDS interface, as shown in Figure 6–17. The external single-resistor solution reduces the external resistor count while still achieving the required signaling level for RSDS. However, the performance of the single-resistor solution is lower than the performance with the three-resistor network.

Figure 6–17 shows the RSDS interface with a single resistor network on the top and bottom I/O banks.

Figure 6–17. RSDS Interface with Single Resistor Network on the Top and Bottom I/O Banks (1)

#### Note to Figure 6-17:

(1) R<sub>P</sub> value is pending characterization.

The first Cyclone IV device in the chain is the configuration master and it controls the configuration of the entire chain. Other Altera devices that support PS configuration can also be part of the chain as configuration slaves.

In the multi-device AS configuration, the board trace length between the serial configuration device and the master device of the Cyclone IV device must follow the recommendations in Table 8–7 on page 8–18.

The nstatus and conf\_done pins on all target devices are connected together with external pull-up resistors, as shown in Figure 8–3 on page 8–13. These pins are open-drain bidirectional pins on the devices. When the first device asserts nceo (after receiving all its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they receive their configuration data. When all target devices in the chain receive their configuration data and release CONF\_DONE, the pull-up resistor drives a high level on CONF\_DONE line and all devices simultaneously enter initialization mode.

Although you can cascade Cyclone IV devices, serial configuration devices cannot be cascaded or chained together.

If the configuration bitstream size exceeds the capacity of a serial configuration device, you must select a larger configuration device, enable the compression feature, or both. When configuring multiple devices, the size of the bitstream is the sum of the individual device's configuration bitstream.

## **Configuring Multiple Cyclone IV Devices with the Same Design**

Certain designs require that you configure multiple Cyclone IV devices with the same design through a configuration bitstream, or a **.sof**. You can do this through the following methods:

- Multiple .sof

- Single .sof

For both methods, the serial configuration devices cannot be cascaded or chained together.

## **Multiple SRAM Object Files**

Two copies of the **.sof** are stored in the serial configuration device. Use the first copy to configure the master device of the Cyclone IV device and the second copy to configure all remaining slave devices concurrently. All slave devices must have the same density and package. The setup is similar to Figure 8–3 on page 8–13.

To configure four identical Cyclone IV devices with the same .sof, you must set up the chain similar to the example shown in Figure 8–4. The first device is the master device and its MSEL pins must be set to select AS configuration. The other three slave devices are set up for concurrent configuration and their MSEL pins must be set to select PS configuration. The nCEO pin from the master device drives the nCE input pins on all three slave devices, as well as the DATA and DCLK pins that connect in parallel to all

For more information about the operation of the Micron P30 Parallel NOR and P33 Parallel NOR flash memories, search for the keyword "P30" or "P33" on the Micron website (www.micron.com) to obtain the P30 or P33 family datasheet.

## **Single-Device AP Configuration**

The following groups of interface pins are supported in Micron P30 and P33 flash memories:

- Control pins

- Address pins

- Data pins

The following control signals are from the supported parallel flash memories:

- CLF

- active-low reset (RST#)

- active-low chip enable (CE#)

- active-low output enable (OE#)

- active-low address valid (ADV#)

- active-low write enable (WE#)

The supported parallel flash memories output a control signal (WAIT) to Cyclone IV E devices to indicate when synchronous data is ready on the data bus. Cyclone IV E devices have a 24-bit address bus connecting to the address bus (A[24:1]) of the flash memory. A 16-bit bidirectional data bus (DATA[15..0]) provides data transfer between the Cyclone IV E device and the flash memory.

The following control signals are from the Cyclone IV E device to flash memory:

- DCLK

- active-low hard rest (nRESET)

- active-low chip enable (FLASH nCE)

- active-low output enable for the DATA[15..0] bus and WAIT pin (nOE)

- active-low address valid signal and is used to write data into the flash (nAVD)

- active-low write enable and is used to write data into the flash (nWE)

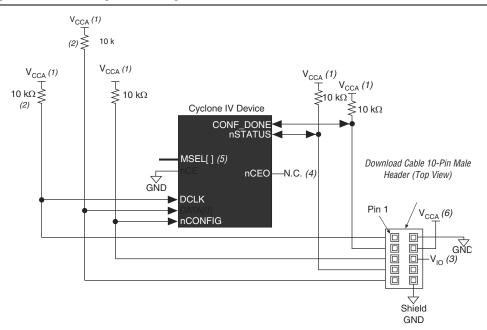

The programming hardware or download cable then places the configuration data one bit at a time on the DATA [0] pin of the device. The configuration data is clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor for the device to initialize.

When you use a download cable, setting the **Auto-restart configuration after error** option does not affect the configuration cycle because you must manually restart configuration in the Quartus II software if an error occurs. Additionally, the **Enable user-supplied start-up clock (CLKUSR)** option has no effect on device initialization, because this option is disabled in the **.sof** when programming the device with the Quartus II Programmer and download cable. Therefore, if you turn on the **CLKUSR** option, you do not have to provide a clock on CLKUSR when you configure the device with the Quartus II Programmer and a download cable.

Figure 8–17 shows PS configuration for Cyclone IV devices with a download cable.

Figure 8-17. PS Configuration Using a Download Cable

#### Notes to Figure 8-17:

- (1) You must connect the pull-up resistor to the same supply voltage as the  $V_{CCA}$  supply.

- (2) The pull-up resistors on DATA[0] and DCLK are only required if the download cable is the only configuration scheme used on your board. This is to ensure that DATA[0] and DCLK are not left floating after configuration. For example, if you also use a configuration device, the pull-up resistors on DATA[0] and DCLK are not required.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. With the USB-Blaster, ByteBlaster II, ByteBlaster MV, and EthernetBlaster, this pin is a no connect.

- (4) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (5) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9 for PS configuration schemes. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (6) Power up the V<sub>CC</sub> of the ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from V<sub>CCA</sub>. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

Figure 8-28. Combining JTAG and AS Configuration Schemes

#### Notes to Figure 8-28:

Download Cable (AS Mode)

10-Pin Male Header

(1) Connect these pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

GND

(2) Power up the  $V_{CC}$  of the EthernetBlaster, ByteBlaster II, or USB-Blaster cable with the 3.3-V supply.

**GND**

10 pf

**GND**

(6)

(3) Pin 6 of the header is a  $V_{10}$  reference voltage for the MasterBlaster output driver. The  $V_{10}$  must match the  $V_{CCA}$  of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. When using the ByteBlasterMV download cable, this pin is a no connect. When using the USB-Blaster and ByteBlaster II cables, this pin is connected to nce when it is used for AS programming, otherwise it is a no connect.

10 pf

GND

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL for AS configuration schemes, refer to Table 8-3 on page 8-8, Table 8-4 on page 8-8, and Table 8-5 on page 8-9. Connect the MSEL pins directly to  $V_{\text{CCA}}$  or GND.

- (5) Power up the  $V_{CC}$  of the EthernetBlaster, ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V  $V_{CCA}$  supply. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a  $V_{CC}$  power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

- (6) You must place the diodes and capacitors as close as possible to the Cyclone IV device. Altera recommends using the Schottky diode, which has a relatively lower forward diode voltage (VF) than the switching and Zener diodes, for effective voltage clamping.

- (7) These pins are dual-purpose I/O pins. The noso pin functions as FLASH note pin in AP mode. The ASDO pin functions as DATA[1] pin in AP and FPP modes.

- (8) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ ..

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCT<sub>1</sub>K

Figure 10–3 shows the JTAG chain of mixed voltages and how a level shifter is inserted in the chain.

# **Boundary-Scan Description Language Support**

The boundary-scan description language (BSDL), a subset of VHDL, provides a syntax that allows you to describe the features of an IEEE Std. 1149.1/IEEE Std. 1149.6 BST-capable device that can be tested.

- For more information about how to download BSDL files for IEEE Std. 1149.1-compliant Cyclone IV E devices, refer to IEEE Std. 1149.1 BSDL Files.

- For more information about how to download BSDL files for IEEE Std. 1149.6-compliant Cyclone IV GX devices, refer to IEEE Std. 1149.6 BSDL Files.

- You can also generate BSDL files (pre-configuration and post-configuration) for IEEE Std. 1149.1/IEEE Std. 1149.6-compliant Cyclone IV devices with the Quartus<sup>®</sup> II software version 9.1 SP1 and later. For more information about the procedure to generate BSDL files using the Quartus II software, refer to BSDL Files Generation in Quartus II.

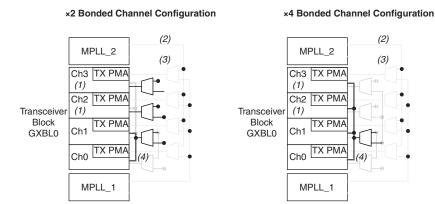

Figure 1–36 and Figure 1–37 show the independent high-speed clock and bonded low-speed clock distributions for transceivers in F324 and smaller packages, and in F484 and larger packages in bonded (×2 and ×4) channel configuration.

Figure 1–36. Clock Distribution in Bonded ( $\times 2$  and  $\times 4$ ) Channel Configuration for Transceivers in F324 and Smaller Packages.

#### Notes to Figure 1-36:

- (1) Transceiver channels 2 and 3 are not available for devices in F169 and smaller packages.

- (2) High-speed clock.

- (3) Low-speed clock.

- (4) Bonded common low-speed clock path.

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 2 of 2)

| Chann                   | nel Configuration        | Quartus II Selection                                                                                                                                                                                        |

|-------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bonded                  | With rate match FIFO (1) | coreclkout clock feeds the FIFO read clock for the bonded channels. coreclkout clock is the common bonded low-speed clock, which also feeds the FIFO read clock and transmitter PCS in the bonded channels. |

| Without rate match FIFO |                          | $rx\_clkout$ clock feeds the FIFO read clock. $rx\_clkout$ is forwarded through the receiver channel from low-speed recovered clock, which also feeds the FIFO write clock.                                 |

#### Note to Table 1-13:

(1) Configuration with rate match FIFO is supported in transmitter and receiver operation.

When using user-specified clock option, ensure that the clock feeding rx\_coreclk port has 0 ppm difference with the RX phase compensation FIFO write clock.

## **Calibration Block**

This block calibrates the OCT resistors and the analog portions of the transceiver blocks to ensure that the functionality is independent of process, voltage, and temperature (PVT) variations.

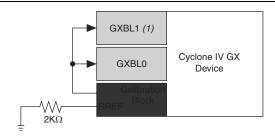

Figure 1–40 shows the location of the calibration block and how it is connected to the transceiver blocks.

Figure 1-40. Transceiver Calibration Blocks Location and Connection

#### Note to Figure 1-40:

(1) Transceiver block GXBL1 is only available for devices in F484 and larger packages.

Table 1–29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for Cyclone IV GX (Part 2 of 2)

| Block                 | Port Name         | Input/<br>Output | Clock Domain                                                                        | Description                                                                                                                                                                                 |  |  |

|-----------------------|-------------------|------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       |                   |                  |                                                                                     | Transceiver block power down.                                                                                                                                                               |  |  |

|                       | gxb_powerdown     | Input            | Asynchronous signal                                                                 | ■ When asserted, all digital and analog circuitry in the PCS, HSSI, CDR, and PCIe modules are powered down.                                                                                 |  |  |

|                       |                   |                  |                                                                                     | <ul> <li>Asserting the gxb_powerdown signal does not power<br/>down the refclk buffers.</li> </ul>                                                                                          |  |  |

| Reset & Power<br>Down | tx_digitalreset   | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Transmitter PCS reset.  When asserted, the transmitter PCS blocks are reset.                                                                                                                |  |  |

| rx_analogreset        |                   | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Receiver PMA reset.  When asserted, analog circuitry in the receiver PMA block is reset.                                                                                                    |  |  |

| rx_digitalreset       |                   | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Receiver PCS reset.  When asserted, the receiver PCS blocks are reset.                                                                                                                      |  |  |

|                       |                   |                  |                                                                                     | Dynamic reconfiguration clock.                                                                                                                                                              |  |  |

|                       | reconfig_clk      | Input            | Clock signal                                                                        | Also used for offset cancellation except in PIPE mode.                                                                                                                                      |  |  |

| Reconfiguration       | Tooding_one       |                  | olook olgilal                                                                       | ■ For the supported frequency range for this clock, refer to the <i>Cyclone IV Device Data Sheet</i> chapter.                                                                               |  |  |

|                       | reconfig_togxb    | Input            | Asynchronous signal                                                                 | From the dynamic reconfiguration controller.                                                                                                                                                |  |  |

|                       | reconfig_fromgxb  | Output           | Asynchronous signal                                                                 | To the dynamic reconfiguration controller.                                                                                                                                                  |  |  |

| Calibration Block     | cal_blk_clk       | Input            | Clock signal                                                                        | Clock for the transceiver calibration block.                                                                                                                                                |  |  |

| Galibration Block     | cal_blk_powerdown | Input            | Asynchronous signal                                                                 | Calibration block power down control.                                                                                                                                                       |  |  |

|                       |                   |                  |                                                                                     | BIST or PRBS test completion indicator.                                                                                                                                                     |  |  |

|                       | rx_bistdone       | Output           | Asynchronous signal                                                                 | ■ A high level during BIST test mode indicates the verifier either receives complete pattern cycle or detects an error and stays asserted until being reset using the rx_digitalreset port. |  |  |

| Test Mode             |                   |                  |                                                                                     | ■ A high level during PRBS test mode indicates the verifier receives complete pattern cycle and stays asserted until being reset using the rx_digitalreset port.                            |  |  |

|                       |                   |                  |                                                                                     | BIST or PRBS verifier error indicator                                                                                                                                                       |  |  |

|                       | rx_bisterr        | Output           | Asynchronous signal                                                                 | ■ In BIST test mode, the signal stays asserted upon detecting an error until being reset using the rx_digitalreset port.                                                                    |  |  |

|                       |                   |                  |                                                                                     | ■ In PRBS test mode, the signal asserts for a minimum of 3 rx_clkout clock cycles upon detecting an error and deasserts if the following PRBS sequence contains no error.                   |  |  |

The deassertion of the busy signal indicates proper completion of the offset cancellation process on the receiver channel.

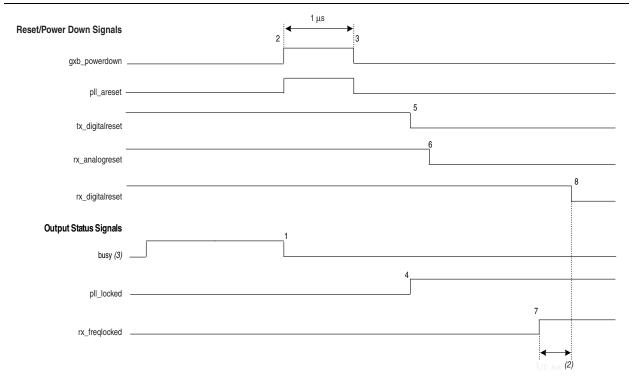

Figure 2–13. Sample Reset Sequence of a Receiver and Transmitter Channels-Receiver CDR in Automatic Lock Mode with the Optional gxb powerdown Signal <sup>(1)</sup>

#### Notes to Figure 2-13:

- (1) The gxb\_powerdown signal must not be asserted during the offset cancellation sequence.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the <code>Cyclone IV Device Datasheet</code> chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

# **Simulation Requirements**

The following are simulation requirements:

- The gxb\_powerdown port is optional. In simulation, if the gxb\_powerdown port is not instantiated, you must assert the tx\_digitalreset, rx\_digitalreset, and rx analogreset signals appropriately for correct simulation behavior.

- If the gxb\_powerdown port is instantiated, and the other reset signals are not used, you must assert the gxb\_powerdown signal for at least 1 μs for correct simulation behavior.

- You can deassert the rx\_digitalreset signal immediately after the rx\_freqlocked signal goes high to reduce the simulation run time. It is not necessary to wait for t<sub>LTD\_Auto</sub> (as suggested in the actual reset sequence).

- The busy signal is deasserted after about 20 parallel reconfig\_clk clock cycles in order to reduce simulation run time. For silicon behavior in hardware, you can follow the reset sequences described in the previous pages.

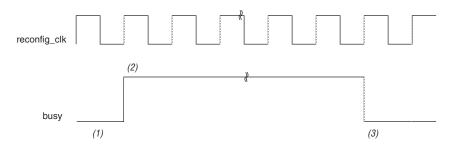

Figure 3–3 shows the timing diagram for a offset cancellation process.

Figure 3-3. Dynamic Reconfiguration Signals Transition during Offset Cancellation

#### Notes to Figure 3-3:

- (1) After device power up, the busy signal remains low for the first reconfig\_clk cycle.

- (2) The busy signal then gets asserted for the second reconfig\_clk cycle, when the dynamic reconfiguration controller initiates the offset cancellation process.

- (3) The deassertion of the busy signal indicates the successful completion of the offset cancellation process.

### **Functional Simulation of the Offset Cancellation Process**

You must connect the ALTGX\_RECONFIG instances to the ALTGX instances in your design for functional simulation. Functional simulation uses a reduced timing model of the dynamic reconfiguration controller. Therefore, the duration of the offset cancellation process is 16 reconfig\_clk clock cycles for functional simulation only. The gxb\_powerdown signal must not be asserted during the offset cancellation sequence (for functional simulation and silicon).

# **Dynamic Reconfiguration Modes**

When you enable the dynamic reconfiguration feature, you can reconfigure the following portions of each transceiver channel dynamically, without powering down the other transceiver channels or the FPGA fabric of the device:

- Analog (PMA) controls reconfiguration

- Channel reconfiguration

- PLL reconfiguration

Table 3–3 lists the supported dynamic reconfiguration modes for Cyclone IV GX devices.

Table 3-3. Cyclone IV GX Supported Dynamic Reconfiguration Mode (Part 1 of 2)

|                                           | Operational Mode    |                  |                                        | Qua   |                    |                     |                      |

|-------------------------------------------|---------------------|------------------|----------------------------------------|-------|--------------------|---------------------|----------------------|

| Dynamic Reconfiguration<br>Supported Mode | Transmitter<br>Only | Receiver<br>Only | Transmitter<br>and<br>Receiver<br>Only | ALTGX | ALTGX_<br>RECONFIG | ALTPLL_<br>RECONFIG | .mif<br>Requirements |

| Offset Cancellation                       | _                   | ✓                | <b>✓</b>                               | ✓     | ✓                  | _                   | _                    |

| Analog (PMA) Controls<br>Reconfiguration  | ~                   | <b>✓</b>         | ~                                      | ~     | ~                  | _                   | _                    |

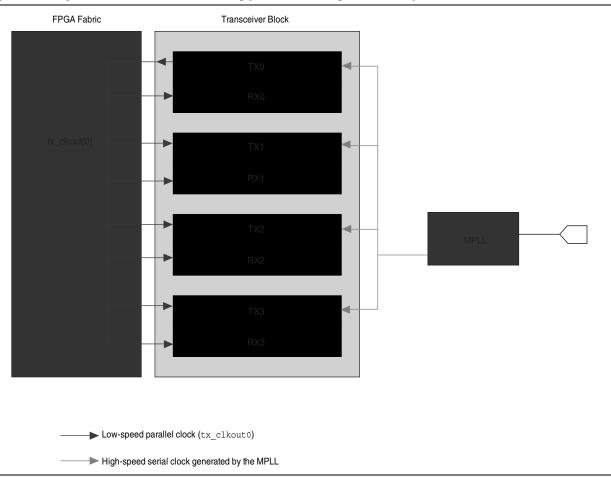

#### **Option 1: Share a Single Transmitter Core Clock Between Receivers**

- Enable this option if you want tx\_clkout of the first channel (channel 0) of the transceiver block to provide the read clock to the Receive Phase Compensation FIFOs of the remaining receiver channels in the transceiver block.

- This option is typically enabled when all the channels of a transceiver block are in a Basic or Protocol configuration with rate matching enabled and are reconfigured to another Basic or Protocol configuration with rate matching enabled.

Figure 3–13 shows the sharing of channel 0's tx\_clkout between all four channels of a transceiver block.

Figure 3-13. Option 1 for Receiver Core Clocking (Channel Reconfiguration Mode)

This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Cyclone® IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                    | Contact Method | Address                   |  |

|--------------------------------|----------------|---------------------------|--|

| Technical support              | Website        | www.altera.com/support    |  |

| Technical training             | Website        | www.altera.com/training   |  |

| 16011110ai trailling           | Email          | custrain@altera.com       |  |

| Product literature             | Website        | www.altera.com/literature |  |

| Nontechnical support (general) | Email          | nacomp@altera.com         |  |

| (software licensing)           | Email          | authorization@altera.com  |  |

#### Note to Table:

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                              |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example,   qdesigns directory, \textbf{D}: drive, and \textbf{chiptrip.gdf} file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                        |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                 |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <file name=""> and <project name="">.pof file.</project></file>                                                                                           |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                    |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                 |

<sup>(1)</sup> You can also contact your local Altera sales office or sales representative.

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up. Use Table 1–10 and Equation 1–1 to determine the final OCT resistance considering the variations after calibration at device power-up. Table 1–10 lists the change percentage of the OCT resistance with voltage and temperature.

Table 1–10. OCT Variation After Calibration at Device Power-Up for Cyclone IV Devices (1)

| Nominal Voltage | dR/dT (%/°C) | dR/dV (%/mV) |

|-----------------|--------------|--------------|

| 3.0             | 0.262        | -0.026       |

| 2.5             | 0.234        | -0.039       |

| 1.8             | 0.219        | -0.086       |

| 1.5             | 0.199        | -0.136       |

| 1.2             | 0.161        | -0.288       |

#### Note to Table 1-10:

(1) This specification is not applicable to EP4CGX15, EP4CGX22, and EP4CGX30 devices.

#### Equation 1-1. Final OCT Resistance (1), (2), (3), (4), (5), (6)

$$\begin{split} &\Delta R_V = (V_2 - V_1) \times 1000 \times dR/dV ------ (7) \\ &\Delta R_T = (T_2 - T_1) \times dR/dT ------ (8) \\ &\text{For } \Delta R_x < 0; \ MF_x = 1/\left(|\Delta R_x|/100 + 1\right) ------- (9) \\ &\text{For } \Delta R_x > 0; \ MF_x = \Delta R_x/100 + 1 ------ (10) \\ &MF = MF_V \times MF_T ------ (11) \\ &R_{final} = R_{initial} \times MF ------ (12) \end{split}$$

#### Notes to Equation 1-1:

- (1)  $T_2$  is the final temperature.

- (2) T<sub>1</sub> is the initial temperature.

- (3) MF is multiplication factor.

- (4) R<sub>final</sub> is final resistance.

- (5) R<sub>initial</sub> is initial resistance.

- (6) Subscript  $_{\text{X}}$  refers to both  $_{\text{V}}$  and  $_{\text{T}}$ .

- (7)  $\Delta R_V$  is a variation of resistance with voltage.

- (8)  $\Delta R_T$  is a variation of resistance with temperature.

- (9) dR/dT is the change percentage of resistance with temperature after calibration at device power-up.

- (10) dR/dV is the change percentage of resistance with voltage after calibration at device power-up.

- (11) V2 is final voltage.

- (12)  $V_1$  is the initial voltage.

## Internal Weak Pull-Up and Weak Pull-Down Resistor

Table 1-12 lists the weak pull-up and pull-down resistor values for Cyclone IV devices.

Table 1–12. Internal Weak Pull-Up and Weak Pull-Down Resistor Values for Cyclone IV Devices (1)

| Symbol   | Parameter                                                                                                    | Conditions                                  | Min | Тур | Max | Unit |

|----------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|          |                                                                                                              | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (2), (3) | 7   | 25  | 41  | kΩ   |

|          | Value of the I/O pin pull-up resistor                                                                        | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (2), (3) | 7   | 28  | 47  | kΩ   |

| <b>D</b> | before and during configuration, as well as user mode if you enable the programmable pull-up resistor option | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (2), (3) | 8   | 35  | 61  | kΩ   |

| I I _PU  |                                                                                                              | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (2), (3) | 10  | 57  | 108 | kΩ   |

|          |                                                                                                              | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (2), (3) | 13  | 82  | 163 | kΩ   |

|          |                                                                                                              | $V_{CCIO} = 1.2 \text{ V} \pm 5\%$ (2), (3) | 19  | 143 | 351 | kΩ   |

|          |                                                                                                              | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (4)      | 6   | 19  | 30  | kΩ   |

|          | Value of the I/O min well down wasints a                                                                     | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (4)      | 6   | 22  | 36  | kΩ   |

| R_PD     | Value of the I/O pin pull-down resistor before and during configuration                                      | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (4)      | 6   | 25  | 43  | kΩ   |

|          | bototo and daring configuration                                                                              | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (4)      | 7   | 35  | 71  | kΩ   |

|          |                                                                                                              | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (4)      | 8   | 50  | 112 | kΩ   |

#### Notes to Table 1-12:

- (1) All I/O pins have an option to enable weak pull-up except the configuration, test, and JTAG pins. The weak pull-down feature is only available for JTAG TCK.

- (2) Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{\text{CCIO}}$ .

- (3)  $R_{PU} = (V_{CC10} V_1)/I_{R_PU}$ Minimum condition:  $-40^{\circ}C$ ;  $V_{CC10} = V_{CC} + 5\%$ ,  $V_1 = V_{CC} + 5\% 50$  mV; Typical condition:  $25^{\circ}C$ ;  $V_{CC10} = V_{CC}$ ,  $V_1 = 0$  V;  $V_2 = 0$  V;  $V_3 = 0$  V;  $V_4 = 0$  V is which  $V_4 = 0$

- Maximum condition:  $100^{\circ}$ C;  $V_{CCIO} = V_{CC} 5\%$ ,  $V_I = 0$  V; in which  $V_I$  refers to the input voltage at the I/O pin.

- (4)  $R_{PD} = V_I/I_{RPD}$

- Minimum condition: -40°C;  $V_{CCIO} = V_{CC} + 5\%$ ,  $V_I = 50$  mV;

- Typical condition: 25°C;  $V_{CCIO} = V_{CC}$ ,  $V_I = V_{CC} 5\%$ ;

- Maximum condition:  $100^{\circ}\text{C}$ ;  $V_{\text{CCIO}} = V_{\text{CC}} 5\%$ ,  $V_{\text{I}} = V_{\text{CC}} 5\%$ ; in which  $V_{\text{I}}$  refers to the input voltage at the I/O pin.

#### **Hot-Socketing**

Table 1–13 lists the hot-socketing specifications for Cyclone IV devices.

Table 1–13. Hot-Socketing Specifications for Cyclone IV Devices

| Symbol                  | Parameter                         | Maximum |  |  |

|-------------------------|-----------------------------------|---------|--|--|

| I <sub>IOPIN(DC)</sub>  | DC current per I/O pin            | 300 μΑ  |  |  |

| I <sub>IOPIN(AC)</sub>  | 8 mA (1)                          |         |  |  |

| I <sub>XCVRTX(DC)</sub> | DC current per transceiver TX pin |         |  |  |

| I <sub>XCVRRX(DC)</sub> | 50 mA                             |         |  |  |

#### Note to Table 1-13:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|IIOPIN| = C \frac{dv}{dt}$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

MHz

| Device  | Performance |       |     |         |         |       |         |    |

|---------|-------------|-------|-----|---------|---------|-------|---------|----|

| Device  | C6          | C7    | C8  | C8L (1) | C9L (1) | 17    | I8L (1) | A7 |

| EP4CE55 | 500         | 437.5 | 402 | 362     | 265     | 437.5 | 362     | _  |

| EP4CE75 | 500         | 437.5 | 402 | 362     | 265     | 437.5 | 362     | _  |

Unit MHz MHz EP4CE115 437.5 402 437.5 MHz 362 265 362 EP4CGX15 500 437.5 402 \_\_\_ 437.5 MHz EP4CGX22 500 437.5 402 437.5 MHz EP4CGX30 500 437.5 402 437.5 MHz EP4CGX50 500 437.5 402 437.5 MHz EP4CGX75 437.5 500 402 437.5 MHz 437.5 EP4CGX110 500 402 437.5 MHz 500 437.5 402 437.5

#### Note to Table 1-24:

EP4CGX150

Table 1–24. Clock Tree Performance for Cyclone IV Devices (Part 2 of 2)

## **PLL Specifications**

Table 1-25 lists the PLL specifications for Cyclone IV devices when operating in the commercial junction temperature range (0°C to 85°C), the industrial junction temperature range (-40°C to 100°C), the extended industrial junction temperature range (-40°C to 125°C), and the automotive junction temperature range (-40°C to 125°C). For more information about the PLL block, refer to "Glossary" on page 1–37.

Table 1–25. PLL Specifications for Cyclone IV Devices (1), (2) (Part 1 of 2)

| Symbol                                           | Parameter                                                    | Min | Тур | Max   | Unit |

|--------------------------------------------------|--------------------------------------------------------------|-----|-----|-------|------|

|                                                  | Input clock frequency (-6, -7, -8 speed grades)              | 5   | _   | 472.5 | MHz  |

| f <sub>IN</sub> (3)                              | Input clock frequency (-8L speed grade)                      | 5   | _   | 362   | MHz  |

|                                                  | Input clock frequency (-9L speed grade)                      | 5   | _   | 265   | MHz  |

| f <sub>INPFD</sub>                               | PFD input frequency                                          | 5   | _   | 325   | MHz  |

| f <sub>VCO</sub> (4)                             | PLL internal VCO operating range                             | 600 | _   | 1300  | MHz  |

| f <sub>INDUTY</sub>                              | Input clock duty cycle                                       | 40  | _   | 60    | %    |

| t <sub>INJITTER_CCJ</sub> (5)                    | Input clock cycle-to-cycle jitter F <sub>REF</sub> ≥ 100 MHz | _   | _   | 0.15  | UI   |

|                                                  | F <sub>REF</sub> < 100 MHz                                   | _   | _   | ±750  | ps   |

| f <sub>OUT_EXT</sub> (external clock output) (3) | PLL output frequency                                         | _   | _   | 472.5 | MHz  |

|                                                  | PLL output frequency (-6 speed grade)                        | _   | _   | 472.5 | MHz  |

|                                                  | PLL output frequency (-7 speed grade)                        | _   | _   | 450   | MHz  |

| f <sub>OUT</sub> (to global clock)               | PLL output frequency (-8 speed grade)                        | _   | _   | 402.5 | MHz  |

|                                                  | PLL output frequency (-8L speed grade)                       | _   | _   | 362   | MHz  |

|                                                  | PLL output frequency (-9L speed grade)                       | _   | _   | 265   | MHz  |

| t <sub>OUTDUTY</sub>                             | Duty cycle for external clock output (when set to 50%)       | 45  | 50  | 55    | %    |

| t <sub>LOCK</sub>                                | Time required to lock from end of device configuration       | _   | _   | 1     | ms   |

<sup>(1)</sup> Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades.

Table 1-46. Glossary (Part 5 of 5)

| Letter | Term                                                                                                                                                                          | Definitions                                                                                                                                                                                    |  |  |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        | V <sub>CM(DC)</sub>                                                                                                                                                           | DC common mode input voltage.                                                                                                                                                                  |  |  |  |  |  |  |

|        | V <sub>DIF(AC)</sub>                                                                                                                                                          | AC differential input voltage: The minimum AC input differential voltage required for switching.                                                                                               |  |  |  |  |  |  |

|        | V <sub>DIF(DC)</sub>                                                                                                                                                          | DC differential input voltage: The minimum DC input differential voltage required for switching.                                                                                               |  |  |  |  |  |  |

|        | V <sub>ICM</sub>                                                                                                                                                              | Input common mode voltage: The common mode of the differential signal at the receiver.                                                                                                         |  |  |  |  |  |  |

|        | V <sub>ID</sub> Input differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver. |                                                                                                                                                                                                |  |  |  |  |  |  |

|        | V <sub>IH</sub>                                                                                                                                                               | Voltage input high: The minimum positive voltage applied to the input that is accepted by the device as a logic high.                                                                          |  |  |  |  |  |  |

|        | V <sub>IH(AC)</sub>                                                                                                                                                           | High-level AC input voltage.                                                                                                                                                                   |  |  |  |  |  |  |

|        | V <sub>IH(DC)</sub>                                                                                                                                                           | High-level DC input voltage.                                                                                                                                                                   |  |  |  |  |  |  |

|        | V <sub>IL</sub>                                                                                                                                                               | Voltage input low: The maximum positive voltage applied to the input that is accepted by the device as a logic low.                                                                            |  |  |  |  |  |  |

|        | V <sub>IL (AC)</sub>                                                                                                                                                          | Low-level AC input voltage.                                                                                                                                                                    |  |  |  |  |  |  |

|        | V <sub>IL (DC)</sub>                                                                                                                                                          | Low-level DC input voltage.                                                                                                                                                                    |  |  |  |  |  |  |

|        | V <sub>IN</sub>                                                                                                                                                               | DC input voltage.                                                                                                                                                                              |  |  |  |  |  |  |

|        | V <sub>OCM</sub>                                                                                                                                                              | Output common mode voltage: The common mode of the differential signal at the transmitter.                                                                                                     |  |  |  |  |  |  |

| V      | V <sub>OD</sub>                                                                                                                                                               | Output differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. $V_{0D} = V_{0H} - V_{0L}$ . |  |  |  |  |  |  |

|        | V <sub>OH</sub>                                                                                                                                                               | Voltage output high: The maximum positive voltage from an output that the device considers is accepted as the minimum positive high level.                                                     |  |  |  |  |  |  |

|        | V <sub>OL</sub>                                                                                                                                                               | Voltage output low: The maximum positive voltage from an output that the device considers is accepted as the maximum positive low level.                                                       |  |  |  |  |  |  |

|        | V <sub>OS</sub>                                                                                                                                                               | Output offset voltage: $V_{OS} = (V_{OH} + V_{OL}) / 2$ .                                                                                                                                      |  |  |  |  |  |  |

|        | V <sub>OX (AC)</sub>                                                                                                                                                          | AC differential output cross point voltage: the voltage at which the differential output signals must cross.                                                                                   |  |  |  |  |  |  |

|        | V <sub>REF</sub>                                                                                                                                                              | Reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                         |  |  |  |  |  |  |

|        | V <sub>REF (AC)</sub>                                                                                                                                                         | AC input reference voltage for the SSTL and HSTL I/O standards. $V_{REF(AC)} = V_{REF(DC)} + noise$ . The peak-to-peak AC noise on $V_{REF}$ must not exceed 2% of $V_{REF(DC)}$ .             |  |  |  |  |  |  |

|        | V <sub>REF (DC)</sub>                                                                                                                                                         | DC input reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                |  |  |  |  |  |  |

|        | V <sub>SWING (AC)</sub>                                                                                                                                                       | AC differential input voltage: AC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |  |  |  |  |  |  |

|        | V <sub>SWING (DC)</sub>                                                                                                                                                       | DC differential input voltage: DC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |  |  |  |  |  |  |

|        | V <sub>TT</sub>                                                                                                                                                               | Termination voltage for the SSTL and HSTL I/O standards.                                                                                                                                       |  |  |  |  |  |  |

|        | V <sub>X (AC)</sub> AC differential input cross point voltage: The voltage at which the differential input cross.                                                             |                                                                                                                                                                                                |  |  |  |  |  |  |

| W      | _                                                                                                                                                                             |                                                                                                                                                                                                |  |  |  |  |  |  |

| X      | _                                                                                                                                                                             |                                                                                                                                                                                                |  |  |  |  |  |  |

| Υ      | _                                                                                                                                                                             | _                                                                                                                                                                                              |  |  |  |  |  |  |

| Z      | _                                                                                                                                                                             | _                                                                                                                                                                                              |  |  |  |  |  |  |