Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 7155                                                       |

| Number of Logic Elements/Cells | 114480                                                     |

| Total RAM Bits                 | 3981312                                                    |

| Number of I/O                  | 528                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.97V ~ 1.03V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29c8ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer/deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe)

Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

Violating the setup or hold time on the M9K memory block input registers may corrupt memory contents. This applies to both read and write operations.

# Single-Port Mode

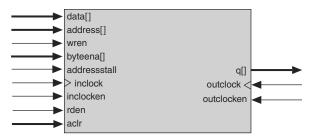

Single-port mode supports non-simultaneous read and write operations from a single address. Figure 3–6 shows the single-port memory configuration for Cyclone IV devices M9K memory blocks.

Figure 3–6. Single-Port Memory (1), (2)

#### Notes to Figure 3-6:

- (1) You can implement two single-port memory blocks in a single M9K block.

- (2) For more information, refer to "Packed Mode Support" on page 3-4.

During a write operation, the behavior of the RAM outputs is configurable. If you activate rden during a write operation, the RAM outputs show either the new data being written or the old data at that address. If you perform a write operation with rden deactivated, the RAM outputs retain the values they held during the most recent active rden signal.

To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about read-during-write mode, refer to "Read-During-Write Operations" on page 3–15.

The port width configurations for M9K blocks in single-port mode are as follow:

- 8192 × 1

- 4096 × 2

- 2048 × 4

- 1024 × 8

- 1024 × 9

- 512 × 16

- 512 × 18

- 256 × 32

- 256 × 36

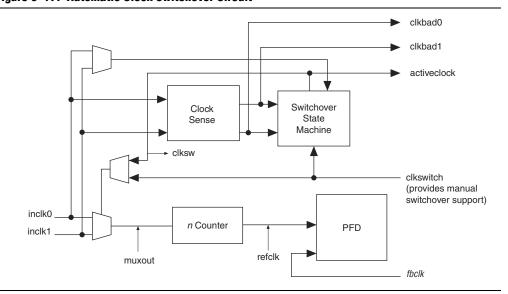

### **Clock Switchover**

The clock switchover feature allows the PLL to switch between two reference input clocks. Use this feature for clock redundancy or for a dual-clock domain application, such as a system that turns on the redundant clock if the previous clock stops running. Your design can automatically perform clock switchover when the clock is no longer toggling, or based on the user control signal, clkswitch.

### **Automatic Clock Switchover**

PLLs of Cyclone IV devices support a fully configurable clock switchover capability.

When the current reference clock is not present, the clock-sense block automatically switches to the backup clock for PLL reference. The clock switchover circuit also sends out three status signals—clkbad0, clkbad1, and activeclock—from the PLL to implement a custom switchover circuit. You can select a clock source at the backup clock by connecting it to the inclk1 port of the PLL in your design.

Figure 5–17 shows the block diagram of the switchover circuit built into the PLL.

Figure 5-17. Automatic Clock Switchover Circuit

There are two ways to use the clock switchover feature:

- Use the switchover circuitry for switching from inclk0 to inclk1 running at the same frequency. For example, in applications that require a redundant clock with the same frequency as the reference clock, the switchover state machine generates a signal that controls the multiplexer select input shown in Figure 5–17. In this case, inclk1 becomes the reference clock for the PLL. This automatic switchover can switch back and forth between the inclk0 and inclk1 clocks any number of times, when one of the two clocks fails and the other clock is available.

- Use the clkswitch input for user- or system-controlled switch conditions. This is possible for same-frequency switchover or to switch between inputs of different frequencies. For example, if inclk0 is 66 MHz and inclk1 is 200 MHz, you must control the switchover because the automatic clock-sense circuitry cannot monitor primary and secondary clock frequencies with a frequency difference of more than

- Low time count = 1 cycle

- rselodd = 1 effectively equals:

- High time count = 1.5 cycles

- Low time count = 1.5 cycles

- Duty cycle = (1.5/3)% high time count and (1.5/3)% low time count

# **Scan Chain Description**

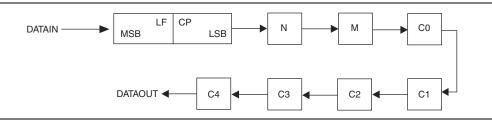

Cyclone IV PLLs have a 144-bit scan chain.

Table 5–7 lists the number of bits for each component of the PLL.

Table 5-7. Cyclone IV PLL Reprogramming Bits

| Die als Name               | Number of Bits            |       |       |  |  |  |  |  |

|----------------------------|---------------------------|-------|-------|--|--|--|--|--|

| Block Name                 | Counter                   | Other | Total |  |  |  |  |  |

| C4 <sup>(1)</sup>          | 16                        | 2 (2) | 18    |  |  |  |  |  |

| C3                         | 16                        | 2 (2) | 18    |  |  |  |  |  |

| C2                         | 16                        | 2 (2) | 18    |  |  |  |  |  |

| C1                         | 16                        | 2 (2) | 18    |  |  |  |  |  |

| CO                         | 16                        | 2 (2) | 18    |  |  |  |  |  |

| M                          | 16                        | 2 (2) | 18    |  |  |  |  |  |

| N                          | 16                        | 2 (2) | 18    |  |  |  |  |  |

| Charge Pump                | 9                         | 0     | 9     |  |  |  |  |  |

| Loop Filter <sup>(3)</sup> | 9                         | 0     | 9     |  |  |  |  |  |

| Total number of bits:      | Total number of bits: 144 |       |       |  |  |  |  |  |

### Notes to Table 5-7:

- (1) LSB bit for C4 low-count value is the first bit shifted into the scan chain.

- (2) These two control bits include rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

- (3) MSB bit for loop filter is the last bit shifted into the scan chain.

Figure 5–24 shows the scan chain order of the PLL components.

Figure 5-24. PLL Component Scan Chain Order

# **External Memory Interfacing**

Cyclone IV devices support I/O standards required to interface with a broad range of external memory interfaces, such as DDR SDRAM, DDR2 SDRAM, and QDR II SRAM.

For more information about Cyclone IV devices external memory interface support, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

# **Pad Placement and DC Guidelines**

You can use the Quartus II software to validate your pad and pin placement.

### **Pad Placement**

Altera recommends that you create a Quartus II design, enter your device I/O assignments and compile your design to validate your pin placement. The Quartus II software checks your pin connections with respect to the I/O assignment and placement rules to ensure proper device operation. These rules depend on device density, package, I/O assignments, voltage assignments and other factors that are not fully described in this chapter.

For more information about how the Quartus II software checks I/O restrictions, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

## **DC** Guidelines

For the Quartus II software to automatically check for illegally placed pads according to the DC guidelines, set the DC current sink or source value to **Electromigration Current** assignment on each of the output pins that are connected to the external resistive load.

The programmable current strength setting has an impact on the amount of DC current that an output pin can source or sink. Determine if the current strength setting is sufficient for the external resistive load condition on the output pin.

# **Clock Pins Functionality**

Cyclone IV clock pins have multiple purposes, as per listed:

- CLK pins—Input support for single-ended and voltage-referenced standards. For I/O standard support, refer to Table 6–3 on page 6–11.

- DIFFCLK pins—Input support for differential standards. For I/O standard support, refer to Table 6–3 on page 6–11. When used as DIFFCLK pins, DC or AC coupling can be used depending on the interface requirements and external termination is required. For more information, refer to "High-Speed I/O Standards Support" on page 6–28.

- REFCLK pins—Input support for high speed differential reference clocks used by the transceivers in Cyclone IV GX devices. For I/O support, coupling, and termination requirements, refer to Table 6–10 on page 6–29.

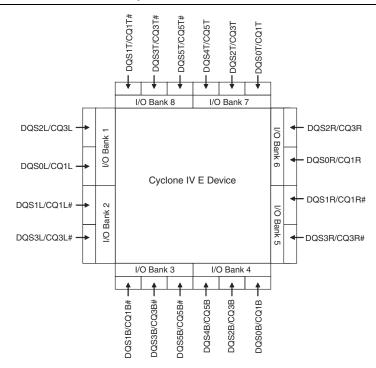

Figure 7–5 shows the location and numbering of the DQS, DQ, or CQ# pins in the Cyclone IV E device I/O banks.

Figure 7–5. DQS, CQ, or CQ# Pins in Cyclone IV E I/O Banks (1)

### Note to Figure 7-5:

(1) The DQS, CQ, or CQ# pin locations in this diagram apply to all packages in Cyclone IV E devices except devices in 144-pin EQFP.

There are no series resistors required in AP configuration mode for Cyclone IV E devices when using the Micron flash at 2.5-, 3.0-, and 3.3-V I/O standard. The output buffer of the Micron P30 IBIS model does not overshoot above 4.1 V. Thus, series resistors are not required for the 2.5-, 3.0-, and 3.3-V AP configuration option. However, if there are any other devices sharing the same flash I/Os with Cyclone IV E devices, all shared pins are still subject to the 4.1-V limit and may require series resistors.

Default read mode of the supported parallel flash memory and all writes to the parallel flash memory are asynchronous. Both the parallel flash families support a synchronous read mode, with data supplied on the positive edge of DCLK.

The serial clock (DCLK) generated by Cyclone IV E devices controls the entire configuration cycle and provides timing for the parallel interface.

### **Multi-Device AP Configuration**

You can configure multiple Cyclone IV E devices using a single parallel flash. You can cascade multiple Cyclone IV E devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to GND. You must connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO signal high to its  $V_{\text{CCIO}}$  level to help the internal weak pull-up resistor. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in the chain is a Cyclone IV E device. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, DATA [15..8], and DATA [7..0] pins of each device in the chain are connected (Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27).

The first Cyclone IV E device in the chain, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27, is the configuration master device and controls the configuration of the entire chain. You must connect its MSEL pins to select the AP configuration scheme. The remaining Cyclone IV E devices are used as configuration slaves. You must connect their MSEL pins to select the FPP configuration scheme. Any other Altera device that supports FPP configuration can also be part of the chain as a configuration slave.

The following are the configurations for the DATA [15..0] bus in a multi-device AP configuration:

- Byte-wide multi-device AP configuration

- Word-wide multi-device AP configuration

The programming hardware or download cable then places the configuration data one bit at a time on the DATA [0] pin of the device. The configuration data is clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor for the device to initialize.

When you use a download cable, setting the **Auto-restart configuration after error** option does not affect the configuration cycle because you must manually restart configuration in the Quartus II software if an error occurs. Additionally, the **Enable user-supplied start-up clock (CLKUSR)** option has no effect on device initialization, because this option is disabled in the **.sof** when programming the device with the Quartus II Programmer and download cable. Therefore, if you turn on the **CLKUSR** option, you do not have to provide a clock on CLKUSR when you configure the device with the Quartus II Programmer and a download cable.

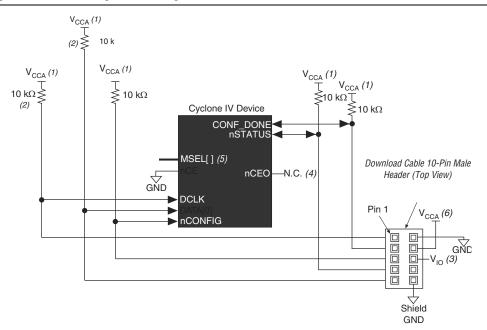

Figure 8–17 shows PS configuration for Cyclone IV devices with a download cable.

Figure 8-17. PS Configuration Using a Download Cable

### Notes to Figure 8-17:

- (1) You must connect the pull-up resistor to the same supply voltage as the  $V_{CCA}$  supply.

- (2) The pull-up resistors on DATA[0] and DCLK are only required if the download cable is the only configuration scheme used on your board. This is to ensure that DATA[0] and DCLK are not left floating after configuration. For example, if you also use a configuration device, the pull-up resistors on DATA[0] and DCLK are not required.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. With the USB-Blaster, ByteBlaster II, ByteBlaster MV, and EthernetBlaster, this pin is a no connect.

- (4) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (5) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9 for PS configuration schemes. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (6) Power up the V<sub>CC</sub> of the ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from V<sub>CCA</sub>. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

Figure 8-28. Combining JTAG and AS Configuration Schemes

### Notes to Figure 8-28:

Download Cable (AS Mode)

10-Pin Male Header

(1) Connect these pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

GND

(2) Power up the  $V_{CC}$  of the EthernetBlaster, ByteBlaster II, or USB-Blaster cable with the 3.3-V supply.

**GND**

10 pf

**GND**

(6)

(3) Pin 6 of the header is a  $V_{10}$  reference voltage for the MasterBlaster output driver. The  $V_{10}$  must match the  $V_{CCA}$  of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. When using the ByteBlasterMV download cable, this pin is a no connect. When using the USB-Blaster and ByteBlaster II cables, this pin is connected to nce when it is used for AS programming, otherwise it is a no connect.

10 pf

GND

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL for AS configuration schemes, refer to Table 8-3 on page 8-8, Table 8-4 on page 8-8, and Table 8-5 on page 8-9. Connect the MSEL pins directly to  $V_{\text{CCA}}$  or GND.

- (5) Power up the  $V_{CC}$  of the EthernetBlaster, ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V  $V_{CCA}$  supply. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a  $V_{CC}$  power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

- (6) You must place the diodes and capacitors as close as possible to the Cyclone IV device. Altera recommends using the Schottky diode, which has a relatively lower forward diode voltage (VF) than the switching and Zener diodes, for effective voltage clamping.

- (7) These pins are dual-purpose I/O pins. The noso pin functions as FLASH note pin in AP mode. The ASDO pin functions as DATA[1] pin in AP and FPP modes.

- (8) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ ..

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCT<sub>1</sub>K

# **Remote System Upgrade Mode**

In remote update mode, Cyclone IV devices load the factory configuration image after power up. The user-defined factory configuration determines the application configuration to be loaded and triggers a reconfiguration cycle. The factory configuration can also contain application logic.

When used with configuration memory, the remote update mode allows an application configuration to start at any flash sector boundary. Additionally, the remote update mode features a user watchdog timer that can detect functional errors in an application configuration.

# **Remote Update Mode**

In AS configuration scheme, when a Cyclone IV device is first powered up in remote update, it loads the factory configuration located at address

boot\_address [23:0] = 24b'0. Altera recommends storing the factory configuration image for your system at boot address 24b'0, which corresponds to the start address location 0×000000 in the serial configuration device. A factory configuration image is a bitstream for the Cyclone IV device in your system that is programmed during production and is the fall-back image when an error occurs. This image is stored in non-volatile memory and is never updated or modified using remote access.

When you use the AP configuration in Cyclone IV E devices, the Cyclone IV E device loads the default factory configuration located at the following address after device power-up in remote update mode:

boot address[23:0] = 24'h010000 = 24'b1 0000 0000 0000 0000.

You can change the default factory configuration address to any desired address using the APFC\_BOOT\_ADDR JTAG instruction. The factory configuration image is stored in non-volatile memory and is never updated or modified using remote access. This corresponds to the default start address location 0×010000 represented in 16-bit word addressing (or the updated address if the default address is changed) in the supported parallel flash memory. For more information about the application of the APFC\_BOOT\_ADDR JTAG instruction in AP configuration scheme, refer to the "JTAG Instructions" on page 8–57.

The factory configuration image is user-designed and contains soft logic (Nios II processor or state machine and the remote communication interface) to:

- Process any errors based on status information from the dedicated remote system upgrade circuitry

- Communicate with the remote host and receive new application configurations and store the new configuration data in the local non-volatile memory device

- Determine the application configuration to be loaded into the Cyclone IV device

- Enable or disable the user watchdog timer and load its time-out value (optional)

- Instruct the dedicated remote system upgrade circuitry to start a reconfiguration cycle

May 2013 Altera Corporation

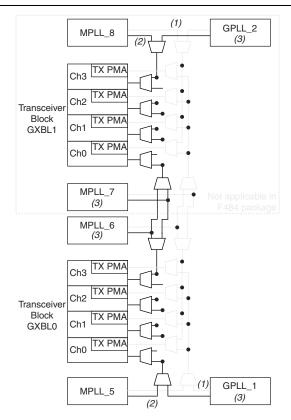

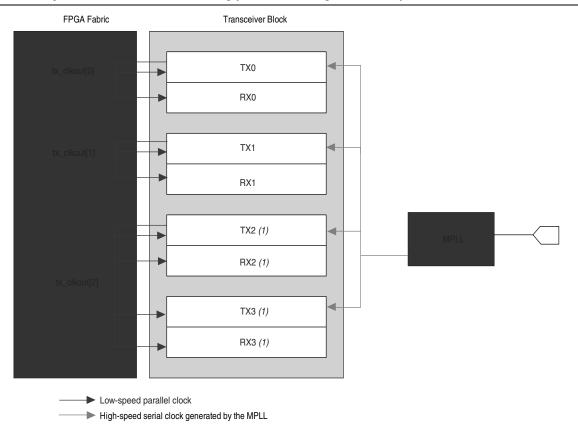

F484 and larger MPLL\_8 GPLL\_2 packages Channel 3 Channel 2 Transceiver Block GXBL1 Channel 1 Channel 0 MPLL\_7 MPLL\_6 Channel 3 PCIe Channel 2 hard IP Transceiver Block GXBL0 Channel 1 Channel 0 Calibration Block MPLL\_5 GPLL\_1

Figure 1–2. F484 and Larger Packages with Transceiver Channels for Cyclone IV GX Devices

For more information about the transceiver architecture, refer to the following sections:

- "Architectural Overview" on page 1–4

- "Transmitter Channel Datapath" on page 1–5

- "Receiver Channel Datapath" on page 1–11

- "Transceiver Clocking Architecture" on page 1–26

- "Transceiver Channel Datapath Clocking" on page 1–29

- "FPGA Fabric-Transceiver Interface Clocking" on page 1–43

- "Calibration Block" on page 1–45

- "PCI-Express Hard IP Block" on page 1–46

Figure 1–32. Clock Distribution in Non-Bonded Channel Configuration for Transceivers in F484 and Larger Packages

### Notes to Figure 1–32:

- (1) High-speed clock.

- (2) Low-speed clock.

- (3) These PLLs have restricted clock driving capability and may not reach all connected channels. For details, refer to Table 1–9.

The transceiver datapath clocking varies in non-bonded channel configuration depending on the PCS configuration.

Figure 1–33 shows the datapath clocking in transmitter only operation. In this mode, each channel selects the high- and low-speed clock from one of the supported PLLs. The high-speed clock feeds to the serializer for parallel to serial operation. The low-speed clock feeds to the following blocks in the transmitter PCS:

- 8B/10B encoder

- read clock of the byte serializer

- read clock of the TX phase compensation FIFO

Table 1-11. FPGA Fabric-Transceiver Interface Clocks (Part 2 of 2)

| Clock Name      | Clock Description                   | Interface Direction        |  |  |  |

|-----------------|-------------------------------------|----------------------------|--|--|--|

| cal_blk_clk (2) | Transceiver calibration block clock | FPGA fabric to transceiver |  |  |  |

#### Notes to Table 1-11:

- (1) Offset cancellation process that is executed after power cycle requires reconfig\_clk clock. The reconfig\_clk must be driven with a free-running clock and not derived from the transceiver blocks.

- (2) For the supported clock frequency range, refer to the Cyclone IV Device Data Sheet.

In the transmitter datapath, TX phase compensation FIFO forms the FPGA fabric-transmitter interface. Data and control signals for the transmitter are clocked with the FIFO write clock. The FIFO write clock supports automatic clock selection by the Quartus II software (depending on channel configuration), or user-specified clock from tx\_coreclk port. Table 1–12 details the automatic TX phase compensation FIFO write clock selection by the Quartus II software.

The Quartus II software assumes automatic clock selection for TX phase compensation FIFO write clock if you do not enable the tx\_coreclk port.

Table 1–12. Automatic TX Phase Compensation FIFO Write Clock Selection

| Channel<br>Configuration | Quartus II Selection                                                                                                                                                                     |  |  |  |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Non-bonded               | tx_clkout clock feeds the FIFO write clock. tx_clkout is forwarded through the transmitter channel from low-speed clock, which also feeds the FIFO read clock.                           |  |  |  |  |  |  |

| Bonded                   | coreclkout clock feeds the FIFO write clock for the bonded channels. coreclkout clock is the common bonded low-speed clock, which also feeds the FIFO read clock in the bonded channels. |  |  |  |  |  |  |

When using user-specified clock option, ensure that the clock feeding tx\_coreclk port has 0 ppm difference with the TX phase compensation FIFO read clock.

In the receiver datapath, RX phase compensation FIFO forms the receiver-FPGA fabric interface. Data and status signals from the receiver are clocked with the FIFO read clock. The FIFO read clock supports automatic clock selection by the Quartus II software (depending on channel configuration), or user-specified clock from rx\_coreclk port. Table 1–13 details the automatic RX phase compensation FIFO read clock selection by the Quartus II software.

The Quartus II software assumes automatic clock selection for RX phase compensation FIFO read clock if you do not enable the rx coreclk port.

Table 1–13. Automatic RX Phase Compensation FIFO Read Clock Selection (Part 1 of 2)

| Chanı      | nel Configuration       | Quartus II Selection                                                                                                                                                            |  |  |  |  |  |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Non-bonded |                         | tx_clkout clock feeds the FIFO read clock. tx_clkout is forwarded through the receiver channel from low-speed clock, which also feeds the FIFO write clock and transmitter PCS. |  |  |  |  |  |

| Non-ponded | Without rate match FIFO | rx_clkout clock feeds the FIFO read clock. rx_clkout is forwarded through the receiver channel from low-speed recovered clock, which also feeds the FIFO write clock.           |  |  |  |  |  |

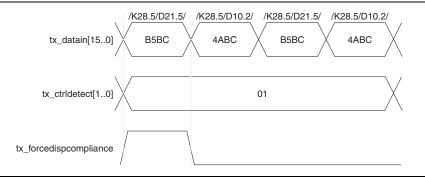

The compliance pattern is a repeating sequence of the four code groups: /K28.5/; /D21.5/; /K28.5/; /D10.2/. Figure 1–53 shows the compliance pattern transmission where the  $tx_forcedispcompliance$  port must be asserted in the same parallel clock cycle as /K28.5/D21.5/ of the compliance pattern on  $tx_datain[15..0]$  port.

Figure 1-53. Compliance Pattern Transmission Support in PCI Express (PIPE) Mode

# **Reset Requirement**

Cyclone IV GX devices meets the PCIe reset time requirement from device power up to the link active state with the configuration schemes listed in Table 1–17.

Table 1–18. Electrical Idle Inference Conditions

| Device       | Configuration Scheme        | <b>Configuration Time (ms)</b> |  |  |

|--------------|-----------------------------|--------------------------------|--|--|

| EP4CGX15     | Passive serial (PS)         | 51                             |  |  |

| EP4CGX22     | PS                          | 92                             |  |  |

| EP4CGX30 (1) | PS                          | 92                             |  |  |

| EP4CGX50     | Fast passive parallel (FPP) | 41                             |  |  |

| EP4CGX75     | FPP                         | 41                             |  |  |

| EP4CGX110    | FPP                         | 70                             |  |  |

| EP4CGX150    | FPP                         | 70                             |  |  |

### Note to Table 1-18:

# **GIGE Mode**

GIGE mode provides the transceiver channel datapath configuration for GbE (specifically the 1000 Base-X physical layer device (PHY) standard) protocol implementation. The Cyclone IV GX transceiver provides the PMA and the following PCS functions as defined in the IEEE 802.3 specification for 1000 Base-X PHY:

- 8B/10B encoding and decoding

- synchronization

If you enabled the auto-negotiation state machine in the FPGA core with the rate match FIFO, refer to "Clock Frequency Compensation" on page 1–63.

<sup>(1)</sup> EP4CGX30 device in F484 package fulfills the PCIe reset time requirement using FPP configuration scheme with configuration time of 41 ms.

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 1 of 3)

| Block  | Port Name                 | Input/<br>Output | Clock Domain                                                                                                                                                                                                | Description                                                                                                                                                                                                                                    |  |  |  |  |

|--------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | rx_syncstatus             | Output           | Synchronous to tx_clkout (non-bonded modes with rate match FIFO), rx_clkout (non-bonded modes without rate match FIFO), coreclkout (bonded modes), or rx_coreclk (when using the optional rx_coreclk input) | Word alignment synchronization status indicator. This signal passes through the RX Phase Compensation FIFO.  Not available in bit-slip mode                                                                                                    |  |  |  |  |

|        | rx_patternde<br>tect      | Output           | Synchronous to tx_clkout (non-bonded modes with rate match FIFO), rx_clkout (non-bonded modes without rate match FIFO), coreclkout (bonded modes), or rx_coreclk (when using the optional rx_coreclk input) | Indicates when the word alignment logic detects the alignment pattern in the current word boundary. This signal passes through the RX Phase Compensation FIFO.                                                                                 |  |  |  |  |

|        | rx_bitslip Input          |                  | Asynchronous signal. Minimum pulse width is two parallel clock cycles.                                                                                                                                      | Bit-slip control for the word aligner configured in bit-slip mode.  At every rising edge, word aligner slips one bit into the received data stream, effectively shifting the word boundary by one bit.                                         |  |  |  |  |

| RX PCS | rx_rlv                    | Output           | Asynchronous signal. Driven for a minimum of two recovered clock cycles in configurations without byte serializer and a minimum of three recovered clock cycles in configurations with byte serializer.     | Run-length violation indicator.  A high pulse indicates that the number of consecutive 1s or 0s in the received data stream exceeds the programmed run length violation threshold.                                                             |  |  |  |  |

|        | rx_invpolarity Input      |                  | Asynchronous signal. Minimum pulse width is two parallel clock cycles.                                                                                                                                      | Generic receiver polarity inversion control.  • A high level to invert the polarity of every bit of the 8-or 10-bit data to the word aligner.                                                                                                  |  |  |  |  |

|        | rx_enapattern<br>align    | Input            | Asynchronous signal.                                                                                                                                                                                        | Controls the word aligner operation configured in manual alignment mode.                                                                                                                                                                       |  |  |  |  |

|        | rx_rmfifodata<br>inserted | Output           | Synchronous to tx_clkout (non-bonded modes) or coreclkout (bonded modes)                                                                                                                                    | Rate match FIFO insertion status indicator.  • A high level indicates the rate match pattern byte is inserted to compensate for the ppm difference in the reference clock frequencies between the upstream transmitter and the local receiver. |  |  |  |  |

|        | rx_rmfifodata<br>deleted  | Output           | Synchronous to tx_clkout (non-bonded modes) or coreclkout (bonded modes)                                                                                                                                    | Rate match FIFO deletion status indicator.  • A high level indicates the rate match pattern byte is deleted to compensate for the ppm difference in the reference clock frequencies between the upstream transmitter and the local receiver.   |  |  |  |  |

The deassertion of the busy signal indicates proper completion of the offset cancellation process on the receiver channel.

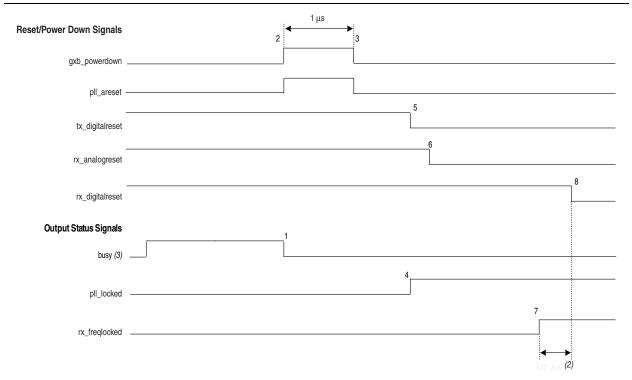

Figure 2–13. Sample Reset Sequence of a Receiver and Transmitter Channels-Receiver CDR in Automatic Lock Mode with the Optional gxb powerdown Signal <sup>(1)</sup>

#### Notes to Figure 2-13:

- (1) The gxb\_powerdown signal must not be asserted during the offset cancellation sequence.

- (2) For  $t_{LTD\_Auto}$  duration, refer to the <code>Cyclone IV Device Datasheet</code> chapter.

- (3) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

# **Simulation Requirements**

The following are simulation requirements:

- The gxb\_powerdown port is optional. In simulation, if the gxb\_powerdown port is not instantiated, you must assert the tx\_digitalreset, rx\_digitalreset, and rx analogreset signals appropriately for correct simulation behavior.

- If the gxb\_powerdown port is instantiated, and the other reset signals are not used, you must assert the gxb\_powerdown signal for at least 1 μs for correct simulation behavior.

- You can deassert the rx\_digitalreset signal immediately after the rx\_freqlocked signal goes high to reduce the simulation run time. It is not necessary to wait for t<sub>LTD\_Auto</sub> (as suggested in the actual reset sequence).

- The busy signal is deasserted after about 20 parallel reconfig\_clk clock cycles in order to reduce simulation run time. For silicon behavior in hardware, you can follow the reset sequences described in the previous pages.

### **Option 2: Use the Respective Channel Transmitter Core Clocks**

- Enable this option if you want the individual transmitter channel's tx\_clkout signal to provide the read clock to its respective Receive Phase Compensation FIFO.

- This option is typically enabled when all the transceiver channels have rate matching enabled with different data rates and are reconfigured to another Basic or Protocol functional mode with rate matching enabled.

Figure 3–14 shows the respective tx\_clkout of each channel clocking the respective channels of a transceiver block.

Figure 3-14. Option 2 for Receiver Core Clocking (Channel Reconfiguration Mode)

### Note to Figure 3-14:

(1) Assuming channel 2 and 3 are running at the same data rate with rate matcher enabled and are reconfigured to another Basic or Protocol functional mode with rate matching enabled.

| Visual Cue                               | Meaning                                                                                                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input. The suffix n denotes an active-low signal. For example, resetn.                 |

| Courier type                             | Indicates command line commands and anything that must be typed exactly as it appears. For example, c:\qdesigns\tutorial\chiptrip.gdf.                                                 |

|                                          | Also indicates sections of an actual file, such as a Report File, references to parts of files (for example, the AHDL keyword SUBDESIGN), and logic function names (for example, TRI). |

| +                                        | An angled arrow instructs you to press the Enter key.                                                                                                                                  |

| 1., 2., 3., and<br>a., b., c., and so on | Numbered steps indicate a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                          |

|                                          | Bullets indicate a list of items when the sequence of the items is not important.                                                                                                      |

|                                          | The hand points to information that requires special attention.                                                                                                                        |

| ?                                        | The question mark directs you to a software help system with related information.                                                                                                      |

| •••                                      | The feet direct you to another document or website with related information.                                                                                                           |

| <b>■</b>                                 | The multimedia icon directs you to a related multimedia presentation.                                                                                                                  |

| AUTION                                   | A caution calls attention to a condition or possible situation that can damage or destroy the product or your work.                                                                    |

| WARNING                                  | A warning calls attention to a condition or possible situation that can cause you injury.                                                                                              |

|                                          | The envelope links to the Email Subscription Management Center page of the Altera website, where you can sign up to receive update notifications for Altera documents.                 |

| Symbol                          | Modes | C   | 6   | C7, | , 17 | C8, | A7  | C8L, | I8L | C   | 9L  | Unit  |

|---------------------------------|-------|-----|-----|-----|------|-----|-----|------|-----|-----|-----|-------|

|                                 |       | Min | Max | Min | Max  | Min | Max | Min  | Max | Min | Max | Julit |

| t <sub>DUTY</sub>               | _     | 45  | 55  | 45  | 55   | 45  | 55  | 45   | 55  | 45  | 55  | %     |

| TCCS                            | _     | _   | 200 | _   | 200  | _   | 200 | _    | 200 | _   | 200 | ps    |

| Output jitter<br>(peak to peak) | _     | _   | 500 | _   | 500  | _   | 550 | _    | 600 | _   | 700 | ps    |

| t <sub>LOCK</sub> (2)           | _     | _   | 1   | _   | 1    | _   | 1   | _    | 1   | _   | 1   | ms    |

#### Notes to Table 1-35:

- (1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

- (2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

- (3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

| Symbol                    | Madaa | C6  |       | C7, I7 |       | C8, A7 |       | C8L, I8L |     | C9L |     |      |

|---------------------------|-------|-----|-------|--------|-------|--------|-------|----------|-----|-----|-----|------|

|                           | Modes | Min | Max   | Min    | Max   | Min    | Max   | Min      | Max | Min | Max | Unit |

|                           | ×10   | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                           | ×8    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

| f <sub>HSCLK</sub> (input | ×7    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

| clock<br>frequency)       | ×4    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                           | ×2    | 10  | 437.5 | 10     | 370   | 10     | 320   | 10       | 320 | 10  | 250 | MHz  |

|                           | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | MHz  |

|                           | ×10   | 100 | 875   | 100    | 740   | 100    | 640   | 100      | 640 | 100 | 500 | Mbps |

|                           | ×8    | 80  | 875   | 80     | 740   | 80     | 640   | 80       | 640 | 80  | 500 | Mbps |

| HSIODR                    | ×7    | 70  | 875   | 70     | 740   | 70     | 640   | 70       | 640 | 70  | 500 | Mbps |

| חשטוטוו                   | ×4    | 40  | 875   | 40     | 740   | 40     | 640   | 40       | 640 | 40  | 500 | Mbps |

|                           | ×2    | 20  | 875   | 20     | 740   | 20     | 640   | 20       | 640 | 20  | 500 | Mbps |

|                           | ×1    | 10  | 437.5 | 10     | 402.5 | 10     | 402.5 | 10       | 362 | 10  | 265 | Mbps |

| SW                        | _     | _   | 400   | _      | 400   | _      | 400   | _        | 550 | _   | 640 | ps   |

| Input jitter<br>tolerance | _     | _   | 500   | _      | 500   | _      | 550   | _        | 600 | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)     | _     | _   | 1     | _      | 1     | _      | 1     | _        | 1   | _   | 1   | ms   |

### Notes to Table 1-36:

- Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

- (2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

- (3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

# **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.