Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 7155                                                      |

| Number of Logic Elements/Cells | 114480                                                    |

| Total RAM Bits                 | 3981312                                                   |

| Number of I/O                  | 528                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 780-BGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29c9l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Reference and Ordering Information**

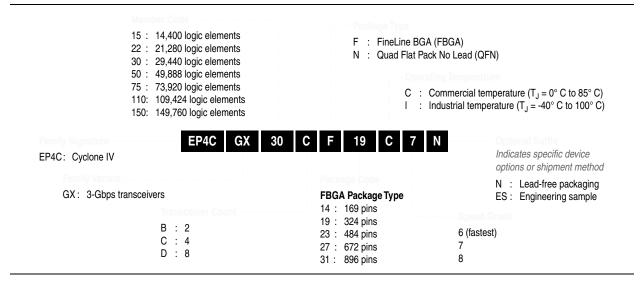

Figure 1–2 shows the ordering codes for Cyclone IV GX devices.

Figure 1–2. Packaging Ordering Information for the Cyclone IV GX Device

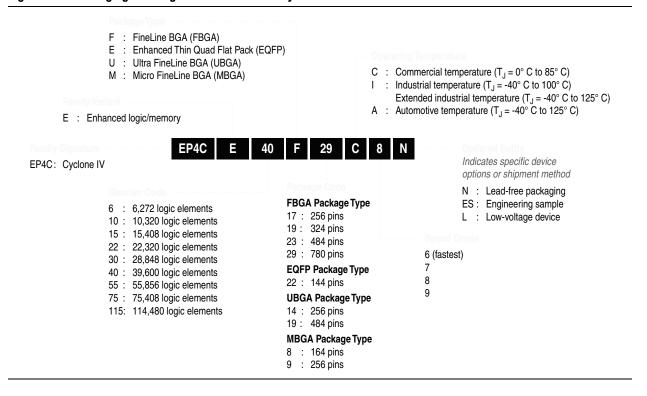

Figure 1–3 shows the ordering codes for Cyclone IV E devices.

Figure 1–3. Packaging Ordering Information for the Cyclone IV E Device

If you do not use dedicated clock pins to feed the GCLKs, you can use them as general-purpose input pins to feed the logic array. However, when using them as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

For more information about how to connect the clock and PLL pins, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

## **Clock Control Block**

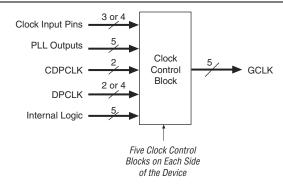

The clock control block drives the GCLKs. Clock control blocks are located on each side of the device, close to the dedicated clock input pins. GCLKs are optimized for minimum clock skew and delay.

Table 5–4 lists the sources that can feed the clock control block, which in turn feeds the GCLKs.

| Input                                           | Description                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedicated clock inputs                          | Dedicated clock input pins can drive clocks or global signals, such as synchronous and asynchronous clears, presets, or clock enables onto given GCLKs.                                                                                                                                             |

| Dual-purpose clock (DPCLK and CDPCLK) I/O input | DPCLK and CDPCLK I/O pins are bidirectional dual function pins that are used for high fan-out control signals, such as protocol signals, TRDY and IRDY signals for PCI, via the GCLK. Clock control blocks that have inputs driven by dual-purpose clock I/O pins are not able to drive PLL inputs. |

| PLL outputs                                     | PLL counter outputs can drive the GCLK.                                                                                                                                                                                                                                                             |

| Internal logic                                  | You can drive the GCLK through logic array routing to enable internal logic elements (LEs) to drive a high fan-out, low-skew signal path. Clock control blocks that have inputs driven by internal logic are not able to drive PLL inputs.                                                          |

Table 5-4. Clock Control Block Inputs

In Cyclone IV devices, dedicated clock input pins, PLL counter outputs, dual-purpose clock I/O inputs, and internal logic can all feed the clock control block for each GCLK. The output from the clock control block in turn feeds the corresponding GCLK. The GCLK can drive the PLL input if the clock control block inputs are outputs of another PLL or dedicated clock input pins. There are five or six clock control blocks on each side of the device periphery—depending on device density; providing up to 30 clock control blocks in each Cyclone IV GX device. The maximum number of clock control blocks per Cyclone IV E device is 20. For the clock control block locations, refer to Figure 5–2 on page 5–12, Figure 5–3 on page 5–13, and Figure 5–4 on page 5–14.

The clock control blocks on the left side of the Cyclone IV GX device do not support any clock inputs.

The control block has two functions:

- Dynamic GCLK clock source selection (not applicable for DPCLK, CDPCLK, and internal logic input)

- GCLK network power down (dynamic enable and disable)

Figure 5–6 shows a simplified version of the five clock control blocks on each side of the Cyclone IV E device periphery.

Figure 5–6. Clock Control Blocks on Each Side of Cyclone IV E Device (1)

#### Note to Figure 5-6:

(1) The left and right sides of the device have two DPCLK pins; the top and bottom of the device have four DPCLK pins.

## **GCLK Network Power Down**

You can disable a Cyclone IV device's GCLK (power down) using both static and dynamic approaches. In the static approach, configuration bits are set in the configuration file generated by the Quartus II software, which automatically disables unused GCLKs. The dynamic clock enable or disable feature allows internal logic to control clock enable or disable the GCLKs in Cyclone IV devices.

When a clock network is disabled, all the logic fed by the clock network is in an off-state, thereby reducing the overall power consumption of the device. This function is independent of the PLL and is applied directly on the clock network, as shown in Figure 5–1 on page 5–11.

You can set the input clock sources and the clkena signals for the GCLK multiplexers through the Quartus II software using the ALTCLKCTRL megafunction.

For more information, refer to the *ALTCLKCTRL Megafunction User Guide*.

## clkena Signals

Cyclone IV devices support clkena signals at the GCLK network level. This allows you to gate-off the clock even when a PLL is used. Upon re-enabling the output clock, the PLL does not need a resynchronization or re-lock period because the circuit gates off the clock at the clock network level. In addition, the PLL can remain locked independent of the clkena signals because the loop-related counters are not affected.

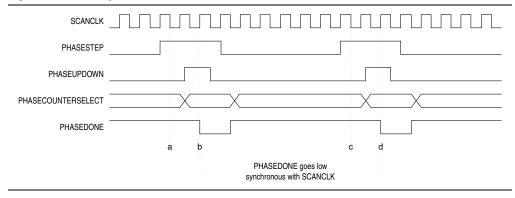

Figure 5–26 shows the dynamic phase shifting waveform.

The PHASESTEP signal is latched on the negative edge of SCANCLK (a,c) and must remain asserted for at least two SCANCLK cycles. Deassert PHASESTEP after PHASEDONE goes low. On the second SCANCLK rising edge (b,d) after PHASESTEP is latched, the values of PHASEUPDOWN and PHASECOUNTERSELECT are latched and the PLL starts dynamic phase-shifting for the specified counters, and in the indicated direction. PHASEDONE is deasserted synchronous to SCANCLK at the second rising edge (b,d) and remains low until the PLL finishes dynamic phase-shifting. Depending on the VCO and SCANCLK frequencies, PHASEDONE low time may be greater than or less than one SCANCLK cycle.

You can perform another dynamic phase-shift after the PHASEDONE signal goes from low to high. Each PHASESTEP pulse enables one phase shift. PHASESTEP pulses must be at least one SCANCLK cycle apart.

For information about the ALTPLL\_RECONFIG MegaWizard™ Plug-In Manager, refer to the ALTPLL\_RECONFIG Megafunction User Guide.

## **Spread-Spectrum Clocking**

Cyclone IV devices can accept a spread-spectrum input with typical modulation frequencies. However, the device cannot automatically detect that the input is a spread-spectrum signal. Instead, the input signal looks like deterministic jitter at the input of the PLL. PLLs of Cyclone IV devices can track a spread-spectrum input clock as long as it is in the input jitter tolerance specifications and the modulation frequency of the input clock is below the PLL bandwidth, that is specified in the fitter report. Cyclone IV devices cannot generate spread-spectrum signals internally.

## **PLL Specifications**

For information about PLL specifications, refer to the *Cyclone IV Device Datasheet* chapter.

The IOE registers in each I/O block share the same source for the preset or clear features. You can program preset or clear for each individual IOE, but you cannot use both features simultaneously. You can also program the registers to power-up high or low after configuration is complete. If programmed to power-up low, an asynchronous clear can control the registers. If programmed to power-up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of the active-low input of another device upon power-up. If one register in an IOE uses a preset or clear signal, all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

For more information about the input and output pin delay settings, refer to the *Area* and *Timing Optimization* chapter in volume 2 of the *Quartus II Handbook*.

## **PCI-Clamp Diode**

Cyclone IV devices provide an optional PCI-clamp diode enabled input and output for each I/O pin. Dual-purpose configuration pins support the diode in user mode if the specific pins are not used as configuration pins for the selected configuration scheme. For example, if you are using the active serial (AS) configuration scheme, you cannot use the clamp diode on the ASDO and nCSO pins in user mode. Dedicated configuration pins do not support the on-chip diode.

The PCI-clamp diode is available for the following I/O standards:

- 3.3-V LVTTL

- 3.3-V LVCMOS

- 3.0-V LVTTL

- 3.0-V LVCMOS

- 2.5-V LVTTL/LVCMOS

- PCI

- PCI-X

If the input I/O standard is one of the listed standards, the PCI-clamp diode is enabled by default in the Quartus II software.

## **OCT Support**

Cyclone IV devices feature OCT to provide I/O impedance matching and termination capabilities. OCT helps prevent reflections and maintain signal integrity while minimizing the need for external resistors in high pin-count ball grid array (BGA) packages. Cyclone IV devices provide I/O driver on-chip impedance matching and  $R_S$  OCT for single-ended outputs and bidirectional pins.

When using R<sub>S</sub> OCT, programmable current strength is not available.

There are two ways to implement OCT in Cyclone IV devices:

- OCT with calibration

- OCT without calibration

Figure 6–3 shows the external calibration resistors setup on the RUP and RDN pins and the associated OCT calibration circuitry.

Cyclone IV Device Family OCT with Calibration with RUP and RDN pins

External Calibration Resistor

OCT Calibration Circuitry

VCCIO

External Calibration Resistor

External Calibration Resistor

Figure 6-3. Cyclone IV Devices R<sub>S</sub> OCT with Calibration Setup

RUP and RDN pins go to a tri-state condition when calibration is completed or not running. These two pins are dual-purpose I/Os and function as regular I/Os if you do not use the calibration circuit.

## **On-Chip Series Termination Without Calibration**

Cyclone IV devices support driver impedance matching to match the impedance of the transmission line, which is typically 25 or 50  $\Omega$ . When used with the output drivers, OCT sets the output driver impedance to 25 or 50  $\Omega$ . Cyclone IV devices also support I/O driver series termination ( $R_S = 50 \Omega$ ) for SSTL-2 and SSTL-18.

Figure 6–16. RSDS, Mini-LVDS, or PPDS Interface with External Resistor Network on the Top and Bottom I/O Banks  $^{(1)}$

#### Note to Figure 6-16:

(1) R<sub>S</sub> and R<sub>P</sub> values are pending characterization.

A resistor network is required to attenuate the output voltage swing to meet RSDS, mini-LVDS, and PPDS specifications when using emulated transmitters. You can modify the resistor network values to reduce power or improve the noise margin.

The resistor values chosen must satisfy Equation 6–1.

## Equation 6-1. Resistor Network

$$\frac{R_S \times \frac{R_P}{2}}{R_S + \frac{R_P}{2}} = 50 \Omega$$

Altera recommends that you perform simulations using Cyclone IV devices IBIS models to validate that custom resistor values meet the RSDS, mini-LVDS, or PPDS requirements.

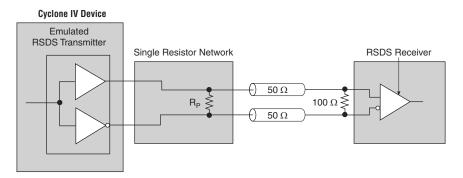

It is possible to use a single external resistor instead of using three resistors in the resistor network for an RSDS interface, as shown in Figure 6–17. The external single-resistor solution reduces the external resistor count while still achieving the required signaling level for RSDS. However, the performance of the single-resistor solution is lower than the performance with the three-resistor network.

Figure 6–17 shows the RSDS interface with a single resistor network on the top and bottom I/O banks.

Figure 6–17. RSDS Interface with Single Resistor Network on the Top and Bottom I/O Banks (1)

#### Note to Figure 6-17:

(1) R<sub>P</sub> value is pending characterization.

**Device** Data Size (bits) EP4CGX15 3,805,568 EP4CGX22 7,600,040 7,600,040 EP4CGX30 22,010,888 (1) Cyclone IV GX 22,010,888 EP4CGX50 EP4CGX75 22,010,888 39,425,016 EP4CGX110 EP4CGX150 39,425,016

Table 8–2. Uncompressed Raw Binary File (.rbf) Sizes for Cyclone IV Devices (Part 2 of 2)

## Note to Table 8-2:

(1) Only for the F484 package.

Use the data in Table 8–2 to estimate the file size before design compilation. Different configuration file formats, such as Hexadecimal (.hex) or Tabular Text File (.ttf) formats, have different file sizes. However, for any specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you use compression, the file size varies after each compilation, because the compression ratio depends on the design.

For more information about setting device configuration options or creating configuration files, refer to the *Software Settings* section in volume 2 of the *Configuration Handbook*.

## **Configuration and JTAG Pin I/O Requirements**

Cyclone IV devices are manufactured using the TSMC 60-nm low-k dielectric process. Although Cyclone IV devices use TSMC 2.5-V transistor technology in the I/O buffers, the devices are compatible and able to interface with 2.5, 3.0, and 3.3-V configuration voltage standards by following specific requirements.

All I/O inputs must maintain a maximum AC voltage of 4.1 V. When using a serial configuration device in an AS configuration scheme, you must connect a 25- $\Omega$  series resistor for the DATA [0] pin. When cascading the Cyclone IV device family in a multi-device configuration for AS, AP, FPP, and PS configuration schemes, you must connect the repeater buffers between the master and slave devices for the DATA and DCLK pins. When using the JTAG configuration scheme in a multi-device configuration, connect 25- $\Omega$  resistors on both ends of the TDO-TDI path if the TDO output driver is a non-Cyclone IV device.

The output resistance of the repeater buffers and the TDO path for all cases must fit the maximum overshoot equation shown in Equation 8–1.

#### **Equation 8–1.** (1)

$$0.8Z_{O} \le R_{E} \le 1.8Z_{O}$$

#### Note to Equation 8-1:

(1)  $Z_0$  is the transmission line impedance and  $R_E$  is the equivalent resistance of the output buffer.

Table 8–8 provides the configuration time for AS configuration.

Table 8–8. AS Configuration Time for Cyclone IV Devices (1)

| Symbol          | Parameter            | Cyclone IV E | Cyclone IV GX | Unit |

|-----------------|----------------------|--------------|---------------|------|

| t <sub>SU</sub> | Setup time           | 10           | 8             | ns   |

| t <sub>H</sub>  | Hold time            | 0            | 0             | ns   |

| t <sub>co</sub> | Clock-to-output time | 4            | 4             | ns   |

#### Note to Table 8-8:

(1) For the AS configuration timing diagram, refer to the Serial Configuration (EPCS) Devices Datasheet.

Enabling compression reduces the amount of configuration data that is sent to the Cyclone IV device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

## **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash memory-based devices. You can program these devices in-system with the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cables. Alternatively, you can program them with the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices through the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone IV devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive  $\rm V_{CC}$  and GND, respectively.

To perform in-system programming of a serial configuration device through the AS programming interface, you must place the diodes and capacitors as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V (Figure 8–6).

If you want to use the setup shown in Figure 8–6 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not require a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

For more information about implementing the SFL with Cyclone IV devices, refer to AN 370: Using the Serial FlashLoader with the Quartus II Software.

May 2013 Altera Corporation

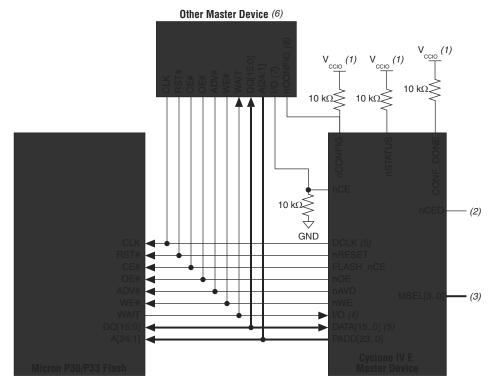

Figure 8–10 shows the AP configuration with multiple bus masters.

Figure 8-10. AP Configuration with Multiple Bus Masters

## Notes to Figure 8-10:

- (1) Connect the pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (5) When cascading Cyclone IV E devices in a multi-device AP configuration, connect the repeater buffers between the master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The other master device must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8-5.

- (7) The other master device can control the AP configuration bus by driving the nCE to high with an output high on the I/O pin.

- (8) The other master device can pulse nCONFIG if it is under system control and not tied to  $V_{CCIO}$ .

The default configuration boot address allows the system to use special parameter blocks in the flash memory map. Parameter blocks are at the top or bottom of the memory map. Figure 8–12 shows the configuration boot address in the AP configuration scheme. You can change the default configuration default boot address 0×010000 to any desired address using the APFC\_BOOT\_ADDR\_JTAG instruction. For more information about the APFC\_BOOT\_ADDR\_JTAG instruction, refer to "JTAG Instructions" on page 8–57.

**Bottom Parameter Flash Memory Top Parameter Flash Memory** Cyclone IV E Cyclone IV E Default Default Boot Boot Address Address x010000 (1) x010000 (1) x00FFFF x00FFFF x000000 x000000 bit[15] bit[0] bit[0] bit[15]

Figure 8-12. Configuration Boot Address in AP Flash Memory Map

Note to Figure 8-12:

(1) The default configuration boot address is x010000 when represented in 16-bit word addressing.

## **PS Configuration**

You can perform PS configuration on Cyclone IV devices with an external intelligent host, such as a MAX® II device, microprocessor with flash memory, or a download cable. In the PS scheme, an external host controls the configuration. Configuration data is clocked into the target Cyclone IV device through DATA[0] at each rising edge of DCLK.

If your system already contains a common flash interface (CFI) flash memory, you can use it for Cyclone IV device configuration storage as well. The MAX II PFL feature provides an efficient method to program CFI flash memory devices through the JTAG interface and the logic to control the configuration from the flash memory device to the Cyclone IV device.

Cyclone IV devices do not support enhanced configuration devices for PS configuration.

Minimum Maximum **Symbol Parameter** Unit Cyclone IV (1) Cyclone IV (1) Cyclone IV E (2) Cyclone IV E (2) nSTATUS high to 2 t<sub>ST2CK</sub> first rising edge of μs DCLK Data hold time after 0 ns  $t_{DH}$ rising edge on DCLK CONF DONE high to 300 650 t<sub>CD2UM</sub> μs user mode (5) CONF DONE high to 4 × maximum DCLK period  $t_{\text{CD2CU}} \\$ CLKUSR enabled CONF DONE high to t<sub>CD2UMC</sub> user mode with  $t_{CD2CU} + (3,192 \times CLKUSR period)$ **CLKUSR** option on Data setup time before rising edge 5 8 ns t<sub>DSU</sub> on DCLK  $t_{CH}$ DCLK high time 3.2 6.4 ns  $t_{\text{CL}}$ 3.2 6.4 DCLK low time ns DCLK period 7.5 15  $t_{CLK}$ ns

Table 8-13. FPP Timing Parameters for Cyclone IV Devices (Part 2 of 2)

## Notes to Table 8-13:

$f_{\text{MAX}}$

- (1) Applicable for Cyclone IV GX and Cyclone IV E with 1.2-V core voltage.

- (2) Applicable for Cyclone IV E with 1.0-V core voltage.

DCLK frequency (6)

- $(3) \quad \text{This value is applicable if you do not delay configuration by extending the $\tt nCONFIG$ or $\tt nSTATUS$ low pulse width.}$

- (4) This value is applicable if you do not delay configuration by externally holding the  ${\tt nSTATUS}$  low.

- (5) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.

- (6) Cyclone IV E devices with 1.0-V core voltage have slower F<sub>MAX</sub> when compared with Cyclone IV GX devices with 1.2-V core voltage.

## **JTAG Configuration**

JTAG has developed a specification for boundary-scan testing (BST). The BST architecture offers the capability to efficiently test components on PCBs with tight lead spacing. The BST architecture can test pin connections without using physical test probes and capture functional data while a device is normally operating. You can also use the JTAG circuitry to shift configuration data into the device. The Quartus II software automatically generates <code>.sof</code> for JTAG configuration with a download cable in the Quartus II software Programmer.

133

66

MHz

For more information about the JTAG boundary-scan testing, refer to the JTAG Boundary-Scan Testing for Cyclone IV Devices chapter.

May 2013 Altera Corporation

## **Programming Serial Configuration Devices In-System with the JTAG Interface**

Cyclone IV devices in a single- or multiple-device chain support in-system programming of a serial configuration device with the JTAG interface through the SFL design. The intelligent host or download cable of the board can use the four JTAG pins on the Cyclone IV device to program the serial configuration device in system, even if the host or download cable cannot access the configuration pins (DCLK, DATA, ASDI, and nCS pins).

The SFL design is a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses their JTAG interface to access the EPCS JTAG Indirect Configuration Device Programming (.jic) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

In a multiple device chain, you must only configure the master device that controls the serial configuration device. Slave devices in the multiple device chain that are configured by the serial configuration device do not have to be configured when using this feature. To successfully use this feature, set the MSEL pins of the master device to select the AS configuration scheme (Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9). The serial configuration device in-system programming through the Cyclone IV device JTAG interface has three stages, which are described in the following sections:

- "Loading the SFL Design"

- "ISP of the Configuration Device" on page 8–56

- "Reconfiguration" on page 8–57

## **Loading the SFL Design**

The SFL design is a design inside the Cyclone IV device that bridges the JTAG interface and AS interface with glue logic.

The intelligent host uses the JTAG interface to configure the master device with a SFL design. The SFL design allows the master device to control the access of four serial configuration device pins, also known as the Active Serial Memory Interface (ASMI) pins, through the JTAG interface. The ASMI pins are serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and active-low chip select (nCS) pins.

May 2013 Altera Corporation

# 11. Power Requirements for Cyclone IV Devices

## CYIV-51011-1.3

This chapter describes information about external power supply requirements, hot-socketing specifications, power-on reset (POR) requirements, and their implementation in Cyclone IV devices.

This chapter includes the following sections:

- "External Power Supply Requirements" on page 11–1

- "Hot-Socketing Specifications" on page 11–2

- "Hot-socketing Feature Implementation" on page 11–3

- "Power-On Reset Circuitry" on page 11–3

## **External Power Supply Requirements**

This section describes the different external power supplies required to power Cyclone IV devices. Table 11–1 and Table 11–2 list the descriptions of external power supply pins for Cyclone IV GX and Cyclone IV E devices, respectively.

- For each Altera recommended power supply's operating conditions, refer to the *Cyclone IV Device Datasheet* chapter.

- For power supply pin connection guidelines and power regulator sharing, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

Table 11–1. Power Supply Descriptions for the Cyclone IV GX Devices (Part 1 of 2)

| Power Supply Pin   | Nominal Voltage Level (V)    | Description                                                                                                 |  |

|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| VCCINT             | 1.2                          | Core voltage, PCI Express (PCIe) hard IP block, and transceiver physical coding sublayer (PCS) power supply |  |

| VCCA (1)           | 2.5                          | PLL analog power supply                                                                                     |  |

| VCCD_PLL           | 1.2                          | PLL digital power supply                                                                                    |  |

| VCCIO (2)          | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | I/O banks power supply                                                                                      |  |

| VCC_CLKIN (3), (4) | 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 | Differential clock input pins power supply                                                                  |  |

| VCCH_GXB           | 2.5                          | Transceiver output (TX) buffer power supply                                                                 |  |

| VCCA_GXB           | 2.5                          | Transceiver physical medium attachment (PMA) and auxiliary power supply                                     |  |

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

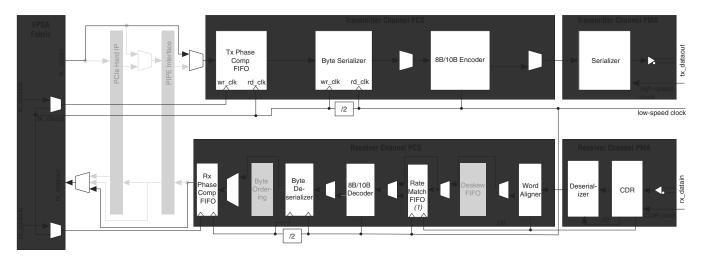

Figure 1–60 shows the transceiver channel datapath and clocking when configured in Serial RapidIO mode.

Figure 1-60. Transceiver Channel Datapath and Clocking when Configured in Serial RapidlO Mode

## Notes to Figure 1–60:

- (1) Optional rate match FIFO.

- (2) High-speed recovered clock.

- (3) Low-speed recovered clock.

The busy signal remains low for the first reconfig\_clk clock cycle. It then gets asserted from the second reconfig\_clk clock cycle. Subsequent deassertion of the busy signal indicates the completion of the offset cancellation process. This busy signal is required in transceiver reset sequences except for transmitter only channel configurations. Refer to the reset sequences shown in Figure 2–2 and the associated references listed in the notes for the figure.

Altera strongly recommends adhering to these reset sequences for proper operation of the Cyclone IV GX transceiver.

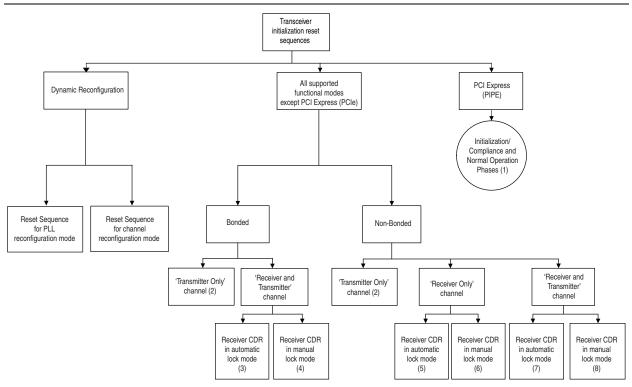

Figure 2–2 shows the transceiver reset sequences for Cyclone IV GX devices.

Figure 2–2. Transceiver Reset Sequences Chart

## Notes to Figure 2-2:

- (1) Refer to the Timing Diagram in Figure 2–10.

- (2) Refer to the Timing Diagram in Figure 2-3.

- (3) Refer to the Timing Diagram in Figure 2–4.

- (4) Refer to the Timing Diagram in Figure 2–5.

- (5) Refer to the Timing Diagram in Figure 2–6.

- (6) Refer to the Timing Diagram in Figure 2–7.

- (7) Refer to the Timing Diagram in Figure 2-8.

- (8) Refer to the Timing Diagram in Figure 2–9.

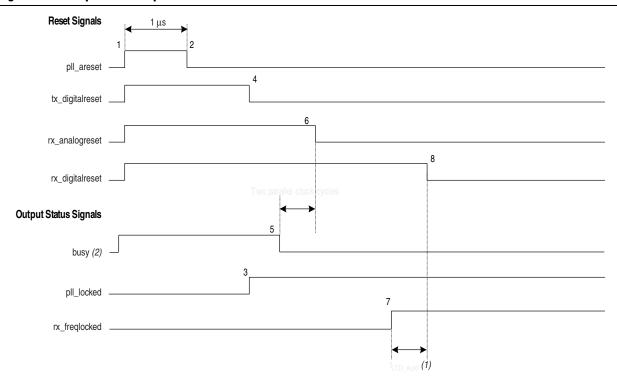

#### Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

This configuration contains both a transmitter and a receiver channel. If you create a **Receiver and Transmitter** instance in the ALTGX MegaWizard Plug-In Manager with the receiver CDR in automatic lock mode, use the reset sequence shown in Figure 2–8.

Figure 2–8. Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Automatic Lock Mode

#### Notes to Figure 2-8:

- (1) For t<sub>LTD Auto</sub> duration, refer to the *Cyclone IV Device Datasheet* chapter.

- (2) The busy signal is asserted and deasserted only during initial power up when offset cancellation occurs. In subsequent reset sequences, the busy signal is asserted and deasserted only if there is a read or write operation to the ALTGX\_RECONFIG megafunction.

As shown in Figure 2–8, perform the following reset procedure for the receiver in CDR automatic lock mode:

- 1. After power up, assert pl1\_areset for a minimum period of 1  $\mu$ s (the time between markers 1 and 2).

- 2. Keep the tx\_digitalreset, rx\_analogreset, and rx\_digitalreset signals asserted during this time period. After you deassert the pll\_areset signal, the multipurpose PLL starts locking to the transmitter input reference clock.

- 3. After the multipurpose PLL locks, as indicated by the pll\_locked signal going high (marker 3), deassert tx\_digitalreset. For receiver operation, after deassertion of busy signal, wait for two parallel clock cycles to deassert the rx analogreset signal.

- 4. Wait for the rx freqlocked signal to go high (marker 7).

- 5. After the  $rx\_freqlocked$  signal goes high, wait for at least  $t_{LTD\_Auto}$ , then deassert the  $rx\_digitalreset$  signal (marker 8). At this point, the transmitter and receiver are ready for data traffic.

As shown in Figure 2–12, perform the following reset procedure when using the dynamic reconfiguration controller to change the configuration of the transceiver channel:

- 1. After power up and establishing that the transceiver is operating as desired, write the desired new value in the appropriate registers (including reconfig\_mode\_sel[2:0]) and subsequently assert the write\_all signal (marker 1) to initiate the dynamic reconfiguration.

- For more information, refer to the *Cyclone IV Dynamic Reconfiguration* chapter.

- 2. Assert the  $tx\_digitalreset$ ,  $rx\_analogreset$ , and  $rx\_digitalreset$  signals.

- 3. As soon as write\_all is asserted, the dynamic reconfiguration controller starts to execute its operation. This is indicated by the assertion of the busy signal (marker 2).

- 4. Wait for the assertion of the channel\_reconfig\_done signal (marker 4) that indicates the completion of dynamic reconfiguration in this mode.

- 5. Deassert the tx\_digitalreset signal (marker 5). This signal must be deasserted after assertion of the channel\_reconfig\_done signal (marker 4) and before the deassertion of the rx\_analogreset signal (marker 6).

- 6. Wait for at least five parallel clock cycles after assertion of the channel\_reconfig\_done signal (marker 4) to deassert the rx\_analogreset signal (marker 6).

- 7. Lastly, wait for the rx\_freqlocked signal to go high. After rx\_freqlocked goes high (marker 7), wait for t<sub>LTD\_Auto</sub> to deassert the rx\_digitalreset signal (marker 8). At this point, the receiver is ready for data traffic.

## **Power Down**

The Quartus II software automatically selects the power-down channel feature, which takes effect when you configure the Cyclone IV GX device. All unused transceiver channels and blocks are powered down to reduce overall power consumption. The gxb\_powerdown signal is an optional transceiver block signal. It powers down all transceiver channels and all functional blocks in the transceiver block. The minimum pulse width for this signal is 1  $\mu$ s. After power up, if you use the gxb\_powerdown signal, wait for deassertion of the busy signal, then assert the gxb\_powerdown signal for a minimum of 1  $\mu$ s. Lastly, follow the sequence shown in Figure 2–13.

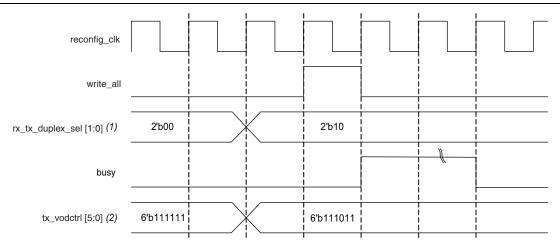

Figure 3–8 shows a write transaction waveform with the **Use the same control signal for all the channels** option disabled.

Figure 3-8. Write Transaction Waveform—Use the same control signal for all the channels Option Disabled

## Notes to Figure 3-8:

- (1) In this waveform example, you want to write to only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels controlled by the dynamic reconfiguration controller (the ALTGX\_RECONFIG instance) is two and that the tx vodctrl control port is enabled.

#### **Read Transaction**

The read transaction in Method 3 is identical to that in Method 2. Refer to "Read Transaction" on page 3–18.

This is the slowest method. You have to write all the PMA settings for all channels even if you may only be changing one parameter on the channel. Altera recommends using the <code>logical\_channel\_address</code> method for time-critical applications.

For each method, you can additionally reconfigure the PMA setting of both transmitter and receiver portion, transmitter portion only, or receiver portion only of the transceiver channel. For more information, refer to "Dynamic Reconfiguration Controller Port List" on page 3–4. You can enable the <code>rx\_tx\_duplex\_sel</code> port by selecting the <code>Use 'rx\_tx\_duplex\_sel'</code> port to enable RX only, TX only or duplex reconfiguration option on the <code>Error</code> checks tab of the ALTGX\_RECONFIG MegaWizard Plug-In Manager.

Figure 3–9 shows the ALTGX\_RECONFIG connection to the ALTGX instances when set in analog reconfiguration mode. For the port information, refer to the "Dynamic Reconfiguration Controller Port List" on page 3–4.

This chapter provides additional information about the document and Altera.

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Cyclone® IV family of devices.

## **How to Contact Altera**

To locate the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                    | Contact Method | Address                   |

|--------------------------------|----------------|---------------------------|

| Technical support              | Website        | www.altera.com/support    |

| Technical training             | Website        | www.altera.com/training   |

| 16011110ai trailling           | Email          | custrain@altera.com       |

| Product literature             | Website        | www.altera.com/literature |

| Nontechnical support (general) | Email          | nacomp@altera.com         |

| (software licensing)           | Email          | authorization@altera.com  |

## Note to Table:

# **Typographic Conventions**

The following table shows the typographic conventions this document uses.

| Visual Cue                                | Meaning                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial Capital<br>Letters | Indicate command names, dialog box titles, dialog box options, and other GUI labels. For example, <b>Save As</b> dialog box. For GUI elements, capitalization matches the GUI.                                              |

| bold type                                 | Indicates directory names, project names, disk drive names, file names, file name extensions, software utility names, and GUI labels. For example,   qdesigns directory, \textbf{D}: drive, and \textbf{chiptrip.gdf} file. |

| Italic Type with Initial Capital Letters  | Indicate document titles. For example, Stratix IV Design Guidelines.                                                                                                                                                        |

|                                           | Indicates variables. For example, $n + 1$ .                                                                                                                                                                                 |

| italic type                               | Variable names are enclosed in angle brackets (< >). For example, <file name=""> and <project name="">.pof file.</project></file>                                                                                           |

| Initial Capital Letters                   | Indicate keyboard keys and menu names. For example, the Delete key and the Options menu.                                                                                                                                    |

| "Subheading Title"                        | Quotation marks indicate references to sections in a document and titles of Quartus II Help topics. For example, "Typographic Conventions."                                                                                 |

<sup>(1)</sup> You can also contact your local Altera sales office or sales representative.