Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Active                                                   |

| Number of LABs/CLBs            | 7155                                                     |

| Number of Logic Elements/Cells | 114480                                                   |

| Total RAM Bits                 | 3981312                                                  |

| Number of I/O                  | 528                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 780-BGA                                                  |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29i7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1–4 lists Cyclone IV GX device package offerings, including I/O and transceiver counts.

Table 1–4. Package Offerings for the Cyclone IV GX Device Family (1)

| Package    |             |   | F169     |       | F324         |          |       |              | F484     |       |              | F672     |       | F896         |          |       |

|------------|-------------|---|----------|-------|--------------|----------|-------|--------------|----------|-------|--------------|----------|-------|--------------|----------|-------|

| Size (mm)  |             | 1 | 14 × 14  |       |              | 19 × 19  |       | 23 × 23      |          |       |              | 27 × 27  |       | 31 × 31      |          |       |

| Pitch (mm) |             |   | 1.0      |       |              | 1.0      |       |              | 1.0      |       |              | 1.0      |       | 1.0          |          |       |

| Device     | Ilser I/D   |   | LVDS (2) | XCVRs | User I/0     | LVDS (2) | XCVRs | User I/O     | (z) SQAT | XCVRs | User I/O     | LVDS (2) | XCVRs | User I/O     | (z) SQA1 | XCVRs |

| EP4CGX15   | <b>↑</b> 72 | 2 | 25       | 2     | _            | _        | _     | _            | _        | _     | _            | _        | _     | _            | _        | _     |

| EP4CGX22   | 7:          | 2 | 25       | 2     | <b>1</b> 50  | 64       | 4     | _            | _        | _     | _            | _        | _     | _            | _        | _     |

| EP4CGX30   | <b>▼</b> 75 | 2 | 25       | 2     | <b>▼</b> 150 | 64       | 4     | <b>▲</b> 290 | 130      | 4     | _            | _        | _     | _            | _        | _     |

| EP4CGX50   | _           | - | _        | _     | _            | _        | _     | 290          | 130      | 4     | <b>★</b> 310 | 140      | 8     | _            | _        | _     |

| EP4CGX75   | _           | - | _        | _     | _            | _        | _     | 290          | 130      | 4     | 310          | 140      | 8     | _            | _        | _     |

| EP4CGX110  | _           | - |          | _     |              | _        |       | 270          | 120      | 4     | 393          | 181      | 8     | <b>▲</b> 475 | 220      | 8     |

| EP4CGX150  | _           | - | _        | _     | _            | _        | _     | <b>▼</b> 270 | 120      | 4     | ▼393         | 181      | 8     | <b>▼</b> 475 | 220      | 8     |

#### Note to Table 1-4:

- (1) Use the Pin Migration View window in Pin Planner of the Quartus II software to verify the pin migration compatibility when you perform device migration. For more information, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

- (2) This includes both dedicated and emulated LVDS pairs. For more information, refer to the I/O Features in Cyclone IV Devices chapter.

### I/O Features

Cyclone IV device I/O supports programmable bus hold, programmable pull-up resistors, programmable delay, programmable drive strength, programmable slew-rate control to optimize signal integrity, and hot socketing. Cyclone IV devices support calibrated on-chip series termination (Rs OCT) or driver impedance matching (Rs) for single-ended I/O standards. In Cyclone IV GX devices, the high-speed transceiver I/Os are located on the left side of the device. The top, bottom, and right sides can implement general-purpose user I/Os.

Table 1–8 lists the I/O standards that Cyclone IV devices support.

Table 1-8. I/O Standards Support for the Cyclone IV Device Family

| Туре             | I/O Standard                                               |

|------------------|------------------------------------------------------------|

| Single-Ended I/O | LVTTL, LVCMOS, SSTL, HSTL, PCI, and PCI-X                  |

| Differential I/O | SSTL, HSTL, LVPECL, BLVDS, LVDS, mini-LVDS, RSDS, and PPDS |

The LVDS SERDES is implemented in the core of the device using logic elements.

For more information, refer to the *I/O Features in Cyclone IV Devices* chapter.

## **Clock Management**

Cyclone IV devices include up to 30 global clock (GCLK) networks and up to eight PLLs with five outputs per PLL to provide robust clock management and synthesis. You can dynamically reconfigure Cyclone IV device PLLs in user mode to change the clock frequency or phase.

Cyclone IV GX devices support two types of PLLs: multipurpose PLLs and general-purpose PLLs:

- Use multipurpose PLLs for clocking the transceiver blocks. You can also use them for general-purpose clocking when they are not used for transceiver clocking.

- Use general purpose PLLs for general-purpose applications in the fabric and periphery, such as external memory interfaces. Some of the general purpose PLLs can support transceiver clocking.

- For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

## **External Memory Interfaces**

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top, bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera® DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. Altera supplies the PHY IP and you can use it in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support the use of error correction coding (ECC) bits on DDR and DDR2 SDRAM interfaces.

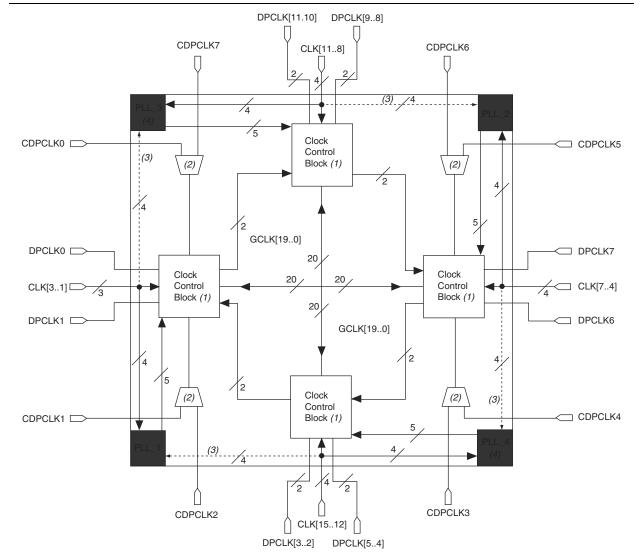

Figure 5-4. Clock Networks and Clock Control Block Locations in Cyclone IV E Devices

#### Notes to Figure 5-4:

- (1) There are five clock control blocks on each side.

- (2) Only one of the corner CDPCLK pins in each corner can feed the clock control block at a time. You can use the other CDPCLK pins as general-purpose I/O (GPIO) pins.

- (3) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

- (4) PLL\_3 and PLL\_4 are not available in EP4CE6 and EP4CE10 devices.

The inputs to the clock control blocks on each side of the Cyclone IV GX device must be chosen from among the following clock sources:

- Four clock input pins

- Ten PLL counter outputs (five from each adjacent PLLs)

- Two, four, or six DPCLK pins from the top, bottom, and right sides of the device

- Five signals from internal logic

- When using manual clock switchover, the difference between inclk0 and inclk1 can be more than 20%. However, differences between the two clock sources (frequency, phase, or both) can cause the PLL to lose lock. Resetting the PLL ensures that the correct phase relationships are maintained between the input and output clocks.

- Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start the manual clock switchover event. Failing to meet this requirement causes the clock switchover to malfunction.

- Applications that require a clock switchover feature and a small frequency drift must use a low-bandwidth PLL. When referencing input clock changes, the low-bandwidth PLL reacts slower than a high-bandwidth PLL. When the switchover happens, the low-bandwidth PLL propagates the stopping of the clock to the output slower than the high-bandwidth PLL. The low-bandwidth PLL filters out jitter on the reference clock. However, the low-bandwidth PLL also increases lock time.

- After a switchover occurs, there may be a finite resynchronization period for the PLL to lock onto a new clock. The exact amount of time it takes for the PLL to re-lock is dependent on the PLL configuration.

- If the phase relationship between the input clock to the PLL and output clock from the PLL is important in your design, assert areset for 10 ns after performing a clock switchover. Wait for the locked signal (or gated lock) to go high before re-enabling the output clocks from the PLL.

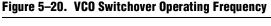

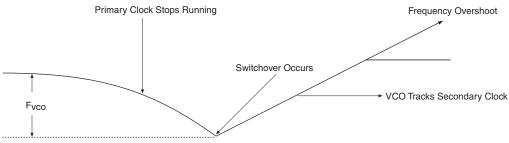

- Figure 5–20 shows how the VCO frequency gradually decreases when the primary clock is lost and then increases as the VCO locks on to the secondary clock. After the VCO locks on to the secondary clock, some overshoot can occur (an over-frequency condition) in the VCO frequency.

■ Disable the system during switchover if the system is not tolerant to frequency variations during the PLL resynchronization period. You can use the clkbad0 and clkbad1 status signals to turn off the PFD (pfdena = 0) so the VCO maintains its last frequency. You can also use the switchover state machine to switch over to the secondary clock. Upon enabling the PFD, output clock enable signals (clkena) can disable clock outputs during the switchover and resynchronization period. After the lock indication is stable, the system can re-enable the output clock or clocks.

Figure 5–21 shows an example of phase shift insertion using fine resolution through VCO phase taps method. The eight phases from the VCO are shown and labeled for reference. In this example, CLK0 is based on 0° phase from the VCO and has the C value for the counter set to one. The CLK1 signal is divided by four, two VCO clocks for high time and two VCO clocks for low time. CLK1 is based on the 135° phase tap from the VCO and has the C value for the counter set to one. The CLK1 signal is also divided by four. In this case, the two clocks are offset by 3  $\Phi_{\rm fine}$ . CLK2 is based on the 0° phase from the VCO but has the C value for the counter set to three. This creates a delay of two  $\Phi_{\rm coarse}$  (two complete VCO periods).

$1/8 t_{VCO} \rightarrow \qquad \qquad t_{VCO} \rightarrow \qquad t_{VCO} \rightarrow$

Figure 5-21. Delay Insertion Using VCO Phase Output and Counter Delay Time

You can use the coarse and fine phase shifts to implement clock delays in Cyclone IV devices.

Cyclone IV devices support dynamic phase shifting of VCO phase taps only. The phase shift is configurable for any number of times. Each phase shift takes about one scanclk cycle, allowing you to implement large phase shifts quickly.

## **PLL Cascading**

Cyclone IV devices allow cascading between general purpose PLLs and multipurpose PLLs in normal or direct mode through the GCLK network. If your design cascades PLLs, the source (upstream) PLL must have a low-bandwidth setting, while the destination (downstream) PLL must have a high-bandwidth setting.

PLL\_6 and PLL7 have upstream cascading capability only.

PLL cascading is not supported when used in transceiver applications.

Each Cyclone IV I/O bank has a VREF bus to accommodate voltage-referenced I/O standards. Each VREF pin is the reference source for its  $V_{REF}$  group. If you use a  $V_{REF}$  group for voltage-referenced I/O standards, connect the VREF pin for that group to the appropriate voltage level. If you do not use all the  $V_{REF}$  groups in the I/O bank for voltage-referenced I/O standards, you can use the VREF pin in the unused voltage-referenced groups as regular I/O pins. For example, if you have SSTL-2 Class I input pins in I/O bank 1 and they are all placed in the VREFB1N[0] group, VREFB1N[0] must be powered with 1.25 V, and the remaining VREFB1N[1..3] pins (if available) are used as I/O pins. If multiple  $V_{REF}$  groups are used in the same I/O bank, the VREF pins must all be powered by the same voltage level because the VREF pins are shorted together within the same I/O bank.

- When VREF pins are used as regular I/Os, they have higher pin capacitance than regular user I/O pins. This has an impact on the timing if the pins are used as inputs and outputs.

- For more information about VREF pin capacitance, refer to the pin capacitance section in the *Cyclone IV Device Datasheet* chapter.

- For information about how to identify V<sub>REF</sub> groups, refer to the Cyclone IV **Device Pin-Out** files or the **Quartus II Pin Planner** tool.

Table 6–4 and Table 6–5 summarize the number of VREF pins in each I/O bank for the Cyclone IV device family.

Table 6-4. Number of VREF Pins Per I/O Bank for Cyclone IV E Devices (Part 1 of 2)

| Device             |          | EP4CE6   |          |          | EP4CE10  |          |          |          | 7 P P P P P P P P P P P P P P P P P P P | Er46E13  |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | 27.0     | EP46E40  |          |          | EP4CE55  |          |          | EP4CE75  |          | ED 40 E11 E | Er46E113 |

|--------------------|----------|----------|----------|----------|----------|----------|----------|----------|-----------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------|----------|

| I/0<br>Bank<br>(1) | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA                                | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA    | 780-FBGA |

| 1                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 2                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 3                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 4                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 5                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 6                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

| 7                  | 1        | 1        | 1        | 1        | 1        | 1        | 2        | 2        | 2                                       | 2        | 2        | 2        | 1        | 1        | 1        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 2        | 2        | 2        | 3        | 3        | 3        | 3           | 3        |

## LVPECL I/O Support in Cyclone IV Devices

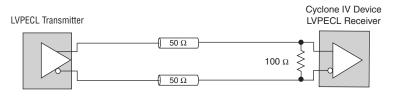

The LVPECL I/O standard is a differential interface standard that requires a 2.5-V  $V_{\text{CCIO.}}$  This standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. Cyclone IV devices support the LVPECL input standard at the dedicated clock input pins only. The LVPECL receiver requires an external  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer.

For the LVPECL I/O standard electrical specification, refer to the *Cyclone IV Device Datasheet* chapter.

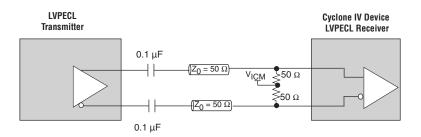

AC coupling is required when the LVPECL common mode voltage of the output buffer is higher than the Cyclone IV devices LVPECL input common mode voltage.

Figure 6–18 shows the AC-coupled termination scheme. The  $50-\Omega$  resistors used at the receiver are external to the device. DC-coupled LVPECL is supported if the LVPECL output common mode voltage is in the Cyclone IV devices LVPECL input buffer specification (refer to Figure 6–19).

Figure 6–18. LVPECL AC-Coupled Termination (1)

#### Note to Figure 6-18:

(1) The LVPECL AC-coupled termination is applicable only when an Altera FPGA transmitter is used.

Figure 6–19 shows the LVPECL DC-coupled termination.

Figure 6–19. LVPECL DC-Coupled Termination (1)

#### Note to Figure 6-19:

(1) The LVPECL DC-coupled termination is applicable only when an Altera FPGA transmitter is used.

Table 8–8 provides the configuration time for AS configuration.

Table 8–8. AS Configuration Time for Cyclone IV Devices (1)

| Symbol          | Parameter            | Cyclone IV E | Cyclone IV GX | Unit |

|-----------------|----------------------|--------------|---------------|------|

| t <sub>SU</sub> | Setup time           | 10           | 8             | ns   |

| t <sub>H</sub>  | Hold time            | 0            | 0             | ns   |

| t <sub>co</sub> | Clock-to-output time | 4            | 4             | ns   |

#### Note to Table 8-8:

(1) For the AS configuration timing diagram, refer to the Serial Configuration (EPCS) Devices Datasheet.

Enabling compression reduces the amount of configuration data that is sent to the Cyclone IV device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

### **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash memory-based devices. You can program these devices in-system with the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cables. Alternatively, you can program them with the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices through the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone IV devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive  $\rm V_{CC}$  and GND, respectively.

To perform in-system programming of a serial configuration device through the AS programming interface, you must place the diodes and capacitors as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V (Figure 8–6).

If you want to use the setup shown in Figure 8–6 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not require a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

For more information about implementing the SFL with Cyclone IV devices, refer to AN 370: Using the Serial FlashLoader with the Quartus II Software.

May 2013 Altera Corporation

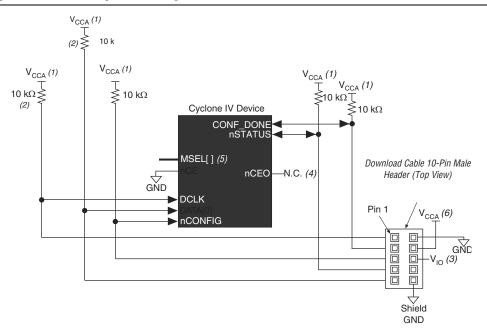

The programming hardware or download cable then places the configuration data one bit at a time on the DATA [0] pin of the device. The configuration data is clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor for the device to initialize.

When you use a download cable, setting the **Auto-restart configuration after error** option does not affect the configuration cycle because you must manually restart configuration in the Quartus II software if an error occurs. Additionally, the **Enable user-supplied start-up clock (CLKUSR)** option has no effect on device initialization, because this option is disabled in the **.sof** when programming the device with the Quartus II Programmer and download cable. Therefore, if you turn on the **CLKUSR** option, you do not have to provide a clock on CLKUSR when you configure the device with the Quartus II Programmer and a download cable.

Figure 8–17 shows PS configuration for Cyclone IV devices with a download cable.

Figure 8-17. PS Configuration Using a Download Cable

### Notes to Figure 8-17:

- (1) You must connect the pull-up resistor to the same supply voltage as the  $V_{CCA}$  supply.

- (2) The pull-up resistors on DATA[0] and DCLK are only required if the download cable is the only configuration scheme used on your board. This is to ensure that DATA[0] and DCLK are not left floating after configuration. For example, if you also use a configuration device, the pull-up resistors on DATA[0] and DCLK are not required.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. With the USB-Blaster, ByteBlaster II, ByteBlaster MV, and EthernetBlaster, this pin is a no connect.

- (4) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (5) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9 for PS configuration schemes. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (6) Power up the V<sub>CC</sub> of the ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from V<sub>CCA</sub>. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

The .rbf used by the JRunner software driver cannot be a compressed .rbf because the JRunner software driver uses JTAG-based configuration. During JTAG-based configuration, the real-time decompression feature is not available.

For more information about the JRunner software driver, refer to *AN 414: JRunner Software Driver: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera website at (www.altera.com).

### **Combining JTAG and AS Configuration Schemes**

You can combine the AS configuration scheme with the JTAG-based configuration (Figure 8–28). This setup uses two 10-pin download cable headers on the board. One download cable is used in JTAG mode to configure the Cyclone IV device directly through the JTAG interface. The other download cable is used in AS mode to program the serial configuration device in-system through the AS programming interface. If you try configuring the device using both schemes simultaneously, JTAG configuration takes precedence and AS configuration terminates.

May 2013 Altera Corporation

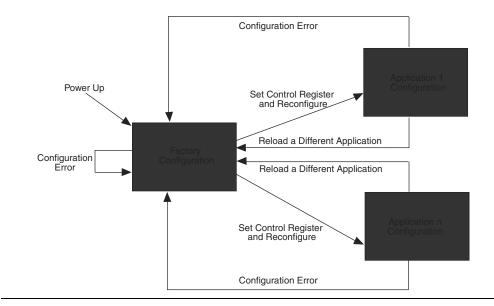

Cyclone IV Device Handbook, Volume 1 Figure 8–32 shows the transitions between the factory configuration and application configuration in remote update mode.

Figure 8–32. Transitions Between Configurations in Remote Update Mode

After power up or a configuration error, the factory configuration logic writes the remote system upgrade control register to specify the address of the application configuration to be loaded. The factory configuration also specifies whether or not to enable the user watchdog timer for the application configuration and, if enabled, specifies the timer setting.

Only valid application configurations designed for remote update mode include the logic to reset the timer in user mode. For more information about the user watchdog timer, refer to the "User Watchdog Timer" on page 8–79.

If there is an error while loading the application configuration, the remote system upgrade status register is written by the dedicated remote system upgrade circuitry of the Cyclone IV device to specify the cause of the reconfiguration.

The following actions cause the remote system upgrade status register to be written:

- nSTATUS driven low externally

- Internal cyclical redundancy check (CRC) error

- User watchdog timer time-out

- A configuration reset (logic array nCONFIG signal or external nCONFIG pin assertion)

The Cyclone IV device automatically loads the factory configuration when an error occurs. This user-designed factory configuration reads the remote system upgrade status register to determine the reason for reconfiguration. Then the factory configuration takes the appropriate error recovery steps and writes to the remote system upgrade control register to determine the next application configuration to be loaded.

### **Remote System Upgrade Registers**

The remote system upgrade block contains a series of registers that stores the configuration addresses, watchdog timer settings, and status information. Table 8-22 lists these registers.

Table 8-22. Remote System Upgrade Registers

| Register            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift<br>register   | This register is accessible by the logic array and allows the update, status, and control registers to be written and sampled by user logic. Write access is enabled in remote update mode for factory configurations to allow writing to the update register. Write access is disabled for all application configurations in remote update mode.                                                                                                                 |

| Control<br>register | This register contains the current configuration address, the user watchdog timer settings, one option bit for checking early CONF_DONE, and one option bit for selecting the internal oscillator as the startup state machine clock. During a read operation in an application configuration, this register is read into the shift register. When a reconfiguration cycle is started, the contents of the update register are written into the control register. |

| Update<br>register  | This register contains data similar to that in the control register. However, it can only be updated by the factory configuration by shifting data into the shift register and issuing an update operation. When a reconfiguration cycle is triggered by the factory configuration, the control register is updated with the contents of the update register. During a read in a factory configuration, this register is read into the shift register.            |

| Status<br>register  | This register is written by the remote system upgrade circuitry on every reconfiguration to record the cause of the reconfiguration. This information is used by the factory configuration to determine the appropriate action following a reconfiguration. During a capture cycle, this register is read into the shift register.                                                                                                                                |

The control and status registers of the remote system upgrade are clocked by the 10-MHz internal oscillator (the same oscillator that controls the user watchdog timer) or the CLKUSR. However, the shift and update registers of the remote system upgrade are clocked by the maximum frequency of 40-MHz user clock input (RU CLK). There is no minimum frequency for RU CLK.

### **Remote System Upgrade Control Register**

The remote system upgrade control register stores the application configuration address, the user watchdog timer settings, and option bits for a application configuration. In remote update mode for the AS configuration scheme, the control register address bits are set to all zeros (24 'b0) at power up to load the AS factory configuration. In remote update mode for the AP configuration scheme, the control register address bits are set to 24'h010000 (24'b1 0000 0000 0000 0000) at power up to load the AP default factory configuration. However, for the AP configuration scheme, you can change the default factory configuration address to any desired address using the APFC BOOT ADDR JTAG instruction. Additionally, a factory configuration in remote update mode has write access to this register.

May 2013 Altera Corporation Cyclone IV Device Handbook, Volume 1

## **EXTEST\_PULSE**

The instruction code for EXTEST\_PULSE is 0010001111. The EXTEST\_PULSE instruction generates three output transitions:

- Driver drives data on the falling edge of TCK in UPDATE\_IR/DR.

- Driver drives inverted data on the falling edge of TCK after entering the RUN\_TEST/IDLE state.

- Driver drives data on the falling edge of TCK after leaving the RUN\_TEST/IDLE state.

If you use DC-coupling on HSSI signals, you must execute the EXTEST instruction. If you use AC-coupling on HSSI signals, you must execute the EXTEST\_PULSE instruction. AC-coupled and DC-coupled HSSI are only supported in post-configuration mode.

## EXTEST\_TRAIN

The instruction code for EXTEST\_TRAIN is 0001001111. The EXTEST\_TRAIN instruction behaves the same as the EXTEST\_PULSE instruction with one exception. The output continues to toggle on the TCK falling edge as long as the test access port (TAP) controller is in the RUN\_TEST/IDLE state.

When you perform JTAG boundary-scan testing before configuration, the nCONFIG pin must be held low.

## I/O Voltage Support in a JTAG Chain

A Cyclone IV device operating in BST mode uses four required pins: TDI, TDO, TMS, and TCK. The TDO output pin and all JTAG input pins are powered by the  $V_{CCIO}$  power supply of I/O Banks (I/O Bank 9 for Cyclone IV GX devices and I/O Bank 1 for Cyclone IV E devices).

A JTAG chain can contain several different devices. However, you must use caution if the chain contains devices that have different  $V_{CCIO}$  levels. The output voltage level of the TDO pin must meet the specification of the TDI pin it drives. For example, a device with a 3.3-V TDO pin can drive a device with a 5.0-V TDI pin because 3.3 V meets the minimum TTL-level  $V_{IH}$  for the 5.0-V TDI pin.

For multiple devices in a JTAG chain with the 3.0-V/3.3-V I/O standard, you must connect a 25- $\Omega$  series resistor on a TDO pin driving a TDI pin.

You can also interface the TDI and TDO lines of the devices that have different  $V_{\rm CCIO}$  levels by inserting a level shifter between the devices. If possible, the JTAG chain should have a device with a higher  $V_{\rm CCIO}$  level driving a device with an equal or lower  $V_{\rm CCIO}$  level. This way, a level shifter may be required only to shift the TDO level to a level acceptable to the JTAG tester.

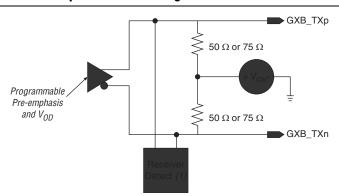

## **Transmitter Output Buffer**

Figure 1–11 shows the transmitter output buffer block diagram.

Figure 1-11. Transmitter Output Buffer Block Diagram

#### Note to Figure 1-11:

Receiver detect function is specific for PCle protocol implementation only. For more information, refer to "PCl Express (PIPE) Mode" on page 1–52.

The Cyclone IV GX transmitter output buffers support the **1.5-V PCML** I/O standard and are powered by VCCH\_GXB power pins with 2.5-V supply. The 2.5-V supply on VCCH\_GXB pins are regulated internally to 1.5-V for the transmitter output buffers. The transmitter output buffers support the following additional features:

- Programmable differential output voltage  $(V_{OD})$ —customizes the  $V_{OD}$  up to 1200 mV to handle different trace lengths, various backplanes, and various receiver requirements.

- Programmable pre-emphasis—boosts high-frequency components in the transmitted signal to maximize the data eye opening at the far-end. The high-frequency components might be attenuated in the transmission media due to data-dependent jitter and intersymbol interference (ISI) effects. The requirement for pre-emphasis increases as the data rates through legacy backplanes increase.

- Programmable differential on-chip termination (OCT)—provides calibrated OCT at differential  $100~\Omega$  or  $150~\Omega$  with on-chip transmitter common mode voltage ( $V_{CM}$ ) at 0.65~V.  $V_{CM}$  is tri-stated when you disable the OCT to use external termination.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- The Cyclone IV GX transmitter output buffers are current-mode drivers. The resulting  $V_{OD}$  voltage is therefore a function of the transmitter termination value. For lists of supported  $V_{OD}$  settings, refer to the *Cyclone IV Device Data Sheet*.

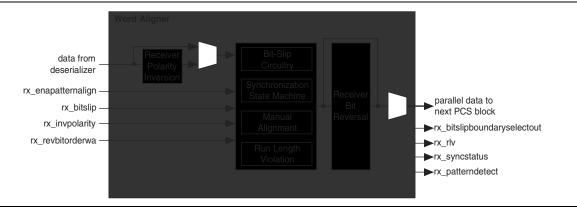

## **Word Aligner**

Figure 1–16 shows the word aligner block diagram. The word aligner receives parallel data from the deserializer and restores the word boundary based on a pre-defined alignment pattern that must be received during link synchronization. The word aligner supports three operational modes as listed in Table 1–3.

Figure 1-16. Word Aligner Block Diagram

Table 1-3. Word Aligner Modes

| Modes                                      | PMA-PCS Interface Widths | Allowed Word Alignment<br>Pattern Lengths |

|--------------------------------------------|--------------------------|-------------------------------------------|

| Manual Alignment                           | 8-bit                    | 16 bits                                   |

| Wandai Angiinient                          | 10-bit                   | 7 or 10 bits                              |

| Dit Clin                                   | 8-bit                    | 16 bits                                   |

| Bit-Slip                                   | 10-bit                   | 7 or 10 bits                              |

| Automatic Synchronization State<br>Machine | 10-bit                   | 7 or 10 bits                              |

### **Manual Alignment Mode**

In manual alignment mode, the rx\_enapatternalign port controls the word aligner with either an 8- or 10-bit data width setting.

The 8-bit word aligner is edge-sensitive to the rx\_enapatternalign signal. A rising edge on rx\_enapatternalign signal after deassertion of the rx\_digitalreset signal triggers the word aligner to look for the word alignment pattern in the received data stream. It updates the word boundary if it finds the word alignment pattern in a new word boundary. Any word alignment pattern received thereafter in a different word boundary causes the word aligner to re-align to the new word boundary only if there is a rising edge in the rx\_enapatternalign signal.

The 10-bit word aligner is level-sensitive to the rx\_enapatternalign signal. The word aligner looks for the programmed 7-bit or 10-bit word alignment pattern or its complement in the received data stream, if the rx\_enapatternalign signal is held high. It updates the word boundary if it finds the word alignment pattern in a new word boundary. If the rx\_enapatternalign signal is deasserted, the word aligner maintains the current word boundary even when it receives the word alignment pattern in a new word boundary.

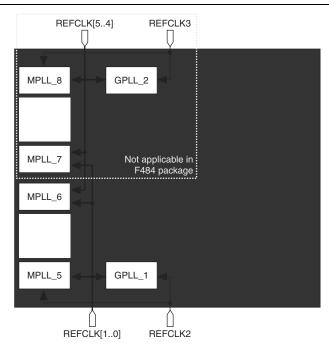

Figure 1–26. PLL Input Reference Clocks in Transceiver Operation for F484 and Larger Packages  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$

#### Notes to Figure 1-26:

- (1) The REFCLK2 and REFCLK3 pins are dual-purpose CLKIO, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A respectively.

- (2) The REFCLK [1..0] and REFCLK [5..4] pins are dual-purpose differential REFCLK or DIFFCLK pins that reside in banks 3B and 8B respectively. These clock input pins do not have access to the clock control blocks and GCLK networks. For more details, refer to the Clock Networks and PLLs in Cyclone IV Devices chapter.

- (3) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs and GPLLs may have reduced jitter performance.

The input reference clocks reside in banks 3A, 3B, 8A, and 8B have dedicated  $V_{CC\_CLKIN3A}$ ,  $V_{CC\_CLKIN3B}$ ,  $V_{CC\_CLKIN8A}$ , and  $V_{CC\_CLKIN8B}$  power supplies separately in their respective I/O banks to avoid the different power level requirements in the same bank for general purpose I/Os (GPIOs). Table 1–6 lists the supported I/O standard for the REFCLK pins.

Table 1–6. REFCLK I/O Standard Support

|                             | HSSI     |                         | Terminatio | VCC_  | CLKIN Level   | I/O Pin Type |         |                    |  |  |

|-----------------------------|----------|-------------------------|------------|-------|---------------|--------------|---------|--------------------|--|--|

| I/O Standard                | Protocol | Coupling                | n          | Input | Output        | Column I/O   | Row I/O | Supported<br>Banks |  |  |

| LVDS                        | ALL      | Differential            | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| LVPECL                      | ALL      | AC (Needs               | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 404454                      | ALL      | off-chip<br>resistor to | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 1.2 V, 1.5 V,<br>3.3 V PCML | ALL      | restore                 | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| 0.0 1 1 02                  | ALL      | V <sub>CM</sub> )       | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

| HCSL                        | PCle     | Differential<br>DC      | Off-chip   | 2.5 V | Not Supported | Yes          | No      | 3A, 3B, 8A, 8B     |  |  |

Figure 1–66 shows the transceiver channel datapath and clocking when configured in deterministic latency mode.

Figure 1-66. Transceiver Channel Datapath and Clocking when Configured in Deterministic Latency Mode

### Note to Figure 1-66:

(1) High-speed recovered clock.

Table 1–27. Receiver Ports in ALTGX Megafunction for Cyclone IV GX (Part 3 of 3)

| Block  | Port Name                          | Input/<br>Output | Clock Domain                                                             | Description                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------|------------------------------------|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|        | rx_coreclk                         | Output           | Clock signal                                                             | Optional read clock port for the RX phase compensation FIFO.                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| RX PCS | rx_phase_comp_fifo<br>_error       | Output           | Synchronous to tx_clkout (non-bonded modes) or coreclkout (bonded modes) | RX phase compensation FIFO full or empty indicator.  A high level indicates FIFO is either full or empty.                                                                                                                                                                                                                              |  |  |  |  |  |

|        | rx_bitslipboundarys<br>electout    | Output           | Asynchronous signal.                                                     | Indicate the number of bits slipped in the word aligner configured in manual alignment mode.  ■ Values range from 0 to 9.                                                                                                                                                                                                              |  |  |  |  |  |

|        | rx_datain                          | Input            | N/A                                                                      | Receiver serial data input port.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|        | rx_freqlocked                      | Output           | Asynchronous signal                                                      | Receiver CDR lock state indicator  A high level indicates the CDR is in LTD state.  A low level indicates the CDR is in LTR state.                                                                                                                                                                                                     |  |  |  |  |  |

|        | rx_locktodata                      | Input            | Asynchronous signal                                                      | Receiver CDR LTD state control signal  A high level forces the CDR to LTD state  When deasserted, the receiver CDR lock state depends on the rx_locktorefclk signal level.                                                                                                                                                             |  |  |  |  |  |

| RX PMA | rx_locktorefclk                    | Input            | Asynchronous signal                                                      | Receiver CDR LTR state control signal.  The rx_locktorefclk and rx_locktodata signals control whether the receiver CDR states as follows:  [rx_locktodata:rx_locktorefclk]  2'b00—receiver CDR is in automatic lock mode  2b'01—receiver CDR is in manual lock mode (LTR state)  2b'1x—receiver CDR is in manual lock mode (LTD state) |  |  |  |  |  |

|        | rx_signaldetect                    | Output           | Asynchronous signal                                                      | Signal threshold detect indicator.  Available in Basic mode when 8B/10B encoder/decoder is used, and in PIPE mode.  A high level indicates that the signal present at the receiver input buffer is above the programmed signal detection threshold value.                                                                              |  |  |  |  |  |

|        | rx_recovclkout Output Clock signal |                  | Clock signal                                                             | CDR low-speed recovered clock ■ Only available in the GIGE mode for applications such as Synchronous Ethernet.                                                                                                                                                                                                                         |  |  |  |  |  |

Table 1–29. Multipurpose PLL, General Purpose PLL and Miscellaneous Ports in ALTGX Megafunction for Cyclone IV GX (Part 2 of 2)

| Block                 | Port Name         | Input/<br>Output | Clock Domain                                                                        | Description                                                                                                                                                                                 |

|-----------------------|-------------------|------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                   |                  |                                                                                     | Transceiver block power down.                                                                                                                                                               |

|                       | gxb_powerdown     | Input            | Asynchronous signal                                                                 | ■ When asserted, all digital and analog circuitry in the PCS, HSSI, CDR, and PCIe modules are powered down.                                                                                 |

| Reset & Power<br>Down |                   |                  |                                                                                     | <ul> <li>Asserting the gxb_powerdown signal does not power<br/>down the refclk buffers.</li> </ul>                                                                                          |

|                       | tx_digitalreset   | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Transmitter PCS reset.  When asserted, the transmitter PCS blocks are reset.                                                                                                                |

|                       | rx_analogreset    | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Receiver PMA reset.  When asserted, analog circuitry in the receiver PMA block is reset.                                                                                                    |

|                       | rx_digitalreset   | Input            | Asynchronous signal.<br>The minimum pulse<br>width is two parallel<br>clock cycles. | Receiver PCS reset.  When asserted, the receiver PCS blocks are reset.                                                                                                                      |

|                       |                   |                  |                                                                                     | Dynamic reconfiguration clock.                                                                                                                                                              |

|                       | reconfig_clk      | Input            | Clock signal                                                                        | Also used for offset cancellation except in PIPE mode.                                                                                                                                      |

| Reconfiguration       | Tooding_one       | mpat             | olook olgilal                                                                       | ■ For the supported frequency range for this clock, refer to the <i>Cyclone IV Device Data Sheet</i> chapter.                                                                               |

|                       | reconfig_togxb    | Input            | Asynchronous signal                                                                 | From the dynamic reconfiguration controller.                                                                                                                                                |

|                       | reconfig_fromgxb  | Output           | Asynchronous signal                                                                 | To the dynamic reconfiguration controller.                                                                                                                                                  |

| Calibration Block     | cal_blk_clk       | Input            | Clock signal                                                                        | Clock for the transceiver calibration block.                                                                                                                                                |

| Calibration Block     | cal_blk_powerdown | Input            | Asynchronous signal                                                                 | Calibration block power down control.                                                                                                                                                       |

|                       |                   |                  |                                                                                     | BIST or PRBS test completion indicator.                                                                                                                                                     |

|                       | rx_bistdone       | Output           | Asynchronous signal                                                                 | ■ A high level during BIST test mode indicates the verifier either receives complete pattern cycle or detects an error and stays asserted until being reset using the rx_digitalreset port. |

| Test Mode             |                   |                  |                                                                                     | ■ A high level during PRBS test mode indicates the verifier receives complete pattern cycle and stays asserted until being reset using the rx_digitalreset port.                            |

|                       |                   |                  |                                                                                     | BIST or PRBS verifier error indicator                                                                                                                                                       |

|                       | rx_bisterr        | Output           | Asynchronous signal                                                                 | ■ In BIST test mode, the signal stays asserted upon detecting an error until being reset using the rx_digitalreset port.                                                                    |

|                       |                   |                  |                                                                                     | ■ In PRBS test mode, the signal asserts for a minimum of 3 rx_clkout clock cycles upon detecting an error and deasserts if the following PRBS sequence contains no error.                   |

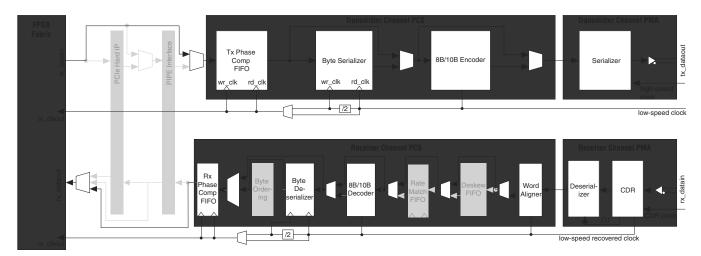

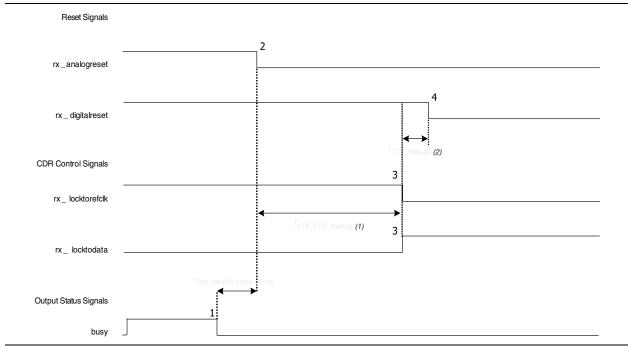

Figure 1–2 shows the lock time parameters in manual mode.

LTD = lock-to-data. LTR = lock-to-reference.

Figure 1–2. Lock Time Parameters for Manual Mode

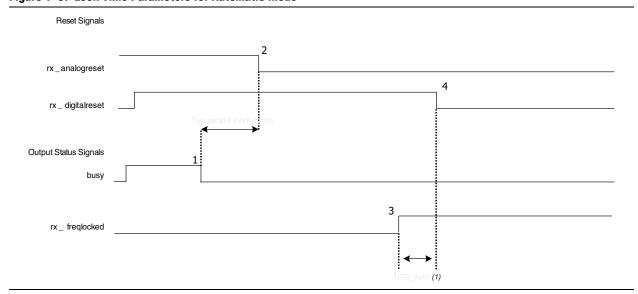

Figure 1–3 shows the lock time parameters in automatic mode.

Figure 1–3. Lock Time Parameters for Automatic Mode