### Intel - EP4CE115F29I7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 7155                                                      |

| Number of Logic Elements/Cells | 114480                                                    |

| Total RAM Bits                 | 3981312                                                   |

| Number of I/O                  | 528                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 780-BGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29i7n |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

CYIV-51002-1.0

This chapter contains feature definitions for logic elements (LEs) and logic array blocks (LABs). Details are provided on how LEs work, how LABs contain groups of LEs, and how LABs interface with the other blocks in Cyclone<sup>®</sup> IV devices.

# **Logic Elements**

Logic elements (LEs) are the smallest units of logic in the Cyclone IV device architecture. LEs are compact and provide advanced features with efficient logic usage. Each LE has the following features:

- A four-input look-up table (LUT), which can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive the following interconnects:

- Local

- Row

- Column

- Register chain

- Direct link

- Register packing support

- Register feedback support

© 2009 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **True Dual-Port Mode**

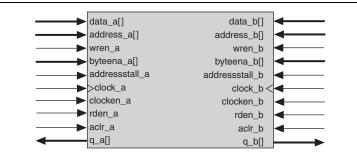

True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write, at two different clock frequencies. Figure 3–10 shows Cyclone IV devices true dual-port memory configuration.

#### Note to Figure 3-10:

(1) True dual-port memory supports input or output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M9K blocks in true dual-port mode is 512 × 16-bit (18-bit with parity).

Table 3–4 lists the possible M9K block mixed-port width configurations.

| Read Port |              |              |              | Write Port   |              |              |              |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| neau ruit | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 1024 × 9     | 512 × 18     |

| 8192 × 1  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 2048 × 4  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 1024 × 8  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 512 × 16  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | —            |

| 1024 × 9  | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ |

| 512 × 18  | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ |

Table 3-4. Cyclone IV Devices M9K Block Mixed-Width Configurations (True Dual-Port Mode)

In true dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "New Data" at that location or "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15.

#### Table 5–2. GCLK Network Connections for EP4CGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Devices <sup>(1), (2)</sup> (Part 4 of 4)

| GCLK Network Clock |   |   |   |   |   |   |   |   |   |   |    |    |    | GC | LK No | etwo | rks |    |    |              |    |    |    |    |    |    |    |    |    |    |

|--------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|-------|------|-----|----|----|--------------|----|----|----|----|----|----|----|----|----|----|

| Sources            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14    | 15   | 16  | 17 | 18 | 19           | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| DPCLK17            | — |   | _ |   | — | _ |   | — | — |   | —  |    |    | —  | _     |      | —   | —  | _  | $\checkmark$ |    | —  |    | _  | —  | —  |    | —  |    | —  |

#### Notes to Table 5-2:

(1) EP4CGX30 information in this table refers to only EP4CGX30 device in F484 package.

(2) PLL\_1, PLL\_2, PLL\_3, and PLL\_4 are general purpose PLLs while PLL\_5, PLL\_6, PLL\_7, and PLL\_8 are multipurpose PLLs.

(3) PLL\_7 and PLL\_8 are not available in EP4CXGX30, EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 devices in F484 package.

| GCLK Network Clock      | ck GCLK Networks |              |              |              |              |   |              |              |              |   |              |              |              |    |              |    |    |    |    |    |

|-------------------------|------------------|--------------|--------------|--------------|--------------|---|--------------|--------------|--------------|---|--------------|--------------|--------------|----|--------------|----|----|----|----|----|

| Sources                 | 0                | 1            | 2            | 3            | 4            | 5 | 6            | 7            | 8            | 9 | 10           | 11           | 12           | 13 | 14           | 15 | 16 | 17 | 18 | 19 |

| CLK1                    | —                | $\checkmark$ | $\checkmark$ | —            | —            | — | —            | —            | —            | _ | _            | —            | —            | —  | —            | —  | —  | —  | —  |    |

| CLK2/DIFFCLK_1p         |                  | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | — | —            | —            | —            | _ | _            | —            |              | —  | —            | —  | —  | _  | —  | —  |

| CLK3/DIFFCLK_1n         | >                |              |              | >            |              |   |              |              |              |   |              |              |              |    | -            | -  |    |    | _  | —  |

| CLK4/DIFFCLK_2p         |                  |              |              |              |              | > |              | >            |              | ~ | —            |              |              |    |              |    |    | —  | —  | —  |

| CLK5/DIFFCLK_2n         |                  | —            | —            |              |              | — | $\checkmark$ | $\checkmark$ | —            | _ | _            | —            |              | —  | —            | —  | —  | _  | —  | —  |

| CLK6/DIFFCLK_3p         | —                | —            | —            | —            | —            | — | $\checkmark$ | —            | $\checkmark$ | ~ | _            | —            |              | —  | _            | _  | —  | _  | —  | —  |

| CLK7/DIFFCLK_3n         |                  |              |              |              |              | > |              |              | >            | — | —            |              |              |    |              |    |    | —  | —  | —  |

| CLK8/DIFFCLK_5n (2)     | —                | —            | —            | —            | —            | — | —            | —            | —            |   | $\checkmark$ | —            | $\checkmark$ | —  | $\checkmark$ | —  | —  | _  | —  | —  |

| CLK9/DIFFCLK_5p (2)     | —                | —            | —            | —            | —            | — | —            | —            | —            |   | _            | $\checkmark$ | $\checkmark$ | —  | —            | —  | —  | _  | —  | —  |

| CLK10/DIFFCLK_4n (2)    | —                |              | _            | —            | —            | _ | _            | _            | _            | _ | _            | ~            | _            | ~  | ~            | _  | _  | _  | _  | —  |

| CLK11/DIFFCLK_4p<br>(2) | _                |              | _            | _            | _            | _ | _            | _            | _            | _ | ~            | _            | _            | ~  | _            | _  | _  | _  | _  | —  |

| CLK12/DIFFCLK_7n (2)    | _                |              | _            | _            | _            | _ | _            |              | _            | _ |              | _            | _            |    |              | ~  |    | ~  | _  | ~  |

| CLK13/DIFFCLK_7p (2)    | _                |              | _            | _            | _            | _ | _            |              | _            | _ | _            | _            | _            |    | _            | _  | ~  | ~  | —  |    |

| CLK14/DIFFCLK_6n (2)    | _                | _            | _            | _            | _            | _ | _            | _            | _            | _ | _            | _            | _            | _  | _            | _  | ~  | _  | ~  | ~  |

## Table 5–3. GCLK Network Connections for Cyclone IV E Devices <sup>(1)</sup> (Part 1 of 3)

The IOE registers in each I/O block share the same source for the preset or clear features. You can program preset or clear for each individual IOE, but you cannot use both features simultaneously. You can also program the registers to power-up high or low after configuration is complete. If programmed to power-up low, an asynchronous clear can control the registers. If programmed to power-up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of the active-low input of another device upon power-up. If one register in an IOE uses a preset or clear signal, all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

**For more information about the input and output pin delay settings, refer to the** *Area and Timing Optimization* chapter in volume 2 of the *Quartus II Handbook*.

## **PCI-Clamp Diode**

Cyclone IV devices provide an optional PCI-clamp diode enabled input and output for each I/O pin. Dual-purpose configuration pins support the diode in user mode if the specific pins are not used as configuration pins for the selected configuration scheme. For example, if you are using the active serial (AS) configuration scheme, you cannot use the clamp diode on the ASDO and nCSO pins in user mode. Dedicated configuration pins do not support the on-chip diode.

The PCI-clamp diode is available for the following I/O standards:

- 3.3-V LVTTL

- 3.3-V LVCMOS

- 3.0-V LVTTL

- 3.0-V LVCMOS

- 2.5-V LVTTL/LVCMOS

- PCI

- PCI-X

If the input I/O standard is one of the listed standards, the PCI-clamp diode is enabled by default in the Quartus II software.

## **OCT Support**

Cyclone IV devices feature OCT to provide I/O impedance matching and termination capabilities. OCT helps prevent reflections and maintain signal integrity while minimizing the need for external resistors in high pin-count ball grid array (BGA) packages. Cyclone IV devices provide I/O driver on-chip impedance matching and R<sub>S</sub> OCT for single-ended outputs and bidirectional pins.

$\mathbb{L}$  When using R<sub>S</sub> OCT, programmable current strength is not available.

There are two ways to implement OCT in Cyclone IV devices:

- OCT with calibration

- OCT without calibration

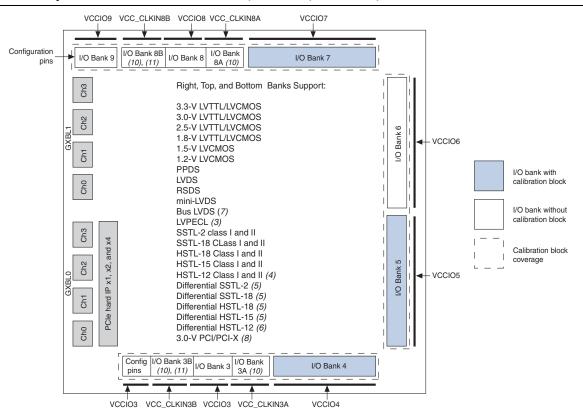

Figure 6-11. Cyclone IV GX I/O Banks for EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 (1), (2), (9)

#### Notes to Figure 6–11:

- (1) This is a top view of the silicon die. For exact pin locations, refer to the pin list and the Quartus II software.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 5 and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 4, 7, and 8.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. PLL output clock pins do not support Class II interface type of differential SSTL-18, HSTL-18, HSTL-15, and HSTL-12 I/O standards.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses the LVDS input buffer.

- (8) The PCI-X I/O standard does not meet the IV curve requirement at the linear region.

- (9) The OCT block is located in the shaded banks 4, 5, and 7.

- (10) The dedicated clock input I/O banks 3A, 3B, 8A, and 8B can be used either for HSSI input reference clock pins or clock input pins.

- (11) Single-ended clock input support is available for dedicated clock input I/O banks 3B and 8B.

When designing LVTTL/LVCMOS inputs with Cyclone IV devices, refer to the following guidelines:

- All pins accept input voltage (V<sub>I</sub>) up to a maximum limit (3.6 V), as stated in the recommended operating conditions provided in the *Cyclone IV Device Datasheet* chapter.

- Whenever the input level is higher than the bank V<sub>CCIO</sub>, expect higher leakage current.

- The LVTTL/LVCMOS I/O standard input pins can only meet the V<sub>IH</sub> and V<sub>IL</sub> levels according to bank voltage level.

Voltage-referenced standards are supported in an I/O bank using any number of single-ended or differential standards, as long as they use the same V<sub>REF</sub> and V<sub>CCIO</sub> values. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone IV devices, I/O pins using these standards—because they require different V<sub>REF</sub> values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the V<sub>CCIO</sub> set to 2.5 V and the V<sub>REF</sub> set to 1.25 V.

- When using Cyclone IV devices as a receiver in 3.3-, 3.0-, or 2.5-V LVTTL/LVCMOS systems, you are responsible for managing overshoot or undershoot to stay in the absolute maximum ratings and the recommended operating conditions, provided in the *Cyclone IV Device Datasheet* chapter.

- The PCI clamping diode is enabled by default in the Quartus II software for input signals with bank  $V_{CCIO}$  at 2.5, 3.0, or 3.3 V.

## **High-Speed Differential Interfaces**

Cyclone IV devices can send and receive data through LVDS signals. For the LVDS transmitter and receiver, the input and output pins of Cyclone IV devices support serialization and deserialization through internal logic.

The BLVDS extends the benefits of LVDS to multipoint applications such as bidirectional backplanes. The loading effect and the need to terminate the bus at both ends for multipoint applications require BLVDS to drive out a higher current than LVDS to produce a comparable voltage swing. All the I/O banks of Cyclone IV devices support BLVDS for user I/O pins.

The RSDS and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI).

The PPDS standard is the next generation of the RSDS standard introduced by National Semiconductor Corporation. Cyclone IV devices meet the National Semiconductor Corporation PPDS Interface Specification and support the PPDS standard for outputs only. All the I/O banks of Cyclone IV devices support the PPDS standard for output pins only.

The LVDS standard does not require an input reference voltage, but it does require a 100- $\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side for the top and bottom I/O banks.

#### Table 6–8. Cyclone IV E I/O and Differential Channel Count

| Device                                                  |          | EP4CE6   |          |          | EP4CE10  |          |          |          |          | 6140613  |          |          |          | EP4CE22  |          |          | EP4CE30  |          |          | ED 40 E 40 |          |          |          | EP4CE55  |          |          | EP4CE75  |          | EDACE11E |          |

|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Numbers of Differential<br>Channels <sup>(1), (2)</sup> | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 144-EQPF | 164-MBGA | 256-MBGA | 256-UBGA | 256-FBGA | 484-FBGA | 144-EQPF | 256-UBGA | 256-FBGA | 324-FBGA | 484-FBGA | 780-FBGA | 324-FBGA | 484-UBGA   | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-UBGA | 484-FBGA | 780-FBGA | 484-FBGA | 780-FBGA |

| User<br>I/O <i>(3)</i>                                  | 91       | 179      | 179      | 91       | 179      | 179      | 81       | 89       | 165      | 165      | 165      | 343      | 79       | 153      | 153      | 193      | 328      | 532      | 193      | 328        | 328      | 532      | 324      | 324      | 374      | 292      | 292      | 426      | 280      | 528      |

| User I/O<br>Banks                                       | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8          | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        | 8        |

| LVDS <sup>(4),</sup> (<br>6)                            | 8        | 23       | 23       | 8        | 23       | 23       | 6        | 8        | 21       | 21       | 21       | 67       | 7        | 20       | 20       | 30       | 60       | 112      | 30       | 60         | 60       | 112      | 62       | 62       | 70       | 54       | 54       | 79       | 50       | 103      |

| Emulated<br>LVDS (5), (<br>6)                           | 13       | 43       | 43       | 13       | 43       | 43       | 12       | 13       | 32       | 32       | 32       | 70       | 10       | 32       | 32       | 38       | 64       | 112      | 38       | 64         | 64       | 112      | 70       | 70       | 90       | 56       | 56       | 99       | 53       | 127      |

Notes to Table 6-8:

(1) User I/O pins are used as inputs or outputs; clock input pins are used as inputs only; clock output pins are used as output only.

(2) For differential pad placement guidelines, refer to "Pad Placement" on page 6-23.

(3) The I/O pin count includes all GPIOs, dedicated clock pins, and dual-purpose configuration pins. Dedicated configuration pins are not included in the pin count.

(4) The true LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in row I/O banks 1, 2, 5, and 6.

(5) The emulated LVDS count includes all LVDS I/O pairs, differential clock input and clock output pins in column I/O banks 3, 4, 7, and 8.

(6) LVDS input and output buffers are sharing the same p and n pins. One LVDS I/O channel can only be either transmitter or receiver at a time.

This section includes the following chapters:

- Chapter 8, Configuration and Remote System Upgrades in Cyclone IV Devices

- Chapter 9, SEU Mitigation in Cyclone IV Devices

- Chapter 10, JTAG Boundary-Scan Testing for Cyclone IV Devices

- Chapter 11, Power Requirements for Cyclone IV Devices

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

## **Configuration Scheme**

A configuration scheme with different configuration voltage standards is selected by driving the MSEL pins either high or low, as shown in Table 8–3, Table 8–4, and Table 8–5.

Hardwire the MSEL pins to V<sub>CCA</sub> or GND without pull-up or pull-down resistors to avoid problems detecting an incorrect configuration scheme. Do not drive the MSEL pins with a microprocessor or another device.

| Table 8–3. | Configuration Schemes for Cyclone IV GX Devices (EP4CGX15, EP4CGX22, and EP4CGX30 [except for F484 |

|------------|----------------------------------------------------------------------------------------------------|

| Package])  |                                                                                                    |

| Configuration Scheme                    | MSEL2 | MSEL1 | MSELO | POR Delay | Configuration Voltage Standard (V) $^{(1)}$ |

|-----------------------------------------|-------|-------|-------|-----------|---------------------------------------------|

|                                         | 1     | 0     | 1     | Fast      | 3.3                                         |

| AS                                      | 0     | 1     | 1     | Fast      | 3.0, 2.5                                    |

| AO                                      | 0     | 0     | 1     | Standard  | 3.3                                         |

|                                         | 0     | 1     | 0     | Standard  | 3.0, 2.5                                    |

|                                         | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                               |

| PS                                      | 1     | 1     | 0     | Fast      | 1.8, 1.5                                    |

|                                         | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                               |

| JTAG-based configuration <sup>(2)</sup> | (3)   | (3)   | (3)   |           | _                                           |

#### Notes to Table 8-3:

(1) Configuration voltage standard applied to the  $V_{CCIO}$  supply of the bank in which the configuration pins reside.

(2) JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored.

(3) Do not leave the MSEL pins floating. Connect them to  $V_{CCA}$  or GND. These pins support the non-JTAG configuration scheme used in production. Altera recommends connecting the MSEL pins to GND if your device is only using JTAG configuration.

| Table 8–4. Configuration Schemes for Cy | clone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, |

|-----------------------------------------|------------------------------------------------------------------|

| EP4CGX75, EP4CGX110, and EP4CGX150)     | (Part 1 of 2)                                                    |

| Configuration Scheme | MSEL3 | MSEL2 | MSEL1 | MSELO    | POR Delay | Configuration Voltage Standard (V) <sup>(1)</sup> |

|----------------------|-------|-------|-------|----------|-----------|---------------------------------------------------|

|                      | 1     | 1     | 0     | 1        | Fast      | 3.3                                               |

| AS                   | 1     | 0     | 1     | 1        | Fast      | 3.0, 2.5                                          |

| AS                   | 1     | 0     | 0     | 1        | Standard  | 3.3                                               |

|                      | 1     | 0     | 1     | 0        | Standard  | 3.0, 2.5                                          |

|                      | 1     | 1     | 0     | 0        | Fast      | 3.3, 3.0, 2.5                                     |

| PS                   | 1     | 1     | 1     | 0        | Fast      | 1.8, 1.5                                          |

| го                   | 1     | 0     | 0     | 0        | Standard  | 3.3, 3.0, 2.5                                     |

|                      | 0     | 0     | 0     | 0        | Standard  | 1.8, 1.5                                          |

|                      | 0     | 0     | 1     | 1        | Fast      | 3.3, 3.0, 2.5                                     |

| FPP                  | 0     | 1     | 0     | 0 0 Fast | 1.8, 1.5  |                                                   |

|                      | 0     | 0     | 0     | 1        | Standard  | 3.3, 3.0, 2.5                                     |

|                      | 0     | 0     | 1     | 0        | Standard  | 1.8, 1.5                                          |

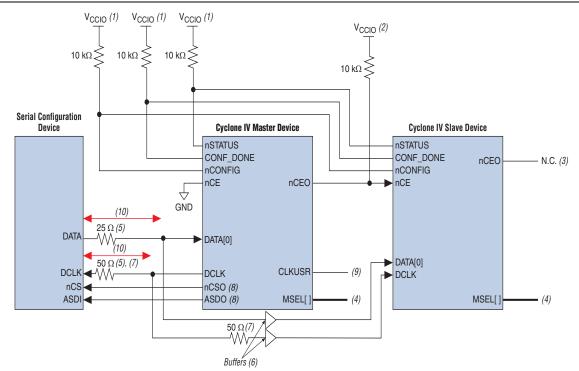

## **Multi-Device AS Configuration**

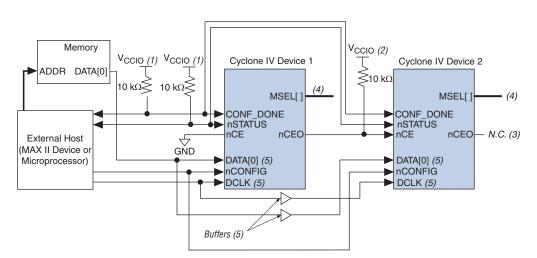

You can configure multiple Cyclone IV devices with a single serial configuration device. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. If the last device in the chain is a Cyclone IV device, you can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, and DATA[0] pins of each device in the chain are connected together (Figure 8–3).

#### Notes to Figure 8-3:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank in which the nCE pin resides.

- (3) You can leave the nCEO pin unconnected or use it as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device of the Cyclone IV device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the master and slave devices of the Cyclone IV device for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

The nSTATUS and CONF\_DONE pins on all target devices are connected together with external pull-up resistors, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27. These pins are open-drain bidirectional pins on the devices. When the first device asserts nCEO (after receiving all its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they receive their configuration data. When all target devices in the chain receive their configuration data and release CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

# Guidelines for Connecting Parallel Flash to Cyclone IV E Devices for an AP Interface

For single- and multi-device AP configuration, the board trace length and loading between the supported parallel flash and Cyclone IV E devices must follow the recommendations listed in Table 8–11. These recommendations also apply to an AP configuration with multiple bus masters.

| Cyclone IV E AP Pins | Maximum Board Trace Length from<br>Cyclone IV E Device to Flash Device<br>(inches) | Maximum Board Load (pF) |

|----------------------|------------------------------------------------------------------------------------|-------------------------|

| DCLK                 | 6                                                                                  | 15                      |

| DATA[150]            | 6                                                                                  | 30                      |

| PADD[230]            | 6                                                                                  | 30                      |

| nRESET               | 6                                                                                  | 30                      |

| Flash_nCE            | 6                                                                                  | 30                      |

| nOE                  | 6                                                                                  | 30                      |

| nAVD                 | 6                                                                                  | 30                      |

| nWE                  | 6                                                                                  | 30                      |

| I/O (1)              | 6                                                                                  | 30                      |

Table 8–11. Maximum Trace Length and Loading for AP Configuration

Note to Table 8-11:

(1) The AP configuration ignores the WAIT signal from the flash during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

## **Configuring With Multiple Bus Masters**

Similar to the AS configuration scheme, the AP configuration scheme supports multiple bus masters for the parallel flash. For another master to take control of the AP configuration bus, the master must assert nCONFIG low for at least 500 ns to reset the master Cyclone IV E device and override the weak 10-k $\Omega$  pull-down resistor on the nCE pin. This resets the master Cyclone IV E device then takes control of the AP configuration bus. The other master device then takes control of the AP configuration bus, then releases the nCE pin, and finally pulses nCONFIG low to restart the configuration.

In the AP configuration scheme, multiple masters share the parallel flash. Similar to the AS configuration scheme, the bus control is negotiated by the nCE pin.

To ensure DCLK and DATA [0] are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA [0] pin is available as a user I/O pin after configuration. In the PS scheme, the DATA [0] pin is tri-stated by default in user mode and must be driven by the external host device. To change this default option in the Quartus II software, select the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified system frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

The external host device can also monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. The CONF\_DONE pin must be monitored by the external device to detect errors and to determine when programming is complete. If all configuration data is sent, but CONF\_DONE or INIT\_DONE has not gone high, the external device must reconfigure the target device.

Figure 8–14 shows how to configure multiple devices using an external host device. This circuit is similar to the PS configuration circuit for a single device, except that Cyclone IV devices are cascaded for multi-device configuration.

#### Figure 8–14. Multi-Device PS Configuration Using an External Host

#### Notes to Figure 8-14:

- (1) The pull-up resistor must be connected to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

| 0kal                | Devenueter                                                     | Minii                           | num                         | Maxir                     | num                         | – Unit |

|---------------------|----------------------------------------------------------------|---------------------------------|-----------------------------|---------------------------|-----------------------------|--------|

| Symbol              | Parameter                                                      | Cyclone IV (1)                  | Cyclone IV E <sup>(2)</sup> | Cyclone IV <sup>(1)</sup> | Cyclone IV E <sup>(2)</sup> | Unit   |

| t <sub>st2CK</sub>  | nSTATUS high to<br>first rising edge of<br>DCLK                | 2                               |                             | _                         | -                           | μs     |

| t <sub>DH</sub>     | Data hold time after<br>rising edge on<br>DCLK                 | C                               |                             | _                         | -                           | ns     |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode <sup>(5)</sup>                     | 30                              | 0                           | 65                        | 0                           | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                               | 4 × maximum                     | DCLK <b>period</b>          | _                         | -                           | _      |

| t <sub>cd2UMC</sub> | CONF_DONE high to<br>user mode with<br><b>CLKUSR</b> option on | t <sub>CD2CU</sub> + (3,192 × C | lkusr period)               | _                         | -                           | _      |

| t <sub>DSU</sub>    | Data setup time<br>before rising edge<br>on DCLK               | 5                               | 8                           | _                         | _                           | ns     |

| t <sub>CH</sub>     | DCLK high time                                                 | 3.2                             | 6.4                         | _                         | _                           | ns     |

| t <sub>CL</sub>     | DCLK low time                                                  | 3.2                             | 6.4                         | _                         | _                           | ns     |

| t <sub>CLK</sub>    | DCLK period                                                    | 7.5                             | 15                          |                           | _                           | ns     |

| f <sub>MAX</sub>    | DCLK frequency (6)                                             |                                 |                             | 133                       | 66                          | MHz    |

| Table 8-13. FPP T | iming Parameters f | for Cyclone IV Devices | (Part 2 of 2) |

|-------------------|--------------------|------------------------|---------------|

|-------------------|--------------------|------------------------|---------------|

#### Notes to Table 8-13:

(1) Applicable for Cyclone IV GX and Cyclone IV E with 1.2-V core voltage.

(2) Applicable for Cyclone IV E with 1.0-V core voltage.

(3) This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

(4) This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

(5) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.

(6) Cyclone IV E devices with 1.0-V core voltage have slower F<sub>MAX</sub> when compared with Cyclone IV GX devices with 1.2-V core voltage.

## **JTAG Configuration**

JTAG has developed a specification for boundary-scan testing (BST). The BST architecture offers the capability to efficiently test components on PCBs with tight lead spacing. The BST architecture can test pin connections without using physical test probes and capture functional data while a device is normally operating. You can also use the JTAG circuitry to shift configuration data into the device. The Quartus II software automatically generates **.sof** for JTAG configuration with a download cable in the Quartus II software Programmer.

For more information about the JTAG boundary-scan testing, refer to the *JTAG Boundary-Scan Testing for Cyclone IV Devices* chapter.

In AP configuration scheme, the only way to re-engage the AP controller is to issue the ACTIVE\_ENGAGE instruction. In this case, asserting the nCONFIG pin does not reengage either active controller.

#### ACTIVE\_ENGAGE

The ACTIVE\_ENGAGE instruction allows you to re-engage a disengaged active controller. You can issue this instruction any time during configuration or user mode to reengage an already disengaged active controller, as well as trigger reconfiguration of the Cyclone IV device in the active configuration scheme.

The ACTIVE\_ENGAGE instruction functions as the PULSE\_NCONFIG instruction when the device is in the PS or FPP configuration schemes. The nCONFIG pin is disabled when the ACTIVE\_ENGAGE instruction is issued.

Altera does not recommend using the ACTIVE\_ENGAGE instruction, but it is provided as a fail-safe instruction for re-engaging the active configuration controller (AS and AP).

#### **Overriding the Internal Oscillator**

This feature allows you to override the internal oscillator during the active configuration scheme. The AS and AP configuration controllers use the internal oscillator as the clock source. You can change the clock source to CLKUSR through the JTAG instruction.

The EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions toggle on or off whether or not the active clock is sourced from the CLKUSR pin or the internal configuration oscillator. To source the active clock from the CLKUSR pin, issue the EN\_ACTIVE\_CLK instruction. This causes the CLKUSR pin to become the active clock source. When using the EN\_ACTIVE\_CLK instruction, you must enable the internal oscillator for the clock change to occur. By default, the configuration oscillator is disabled after configuration and initialization is complete as well as the device has entered user mode.

However, the internal oscillator is enabled in user mode by any of the following conditions:

- A reconfiguration event (for example, driving the nCONFIG pin to go low)

- Remote update is enabled

- Error detection is enabled

- When using the EN\_ACTIVE\_CLK and DIS\_ACTIVE\_CLK JTAG instructions to override the internal oscillator, you must clock the CLKUSR pin at two times the expected DCLK frequency. The CLKUSR pin allows a maximum frequency of 40 MHz (40 MHz DCLK).

Normally, a test instrument uses the CLKUSR pin when it wants to drive its own clock to control the AS state machine.

To revert the clock source back to the configuration oscillator, issue the DIS\_ACTIVE\_CLK instruction. After you issue the DIS\_ACTIVE\_CLK instruction, you must continue to clock the CLKUSR pin for 10 clock cycles. Otherwise, even toggling the nCONFIG pin does not revert the clock source and reconfiguration does not occur. A POR reverts the clock source back to the configuration oscillator. Toggling the nCONFIG pin or driving the JTAG state machine to reset state does not revert the clock source.

#### CYIV-51009-1.3

This chapter describes the cyclical redundancy check (CRC) error detection feature in user mode and how to recover from soft errors.

Configuration error detection is supported in all Cyclone<sup>®</sup> IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage. However, user mode error detection is only supported in Cyclone IV GX devices and Cyclone IV E devices with 1.2-V core voltage.

Dedicated circuitry built into Cyclone IV devices consists of a CRC error detection feature that can optionally check for a single-event upset (SEU) continuously and automatically.

In critical applications used in the fields of avionics, telecommunications, system control, medical, and military applications, it is important to be able to:

- Confirm the accuracy of the configuration data stored in an FPGA device

- Alert the system to an occurrence of a configuration error

Using the CRC error detection feature for Cyclone IV devices does not impact fitting or performance.

This chapter contains the following sections:

- "Configuration Error Detection" on page 9–1

- "User Mode Error Detection" on page 9–2

- "Automated SEU Detection" on page 9–3

- "CRC\_ERROR Pin" on page 9–3

- "Error Detection Block" on page 9–4

- "Error Detection Timing" on page 9–5

- "Software Support" on page 9–6

- "Recovering from CRC Errors" on page 9–9

## **Configuration Error Detection**

Configuration error detection is available in all Cyclone IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage.

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Cyclone IV Device Handbook, Volume 1 May 2013

# **Contents**

| Chapter Revision Dates                          | vii    |

|-------------------------------------------------|--------|

| Additional Information                          |        |

| How to Contact Altera                           | Info–1 |

| Typographic Conventions                         |        |

| Section I. Transceivers                         |        |

| Chapter 1. Cyclone IV Transceivers Architecture |        |

| Transceiver Architecture                        |        |

| Architectural Overview                          |        |

| Transmitter Channel Datapath                    |        |

| TX Phase Compensation FIFO                      |        |

| Byte Serializer                                 |        |

| 8B/10B Encoder                                  |        |

| Miscellaneous Transmitter PCS Features          |        |

| Serializer                                      |        |

| Transmitter Output Buffer                       |        |

| Receiver Channel Datapath                       |        |

| Receiver Input Buffer                           |        |

| Clock Data Recovery                             |        |

| Automatic Lock Mode                             |        |

| Manual Lock Mode                                |        |

| Deserializer                                    |        |

| Word Aligner                                    |        |

| Deskew FIFO                                     |        |

| Rate Match FIFO                                 |        |

| 8B/10B Decoder                                  |        |

| Byte Deserializer                               |        |

| Byte Ordering                                   |        |

| RX Phase Compensation FIFO                      |        |

| Miscellaneous Receiver PCS Feature              |        |

| Transceiver Clocking Architecture               |        |

| Input Reference Clocking                        |        |

| Transceiver Channel Datapath Clocking           |        |

| Non-Bonded Channel Configuration                |        |

| Bonded Channel Configuration                    |        |

| FPGA Fabric-Transceiver Interface Clocking      |        |

| Calibration Block                               |        |

| PCI-Express Hard IP Block                       |        |

| Transceiver Functional Modes                    |        |

| Basic Mode                                      |        |

| Rate Match FIFO Operation in Basic Mode         |        |

| Additional Options in Basic Mode                |        |

| PCI Express (PIPE) Mode                         |        |

| PIPE Interface                                  |        |

| Receiver Detection Circuitry                    |        |

| Electrical Idle Control                         |        |

## BIST

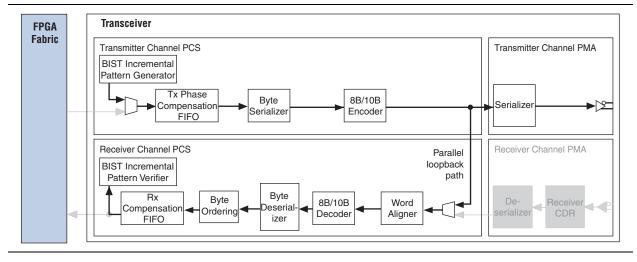

Figure 1–73 shows the datapath for BIST incremental data pattern test mode. The BIST incremental data generator and verifier are located near the FPGA fabric in the PCS block of the transceiver channel.

Figure 1–73. BIST Incremental Pattern Test Mode Datapath

The incremental pattern generator and verifier are 16-bits wide. The generated pattern increments from 00 to FF and passes through the TX PCS blocks, parallel looped back to RX PCS blocks, and checked by the verifier. The pattern is also available as serial data at the tx\_dataout port. The differential output voltage of the transmitted serial data on the tx\_dataout port is based on the selected  $V_{OD}$  settings. The incremental data pattern is not available to the FPGA logic at the receiver for verification.

The following are the transceiver channel configuration settings in this mode:

- PCS-FPGA fabric channel width: 16-bit

- 8B/10B blocks: Enabled

- Byte serializer/deserializer: Enabled

- Word aligner: Automatic synchronization state machine mode

- Byte ordering: Enabled

The rx\_bisterr and rx\_bistdone signals indicate the status of the verifier. The rx\_bisterr signal is asserted and stays high when detecting an error in the data. The rx\_bistdone signal is asserted and stays high when the verifier either receives a full cycle of incremental pattern or it detects an error in the receiver data. You can reset the incremental pattern generator and verifier by asserting the tx\_digitalreset and rx\_digitalreset ports, respectively.

| Symbol                                                | Parameter                                                                                                                      | Min | Тур     | Max  | Unit              |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|-------------------|

| t <sub>DLOCK</sub>                                    | Time required to lock dynamically (after switchover, reconfiguring any non-post-scale counters/delays or areset is deasserted) |     | _       | 1    | ms                |

| t <sub>outjitter_period_dedclk</sub> (6)              | Dedicated clock output period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                             |     | _       | 300  | ps                |

|                                                       | F <sub>OUT</sub> < 100 MHz                                                                                                     | —   |         | 30   | mUI               |

| toutjitter_ccj_dedclk <sup>(6)</sup>                  | Dedicated clock output cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                     | _   | _       | 300  | ps                |

|                                                       | F <sub>OUT</sub> < 100 MHz                                                                                                     | —   | —       | 30   | mUI               |

| t <sub>outjitter_period_io</sub> (6)                  | Regular I/O period jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                        | _   | _       | 650  | ps                |

|                                                       | F <sub>OUT</sub> < 100 MHz                                                                                                     | —   | —       | 75   | mUI               |

| t <sub>outjitter_ccj_io</sub> (6)                     | Regular I/O cycle-to-cycle jitter $F_{OUT} \ge 100 \text{ MHz}$                                                                | _   | _       | 650  | ps                |

|                                                       | F <sub>OUT</sub> < 100 MHz                                                                                                     | —   | —       | 75   | mUI               |

| t <sub>PLL_PSERR</sub>                                | Accuracy of PLL phase shift                                                                                                    |     |         | ±50  | ps                |

| t <sub>ARESET</sub>                                   | Minimum pulse width on areset signal. 10 —                                                                                     |     | —       | ns   |                   |

| t <sub>configpll</sub>                                | Time required to reconfigure scan chains for PLLs                                                                              | _   | 3.5 (7) | _    | SCANCLK<br>cycles |

| f <sub>scanclk</sub>                                  | scanclk frequency —                                                                                                            |     |         | 100  | MHz               |

| t <sub>CASC_OUTJITTER_PERIOD_DEDCLK</sub><br>(8), (9) | Period jitter for dedicated clock output in cascaded PLLs ( $F_{OUT} \ge 100 \text{ MHz}$ )                                    | -   | _       | 425  | ps                |

|                                                       | Period jitter for dedicated clock output in cascaded PLLs (F <sub>OUT</sub> < 100 MHz)                                         | -   | _       | 42.5 | mUI               |

| Table 1-25. | PLL Specifications | for Cyclone IV Device | S <sup>(1),</sup> (2) | (Part 2 of 2) |

|-------------|--------------------|-----------------------|-----------------------|---------------|

|-------------|--------------------|-----------------------|-----------------------|---------------|

#### Notes to Table 1-25:

- (1) This table is applicable for general purpose PLLs and multipurpose PLLs.

- (2) You must connect  $V_{CCD PLL}$  to  $V_{CCINT}$  through the decoupling capacitor and ferrite bead.

- (3) This parameter is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

- (4) The V<sub>C0</sub> frequency reported by the Quartus II software in the PLL Summary section of the compilation report takes into consideration the V<sub>C0</sub> post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VC0</sub> specification.

- (5) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source that is less than 200 ps.

- (6) Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.9999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL when an input jitter of 30 ps is applied.

- (7) With 100-MHz scanclk frequency.

(8) The cascaded PLLs specification is applicable only with the following conditions:

- Upstream PLL—0.59 MHz ≤ Upstream PLL bandwidth < 1 MHz

- Downstream PLL—Downstream PLL bandwidth > 2 MHz

- (9) PLL cascading is not supported for transceiver applications.