Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 7155                                                      |

| Number of Logic Elements/Cells | 114480                                                    |

| Total RAM Bits                 | 3981312                                                   |

| Number of I/O                  | 528                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 0.97V ~ 1.03V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 780-BGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29i8l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

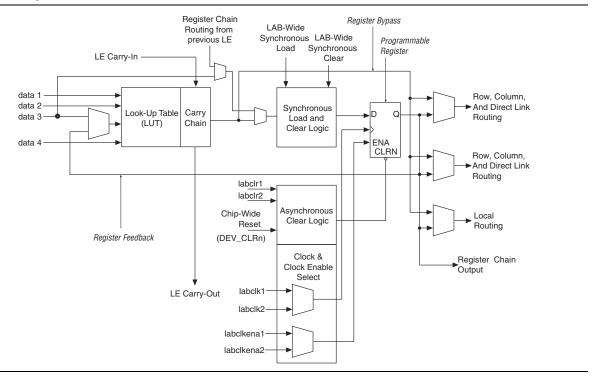

Figure 2–1 shows the LEs for Cyclone IV devices.

Figure 2–1. Cyclone IV Device LEs

## **LE Features**

You can configure the programmable register of each LE for D, T, JK, or SR flipflop operation. Each register has data, clock, clock enable, and clear inputs. Signals that use the global clock network, general-purpose I/O pins, or any internal logic can drive the clock and clear control signals of the register. Either general-purpose I/O pins or the internal logic can drive the clock enable. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output independently drives these three outputs. Two LE outputs drive the column or row and direct link routing connections, while one LE drives the local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. The LAB-wide synchronous load control signal is not available when using register packing. For more information about the synchronous load control signal, refer to "LAB Control Signals" on page 2-6.

The register feedback mode allows the register output to feed back into the LUT of the same LE to ensure that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

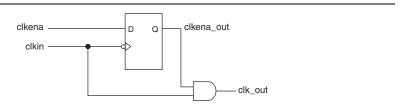

Figure 5–7 shows how to implement the clkena signal with a single register.

Figure 5-7. clkena Implementation

The clkena circuitry controlling the output C0 of the PLL to an output pin is implemented with two registers instead of a single register, as shown in Figure 5–7.

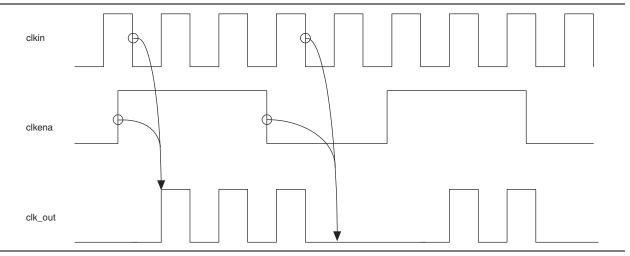

Figure 5–8 shows the waveform example for a clock output enable. The clkena signal is sampled on the falling edge of the clock (clkin).

This feature is useful for applications that require low power or sleep mode.

Figure 5-8. clkena Implementation: Output Enable

The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during PLL resynchronization.

Altera recommends using the clkena signals when switching the clock source to the PLLs or the GCLK. The recommended sequence is:

- 1. Disable the primary output clock by de-asserting the clkena signal.

- 2. Switch to the secondary clock using the dynamic select signals of the clock control block.

- 3. Allow some clock cycles of the secondary clock to pass before reasserting the clkena signal. The exact number of clock cycles you must wait before enabling the secondary clock is design-dependent. You can build custom logic to ensure glitch-free transition when switching between different clock sources.

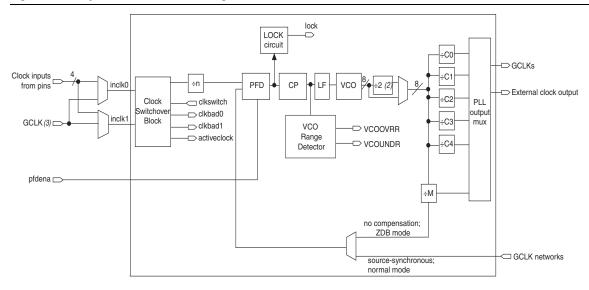

Figure 5–10 shows a simplified block diagram of the major components of the PLL of Cyclone IV E devices.

Figure 5–10. Cyclone IV E PLL Block Diagram (1)

#### Notes to Figure 5-10:

- (1) Each clock source can come from any of the four clock pins located on the same side of the device as the PLL.

- (2) This is the VCO post-scale counter K.

- (3) This input port is fed by a pin-driven dedicated GCLK, or through a clock control block if the clock control block is fed by an output from another PLL or a pin-driven dedicated GCLK. An internally generated global signal cannot drive the PLL.

The VCO post-scale counter K is used to divide the supported VCO range by two. The VCO frequency reported by the Quartus II software in the PLL summary section of the compilation report takes into consideration the VCO post-scale counter value. Therefore, if the VCO post-scale counter has a value of 2, the frequency reported is lower than the  $f_{\text{VCO}}$  specification specified in the *Cyclone IV Device Datasheet* chapter.

# **External Clock Outputs**

Each PLL of Cyclone IV devices supports one single-ended clock output or one differential clock output. Only the C0 output counter can feed the dedicated external clock outputs, as shown in Figure 5–11, without going through the GCLK. Other output counters can feed other I/O pins through the GCLK.

# **Programmable Bandwidth**

The PLL bandwidth is the measure of the PLL's ability to track the input clock and its associated jitter. PLLs of Cyclone IV devices provide advanced control of the PLL bandwidth using the programmable characteristics of the PLL loop, including loop filter and charge pump. The closed-loop gain 3-dB frequency in the PLL determines the PLL bandwidth. The bandwidth is approximately the unity gain point for open loop PLL response.

# **Phase Shift Implementation**

Phase shift is used to implement a robust solution for clock delays in Cyclone IV devices. Phase shift is implemented with a combination of the VCO phase output and the counter starting time. The VCO phase output and counter starting time are the most accurate methods of inserting delays, because they are based only on counter settings that are independent of process, voltage, and temperature.

You can phase shift the output clocks from the PLLs of Cyclone IV devices in one of two ways:

- Fine resolution using VCO phase taps

- Coarse resolution using counter starting time

Fine resolution phase shifts are implemented by allowing any of the output counters (C[4..0]) or the M counter to use any of the eight phases of the VCO as the reference clock. This allows you to adjust the delay time with a fine resolution.

Equation 5–1 shows the minimum delay time that you can insert using this method.

### **Equation 5–1. Fine Resolution Phase Shift**

$$f_{\text{fine}} = \frac{T_{VCO}}{8} = \frac{1}{8f_{VCO}} = \frac{N}{8Mf_{REF}}$$

in which  $f_{REF}$  is the input reference clock frequency.

For example, if  $f_{REF}$  is 100 MHz, N = 1, and M = 8, then  $f_{VCO}$  = 800 MHz, and  $\Phi_{fine}$  = 156.25 ps. The PLL operating frequency defines this phase shift, a value that depends on reference clock frequency and counter settings.

Coarse resolution phase shifts are implemented by delaying the start of the counters for a predetermined number of counter clocks. Equation 5–2 shows the coarse phase shift.

#### **Equation 5–2. Coarse Resolution Phase Shift**

$$\Phi_{\text{coarse}} = \frac{C - 1}{f_{VCO}} = \frac{(C - 1)N}{Mf_{REF}}$$

C is the count value set for the counter delay time (this is the initial setting in the PLL usage section of the compilation report in the Quartus II software). If the initial value is 1,  $C - 1 = 0^{\circ}$  phase shift.

- Low time count = 1 cycle

- rselodd = 1 effectively equals:

- High time count = 1.5 cycles

- Low time count = 1.5 cycles

- Duty cycle = (1.5/3)% high time count and (1.5/3)% low time count

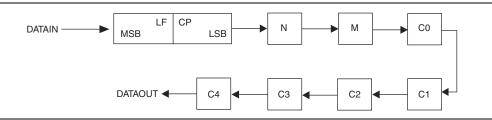

## **Scan Chain Description**

Cyclone IV PLLs have a 144-bit scan chain.

Table 5–7 lists the number of bits for each component of the PLL.

Table 5-7. Cyclone IV PLL Reprogramming Bits

| Die als Name               | Number of Bits            |       |       |  |  |  |  |  |  |  |  |

|----------------------------|---------------------------|-------|-------|--|--|--|--|--|--|--|--|

| Block Name                 | Counter                   | Other | Total |  |  |  |  |  |  |  |  |

| C4 <sup>(1)</sup>          | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| C3                         | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| C2                         | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| C1                         | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| CO                         | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| M                          | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| N                          | 16                        | 2 (2) | 18    |  |  |  |  |  |  |  |  |

| Charge Pump                | 9                         | 0     | 9     |  |  |  |  |  |  |  |  |

| Loop Filter <sup>(3)</sup> | 9                         | 0     | 9     |  |  |  |  |  |  |  |  |

| Total number of bits:      | Total number of bits: 144 |       |       |  |  |  |  |  |  |  |  |

#### Notes to Table 5-7:

- (1) LSB bit for C4 low-count value is the first bit shifted into the scan chain.

- (2) These two control bits include rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

- (3) MSB bit for loop filter is the last bit shifted into the scan chain.

Figure 5–24 shows the scan chain order of the PLL components.

Figure 5-24. PLL Component Scan Chain Order

Table 6-3. Cyclone IV Devices Supported I/O Standards and Constraints (Part 2 of 3)

|                                             |                        |                      | V <sub>CCIO</sub> Leve | el (in V) | C        | olumn I/O P                   | ins                 | Row I/O Pins (1) |                  |  |

|---------------------------------------------|------------------------|----------------------|------------------------|-----------|----------|-------------------------------|---------------------|------------------|------------------|--|

| I/O Standard                                | Туре                   | Standard<br>Support  | Input                  | ıt Output |          | PLL_OUT                       | User<br>I/O<br>Pins | CLK,<br>DQS      | User I/O<br>Pins |  |

| 2.5-V LVTTL /<br>LVCMOS                     | Single-ended           | JESD8-5              | 3.3/3.0/2.5<br>(3)     | 2.5       | ~        | ~                             | ✓                   | ~                | ~                |  |

| 1.8-V LVTTL /<br>LVCMOS                     | Single-ended           | JESD8-7              | 1.8/1.5 <sup>(3)</sup> | 1.8       | ~        | ~                             | ✓                   | ~                | ~                |  |

| 1.5-V LVCMOS                                | Single-ended           | JESD8-11             | 1.8/1.5 (3)            | 1.5       | <b>✓</b> | ✓                             | <b>✓</b>            | ✓                | ~                |  |

| 1.2-V LVCMOS (4)                            | Single-ended           | JESD8-12A            | 1.2                    | 1.2       | ✓        | <b>✓</b>                      | <b>✓</b>            | ✓                | ~                |  |

| SSTL-2 Class I,<br>SSTL-2 Class II          | voltage-<br>referenced | JESD8-9A             | 2.5                    | 2.5       | ~        | ~                             | <b>✓</b>            | ~                | ✓                |  |

| SSTL-18 Class I,<br>SSTL-18 Class II        | voltage-<br>referenced | JESD815              | 1.8                    | 1.8       | ~        | ~                             | <b>✓</b>            | ~                | <b>✓</b>         |  |

| HSTL-18 Class I,<br>HSTL-18 Class II        | voltage-<br>referenced | JESD8-6              | 1.8                    | 1.8       | ~        | ~                             | <b>✓</b>            | ~                | ~                |  |

| HSTL-15 Class I,<br>HSTL-15 Class II        | voltage-<br>referenced | JESD8-6              | 1.5                    | 1.5       | ~        | ~                             | <b>✓</b>            | ~                | ~                |  |

| HSTL-12 Class I                             | voltage-<br>referenced | JESD8-16A            | 1.2                    | 1.2       | ~        | ~                             | ✓                   | ~                | ~                |  |

| HSTL-12 Class II (9)                        | voltage-<br>referenced | JESD8-16A            | 1.2                    | 1.2       | ~        | ~                             | ✓                   | _                | _                |  |

| PCI and PCI-X                               | Single-ended           | _                    | 3.0                    | 3.0       | <b>✓</b> | ✓                             | <b>✓</b>            | <b>✓</b>         | ✓                |  |

| Differential SSTL-2                         | Differential           | JESD8-9A             | _                      | 2.5       | _        | <b>✓</b>                      | -                   | _                | _                |  |

| Class I or Class II                         | (5)                    | JEODO-JA             | 2.5                    | _         | <b>✓</b> | _                             |                     | <b>✓</b>         | _                |  |

| Differential SSTL-18                        | Differential           | JESD815              | _                      | 1.8       | _        | ✓                             | _                   | _                | _                |  |

| Class I or Class II                         | (5)                    | 0200010              | 1.8                    |           | <b>✓</b> | _                             |                     | <b>✓</b>         |                  |  |

| Differential HSTL-18                        | Differential           | JESD8-6              | _                      | 1.8       |          | <b>✓</b>                      | _                   | _                | _                |  |

| Class I or Class II                         | (5)                    | 02000                | 1.8                    |           | <b>✓</b> | _                             |                     | ✓                |                  |  |

| Differential HSTL-15                        | Differential           | JESD8-6              | _                      | 1.5       |          | <b>✓</b>                      |                     | _                |                  |  |

| Class I or Class II                         | (5)                    | 02000                | 1.5                    | _         | <b>✓</b> | _                             | _                   | ✓                | _                |  |

| Differential HSTL-12<br>Class I or Class II | Differential (5)       | JESD8-16A            | 1.2                    | 1.2       | <u> </u> | <ul><li>✓</li><li>—</li></ul> | _                   | <u> </u>         | _                |  |

| PPDS (6)                                    | Differential           | _                    | _                      | 2.5       | _        | <b>✓</b>                      | <b>✓</b>            | _                | <b>✓</b>         |  |

| LVDS (10)                                   | Differential           | ANSI/TIA/<br>EIA-644 | 2.5                    | 2.5       | ~        | ~                             | ✓                   | ~                | ~                |  |

| RSDS and mini-LVDS (6)                      | Differential           | _                    | _                      | 2.5       | _        | ~                             | <b>✓</b>            | _                | ~                |  |

| BLVDS (8)                                   | Differential           | _                    | 2.5                    | 2.5       | _        | _                             | <b>✓</b>            | _                | ~                |  |

# 8. Configuration and Remote System Upgrades in Cyclone IV Devices

CYIV-51008-1.7

This chapter describes the configuration and remote system upgrades in Cyclone<sup>®</sup> IV devices. Cyclone IV (Cyclone IV GX and Cyclone IV E) devices use SRAM cells to store configuration data. You must download the configuration data to Cyclone IV devices each time the device powers up because SRAM memory is volatile.

Cyclone IV devices are configured using one of the following configuration schemes:

- Active serial (AS)

- Active parallel (AP) (supported in Cyclone IV E devices only)

- Passive serial (PS)

- Fast passive parallel (FPP) (not supported in EP4CGX15, EP4CGX22, and EP4CGX30 [except for the F484 package] devices)

- JTAG

Cyclone IV devices offer the following configuration features:

- Configuration data decompression ("Configuration Data Decompression" on page 8–2)

- Remote system upgrade ("Remote System Upgrade" on page 8–69)

System designers face difficult challenges, such as shortened design cycles, evolving standards, and system deployments in remote locations. Cyclone IV devices help overcome these challenges with inherent re-programmability and dedicated circuitry to perform remote system upgrades. Remote system upgrades help deliver feature enhancements and bug fixes without costly recalls, reduced time-to-market, and extended product life.

# **Configuration**

This section describes Cyclone IV device configuration and includes the following topics:

- "Configuration Features" on page 8–2

- "Configuration Requirement" on page 8–3

- "Configuration Process" on page 8–6

- "Configuration Scheme" on page 8–8

- "AS Configuration (Serial Configuration Devices)" on page 8–10

- "AP Configuration (Supported Flash Memories)" on page 8–21

- "PS Configuration" on page 8–32

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

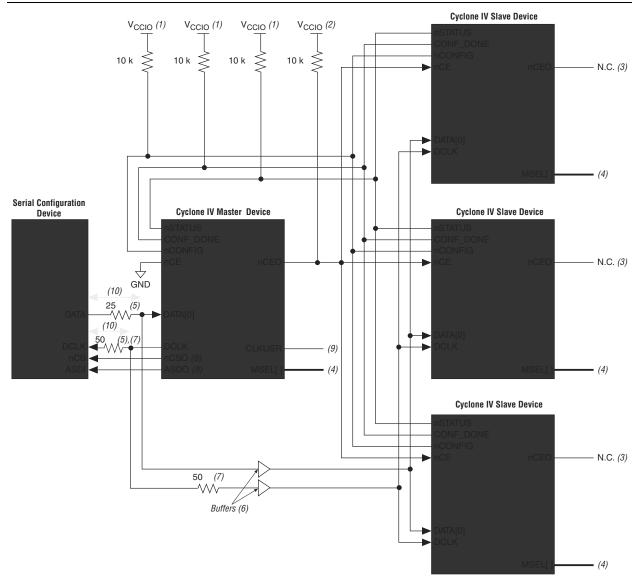

Figure 8–4. Multi-Device AS Configuration in Which Devices Receive the Same Data with Multiple .sof

#### Notes to Figure 8-4:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{\text{CCIO}}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AS mode and the slave devices in PS mode. To connect the MSEL pins for the master device in AS mode and the slave devices in PS mode, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the master and slave devices for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- (8) These pins are dual-purpose I/O pins. The nCSO pin functions as FLASH\_nCE pin in AP mode. The ASDO pin functions as DATA [1] pin in AP and FPP modes.

- (9) Only Cyclone IV GX devices have an option to select CLKUSR (40 MHz maximum) as the external clock source for DCLK.

- (10) For multi-devices AS configuration using Cyclone IV E with 1,0 V core voltage, the maximum board trace-length from the serial configuration device to the junction-split on both DCLK and Data0 line is 3.5 inches.

Table 8–8 provides the configuration time for AS configuration.

Table 8–8. AS Configuration Time for Cyclone IV Devices (1)

| Symbol          | Parameter            | Cyclone IV E | Cyclone IV GX | Unit |

|-----------------|----------------------|--------------|---------------|------|

| t <sub>SU</sub> | Setup time           | 10           | 8             | ns   |

| t <sub>H</sub>  | Hold time            | 0            | 0             | ns   |

| t <sub>co</sub> | Clock-to-output time | 4            | 4             | ns   |

#### Note to Table 8-8:

(1) For the AS configuration timing diagram, refer to the Serial Configuration (EPCS) Devices Datasheet.

Enabling compression reduces the amount of configuration data that is sent to the Cyclone IV device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

## **Programming Serial Configuration Devices**

Serial configuration devices are non-volatile, flash memory-based devices. You can program these devices in-system with the USB-Blaster<sup>TM</sup> or ByteBlaster<sup>TM</sup> II download cables. Alternatively, you can program them with the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices through the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone IV devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive  $\rm V_{CC}$  and GND, respectively.

To perform in-system programming of a serial configuration device through the AS programming interface, you must place the diodes and capacitors as close as possible to the Cyclone IV device. You must ensure that the diodes and capacitors maintain a maximum AC voltage of 4.1 V (Figure 8–6).

If you want to use the setup shown in Figure 8–6 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not require a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone IV device that uses its JTAG interface to access the EPCS JIC (JTAG Indirect Configuration Device Programming) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design.

For more information about implementing the SFL with Cyclone IV devices, refer to AN 370: Using the Serial FlashLoader with the Quartus II Software.

May 2013 Altera Corporation

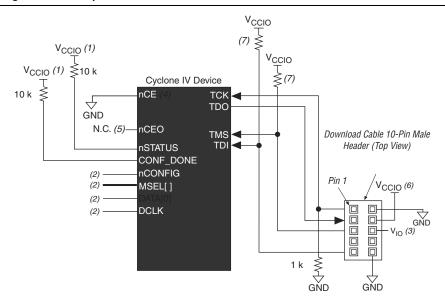

Figure 8–24. JTAG Configuration of a Single Device Using a Download Cable (1.5-V or 1.8-V  $V_{\text{CCIO}}$  Powering the JTAG Pins)

#### Notes to Figure 8-24:

- (1) Connect these pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) Connect the nCONFIG and MSEL pins to support a non-JTAG configuration scheme. If you only use JTAG configuration, connect the nCONFIG pin to logic-high and the MSEL pins to GND. In addition, pull DCLK and DATA[0] to either high or low, whichever is convenient on your board.

- (3) In the USB-Blaster and ByteBlaster II cables, this pin is connected to nce when it is used for AS programming; otherwise it is a no connect.

- (4) The nce must be connected to GND or driven low for successful JTAG configuration.

- (5) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (6) Power up the V<sub>CC</sub> of the EthernetBlaster, ByteBlaster II or USB-Blaster cable with supply from V<sub>CCIO</sub>. The Ethernet-Blaster, ByteBlaster II, and USB-Blaster cables do not support a target supply voltage of 1.2 V. For the target supply voltage value, refer to the ByteBlaster II Download Cable User Guide, the USB-Blaster Download Cable User Guide, and the EthernetBlaster Communications Cable User Guide.

- (7) Resistor value can vary from 1 k $\Omega$  to 10 k $\Omega$ .

To configure a single device in a JTAG chain, the programming software places all other devices in bypass mode. In bypass mode, devices pass programming data from the TDI pin to the TDO pin through a single bypass register without being affected internally. This scheme enables the programming software to program or verify the target device. Configuration data driven into the device appears on the TDO pin one clock cycle later.

The Quartus II software verifies successful JTAG configuration after completion. At the end of configuration, the software checks the state of CONF\_DONE through the JTAG port. When Quartus II generates a .jam for a multi-device chain, it contains instructions so that all the devices in the chain are initialized at the same time. If CONF\_DONE is not high, the Quartus II software indicates that configuration has failed. If CONF\_DONE is high, the software indicates that configuration was successful. After the configuration bitstream is serially sent using the JTAG TDI port, the TCK port clocks an additional clock cycles to perform device initialization.

Table 8–21 lists the optional configuration pins. If you do not enable these optional configuration pins in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

Table 8-21. Optional Configuration Pins

| Pin Name  | User Mode                                     | Pin Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | N/A if option is on.                          |                      | Optional user-supplied clock input synchronizes the initialization of one or more devices. This pin is enabled by turning on the <b>Enable user-supplied start-up clock (CLKUSR)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLKUSR    | I/O if option is off.                         | Input                | In AS configuration for Cyclone IV GX devices, you can use this pin as an external clock source to generate the DCLK by changing the clock source option in the Quartus II software in the <b>Configuration</b> tab of the <b>Device and Pin Options</b> dialog box.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| INIT_DONE | N/A if option is on.<br>I/O if option is off. | Output<br>open-drain | Status pin is used to indicate when the device has initialized and is in user-mode. When nconfig is low, the INIT_DONE pin is tri-stated and pulled high due to an external 10-k $\Omega$ pull-up resistor during the beginning of configuration. After the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the INIT_DONE pin goes low. When initialization is complete, the INIT_DONE pin is released and pulled high and the device enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |

|           |                                               |                      | The functionality of this pin changes if the <b>Enable OCT_DONE</b> option is enabled in the Quartus II software. This option controls whether the INIT_DONE signal is gated by the OCT_DONE signal, which indicates the power-up on-chip termination (OCT) calibration is complete. If this option is turned off, the INIT_DONE signal is not gated by the OCT_DONE signal.                                                                                                                                                                                                                                                                                                                                 |

| DEV_OE    | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as programmed. This pin is enabled by turning on the <b>Enable device-wide output enable (DEV_OE)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                  |

| DEV_CLRn  | N/A if option is on.<br>I/O if option is off. | Input                | Optional pin that allows you to override all clears on all device registers. When this pin is driven low, all registers are cleared; when this pin is driven high, all registers behave as programmed. You can enable this pin by turning on the <b>Enable device-wide reset (DEV_CLRn)</b> option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                               |

# 9. SEU Mitigation in Cyclone IV Devices

#### CYIV-51009-1.3

This chapter describes the cyclical redundancy check (CRC) error detection feature in user mode and how to recover from soft errors.

Configuration error detection is supported in all Cyclone<sup>®</sup> IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage. However, user mode error detection is only supported in Cyclone IV GX devices and Cyclone IV E devices with 1.2-V core voltage.

Dedicated circuitry built into Cyclone IV devices consists of a CRC error detection feature that can optionally check for a single-event upset (SEU) continuously and automatically.

In critical applications used in the fields of avionics, telecommunications, system control, medical, and military applications, it is important to be able to:

- Confirm the accuracy of the configuration data stored in an FPGA device

- Alert the system to an occurrence of a configuration error

Using the CRC error detection feature for Cyclone IV devices does not impact fitting or performance.

This chapter contains the following sections:

- "Configuration Error Detection" on page 9–1

- "User Mode Error Detection" on page 9–2

- "Automated SEU Detection" on page 9–3

- "CRC\_ERROR Pin" on page 9–3

- "Error Detection Block" on page 9–4

- "Error Detection Timing" on page 9–5

- "Software Support" on page 9–6

- "Recovering from CRC Errors" on page 9–9

## **Configuration Error Detection**

Configuration error detection is available in all Cyclone IV devices including Cyclone IV GX devices, Cyclone IV E devices with 1.0-V core voltage, and Cyclone IV E devices with 1.2-V core voltage.

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

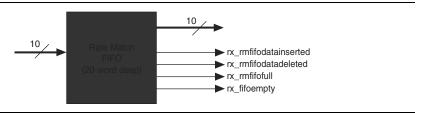

## **Rate Match FIF0**

In asynchronous systems, the upstream transmitter and local receiver can be clocked with independent reference clocks. Frequency differences in the order of a few hundred ppm can corrupt the data when latching from the recovered clock domain (the same clock domain as the upstream transmitter reference clock) to the local receiver reference clock domain. Figure 1–21 shows the rate match FIFO block diagram.

Figure 1-21. Rate Match FIFO Block Diagram

The rate match FIFO compensates for small clock frequency differences of up to  $\pm 300$  ppm (600 ppm total) between the upstream transmitter and the local receiver clocks by performing the following functions:

- Insert skip symbols when the local receiver reference clock frequency is greater than the upstream transmitter reference clock frequency

- Delete skip symbols when the local receiver reference clock frequency is less than the upstream transmitter reference clock frequency

The 20-word deep rate match FIFO and logics control insertion and deletion of skip symbols, depending on the ppm difference. The operation begins after the word aligner synchronization status (rx syncstatus) is asserted.

Rate match FIFO is only supported with 8B/10B encoded data and the word aligner in automatic synchronization state machine mode.

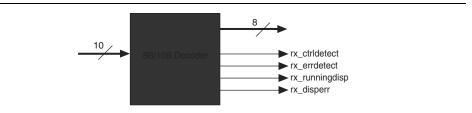

## 8B/10B Decoder

The 8B/10B decoder receives 10-bit data and decodes it into an 8-bit data and a 1-bit control identifier. The decoder is compliant with Clause 36 of the IEEE 802.3 specification.

Figure 1–22 shows the 8B/10B decoder block diagram.

Figure 1–22. 8B/10B Decoder Block Diagram

## **Clock Rate Compensation**

In XAUI mode, the rate match FIFO compensates up to  $\pm 100$  ppm (200 ppm total) difference between the upstream transmitter and the local receiver reference clock. The XAUI protocol requires the transmitter to send /R/ (/K28.0/) code groups simultaneously on all four lanes (denoted as |R| column) during inter-packet gaps, adhering to rules listed in the IEEE P802.3ae specification.

The rate match operation begins after rx\_syncstatus and rx\_channelaligned are asserted. The rx\_syncstatus signal is from the word aligner, indicating that synchronization is acquired on all four channels, while rx\_channelaligned signal is from the deskew FIFO, indicating channel alignment.

The rate match FIFO looks for the |R| column (simultaneous R code groups on all four channels) and deletes or inserts |R| columns to prevent the rate match FIFO from overflowing or under running. The rate match FIFO can insert or delete as many |R| columns as necessary to perform the rate match operation.

The rx\_rmfifodatadeleted and rx\_rmfifodatainserted flags that indicate rate match FIFO deletion and insertion events, respectively, are forwarded to the FPGA fabric. If an | |R| | column is deleted, the rx\_rmfifodeleted flag from each of the four channels goes high for one clock cycle per deleted | |R| | column. If an | |R| | column is inserted, the rx\_rmfifoinserted flag from each of the four channels goes high for one clock cycle per inserted | |R| | column.

The rate match FIFO does not insert or delete code groups automatically to overcome FIFO empty or full conditions. In this case, the rate match FIFO asserts the rx\_rmfifofull and rx\_rmfifoempty flags for at least three recovered clock cycles to indicate rate match FIFO full and empty conditions, respectively. You must then assert the rx\_digitalreset signal to reset the receiver PCS blocks.

# **Deterministic Latency Mode**

Deterministic Latency mode provides the transceiver configuration that allows no latency uncertainty in the datapath and features to strictly control latency variation. This mode supports non-bonded (×1) and bonded (×4) channel configurations, and is typically used to support CPRI and OBSAI protocols that require accurate delay measurements along the datapath. The Cyclone IV GX transceivers configured in Deterministic Latency mode provides the following features:

- registered mode phase compensation FIFO

- receive bit-slip indication

- transmit bit-slip control

- PLL PFD feedback

Table 1–28. PIPE Interface Ports in ALTGX Megafunction for Cyclone IV GX (1) (Part 1 of 2)

| Port Name                  | Input/<br>Output | Clock Domain            | Description                                                                                                                                                                                                                                                                    |

|----------------------------|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fixedclk                   | Input            | Clock signal            | 125-MHz clock for receiver detect and offset cancellation only in PIPE mode.                                                                                                                                                                                                   |

|                            |                  |                         | Receiver detect or reverse parallel loopback control.                                                                                                                                                                                                                          |

| tx_detectrxloop            | Input            | Asynchronous signal     | ■ A high level in the P1 power state and tx_forceelecidle signal asserted begins the receiver detection operation to determine if there is a valid receiver downstream. This signal must be deasserted when the pipephydonestatus signal indicates receiver detect completion. |

|                            |                  |                         | ■ A high level in the PO power state with the tx_forceelecidle signal deasserted dynamically configures the channel to support reverse parallel loopback mode.                                                                                                                 |

|                            |                  |                         | Force the 8B/10B encoder to encode with negative running disparity.                                                                                                                                                                                                            |

| tx_forcedisp<br>compliance | Input            | Asynchronous signal     | Assert only when transmitting the first byte of the PIPE-compliance<br>pattern to force the 8B/10B encoder with a negative running<br>disparity.                                                                                                                               |

| pipe8b10binvpolarity       | Input            | Asynchronous signal     | Invert the polarity of every bit of the 10-bit input to the 8B/10B decoder                                                                                                                                                                                                     |

|                            |                  |                         | PIPE power state control.                                                                                                                                                                                                                                                      |

|                            |                  |                         | ■ Signal is 2 bits wide and is encoded as follows:                                                                                                                                                                                                                             |

| powerdn                    | Input            | Asynchronous signal     | ■ 2'b00: P0 (Normal operation)                                                                                                                                                                                                                                                 |

| powerun                    | IIIput           | Asylicili ollous signal | <ul><li>2'b01: P0s (Low recovery time latency, low power state)</li></ul>                                                                                                                                                                                                      |

|                            |                  |                         | <ul><li>2'b10: P1 (Longer recovery time latency, lower power state)</li></ul>                                                                                                                                                                                                  |

|                            |                  |                         | <ul><li>2'b11: P2 (Lowest power state)</li></ul>                                                                                                                                                                                                                               |

| pipedatavalid              | Output           | N/A                     | Valid data and control on the rx_dataout and rx_ctrldetect ports indicator.                                                                                                                                                                                                    |

|                            |                  |                         | PHY function completion indicator.                                                                                                                                                                                                                                             |

| pipephydone<br>status      | Output           | Asynchronous signal     | Asserted for one clock cycle to communicate completion of several<br>PHY functions, such as power state transition and receiver<br>detection.                                                                                                                                  |

|                            |                  |                         | Electrical idle detected or inferred at the receiver indicator.                                                                                                                                                                                                                |

| pipeelecidle               | Output           | Asynchronous signal     | <ul> <li>When electrical idle inference is used, this signal is driven high<br/>when it infers an electrical idle condition</li> </ul>                                                                                                                                         |

|                            |                  |                         | ■ When electrical idle inference is not used, the rx_signaldetect signal is inverted and driven on this port.                                                                                                                                                                  |

Table 3-1. Glossary of Terms Used in this Chapter (Part 2 of 2)

| Term                                                     | Description                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | A file with the .mif extension will be generated for .mif-based reconfiguration mode. It can be either in Channel Reconfiguration mode or PLL Reconfiguration mode.                                                                                                                                                                                 |

| Memory Initialization File,<br>also known as <b>.mif</b> | ■ Channel Reconfiguration mode—this file contains information about the various ALTGX MegaWizard Plug-In Manager options that you set. Each word in the .mif is 16 bits wide. The dynamic reconfiguration controller writes information from the .mif into the transceiver channel.                                                                 |

|                                                          | ■ PLL Reconfiguration mode—this file contains information about the various PLL parameters and settings that you use to configure the transceiver PLL to different output frequency. The .mif file is 144 × 1-bit size. During PLL reconfiguration mode, the PLL reconfiguration controller shifts these 144-bit serially into the transceiver PLL. |

| PMA controls                                             | Represents analog controls (Voltage Output Differential [VoD], Pre-emphasis, DC Gain, and Manual Equalization) as displayed in both the ALTGX and ALTGX_RECONFIG MegaWizard Plug-In Managers.                                                                                                                                                       |

| Transceiver channel                                      | Refers to a transmitter channel, a receiver channel, or a duplex channel that has both PMA and PCS blocks.                                                                                                                                                                                                                                          |

# **Dynamic Reconfiguration Controller Architecture**

The dynamic reconfiguration controller is a soft intellectual property (IP) that utilizes FPGA-fabric resources. You can use only one controller per transceiver block. You cannot use the dynamic reconfiguration controller to control multiple Cyclone IV devices or any off-chip interfaces.

Cyclone IV E industrial devices I7 are offered with extended operating temperature range.

## **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Cyclone IV devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied at these conditions. Table 1–1 lists the absolute maximum ratings for Cyclone IV devices.

Conditions beyond those listed in Table 1–1 cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time have adverse effects on the device.

Table 1–1. Absolute Maximum Ratings for Cyclone IV Devices (1)

| Symbol                | Parameter                                                                                                     | Min  | Max  | Unit |

|-----------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>CCINT</sub>    | Core voltage, PCI Express® (PCIe®) hard IP block, and transceiver physical coding sublayer (PCS) power supply | -0.5 | 1.8  | V    |

| V <sub>CCA</sub>      | Phase-locked loop (PLL) analog power supply                                                                   | -0.5 | 3.75 | V    |

| V <sub>CCD_PLL</sub>  | PLL digital power supply                                                                                      | -0.5 | 1.8  | V    |

| V <sub>CCIO</sub>     | I/O banks power supply                                                                                        | -0.5 | 3.75 | V    |

| V <sub>CC_CLKIN</sub> | Differential clock input pins power supply                                                                    | -0.5 | 4.5  | V    |

| V <sub>CCH_GXB</sub>  | Transceiver output buffer power supply                                                                        | -0.5 | 3.75 | V    |

| V <sub>CCA_GXB</sub>  | Transceiver physical medium attachment (PMA) and auxiliary power supply                                       | -0.5 | 3.75 | V    |

| V <sub>CCL_GXB</sub>  | Transceiver PMA and auxiliary power supply                                                                    | -0.5 | 1.8  | V    |

| VI                    | DC input voltage                                                                                              | -0.5 | 4.2  | V    |

| I <sub>OUT</sub>      | DC output current, per pin                                                                                    | -25  | 40   | mA   |

| T <sub>STG</sub>      | Storage temperature                                                                                           | -65  | 150  | °C   |

| T <sub>J</sub>        | Operating junction temperature                                                                                | -40  | 125  | °C   |

#### Note to Table 1-1:

## **Maximum Allowed Overshoot or Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 1–2 and undershoot to -2.0 V for a magnitude of currents less than 100 mA and for periods shorter than 20 ns. Table 1-2 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage over the lifetime of the device. The maximum allowed overshoot duration is specified as a percentage of high-time over the lifetime of the device.

<sup>(1)</sup> Supply voltage specifications apply to voltage readings taken at the device pins with respect to ground, not at the power supply.

For more information about the supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to Section III: System Performance Specifications of the External Memory Interfaces Handbook.

Actual achievable frequency depends on design- and system-specific factors. Perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## **High-Speed I/O Specifications**

Table 1–31 through Table 1–36 list the high-speed I/O timing for Cyclone IV devices. For definitions of high-speed timing specifications, refer to "Glossary" on page 1–37.

Table 1–31. RSDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4) (Part 1 of 2)

| Cumbal Madas                               |                                 | C6  |     |     | C7, I7 |     | C8, A7 |     |     | C8L, I8L |     |     | C9L   |     |     |       |      |

|--------------------------------------------|---------------------------------|-----|-----|-----|--------|-----|--------|-----|-----|----------|-----|-----|-------|-----|-----|-------|------|

| Symbol                                     | Modes                           | Min | Тур | Max | Min    | Тур | Max    | Min | Тур | Max      | Min | Тур | Max   | Min | Тур | Max   | Unit |

|                                            | ×10                             | 5   | _   | 180 | 5      | _   | 155.5  | 5   | _   | 155.5    | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                            | ×8                              | 5   |     | 180 | 5      |     | 155.5  | 5   | _   | 155.5    | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

| f <sub>HSCLK</sub><br>(input clock         | ×7                              | 5   | _   | 180 | 5      |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   |     | 132.5 | MHz  |

| frequency)                                 | ×4                              | 5   |     | 180 | 5      |     | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   | -   | 132.5 | MHz  |

| ,                                          | ×2                              | 5   | _   | 180 | 5      | _   | 155.5  | 5   |     | 155.5    | 5   |     | 155.5 | 5   | _   | 132.5 | MHz  |

|                                            | ×1                              | 5   | _   | 360 | 5      |     | 311    | 5   |     | 311      | 5   |     | 311   | 5   |     | 265   | MHz  |

|                                            | ×10                             | 100 | _   | 360 | 100    | _   | 311    | 100 | _   | 311      | 100 | _   | 311   | 100 | _   | 265   | Mbps |

|                                            | ×8                              | 80  | _   | 360 | 80     |     | 311    | 80  | _   | 311      | 80  |     | 311   | 80  | _   | 265   | Mbps |

| Device operation in                        | ×7                              | 70  | _   | 360 | 70     |     | 311    | 70  | _   | 311      | 70  |     | 311   | 70  | _   | 265   | Mbps |

| Mbps                                       | ×4                              | 40  | _   | 360 | 40     | _   | 311    | 40  | _   | 311      | 40  | _   | 311   | 40  | _   | 265   | Mbps |

| ·                                          | ×2                              | 20  | _   | 360 | 20     |     | 311    | 20  | _   | 311      | 20  |     | 311   | 20  | _   | 265   | Mbps |

|                                            | ×1                              | 10  | _   | 360 | 10     |     | 311    | 10  | _   | 311      | 10  |     | 311   | 10  | _   | 265   | Mbps |

| t <sub>DUTY</sub>                          | _                               | 45  |     | 55  | 45     |     | 55     | 45  | _   | 55       | 45  |     | 55    | 45  | _   | 55    | %    |

| Transmitter channel-to-channel skew (TCCS) | _                               | _   | _   | 200 | _      | _   | 200    | _   | _   | 200      | _   | _   | 200   | _   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)            | _                               | _   | _   | 500 | _      | _   | 500    | _   | _   | 550      | _   | _   | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                          | $20 - 80\%,$ $C_{LOAD} =$ 5 pF  | _   | 500 | _   | _      | 500 | _      | _   | 500 | _        | _   | 500 | _     | _   | 500 | _     | ps   |

| t <sub>FALL</sub>                          | $20 - 80\%$ , $C_{LOAD} = 5 pF$ | _   | 500 | _   | _      | 500 | 1      |     | 500 | _        | _   | 500 | ı     | _   | 500 |       | ps   |

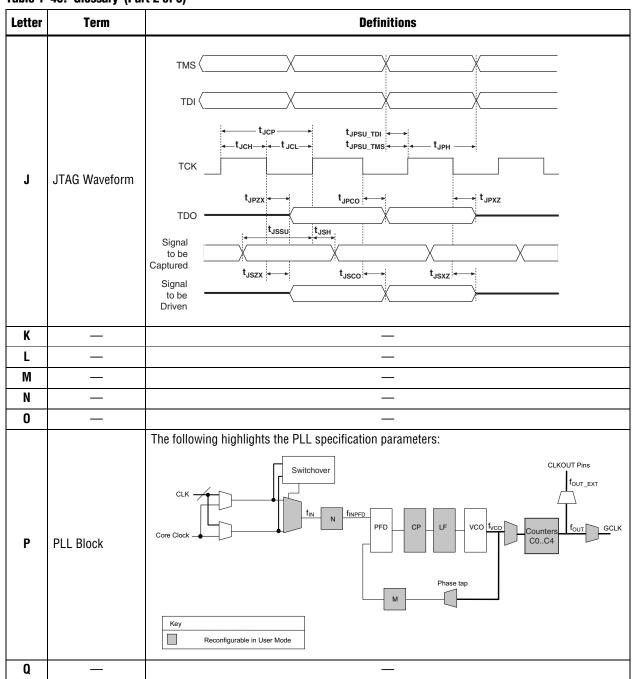

Table 1-46. Glossary (Part 2 of 5)

Table 1-46. Glossary (Part 5 of 5)

| Letter | Term                    | Definitions                                                                                                                                                                                    |

|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | V <sub>CM(DC)</sub>     | DC common mode input voltage.                                                                                                                                                                  |

|        | V <sub>DIF(AC)</sub>    | AC differential input voltage: The minimum AC input differential voltage required for switching.                                                                                               |

|        | V <sub>DIF(DC)</sub>    | DC differential input voltage: The minimum DC input differential voltage required for switching.                                                                                               |

|        | V <sub>ICM</sub>        | Input common mode voltage: The common mode of the differential signal at the receiver.                                                                                                         |

|        | V <sub>ID</sub>         | Input differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                  |

|        | V <sub>IH</sub>         | Voltage input high: The minimum positive voltage applied to the input that is accepted by the device as a logic high.                                                                          |

|        | V <sub>IH(AC)</sub>     | High-level AC input voltage.                                                                                                                                                                   |

|        | V <sub>IH(DC)</sub>     | High-level DC input voltage.                                                                                                                                                                   |

|        | V <sub>IL</sub>         | Voltage input low: The maximum positive voltage applied to the input that is accepted by the device as a logic low.                                                                            |

|        | V <sub>IL (AC)</sub>    | Low-level AC input voltage.                                                                                                                                                                    |

|        | V <sub>IL (DC)</sub>    | Low-level DC input voltage.                                                                                                                                                                    |

|        | V <sub>IN</sub>         | DC input voltage.                                                                                                                                                                              |

|        | V <sub>OCM</sub>        | Output common mode voltage: The common mode of the differential signal at the transmitter.                                                                                                     |

| V      | V <sub>OD</sub>         | Output differential voltage swing: The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. $V_{0D} = V_{0H} - V_{0L}$ . |

|        | V <sub>OH</sub>         | Voltage output high: The maximum positive voltage from an output that the device considers is accepted as the minimum positive high level.                                                     |

|        | V <sub>OL</sub>         | Voltage output low: The maximum positive voltage from an output that the device considers is accepted as the maximum positive low level.                                                       |

|        | V <sub>OS</sub>         | Output offset voltage: $V_{OS} = (V_{OH} + V_{OL}) / 2$ .                                                                                                                                      |

|        | V <sub>OX (AC)</sub>    | AC differential output cross point voltage: the voltage at which the differential output signals must cross.                                                                                   |

|        | V <sub>REF</sub>        | Reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                         |

|        | V <sub>REF (AC)</sub>   | AC input reference voltage for the SSTL and HSTL I/O standards. $V_{REF(AC)} = V_{REF(DC)} + noise$ . The peak-to-peak AC noise on $V_{REF}$ must not exceed 2% of $V_{REF(DC)}$ .             |

|        | V <sub>REF (DC)</sub>   | DC input reference voltage for the SSTL and HSTL I/O standards.                                                                                                                                |

|        | V <sub>SWING (AC)</sub> | AC differential input voltage: AC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |

|        | V <sub>SWING (DC)</sub> | DC differential input voltage: DC input differential voltage required for switching. For the SSTL differential I/O standard, refer to Input Waveforms.                                         |

|        | V <sub>TT</sub>         | Termination voltage for the SSTL and HSTL I/O standards.                                                                                                                                       |

|        | V <sub>X (AC)</sub>     | AC differential input cross point voltage: The voltage at which the differential input signals must cross.                                                                                     |

| W      |                         |                                                                                                                                                                                                |

| X      | _                       |                                                                                                                                                                                                |

| Υ      | _                       | _                                                                                                                                                                                              |

| Z      |                         | _                                                                                                                                                                                              |