Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 7155                                                       |

| Number of Logic Elements/Cells | 114480                                                     |

| Total RAM Bits                 | 3981312                                                    |

| Number of I/O                  | 528                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.97V ~ 1.03V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 780-BGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce115f29i8ln |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1–4 lists Cyclone IV GX device package offerings, including I/O and transceiver counts.

Table 1–4. Package Offerings for the Cyclone IV GX Device Family (1)

| Package    |             |   | F169     |       |              | F324     |       |              | F484     |       |              | F672     |       |              | F896     |       |

|------------|-------------|---|----------|-------|--------------|----------|-------|--------------|----------|-------|--------------|----------|-------|--------------|----------|-------|

| Size (mm)  |             | 1 | 14 × 14  |       |              | 19 × 19  |       | 2            | 23 × 23  |       |              | 27 × 27  |       | 31 × 31      |          |       |

| Pitch (mm) |             |   | 1.0      |       |              | 1.0      |       |              | 1.0      |       |              | 1.0      |       | 1.0          |          |       |

| Device     | Ilser I/D   |   | LVDS (2) | XCVRs | User I/0     | LVDS (2) | XCVRs | User I/O     | (z) SQAT | XCVRs | User I/O     | LVDS (2) | XCVRs | User I/O     | (z) SQA1 | XCVRs |

| EP4CGX15   | <b>↑</b> 72 | 2 | 25       | 2     | _            | _        | _     | _            | _        | _     | _            | _        | _     | _            | _        | _     |

| EP4CGX22   | 7:          | 2 | 25       | 2     | <b>1</b> 50  | 64       | 4     | _            | _        | _     | _            | _        | _     | _            | _        | _     |

| EP4CGX30   | <b>▼</b> 75 | 2 | 25       | 2     | <b>▼</b> 150 | 64       | 4     | <b>▲</b> 290 | 130      | 4     | _            | _        | _     | _            | _        | _     |

| EP4CGX50   | _           | - | _        | _     | _            | _        | _     | 290          | 130      | 4     | <b>★</b> 310 | 140      | 8     | _            | _        | _     |

| EP4CGX75   | _           | - | _        | _     | _            | _        | _     | 290          | 130      | 4     | 310          | 140      | 8     | _            | _        | _     |

| EP4CGX110  | _           | - |          | _     |              | _        |       | 270          | 120      | 4     | 393          | 181      | 8     | <b>▲</b> 475 | 220      | 8     |

| EP4CGX150  | _           | - | _        | _     | _            | _        | _     | <b>▼</b> 270 | 120      | 4     | ▼393         | 181      | 8     | <b>▼</b> 475 | 220      | 8     |

#### Note to Table 1-4:

- (1) Use the Pin Migration View window in Pin Planner of the Quartus II software to verify the pin migration compatibility when you perform device migration. For more information, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

- (2) This includes both dedicated and emulated LVDS pairs. For more information, refer to the I/O Features in Cyclone IV Devices chapter.

## **Cyclone IV Device Family Speed Grades**

Table 1–5 lists the Cyclone IV GX devices speed grades.

Table 1-5. Speed Grades for the Cyclone IV GX Device Family

| Device    | F169           | F324           | F484           | F672           | F896       |

|-----------|----------------|----------------|----------------|----------------|------------|

| EP4CGX15  | C6, C7, C8, I7 | _              | _              | _              | _          |

| EP4CGX22  | C6, C7, C8, I7 | C6, C7, C8, I7 | _              | _              | _          |

| EP4CGX30  | C6, C7, C8, I7 | C6, C7, C8, I7 | C6, C7, C8, I7 | _              | _          |

| EP4CGX50  | _              | _              | C6, C7, C8, I7 | C6, C7, C8, I7 | _          |

| EP4CGX75  | _              | _              | C6, C7, C8, I7 | C6, C7, C8, I7 | _          |

| EP4CGX110 | _              | _              | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |

| EP4CGX150 | _              | _              | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |

Table 1–6 lists the Cyclone IV E devices speed grades.

Table 1-6. Speed Grades for the Cyclone IV E Device Family (1), (2)

| Device   | E144                                   | M164 | M256     | U256 | F256                                   | F324                                     | U484 | F484                                   | F780                            |

|----------|----------------------------------------|------|----------|------|----------------------------------------|------------------------------------------|------|----------------------------------------|---------------------------------|

| EP4CE6   | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | -    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _                                        | _    | _                                      | _                               |

| EP4CE10  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _                                        | _    | _                                      | _                               |

| EP4CE15  | C8L, C9L, I8L<br>C6, C7, C8, I7        | I7N  | C7N, I7N | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | — C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |      | _                                      |                                 |

| EP4CE22  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _                                        | _    | _                                      | _                               |

| EP4CE30  | _                                      | _    | _        | _    | _                                      | A7N                                      | _    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE40  | _                                      | _    | _        | _    | _                                      | A7N                                      | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE55  | _                                      |      | _        | _    | _                                      | _                                        | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE75  | _                                      |      | _        | _    | _                                      | _                                        | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE115 | _                                      | _    | _        | _    | _                                      | _                                        | _    | C8L, C9L, I8L<br>C7, C8, I7            | C8L, C9L, I8L<br>C7, C8, I7     |

#### Notes to Table 1-6:

<sup>(1)</sup> C8L, C9L, and I8L speed grades are applicable for the 1.0-V core voltage.

<sup>(2)</sup> C6, C7, C8, I7, and A7 speed grades are applicable for the 1.2-V core voltage.

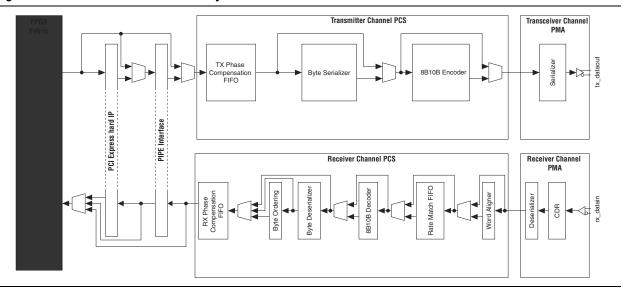

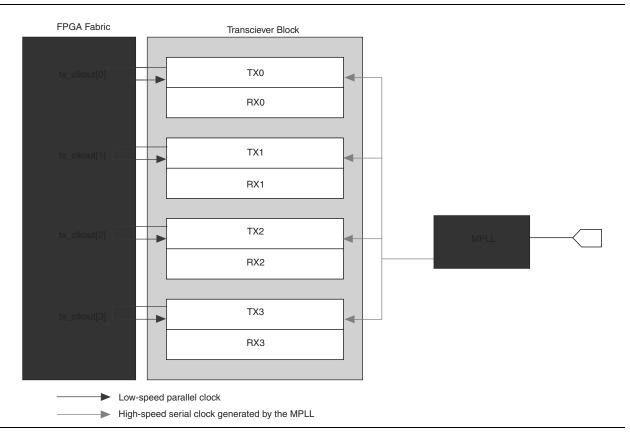

Figure 1–1 shows the structure of the Cyclone IV GX transceiver.

Figure 1-1. Transceiver Channel for the Cyclone IV GX Device

For more information, refer to the *Cyclone IV Transceivers Architecture* chapter.

## Hard IP for PCI Express (Cyclone IV GX Devices Only)

Cyclone IV GX devices incorporate a single hard IP block for ×1, ×2, or ×4 PCIe (PIPE) in each device. This hard IP block is a complete PCIe (PIPE) protocol solution that implements the PHY-MAC layer, Data Link Layer, and Transaction Layer functionality. The hard IP for the PCIe (PIPE) block supports root-port and end-point configurations. This pre-verified hard IP block reduces risk, design time, timing closure, and verification. You can configure the block with the Quartus II software's PCI Express Compiler, which guides you through the process step by step.

For more information, refer to the *PCI Express Compiler User Guide*.

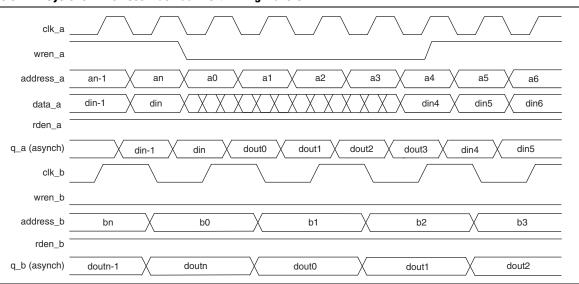

In true dual-port mode, you can access any memory location at any time from either port A or port B. However, when accessing the same memory location from both ports, you must avoid possible write conflicts. When you attempt to write to the same address location from both ports at the same time, a write conflict happens. This results in unknown data being stored to that address location. There is no conflict resolution circuitry built into the Cyclone IV devices M9K memory blocks. You must handle address conflicts external to the RAM block.

Figure 3–11 shows true dual-port timing waveforms for the write operation at port A and read operation at port B. Registering the outputs of the RAM simply delays the q outputs by one clock cycle.

Figure 3-11. Cyclone IV Devices True Dual-Port Timing Waveform

## **Shift Register Mode**

Cyclone IV devices M9K memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flipflops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

The size of a  $(w \times m \times n)$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 9,216 bits. In addition, the size of  $(w \times n)$  must be less than or equal to the maximum width of the block, which is 36 bits. If you need a larger shift register, you can cascade the M9K memory blocks.

### **Power-Up Conditions and Memory Initialization**

The M9K memory block outputs of Cyclone IV devices power up to zero (cleared) regardless of whether the output registers are used or bypassed. All M9K memory blocks support initialization using a .mif. You can create .mifs in the Quartus II software and specify their use using the RAM MegaWizard Plug-In Manager when instantiating memory in your design. Even if memory is pre-initialized (for example, using a .mif), it still powers up with its outputs cleared. Only the subsequent read after power up outputs the pre-initialized values.

For more information about .mifs, refer to the RAM Megafunction User Guide and the Quartus II Handbook.

### **Power Management**

The M9K memory block clock enables of Cyclone IV devices allow you to control clocking of each M9K memory block to reduce AC power consumption. Use the rden signal to ensure that read operations only occur when necessary. If your design does not require read-during-write, reduce power consumption by deasserting the rden signal during write operations or any period when there are no memory operations. The Quartus II software automatically powers down any unused M9K memory blocks to save static power.

## **Document Revision History**

Table 3–6 shows the revision history for this chapter.

Table 3-6. Document Revision History

| Date          | Version | Changes                                    |

|---------------|---------|--------------------------------------------|

| November 2011 | 1.1     | Updated the "Byte Enable Support" section. |

| November 2009 | 1.0     | Initial release.                           |

## 6. I/O Features in Cyclone IV Devices

#### CYIV-51006-2.7

This chapter describes the I/O and high speed I/O capabilities and features offered in Cyclone<sup>®</sup> IV devices.

The I/O capabilities of Cyclone IV devices are driven by the diversification of I/O standards in many low-cost applications, and the significant increase in required I/O performance. Altera's objective is to create a device that accommodates your key board design needs with ease and flexibility.

The I/O flexibility of Cyclone IV devices is increased from the previous generation low-cost FPGAs by allowing all I/O standards to be selected on all I/O banks. Improvements to on-chip termination (OCT) support and the addition of true differential buffers have eliminated the need for external resistors in many applications, such as display system interfaces.

High-speed differential I/O standards have become popular in high-speed interfaces because of their significant advantages over single-ended I/O standards. The Cyclone IV devices support LVDS, BLVDS, RSDS, mini-LVDS, and PPDS. The transceiver reference clocks and the existing general-purpose I/O (GPIO) clock input features also support the LVDS I/O standards.

The Quartus® II software completes the solution with powerful pin planning features that allow you to plan and optimize I/O system designs even before the design files are available.

This chapter includes the following sections:

- "Cyclone IV I/O Elements" on page 6–2

- "I/O Element Features" on page 6–3

- "OCT Support" on page 6–6

- "I/O Standards" on page 6–11

- "Termination Scheme for I/O Standards" on page 6–13

- "I/O Banks" on page 6–16

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 6-2. Cyclone IV Device I/O Features Support (Part 2 of 2)

| I/O Standard                    | IOH/IOL Current Strength<br>Setting (mA) <sup>(1)</sup> , <sup>(9)</sup> |         | ${\bf R_S}$ OCT with Calibration Setting, Ohm $(\Omega)$ |                           | $\mathbf{R_S}$ OCT Without Calibration Setting, Ohm ( $\Omega$ ) |                           | Cyclone<br>IV E I/O<br>Banks | Cyclone<br>IV GX I/O<br>Banks | Slew<br>Rate<br>Option | PCI-<br>clamp<br>Diode |               |   |

|---------------------------------|--------------------------------------------------------------------------|---------|----------------------------------------------------------|---------------------------|------------------------------------------------------------------|---------------------------|------------------------------|-------------------------------|------------------------|------------------------|---------------|---|

|                                 | Column I/O                                                               | Row I/O | Column<br>I/O                                            | Row<br>I/O <sup>(8)</sup> | Column<br>I/O                                                    | Row<br>I/O <sup>(8)</sup> | Support                      |                               | (6)                    | Support                |               |   |

| BLVDS                           | 8,12,16                                                                  | 8,12,16 | _                                                        | _                         | _                                                                | _                         |                              |                               |                        | 3,4,5,6,<br>7,8        | 0,1, <b>2</b> | _ |

| LVDS (3)                        | _                                                                        | _       | _                                                        | _                         | _                                                                | _                         |                              | 5,6                           | _                      | _                      |               |   |

| PPDS (3), (4)                   | <del></del>                                                              | _       | _                                                        | _                         | _                                                                |                           | 1,2,3,4,                     |                               |                        | _                      |               |   |

| RSDS and mini-<br>LVDS (3), (4) | _                                                                        | _       | _                                                        | _                         | _                                                                | _                         | 5,6,7,8                      |                               | _                      | _                      |               |   |

| Differential LVPECL (5)         | _                                                                        | _       | _                                                        |                           | _                                                                |                           |                              | 3,4,5,6,<br>7,8               | _                      | _                      |               |   |

#### Notes to Table 6-2:

- (1) The default current strength setting in the Quartus II software is 50-Ω OCT without calibration for all non-voltage reference and HSTL/SSTL Class I I/O standards. The default setting is 25-Ω OCT without calibration for HSTL/SSTL Class II I/O standards.

- (2) The differential SSTL-18 and SSTL-2, differential HSTL-18, HSTL-15, and HSTL-12 I/O standards are supported only on clock input pins and PLL output clock pins.

- (3) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 1, 2, 5, and 6 only for Cyclone IV E devices and right I/O banks 5 and 6 only for Cyclone IV GX devices. Differential outputs in column I/O banks require an external resistor network.

- (4) This I/O standard is supported for outputs only.

- (5) This I/O standard is supported for clock inputs only

- (6) The default Quartus II slew rate setting is in bold; 2 for all I/O standards that supports slew rate option.

- (7) Differential SSTL-18, differential HSTL-18, HSTL-15, and HSTL-12 I/O standards do not support Class II output.

- (8) Cyclone IV GX devices only support right I/O pins.

- (9) Altera not only offers current strength that meets the industrial standard specification but also other additional current strengths.

For more details about the differential I/O standards supported in Cyclone IV I/O banks, refer to "High-Speed I/O Interface" on page 6–24.

## **On-Chip Series Termination with Calibration**

Cyclone IV devices support  $R_S$  OCT with calibration in the top, bottom, and right I/O banks. The  $R_S$  OCT calibration circuit compares the total impedance of the I/O buffer to the external 25- $\Omega$  ±1% or 50- $\Omega$  ±1% resistors connected to the RUP and RDN pins, and dynamically adjusts the I/O buffer impedance until they match (as shown in Figure 6–2).

When designing LVTTL/LVCMOS inputs with Cyclone IV devices, refer to the following guidelines:

- All pins accept input voltage (V<sub>I</sub>) up to a maximum limit (3.6 V), as stated in the recommended operating conditions provided in the *Cyclone IV Device Datasheet* chapter.

- Whenever the input level is higher than the bank V<sub>CCIO</sub>, expect higher leakage current.

- The LVTTL/LVCMOS I/O standard input pins can only meet the  $V_{IH}$  and  $V_{IL}$  levels according to bank voltage level.

Voltage-referenced standards are supported in an I/O bank using any number of single-ended or differential standards, as long as they use the same  $V_{REF}$  and  $V_{CCIO}$  values. For example, if you choose to implement both SSTL-2 and SSTL-18 in your Cyclone IV devices, I/O pins using these standards—because they require different  $V_{REF}$  values—must be in different banks from each other. However, the same I/O bank can support SSTL-2 and 2.5-V LVCMOS with the  $V_{CCIO}$  set to 2.5 V and the  $V_{REF}$  set to 1.25 V.

- When using Cyclone IV devices as a receiver in 3.3-, 3.0-, or 2.5-V LVTTL/LVCMOS systems, you are responsible for managing overshoot or undershoot to stay in the absolute maximum ratings and the recommended operating conditions, provided in the *Cyclone IV Device Datasheet* chapter.

- The PCI clamping diode is enabled by default in the Quartus II software for input signals with bank  $V_{\text{CCIO}}$  at 2.5, 3.0, or 3.3 V.

## **High-Speed Differential Interfaces**

Cyclone IV devices can send and receive data through LVDS signals. For the LVDS transmitter and receiver, the input and output pins of Cyclone IV devices support serialization and deserialization through internal logic.

The BLVDS extends the benefits of LVDS to multipoint applications such as bidirectional backplanes. The loading effect and the need to terminate the bus at both ends for multipoint applications require BLVDS to drive out a higher current than LVDS to produce a comparable voltage swing. All the I/O banks of Cyclone IV devices support BLVDS for user I/O pins.

The RSDS and mini-LVDS standards are derivatives of the LVDS standard. The RSDS and mini-LVDS I/O standards are similar in electrical characteristics to LVDS, but have a smaller voltage swing and therefore provide increased power benefits and reduced electromagnetic interference (EMI).

The PPDS standard is the next generation of the RSDS standard introduced by National Semiconductor Corporation. Cyclone IV devices meet the National Semiconductor Corporation PPDS Interface Specification and support the PPDS standard for outputs only. All the I/O banks of Cyclone IV devices support the PPDS standard for output pins only.

The LVDS standard does not require an input reference voltage, but it does require a  $100-\Omega$  termination resistor between the two signals at the input buffer. An external resistor network is required on the transmitter side for the top and bottom I/O banks.

You can begin reconfiguration by pulling the nCONFIG pin low. The nCONFIG pin must be low for at least 500 ns. When nCONFIG is pulled low, the Cyclone IV device is reset. The Cyclone IV device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. When nCONFIG returns to a logic-high level and nSTATUS is released by the Cyclone IV device, reconfiguration begins.

#### **Configuration Error**

If an error occurs during configuration, Cyclone IV devices assert the nSTATUS signal low, indicating a data frame error and the CONF\_DONE signal stays low. If the **Auto-restart configuration after error** option (available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box) is turned on, the Cyclone IV device releases nSTATUS after a reset time-out period (a maximum of 230  $\mu$ s), and retries configuration. If this option is turned off, the system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 500 ns to restart configuration.

#### Initialization

In Cyclone IV devices, the initialization clock source is either the internal oscillator or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If you use the internal oscillator, the device provides itself with enough clock cycles for proper initialization. When using the internal oscillator, you do not have to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. Additionally, you can use the CLKUSR pin as a user I/O pin.

You also have the flexibility to synchronize initialization of multiple devices or to delay initialization with the **CLKUSR** option. The CLKUSR pin allows you to control when your device enters user mode for an indefinite amount of time. You can turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. When you turn on the **Enable user supplied start-up clock option (CLKUSR)** option, the CLKUSR pin is the initialization clock source. Supplying a clock on the CLKUSR pin does not affect the configuration process. After the configuration data is accepted and CONF\_DONE goes high, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter user mode.

If you use the optional CLKUSR pin and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure that the CLKUSR pin continues to toggle when nSTATUS is low (a maximum of 230  $\mu$ s).

#### **User Mode**

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE Output** option is available in the Quartus II software in the **General** tab of the **Device and Pin Options** dialog box. If you use the INIT\_DONE pin, it is high due to an external  $10\text{-k}\Omega$  pull-up resistor when nCONFIG is low and during the beginning of configuration. After the option bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the device has entered user mode. In user mode, the user I/O pins function as assigned in your design and no longer have weak pull-up resistors.

May 2013 Altera Corporation

There are no series resistors required in AP configuration mode for Cyclone IV E devices when using the Micron flash at 2.5-, 3.0-, and 3.3-V I/O standard. The output buffer of the Micron P30 IBIS model does not overshoot above 4.1 V. Thus, series resistors are not required for the 2.5-, 3.0-, and 3.3-V AP configuration option. However, if there are any other devices sharing the same flash I/Os with Cyclone IV E devices, all shared pins are still subject to the 4.1-V limit and may require series resistors.

Default read mode of the supported parallel flash memory and all writes to the parallel flash memory are asynchronous. Both the parallel flash families support a synchronous read mode, with data supplied on the positive edge of DCLK.

The serial clock (DCLK) generated by Cyclone IV E devices controls the entire configuration cycle and provides timing for the parallel interface.

#### **Multi-Device AP Configuration**

You can configure multiple Cyclone IV E devices using a single parallel flash. You can cascade multiple Cyclone IV E devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to GND. You must connect its nCEO pin to the nCE pin of the next device in the chain. Use an external 10-k $\Omega$  pull-up resistor to pull the nCEO signal high to its  $V_{\text{CCIO}}$  level to help the internal weak pull-up resistor. When the first device captures all its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in the chain is a Cyclone IV E device. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, DATA [15..8], and DATA [7..0] pins of each device in the chain are connected (Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27).

The first Cyclone IV E device in the chain, as shown in Figure 8–8 on page 8–26 and Figure 8–9 on page 8–27, is the configuration master device and controls the configuration of the entire chain. You must connect its MSEL pins to select the AP configuration scheme. The remaining Cyclone IV E devices are used as configuration slaves. You must connect their MSEL pins to select the FPP configuration scheme. Any other Altera device that supports FPP configuration can also be part of the chain as a configuration slave.

The following are the configurations for the DATA [15..0] bus in a multi-device AP configuration:

- Byte-wide multi-device AP configuration

- Word-wide multi-device AP configuration

VCCIO (1) VCCIO (2)

VCCIO (3)

Refers (6)

Refers (6)

VCCIO (1)

Figure 8-9. Word-Wide Multi-Device AP Configuration

#### Notes to Figure 8-9:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AP mode and the slave devices in FPP mode. To connect MSEL [3..0] for the master device in AP mode and the slave devices in FPP mode, refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O pin to monitor the WAIT signal from the Micron P30 or P33 flash.

- (6) Connect the repeater buffers between the Cyclone IV E master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

In a multi-device AP configuration, the board trace length between the parallel flash and the master device must follow the recommendations listed in Table 8–11.

DQ[15..8]

The programming hardware or download cable then places the configuration data one bit at a time on the DATA [0] pin of the device. The configuration data is clocked into the target device until CONF\_DONE goes high. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor for the device to initialize.

When you use a download cable, setting the **Auto-restart configuration after error** option does not affect the configuration cycle because you must manually restart configuration in the Quartus II software if an error occurs. Additionally, the **Enable user-supplied start-up clock (CLKUSR)** option has no effect on device initialization, because this option is disabled in the **.sof** when programming the device with the Quartus II Programmer and download cable. Therefore, if you turn on the **CLKUSR** option, you do not have to provide a clock on CLKUSR when you configure the device with the Quartus II Programmer and a download cable.

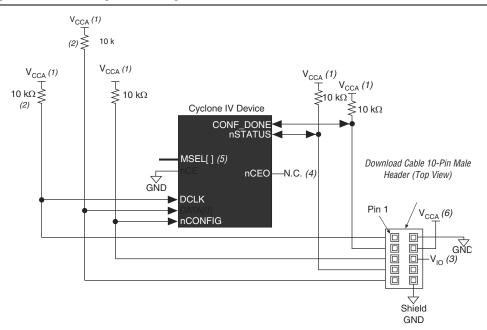

Figure 8–17 shows PS configuration for Cyclone IV devices with a download cable.

Figure 8-17. PS Configuration Using a Download Cable

#### Notes to Figure 8-17:

- (1) You must connect the pull-up resistor to the same supply voltage as the  $V_{CCA}$  supply.

- (2) The pull-up resistors on DATA[0] and DCLK are only required if the download cable is the only configuration scheme used on your board. This is to ensure that DATA[0] and DCLK are not left floating after configuration. For example, if you also use a configuration device, the pull-up resistors on DATA[0] and DCLK are not required.

- (3) Pin 6 of the header is a V<sub>10</sub> reference voltage for the MasterBlaster output driver. V<sub>10</sub> must match the V<sub>CCA</sub> of the device. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide. With the USB-Blaster, ByteBlaster II, ByteBlaster MV, and EthernetBlaster, this pin is a no connect.

- (4) The nceo pin is left unconnected or used as a user I/O pin when it does not feed the nce pin of another device.

- (5) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9 for PS configuration schemes. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (6) Power up the V<sub>CC</sub> of the ByteBlaster II, USB-Blaster, or ByteBlasterMV cable with a 2.5-V supply from V<sub>CCA</sub>. Third-party programmers must switch to 2.5 V. Pin 4 of the header is a V<sub>CC</sub> power supply for the MasterBlaster cable. The MasterBlaster cable can receive power from either 5.0- or 3.3-V circuit boards, DC power supply, or 5.0 V from the USB cable. For this value, refer to the MasterBlaster Serial/USB Communications Cable User Guide.

Configuration error detection determines if the configuration data received through an external memory device is corrupted during configuration. To validate the configuration data, the Quartus<sup>®</sup> II software uses a function to calculate the CRC value for each configuration data frame and stores the frame-based CRC value in the configuration data as part of the configuration bit stream.

During configuration, Cyclone IV devices use the same methodology to calculate the CRC value based on the frame of data that is received and compares it against the frame CRC value in the data stream. Configuration continues until either the device detects an error or all the values are calculated.

In addition to the frame-based CRC value, the Quartus II software generates a 32-bit CRC value for the whole configuration bit stream. This 32-bit CRC value is stored in the 32-bit storage register at the end of the configuration and is used for user mode error detection that is discussed in "User Mode Error Detection".

### **User Mode Error Detection**

User mode error detection is available in Cyclone IV GX and Cyclone IV E devices with 1.2-V core voltage. Cyclone IV E devices with 1.0-V core voltage do not support user mode error detection.

Soft errors are changes in a configuration random-access memory (CRAM) bit state due to an ionizing particle. Cyclone IV devices have built-in error detection circuitry to detect data corruption by soft errors in the CRAM cells.

This error detection capability continuously computes the CRC of the configured CRAM bits based on the contents of the device and compares it with the pre-calculated CRC value obtained at the end of the configuration. If the CRCs match, there is no error in the current configuration CRAM bits. The process of error detection continues until the device is reset (by setting nCONFIG to low).

The Cyclone IV device error detection feature does not check memory blocks and I/O buffers. These device memory blocks support parity bits that are used to check the contents of memory blocks for any error. The I/O buffers are not verified during error detection because the configuration data uses flip-flops as storage elements that are more resistant to soft errors. Similar flip-flops are used to store the pre-calculated CRC and other error detection circuitry option bits.

The error detection circuitry in Cyclone IV devices uses a 32-bit CRC IEEE 802 standard and a 32-bit polynomial as the CRC generator. Therefore, a single 32-bit CRC calculation is performed by the device. If a soft error does not occur, the resulting 32-bit signature value is 0x00000000, that results in a 0 on the CRC\_ERROR output signal. If a soft error occurs in the device, the resulting signature value is non-zero and the CRC\_ERROR output signal is 1.

You can inject a soft error by changing the 32-bit CRC storage register in the CRC circuitry. After verifying the induced failure, you can restore the 32-bit CRC value to the correct CRC value with the same instruction and inserting the correct value.

Before updating it with a known bad value, Altera recommends reading out the correct value.

## **Section I. Transceivers**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device transceivers. This section includes the following chapters:

- Chapter 1, Cyclone IV Transceivers Architecture

- Chapter 2, Cyclone IV Reset Control and Power Down

- Chapter 3, Cyclone IV Dynamic Reconfiguration

## **Revision History**

Refer to the chapter for its own specific revision history. For information about when the chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

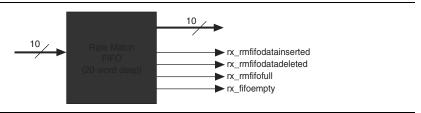

### **Rate Match FIF0**

In asynchronous systems, the upstream transmitter and local receiver can be clocked with independent reference clocks. Frequency differences in the order of a few hundred ppm can corrupt the data when latching from the recovered clock domain (the same clock domain as the upstream transmitter reference clock) to the local receiver reference clock domain. Figure 1–21 shows the rate match FIFO block diagram.

Figure 1-21. Rate Match FIFO Block Diagram

The rate match FIFO compensates for small clock frequency differences of up to  $\pm 300$  ppm (600 ppm total) between the upstream transmitter and the local receiver clocks by performing the following functions:

- Insert skip symbols when the local receiver reference clock frequency is greater than the upstream transmitter reference clock frequency

- Delete skip symbols when the local receiver reference clock frequency is less than the upstream transmitter reference clock frequency

The 20-word deep rate match FIFO and logics control insertion and deletion of skip symbols, depending on the ppm difference. The operation begins after the word aligner synchronization status (rx syncstatus) is asserted.

Rate match FIFO is only supported with 8B/10B encoded data and the word aligner in automatic synchronization state machine mode.

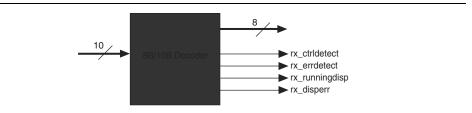

## 8B/10B Decoder

The 8B/10B decoder receives 10-bit data and decodes it into an 8-bit data and a 1-bit control identifier. The decoder is compliant with Clause 36 of the IEEE 802.3 specification.

Figure 1–22 shows the 8B/10B decoder block diagram.

Figure 1–22. 8B/10B Decoder Block Diagram

# **Document Revision History**

Table 2–8 lists the revision history for this chapter.

Table 2–8. Document Revision History

| Date           | Version | Changes                                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2014 | 1.4     | ■ Removed the rx_pll_locked signal from the "Sample Reset Sequence of Receiver Only Channel—Receiver CDR in Manual Lock Mode" and the "Sample Reset Sequence of Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode" figures.                                                                                                              |

|                |         | ■ Added rx_pll_locked to Figure 2–7 and Figure 2–9.                                                                                                                                                                                                                                                                                                      |

| May 2013       | 1.3     | Added information on rx_pll_locked to "Receiver Only Channel—Receiver CDR in<br>Manual Lock Mode" and "Receiver and Transmitter Channel—Receiver CDR in<br>Manual Lock Mode".                                                                                                                                                                            |

| November 2011  | 1.2     | Updated the "All Supported Functional Modes Except the PCIe Functional Mode" section.                                                                                                                                                                                                                                                                    |

|                |         | ■ Updated for the Quartus II software version 10.1 release.                                                                                                                                                                                                                                                                                              |

|                |         | ■ Updated all pll_powerdown to pll_areset.                                                                                                                                                                                                                                                                                                               |

|                |         | ■ Added information about the busy signal in Figure 2–4, Figure 2–5, Figure 2–6, Figure 2–7, Figure 2–8, Figure 2–9, Figure 2–10, Figure 2–12, and Figure 2–13.                                                                                                                                                                                          |

| December 2010  | 1.1     | ■ Added information for clarity ("Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode", "Receiver Only Channel—Receiver CDR in Automatic Lock Mode", "Receiver Only Channel—Receiver CDR in Manual Lock Mode", "Receiver and Transmitter Channel—Receiver CDR in Manual Lock Mode", and "Reset Sequence in Channel Reconfiguration Mode"). |

|                |         | ■ Minor text edits.                                                                                                                                                                                                                                                                                                                                      |

| July 2010      | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                         |

Table 3-5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 2 of 3)

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA Fabric-Transceiver Channel Interface Widths)                                           |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                          | Two 8-bit unencoded Data (rx_dataout)                                                                                                                    |  |  |  |  |

|                                                          | rx_dataoutfull[7:0] - rx_dataout (LSByte) and                                                                                                            |  |  |  |  |

|                                                          | rx_dataoutfull[23:16]-rx_dataout (MSByte)                                                                                                                |  |  |  |  |

|                                                          | The following signals are used in 16-bit 8B/10B modes:                                                                                                   |  |  |  |  |

|                                                          | Two Control Bits                                                                                                                                         |  |  |  |  |

|                                                          | rx_dataoutfull[8] - rx_ctrldetect (LSB) and                                                                                                              |  |  |  |  |

|                                                          | rx_dataoutfull[24]-rx_ctrldetect (MSB)                                                                                                                   |  |  |  |  |

|                                                          | Two Receiver Error Detect Bits                                                                                                                           |  |  |  |  |

|                                                          | rx_dataoutfull[9] - rx_errdetect (LSB) and                                                                                                               |  |  |  |  |

|                                                          | rx_dataoutfull[25]-rx_errdetect (MSB)                                                                                                                    |  |  |  |  |

|                                                          | Two Receiver Sync Status Bits                                                                                                                            |  |  |  |  |

|                                                          | rx_dataoutfull [10] - rx_syncstatus (LSB) and                                                                                                            |  |  |  |  |

| 16-bit FPGA fabric-Transceiver                           | rx_dataoutfull[26] -rx_syncstatus (MSB)                                                                                                                  |  |  |  |  |

| Channel Interface with PCS-PMA set to 8/10 bits          | Two Receiver Disparity Error Bits                                                                                                                        |  |  |  |  |

| SEL IO O/ TO DIES                                        | rx_dataoutfull [11] - rx_disperr (LSB) and                                                                                                               |  |  |  |  |

|                                                          | rx_dataoutfull[27] - rx_disperr (MSB)                                                                                                                    |  |  |  |  |

|                                                          | Two Receiver Pattern Detect Bits                                                                                                                         |  |  |  |  |

|                                                          | rx_dataoutfull[12] - rx_patterndetect (LSB) and                                                                                                          |  |  |  |  |

|                                                          | rx_dataoutfull[28]-rx_patterndetect (MSB)                                                                                                                |  |  |  |  |

|                                                          | rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion status indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes   |  |  |  |  |

|                                                          | rx_dataoutfull[14] and rx_dataoutfull[30]: Rate Match FIFO insertion status indicator (rx rmfifodatainserted) in non-PCI Express (PIPE) functional modes |  |  |  |  |

|                                                          | Two 2-bit PCI Express (PIPE) Functional Mode Status Bits                                                                                                 |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[14:13] - rx_pipestatus (LSB) and rx_dataoutfull[30:29] - rx_pipestatus (MSB)</pre>                                                   |  |  |  |  |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                                |  |  |  |  |

#### **Option 2: Use the Respective Channel Transmitter Core Clocks**

- Enable this option if you want the individual transmitter channel tx\_clkout signals to provide the write clock to their respective Transmit Phase Compensation FIFOs.

- This option is typically enabled when each transceiver channel is reconfigured to a different functional mode using channel reconfiguration.

Figure 3–12 shows how each transmitter channel's tx\_clkout signal provides a clock to the Transmit Phase Compensation FIFOs of the respective transceiver channels.

Figure 3–12. Option 2 for Transmitter Core Clocking (Channel Reconfiguration Mode)

Receiver core clocking refers to the clock that is used to read the parallel data from the Receiver Phase Compensation FIFO into the FPGA fabric. You can use one of the following clocks to read from the Receive Phase Compensation FIFO:

- rx\_coreclk—you can use a clock of the same frequency as rx\_clkout from the FPGA fabric to provide the read clock to the Receive Phase Compensation FIFO. If you use rx\_coreclk, it overrides the rx\_clkout options in the ALTGX MegaWizard Plug-In Manager.

- rx\_clkout—the Quartus II software automatically routes rx\_clkout to the FPGA fabric and back into the Receive Phase Compensation FIFO.

| Symbol               | Parameter                                                      | Conditions                        | Min   | Тур | Max               | Unit |

|----------------------|----------------------------------------------------------------|-----------------------------------|-------|-----|-------------------|------|

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                     | _                                 | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                     |                                   | 1.16  | 1.2 | 1.24              | V    |

| V <sub>I</sub>       | DC input voltage                                               | _                                 | -0.5  |     | 3.6               | V    |

| V <sub>0</sub>       | DC output voltage                                              | _                                 | 0     | _   | V <sub>CCIO</sub> | V    |

| т                    | Operating junction temperature                                 | For commercial use                | 0     | _   | 85                | °C   |

| T <sub>J</sub>       | Operating junction temperature                                 | For industrial use                | -40   |     | 100               | °C   |

| t <sub>RAMP</sub>    | Power supply ramp time                                         | Standard power-on reset (POR) (7) | 50 μs | _   | 50 ms             | _    |

|                      |                                                                | Fast POR (8)                      | 50 μs | _   | 3 ms              | _    |

| I <sub>Diode</sub>   | Magnitude of DC current across<br>PCI-clamp diode when enabled | _                                 | _     | _   | 10                | mA   |

#### Notes to Table 1-4:

- (1) All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (2) You must connect V<sub>CCD PLL</sub> to V<sub>CCINT</sub> through a decoupling capacitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up by V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 where I/O Banks 3 and 9 only support V<sub>CCIO</sub> of 1.5, 1.8, 2.5, 3.0, and 3.3 V. For fast passive parallel (FPP) configuration mode, the V<sub>CCIO</sub> level of I/O Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $V_{CC\_CLKIN}$  to 2.5 V if you use CLKIN as a high-speed serial interface (HSSI) refclk or as a DIFFCLK input.

- (6) The CLKIN pins in I/O Banks 3B and 8B can support single-ended I/O standard when the pins are used to clock left PLLs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and 200 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and 9 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

#### **ESD Performance**

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5 lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

Table 1-5. ESD for Cyclone IV Devices GPIOs and HSSI I/Os

| Symbol              | Parameter                             | Passing Voltage | Unit |

|---------------------|---------------------------------------|-----------------|------|

| V <sub>ESDHBM</sub> | ESD voltage using the HBM (GPIOs) (1) | ± 2000          | V    |

|                     | ESD using the HBM (HSSI I/Os) (2)     | ± 1000          | V    |

| V <sub>ESDCDM</sub> | ESD using the CDM (GPIOs)             | ± 500           | V    |

|                     | ESD using the CDM (HSSI I/Os) (2)     | ± 250           | V    |

#### Notes to Table 1-5:

- (1) The passing voltage for EP4CGX15 and EP4CGX30 row I/Os is ±1000V.

- (2) This value is applicable only to Cyclone IV GX devices.