## Intel - <u>EP4CE15E22C6N Datasheet</u>

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 963                                                      |

| Number of Logic Elements/Cells | 15408                                                    |

| Total RAM Bits                 | 516096                                                   |

| Number of I/O                  | 81                                                       |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 144-LQFP Exposed Pad                                     |

| Supplier Device Package        | 144-EQFP (20x20)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15e22c6n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

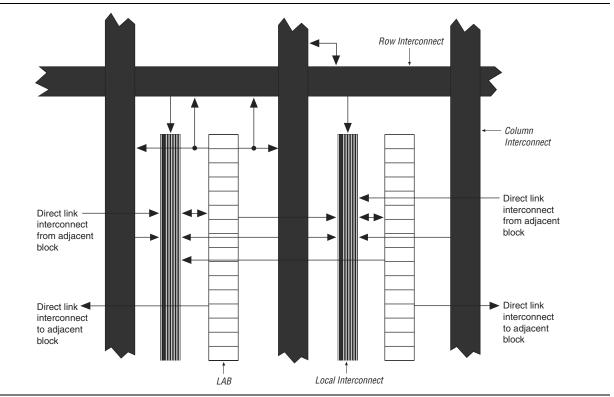

# **Logic Array Blocks**

Logic array blocks (LABs) contain groups of LEs.

## Topology

Each LAB consists of the following features:

- 16 LEs

- LAB control signals

- LE carry chains

- Register chains

- Local interconnect

The local interconnect transfers signals between LEs in the same LAB. Register chain connections transfer the output of one LE register to the adjacent LE register in an LAB. The Quartus II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local and register chain connections for performance and area efficiency.

Figure 2–4 shows the LAB structure for Cyclone IV devices.

Figure 2–4. Cyclone IV Device LAB Structure

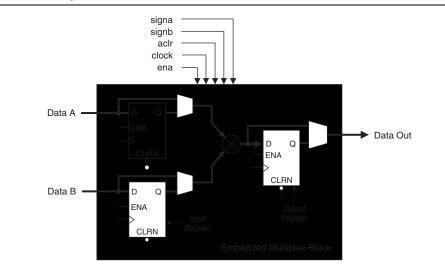

Figure 4–2 shows the multiplier block architecture.

#### Figure 4–2. Multiplier Block Architecture

## **Input Registers**

You can send each multiplier input signal into an input register or directly into the multiplier in 9- or 18-bit sections, depending on the operational mode of the multiplier. You can send each multiplier input signal through a register independently of other input signals. For example, you can send the multiplier Data A signal through a register and send the Data B signal directly to the multiplier.

The following control signals are available for each input register in the embedded multiplier:

- clock

- clock enable

- asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

## **Multiplier Stage**

The multiplier stage of an embedded multiplier block supports  $9 \times 9$  or  $18 \times 18$  multipliers, as well as other multipliers between these configurations. Depending on the data width or operational mode of the multiplier, a single embedded multiplier can perform one or two multiplications in parallel. For multiplier information, refer to "Operational Modes" on page 4–4.

Each multiplier operand is a unique signed or unsigned number. The signa and signb signals control an input of a multiplier and determine if the value is signed or unsigned. If the signa signal is high, the Data A operand is a signed number. If the signa signal is low, the Data A operand is an unsigned number.

# 5. Clock Networks and PLLs in Cyclone IV Devices

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in the Cyclone<sup>®</sup> IV device family. It includes details about the ability to reconfigure the PLL counter clock frequency and phase shift in real time, allowing you to sweep PLL output frequencies and dynamically adjust the output clock phase shift.

The Quartus<sup>®</sup> II software enables the PLLs and their features without external devices.

This chapter contains the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–18

- "Cyclone IV PLL Hardware Overview" on page 5–20

- "Clock Feedback Modes" on page 5–23

- "Hardware Features" on page 5–26

- "Programmable Bandwidth" on page 5–32

- "Phase Shift Implementation" on page 5–32

- "PLL Cascading" on page 5–33

- "PLL Reconfiguration" on page 5–34

- "Spread-Spectrum Clocking" on page 5–41

- "PLL Specifications" on page 5–41

# **Clock Networks**

The Cyclone IV GX device provides up to 12 dedicated clock pins (CLK[15..4]) that can drive the global clocks (GCLKs). Cyclone IV GX devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

The Cyclone IV E device provides up to 15 dedicated clock pins (CLK[15..1]) that can drive up to 20 GCLKs. Cyclone IV E devices support three dedicated clock pins on the left side and four dedicated clock pins on the top, right, and bottom sides of the device except EP4CE6 and EP4CE10 devices. EP4CE6 and EP4CE10 devices only support three dedicated clock pins on the left side and four dedicated clock pins on the right side of the device.

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. If you do not use dedicated clock pins to feed the GCLKs, you can use them as general-purpose input pins to feed the logic array. However, when using them as general-purpose input pins, they do not have support for an I/O register and must use LE-based registers in place of an I/O register.

**Constitution** For more information about how to connect the clock and PLL pins, refer to the *Cyclone IV Device Family Pin Connection Guidelines*.

## **Clock Control Block**

The clock control block drives the GCLKs. Clock control blocks are located on each side of the device, close to the dedicated clock input pins. GCLKs are optimized for minimum clock skew and delay.

Table 5–4 lists the sources that can feed the clock control block, which in turn feeds the GCLKs.

| Input                                                 | Description                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedicated clock inputs                                | Dedicated clock input pins can drive clocks or global signals, such as synchronous and asynchronous clears, presets, or clock enables onto given GCLKs.                                                                                                                                                         |

| Dual-purpose clock<br>(DPCLK and CDPCLK)<br>I/O input | DPCLK and CDPCLK I/O pins are bidirectional dual function pins that<br>are used for high fan-out control signals, such as protocol signals,<br>TRDY and IRDY signals for PCI, via the GCLK. Clock control blocks<br>that have inputs driven by dual-purpose clock I/O pins are not able to<br>drive PLL inputs. |

| PLL outputs                                           | PLL counter outputs can drive the GCLK.                                                                                                                                                                                                                                                                         |

| Internal logic                                        | You can drive the GCLK through logic array routing to enable internal<br>logic elements (LEs) to drive a high fan-out, low-skew signal path.<br>Clock control blocks that have inputs driven by internal logic are not<br>able to drive PLL inputs.                                                             |

Table 5-4. Clock Control Block Inputs

In Cyclone IV devices, dedicated clock input pins, PLL counter outputs, dual-purpose clock I/O inputs, and internal logic can all feed the clock control block for each GCLK. The output from the clock control block in turn feeds the corresponding GCLK. The GCLK can drive the PLL input if the clock control block inputs are outputs of another PLL or dedicated clock input pins. There are five or six clock control blocks on each side of the device periphery—depending on device density; providing up to 30 clock control blocks in each Cyclone IV GX device. The maximum number of clock control blocks per Cyclone IV E device is 20. For the clock control block locations, refer to Figure 5–2 on page 5–12, Figure 5–3 on page 5–13, and Figure 5–4 on page 5–14.

The clock control blocks on the left side of the Cyclone IV GX device do not support any clock inputs.

The control block has two functions:

- Dynamic GCLK clock source selection (not applicable for DPCLK, CDPCLK, and internal logic input)

- GCLK network power down (dynamic enable and disable)

## **Deterministic Latency Compensation Mode**

The deterministic latency mode compensates for the delay of the multipurpose PLLs through the clock network and serializer in Common Public Radio Interface (CPRI) applications. In this mode, the PLL PFD feedback path compensates the latency uncertainty in Tx dataout and Tx clkout paths relative to the reference clock.

# **Hardware Features**

Cyclone IV PLLs support several features for general-purpose clock management. This section discusses clock multiplication and division implementation, phase shifting implementations, and programmable duty cycles.

# **Clock Multiplication and Division**

Each Cyclone IV PLL provides clock synthesis for PLL output ports using  $M/(N^*post-scale \text{ counter})$  scaling factors. The input clock is divided by a pre-scale factor, N, and is then multiplied by the M feedback factor. The control loop drives the VCO to match  $f_{IN}$  (M/N). Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO value is the least common multiple of the output frequencies that meets its frequency specifications. For example, if output frequencies required from one PLL are 33 and 66 MHz, the Quartus II software sets the VCO to 660 MHz (the least common multiple of 33 and 66 MHz in the VCO range). Then, the post-scale counters scale down the VCO frequency for each output port.

There is one pre-scale counter, N, and one multiply counter, M, per PLL, with a range of 1 to 512 for both M and N. The N counter does not use duty cycle control because the purpose of this counter is only to calculate frequency division. There are five generic post-scale counters per PLL that can feed GCLKs or external clock outputs. These post-scale counters range from 1 to 512 with a 50% duty cycle setting. The post-scale counters range from 1 to 256 with any non-50% duty cycle setting. The sum of the high/low count values chosen for a design selects the divide value for a given counter.

The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered into the ALTPLL megafunction.

Phase alignment between output counters is determined using the t<sub>PLL\_PSERR</sub> specification.

In this mode, the activeclock signal mirrors the clkswitch signal. As both blocks are still functional during the manual switch, neither clkbad signals go high. Because the switchover circuit is positive edge-sensitive, the falling edge of the clkswitch signal does not cause the circuit to switch back from inclk1 to inclk0. When the clkswitch signal goes high again, the process repeats. The clkswitch signal and the automatic switch only works depending on the availability of the clock that is switched to. If the clock is unavailable, the state machine waits until the clock is available.

When CLKSWITCH = 1, it overrides the automatic switch-over function. As long as clkswitch signal is high, further switch-over action is blocked.

|               | • |

|---------------|---|

| inclk0        |   |

| inclk1        |   |

| muxout        |   |

| clkswitch _   |   |

| activeclock _ |   |

| clkbad0 -     |   |

| clkbad1 -     |   |

### Figure 5–19. Clock Switchover Using the clkswitch Control (1)

#### Note to Figure 5–19:

(1) Both inclk0 and inclk1 must be running when the clkswitch signal goes high to start a manual clock switchover event.

## **Manual Clock Switchover**

PLLs of Cyclone IV devices support manual switchover, in which the clkswitch signal controls whether inclk0 or inclk1 is the input clock to the PLL. The characteristics of a manual switchover are similar to the manual override feature in an automatic clock switchover, in which the switchover circuit is edge-sensitive. When the clkswitch signal goes high, the switchover sequence starts. The falling edge of the clkswitch signal does not cause the circuit to switch back to the previous input clock.

• For more information about PLL software support in the Quartus II software, refer to the *ALTPLL Megafunction User Guide*.

## Guidelines

Use the following guidelines to design with clock switchover in PLLs:

Clock loss detection and automatic clock switchover require the inclk0 and inclk1 frequencies be within 20% of each other. Failing to meet this requirement causes the clkbad0 and clkbad1 signals to function improperly. • For the specific sustaining current for each V<sub>CCIO</sub> voltage level driven through the resistor and for the overdrive current used to identify the next driven input level, refer to the *Cyclone IV Device Datasheet* chapter.

## **Programmable Pull-Up Resistor**

Each Cyclone IV device I/O pin provides an optional programmable pull-up resistor while in user mode. If you enable this feature for an I/O pin, the pull-up resistor holds the output to the  $V_{CCIO}$  level of the output pin's bank.

- IF you enable the programmable pull-up resistor, the device cannot use the bus-hold feature. Programmable pull-up resistors are not supported on the dedicated configuration, JTAG, and dedicated clock pins.

- When the optional DEV\_OE signal drives low, all I/O pins remains tri-stated even with the programmable pull-up option enabled.

## **Programmable Delay**

The Cyclone IV IOE includes programmable delays to ensure zero hold times, minimize setup times, increase clock-to-output times, and delay the clock input signal.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays minimize setup time. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output registers. Each dual-purpose clock input pin provides a programmable delay to the global clock networks.

Table 6–1 shows the programmable delays for Cyclone IV devices.

| Programmable Delay                 | Quartus II Logic Option                                         |

|------------------------------------|-----------------------------------------------------------------|

| Input pin-to-logic array delay     | Input delay from pin to internal cells                          |

| Input pin-to-input register delay  | Input delay from pin to input register                          |

| Output pin delay                   | Delay from output register to output pin                        |

| Dual-purpose clock input pin delay | Input delay from dual-purpose clock pin to fan-out destinations |

Table 6-1. Cyclone IV Devices Programmable Delay Chain

There are two paths in the IOE for an input to reach the logic array. Each of the two paths can have a different delay. This allows you to adjust delays from the pin to the internal logic element (LE) registers that reside in two different areas of the device. You must set the two combinational input delays with the input delay from pin to internal cells logic option in the Quartus II software for each path. If the pin uses the input register, one of the delays is disregarded and the delay is set with the input delay from pin to input register logic option in the Quartus II software.

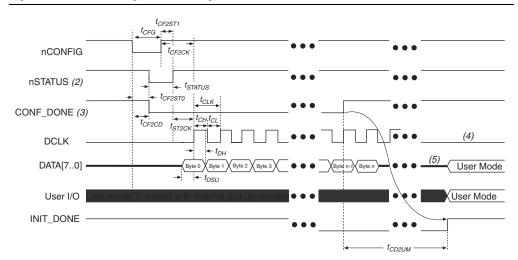

## **FPP Configuration Timing**

Figure 8–22 shows the timing waveform for the FPP configuration when using an external host.

### Notes to Figure 8-22:

- (1) The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and  $CONF_DONE$  are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- (2) After power up, the Cyclone IV device holds  ${\tt nSTATUS}$  low during POR delay.

- (3) After power up, before and during configuration,  $CONF_DONE$  is low.

- (4) Do not leave DCLK floating after configuration. It must be driven high or low, whichever is more convenient.

- (5) DATA [7..0] is available as a user I/O pin after configuration; the state of the pin depends on the dual-purpose pin settings.

Table 8–13 lists the FPP configuration timing parameters for Cyclone IV devices.

Table 8–13. FPP Timing Parameters for Cyclone IV Devices (Part 1 of 2)

| 0hal                | Deventer                                        | Minimum                   |                             | Maximum                   |                             |      |  |    |

|---------------------|-------------------------------------------------|---------------------------|-----------------------------|---------------------------|-----------------------------|------|--|----|

| Symbol              | Parameter                                       | Cyclone IV <sup>(1)</sup> | Cyclone IV E <sup>(2)</sup> | Cyclone IV <sup>(1)</sup> | Cyclone IV E <sup>(2)</sup> | Unit |  |    |

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                    | —                         |                             | — 500                     |                             | ns   |  |    |

| t <sub>CF2ST0</sub> | nCONFIG <b>low to</b><br>nSTATUS <b>low</b>     | _                         |                             | — 500                     |                             | ns   |  |    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                         | 500                       |                             | 500 —                     |                             | ns   |  |    |

| t <sub>status</sub> | nSTATUS low pulse width                         | 45                        |                             | 230                       | (3)                         | μs   |  |    |

| t <sub>CF2ST1</sub> | nCONFIG high to<br>nSTATUS high                 | _                         |                             | — 230 (4                  |                             | μs   |  |    |

| t <sub>CF2CK</sub>  | nCONFIG high to<br>first rising edge on<br>DCLK | 230 <sup>(3)</sup>        |                             | 230 (3)                   |                             | _    |  | μs |

| Bank | Description           | Input/Output  | Dedicated     | Powered By         | <b>Configuration Mode</b> |

|------|-----------------------|---------------|---------------|--------------------|---------------------------|

| 1    | DATA[0] (1), (2)      | Input         |               | V <sub>CCIO</sub>  | PS, FPP, AS               |

| I    |                       | Bidirectional | Bidirectional |                    | AP                        |

|      |                       | Input         |               | V <sub>CCIO</sub>  | FPP                       |

| 1    | DATA[1] (2) /ASDO (1) | Output        | _ [           | V <sub>CCIO</sub>  | AS                        |

|      |                       | Bidirectional | 1             | V <sub>CCIO</sub>  | AP                        |

| 8    | DATA[72] (2)          | Input         |               | V <sub>CCIO</sub>  | FPP                       |

| 0    | DAIA[/2] (-/          | Bidirectional |               | V <sub>CCIO</sub>  | AP                        |

| 8    | DATA[158] (2)         | Bidirectional | —             | V <sub>CCIO</sub>  | AP                        |

| 6    | INIT_DONE             | Output        | —             | Pull-up            | Optional, all modes       |

| 1    | nSTATUS               | Bidirectional | Yes           | Pull-up            | All modes                 |

| 1    | nCE                   | Input         | Yes           | V <sub>CCIO</sub>  | All modes                 |

| 1    | DCLK (1), (2)         | Input         | Yes           | V <sub>CCIO</sub>  | PS, FPP                   |

| I    | DCLK (1), (-)         | Output        | —             | V <sub>CCIO</sub>  | AS, AP                    |

| 6    | CONF_DONE             | Bidirectional | Yes           | Pull-up            | All modes                 |

| 1    | TDI                   | Input         | Yes           | V <sub>CCIO</sub>  | JTAG                      |

| 1    | TMS                   | Input         | Yes           | V <sub>CCIO</sub>  | JTAG                      |

| 1    | ТСК                   | Input         | Yes           | V <sub>CCIO</sub>  | JTAG                      |

| 1    | nCONFIG               | Input         | Yes           | V <sub>CCIO</sub>  | All modes                 |

| 6    | CLKUSR                | Input         | —             | V <sub>CCIO</sub>  | Optional                  |

| 6    | nCEO                  | Output        | —             | V <sub>CCIO</sub>  | Optional, all modes       |

| 6    | MSEL[]                | Input         | Yes           | V <sub>CCINT</sub> | All modes                 |

| 1    | TDO                   | Output        | Yes           | V <sub>CCIO</sub>  | JTAG                      |

| 7    | PADD[140]             | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 8    | PADD[1915]            | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 6    | PADD[2320]            | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 1    | nRESET                | Output        | _             | V <sub>CCIO</sub>  | AP                        |

| 6    | nAVD                  | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 6    | nOE                   | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 6    | nWE                   | Output        | —             | V <sub>CCIO</sub>  | AP                        |

| 5    | DEV OE                | Input         |               | V <sub>CCIO</sub>  | Optional, AP              |

Table 8–19. Configuration Pin Summary for Cyclone IV E Devices (Part 2 of 3)

| Chapter Revision Dates                          | vii    |

|-------------------------------------------------|--------|

| Additional Information                          |        |

| How to Contact Altera                           |        |

| Typographic Conventions                         | Info–1 |

| Section I. Transceivers                         |        |

|                                                 |        |

| Chapter 1. Cyclone IV Transceivers Architecture | 1.0    |

| Transceiver Architecture                        |        |

| Architectural Overview                          |        |

| Transmitter Channel Datapath                    |        |

| TX Phase Compensation FIFO      Byte Serializer |        |

| 8B/10B Encoder                                  |        |

| Miscellaneous Transmitter PCS Features          |        |

| Serializer                                      |        |

| Transmitter Output Buffer                       |        |

| Receiver Channel Datapath                       |        |

| Receiver Input Buffer                           |        |

| Clock Data Recovery                             |        |

| Automatic Lock Mode                             |        |

| Manual Lock Mode                                |        |

| Deserializer                                    |        |

| Word Aligner                                    |        |

| Deskew FIFO                                     |        |

| Rate Match FIFO                                 |        |

| 8B/10B Decoder                                  |        |

| Byte Deserializer                               |        |

| Byte Ordering                                   | 1–24   |

| RX Phase Compensation FIFO                      | 1–25   |

| Miscellaneous Receiver PCS Feature              |        |

| Transceiver Clocking Architecture               |        |

| Input Reference Clocking                        |        |

| Transceiver Channel Datapath Clocking           |        |

| Non-Bonded Channel Configuration                |        |

| Bonded Channel Configuration                    |        |

| FPGA Fabric-Transceiver Interface Clocking      |        |

| Calibration Block                               |        |

| PCI-Express Hard IP Block                       |        |

| Transceiver Functional Modes                    |        |

| Basic Mode                                      |        |

| Rate Match FIFO Operation in Basic Mode         |        |

| Additional Options in Basic Mode                |        |

| PCI Express (PIPE) Mode                         |        |

| PIPE Interface                                  |        |

| Receiver Detection Circuitry                    |        |

| Electrical Idle Control                         |        |

In any configuration, a receiver channel cannot source CDR clocks from other PLLs beyond the two multipurpose PLLs directly adjacent to transceiver block where the channel resides.

The Cyclone IV GX transceivers support non-bonded (×1) and bonded (×2 and ×4) channel configurations. The two configurations differ in regards to clocking and phase compensation FIFO control. Bonded configuration provides a relatively lower channel-to-channel skew between the bonded channels than in non-bonded configuration. Table 1–8 lists the supported conditions in non-bonded and bonded channel configurations.

Table 1–8. Supported Conditions in Non-Bonded and Bonded Channel Configurations

| Channel<br>Configuration | Description                                                                                                                                                            | Supported Channel<br>Operation Mode                                     |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Non-bonded               | <ul> <li>Low-speed clock in each channel is sourced independently</li> <li>Dece componentian EIFO in each channel has its own pointers and control logic</li> </ul>    | <ul> <li>Transmitter Only</li> <li>Dessiver Only</li> </ul>             |

| (×1)                     | Phase compensation FIFO in each channel has its own pointers and control logic                                                                                         | <ul> <li>Receiver Only</li> <li>Transmitter and<br/>Receiver</li> </ul> |

| Bonded (×2<br>and ×4)    | <ul> <li>Low-speed clock in each bonded channel is sourced from a common bonded<br/>clock path for lower channel-to-channel skew</li> </ul>                            | <ul> <li>Transmitter Only</li> <li>Transmitter and</li> </ul>           |

|                          | <ul> <li>Phase compensation FIFOs in bonded channels share common pointers and<br/>control logic for equal latency through the FIFOs in all bonded channels</li> </ul> | Receiver                                                                |

|                          | <ul> <li>×2 bonded configuration is supported with channel 0 and channel 1 in a<br/>transceiver block</li> </ul>                                                       |                                                                         |

|                          | • ×4 bonded configuration is supported with all four channels in a transceiver block                                                                                   |                                                                         |

## **Non-Bonded Channel Configuration**

In non-bonded channel configuration, the high- and low-speed clocks for each channel are sourced independently. The phase compensation FIFOs in each channel has its own pointers and control logic. When implementing multi-channel serial interface in non-bonded channel configuration, the clock skew and unequal latency results in larger channel-to-channel skew.

Altera recommends using bonded channel configuration (×2 or ×4) when implementing multi-channel serial interface for a lower channel-to-channel skew.

In a transceiver block, the high- and low-speed clocks for each channel are distributed primarily from one of the two multipurpose PLLs directly adjacent to the block. Transceiver channels for devices in F484 and larger packages support additional clocking flexibility. In these packages, some channels support high-speed and low-speed clock distribution from PLLs beyond the two multipurpose PLLs directly adjacent to the block.

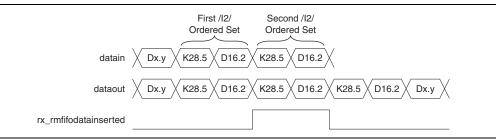

Figure 1–59 shows an example of rate match FIFO insertion in the case where one symbol must be inserted. Because the rate match FIFO can only insert /I2/ ordered sets, it inserts one /I2/ ordered set (two symbols inserted).

Figure 1–59. Example of Rate Match FIFO Insertion in GIGE Mode

The rate match FIFO does not insert or delete code groups automatically to overcome FIFO empty or full conditions. In this case, the rate match FIFO asserts the rx\_rmfifofull and rx\_rmfifoempty flags for at least two recovered clock cycles to indicate rate match FIFO full and empty conditions, respectively. You must then assert the rx\_digitalreset signal to reset the receiver PCS blocks.

## **Serial RapidIO Mode**

Serial RapidIO mode provides the non-bonded (×1) transceiver channel datapath configuration for SRIO protocol implementation. The Cyclone IV GX transceiver provides the PMA and the following PCS functions:

- 8B/10B encoding and decoding

- lane synchronization state machine

Cyclone IV GX transceivers do not have built-in support for some PCS functions such as pseudo-random idle sequence generation and lane alignment in ×4 bonded channel configuration. If required, you must implement these functions in a user logics or external circuits.

The RapidIO Trade Association defines a high-performance, packet-switched interconnect standard to pass data and control information between microprocessors, digital signals, communications, network processes, system memories, and peripheral devices. The SRIO physical layer specification defines serial protocol running at 1.25 Gbps, 2.5 Gbps, and 3.125 Gbps in either single-lane (×1) or bonded four-lane (×4) at each line rate. Cyclone IV GX transceivers support single-lane (×1) configuration at all three line rates. Four ×1 channels configured in Serial RapidIO mode can be instantiated to achieve one non-bonded ×4 SRIO link. When implementing four ×1 SRIO channels, the receivers do not have lane alignment or deskew capability.

# 3. Cyclone IV Dynamic Reconfiguration

Cyclone<sup>®</sup> IV GX transceivers allow you to dynamically reconfigure different portions of the transceivers without powering down any part of the device. This chapter describes and provides examples about the different modes available for dynamic reconfiguration.

You can use the ALTGX\_RECONFIG and ALTPLL\_RECONFIG controller instance to reconfigure the physical medium attachment (PMA) controls, physical coding sublayer (PCS), multipurpose phase locked loops (PLLs), and general purpose PLLs.

This chapter contains the following sections:

- "Glossary of Terms" on page 3–1

- "Dynamic Reconfiguration Controller Architecture" on page 3–2

- "Dynamic Reconfiguration Modes" on page 3–12

- "Error Indication During Dynamic Reconfiguration" on page 3–36

- "Functional Simulation of the Dynamic Reconfiguration Process" on page 3–37

# **Glossary of Terms**

Table 3–1 lists the terms used in this chapter:

| Table 3-1. | <b>Glossary</b> of | <b>Terms Used in</b> | this Chapter | (Part 1 of 2) |

|------------|--------------------|----------------------|--------------|---------------|

|------------|--------------------|----------------------|--------------|---------------|

| Term                       | Description                                                                                                                                                                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALTGX_RECONFIG Instance    | Dynamic reconfiguration controller instance generated by the ALTGX_RECONFIG MegaWizard <sup>™</sup> Plug-In Manager.                                                                           |

| ALTGX Instance             | Transceiver instance generated by the ALTGX MegaWizard Plug-In Manager.                                                                                                                        |

| ALTPLL_RECONFIG Instance   | Dynamic PLL reconfiguration controller instance generated by the ALTPLL_RECONFIG Megawizard Plug-In Manager                                                                                    |

| Logical Channel Addressing | Used whenever the concept of logical channel addressing is explained. This term does not refer to the logical_channel_address port available in the ALTGX_RECONFIG MegaWizard Plug-In Manager. |

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

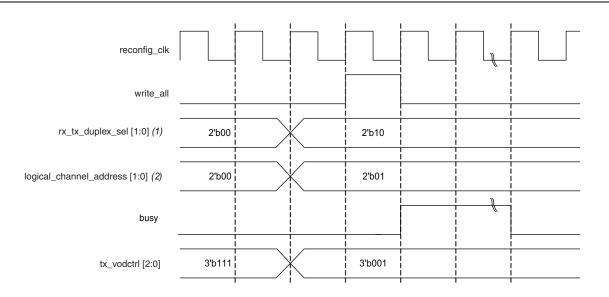

Figure 3–4 shows the write transaction waveform for Method 1.

#### Figure 3-4. Write Transaction Waveform—Use 'logical\_channel\_address port' Option

#### Notes to Figure 3-4:

- (1) In this waveform example, you are writing to only the transmitter portion of the channel.

- (2) In this waveform example, the number of channels connected to the dynamic reconfiguration controller is four. Therefore, the

- logical\_channel\_address port is 2 bits wide.

#### **Read Transaction**

For example, to read the existing  $V_{OD}$  values from the transmit  $V_{OD}$  control registers of the transmitter portion of a specific channel controlled by the ALTGX\_RECONFIG instance, perform the following steps:

- Set the logical\_channel\_address input port to the logical channel address of the transceiver channel whose PMA controls you want to read (for example, tx\_vodctrl\_out).

- 2. Set the rx\_tx\_duplex\_sel port to **2'b10** so that only the transmit PMA controls are read from the transceiver channel.

- 3. Ensure that the busy signal is low before you start a read transaction.

- 4. Assert the read signal for one reconfig\_clk clock cycle. This initiates the read transaction.

The busy output status signal is asserted high to indicate that the dynamic reconfiguration controller is busy reading the PMA control values. When the read transaction has completed, the busy signal goes low. The data\_valid signal is asserted to indicate that the data available at the read control signal is valid.

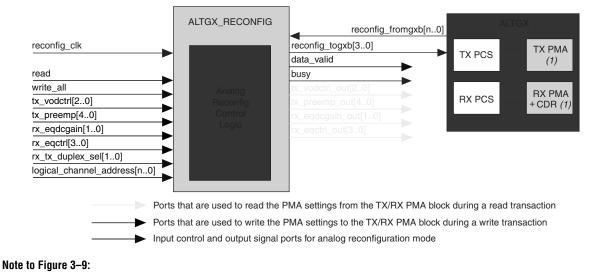

Figure 3–9 shows the connection for PMA reconfiguration mode.

(1) This block can be reconfigured in PMA reconfiguration mode.

## **Transceiver Channel Reconfiguration Mode**

You can dynamically reconfigure the transceiver channel from an existing functional mode to a different functional mode by selecting the **Channel Reconfiguration** option in ALTGX and ALTGX\_RECONFIG MegaWizards. The blocks that are reconfigured by channel reconfiguration mode are the PCS and RX PMA blocks of a transceiver channel.

For more information about reconfiguring the RX PMA blocks of the transceiver channel using channel reconfiguration mode, you can refer to "Data Rate Reconfiguration Mode Using RX Local Divider" on page 3–26.

In channel reconfiguration, only a write transaction can occur; no read transactions are allowed. You can optionally choose to trigger write\_all once by selecting the continuous write operation in the ALTGX\_RECONFIG MegaWizard Plug-In Manager. The Quartus II software then continuously writes all the words required for reconfiguration.

For channel reconfiguration, **.mif** files are required to dynamically reconfigure the transceivers channels in channel reconfiguration modes. The **.mif** carries the reconfiguration information that will be used to reconfigure the transceivers channel dynamically on-the-fly. The **.mif** contents is generated automatically when you select the **Generate GXB Reconfig MIF** option in the Quartus II software setting. For different **.mif** settings, you need to later reconfigure and recompile the ALTGX MegaWizard to generate the **.mif** based on the required reconfiguration settings.

The dynamic reconfiguration controller can optionally perform a continuos write operation or a regular write operation of the **.mif** contents in terms of word size (16-bit data) to the transceivers channel that is selected for reconfiguration.

## Figure 3–9. ALTGX and ALTGX\_RECONFIG Connection for PMA Reconfiguration Mode

| FPGA Fabric-Transceiver Channel<br>Interface Description | Receive Signal Description (Based on Cyclone IV GX Supported FPGA<br>Fabric-Transceiver Channel Interface Widths)                                                       |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                          | Two 10-bit Data (rx_dataout)                                                                                                                                            |  |  |

|                                                          | <pre>rx_dataoutfull[9:0] - rx_dataout (LSByte) and rx_dataoutfull[25:16] - rx_dataout (MSByte)</pre>                                                                    |  |  |

|                                                          | wo Receiver Sync Status Bits                                                                                                                                            |  |  |

|                                                          | <pre>rx_dataoutfull[10] - rx_syncstatus (LSB) and rx_dataoutfull[26] - rx_syncstatus (MSB)</pre>                                                                        |  |  |

| 20-bit FPGA fabric-Transceiver                           | <pre>rx_dataoutfull[11] and rx_dataoutfull[27]: 8B/10B disparity error indicator (rx_disperr)</pre>                                                                     |  |  |

| Channel Interface with PCS-PMA                           | Two Receiver Pattern Detect Bits                                                                                                                                        |  |  |

| set to 10 bits                                           | <pre>rx_dataoutfull[12] - rx_patterndetect (LSB) and rx_dataoutfull[28] - rx_patterndetect (MSB)</pre>                                                                  |  |  |

|                                                          | <pre>rx_dataoutfull[13] and rx_dataoutfull[29]: Rate Match FIFO deletion status<br/>indicator (rx_rmfifodatadeleted) in non-PCI Express (PIPE) functional modes</pre>   |  |  |

|                                                          | <pre>rx_dataoutfull[14] and rx_dataoutfull[30]: Rate Match FIFO insertion status<br/>indicator (rx_rmfifodatainserted) in non-PCI Express (PIPE) functional modes</pre> |  |  |

|                                                          | <pre>rx_dataoutfull[15] and rx_dataoutfull[31]: 8B/10B running disparity indicator (rx_runningdisp)</pre>                                                               |  |  |

### Table 3–5. rx\_dataoutfull[31..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions (Part 3 of 3)

## **Data Rate Reconfiguration Mode Using RX Local Divider**

The RX local divider resides in the RX PMA block for every channels. This is a hardware feature where a /2 divider is available in each of the receiver channel for the supported device. You can use this RX local divider to reconfigure the data rate at the receiver channel. This can be used for protocols such as SDI that has data rates in divisions of 2.

By using this RX local divider, you can support two different data rates without using additional transceiver PLLs. This dynamic reconfiguration mode is available only for the receiver and not applicable to the transmitter. This reconfiguration mode using the RX local divider (/2) is only supported and available in EP4CGX30 (F484 package), EP4CGX50, and EP4CGX75 devices.

**The Second Provided Formula Control C**

# **Transceiver Performance Specifications**

Table 1–21 lists the Cyclone IV GX transceiver specifications.

| Table 1-21. | . Transceiver Specification for Cyclone IV GX Devices | (Part 1 of 4) |

|-------------|-------------------------------------------------------|---------------|

|-------------|-------------------------------------------------------|---------------|

| Symbol/                                                   | Ocuditions                                           |                            | <b>C6</b>    |            |                            | C7, I7        |            |                            |              |          |        |

|-----------------------------------------------------------|------------------------------------------------------|----------------------------|--------------|------------|----------------------------|---------------|------------|----------------------------|--------------|----------|--------|

| Description                                               | Conditions                                           | Min                        | Тур          | Max        | Min                        | Тур           | Max        | Min                        | Тур          | Max      | Unit   |

| Reference Clock                                           |                                                      |                            |              |            |                            | -             |            | <u>.</u>                   |              | <u>.</u> |        |

| Supported I/O<br>Standards                                |                                                      | 1.2 V F                    | PCML, 1.5    | V PCML, 3. | 3 V PCN                    | IL, Differe   | ntial LVPE | CL, LVD                    | S, HCSL      |          |        |

| Input frequency<br>from REFCLK input<br>pins              | _                                                    | 50                         | _            | 156.25     | 50                         | _             | 156.25     | 50                         | _            | 156.25   | MHz    |

| Spread-spectrum<br>modulating clock<br>frequency          | Physical interface<br>for PCI Express<br>(PIPE) mode | 30                         | _            | 33         | 30                         | _             | 33         | 30                         | _            | 33       | kHz    |

| Spread-spectrum<br>downspread                             | PIPE mode                                            | _                          | 0 to<br>0.5% | _          | _                          | 0 to<br>-0.5% | _          | _                          | 0 to<br>0.5% | _        | _      |

| Peak-to-peak<br>differential input<br>voltage             | _                                                    | 0.1                        | _            | 1.6        | 0.1                        | _             | 1.6        | 0.1                        | _            | 1.6      | V      |

| $V_{\text{ICM}}$ (AC coupled)                             |                                                      | 1100 ± 5%                  |              |            |                            | 1100 ± 59     | %          | 1100 ± 5%                  |              |          | mV     |

| $V_{\text{ICM}}$ (DC coupled)                             | HCSL I/O<br>standard for PCIe<br>reference clock     | 250                        | _            | 550        | 250                        | _             | 550        | 250                        | _            | 550      | mV     |

| Transmitter REFCLK<br>Phase Noise <sup>(1)</sup>          | Frequency offset                                     |                            | _            | -123       | _                          | _             | -123       | _                          | _            | -123     | dBc/Hz |

| Transmitter REFCLK<br>Total Jitter <sup>(1)</sup>         | = 1 MHz – 8 MHZ                                      |                            | _            | 42.3       | _                          | _             | 42.3       | _                          | _            | 42.3     | ps     |

| R <sub>ref</sub>                                          | _                                                    |                            | 2000<br>± 1% |            | _                          | 2000<br>± 1%  | _          | _                          | 2000<br>± 1% | _        | Ω      |

| Transceiver Clock                                         |                                                      |                            |              |            |                            |               |            |                            |              |          |        |

| cal_blk_clk <b>clock</b><br>frequency                     | _                                                    | 10                         | _            | 125        | 10                         | _             | 125        | 10                         | _            | 125      | MHz    |

| fixedclk clock<br>frequency                               | PCIe Receiver<br>Detect                              |                            | 125          | _          | _                          | 125           | _          | _                          | 125          | _        | MHz    |

| reconfig_clk<br>clock frequency                           | Dynamic<br>reconfiguration<br>clock frequency        | 2.5/<br>37.5<br><i>(2)</i> | _            | 50         | 2.5/<br>37.5<br><i>(2)</i> | _             | 50         | 2.5/<br>37.5<br><i>(2)</i> | _            | 50       | MHz    |

| Delta time between<br>reconfig_clk                        | —                                                    | —                          | _            | 2          | —                          | _             | 2          | —                          | _            | 2        | ms     |

| Transceiver block<br>minimum<br>power-down pulse<br>width | _                                                    |                            | 1            |            | _                          | 1             |            |                            | 1            |          | μs     |

Table 1–29 lists the active configuration mode specifications for Cyclone IV devices.

| Programming Mode                    | DCLK Range | Typical DCLK | Unit |

|-------------------------------------|------------|--------------|------|

| Active Parallel (AP) <sup>(1)</sup> | 20 to 40   | 33           | MHz  |

| Active Serial (AS)                  | 20 to 40   | 33           | MHz  |

Table 1–29. Active Configuration Mode Specifications for Cyclone IV Devices

#### Note to Table 1-29:

(1) AP configuration mode is only supported for Cyclone IV E devices.

Table 1-30 lists the JTAG timing parameters and values for Cyclone IV devices.

Table 1–30. JTAG Timing Parameters for Cyclone IV Devices (1)

| Symbol                | Parameter                                                    | Min | Max | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>JCP</sub>      | TCK clock period                                             | 40  | —   | ns   |

| t <sub>JCH</sub>      | TCK clock high time                                          | 19  | _   | ns   |

| t <sub>JCL</sub>      | TCK clock low time                                           | 19  | _   | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time for TDI                                 | 1   | _   | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time for TMS                                 | 3   | _   | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                                          | 10  | _   | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output <sup>(2), (3)</sup>                | —   | 15  | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output <sup>(2), (3)</sup> | —   | 15  | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance $(2)$ , $(3)$       | —   | 15  | ns   |

| t <sub>JSSU</sub>     | Capture register setup time                                  | 5   | _   | ns   |

| t <sub>JSH</sub>      | Capture register hold time                                   | 10  | _   | ns   |

| t <sub>JSC0</sub>     | Update register clock to output                              | —   | 25  | ns   |

| t <sub>JSZX</sub>     | Update register high impedance to valid output               | _   | 25  | ns   |

| t <sub>JSXZ</sub>     | Update register valid output to high impedance               | —   | 25  | ns   |

#### Notes to Table 1-30:

(1) For more information about JTAG waveforms, refer to "JTAG Waveform" in "Glossary" on page 1-37.

- (2) The specification is shown for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 16 ns.

- (3) For EP4CGX22, EP4CGX30 (F324 and smaller package), EP4CGX110, and EP4CGX150 devices, the output time specification for 3.3-, 3.0-, and 2.5-V LVTTL/LVCMOS operation of JTAG pins is 16 ns. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the output time specification is 18 ns.

## **Periphery Performance**

This section describes periphery performance, including high-speed I/O and external memory interface.

I/O performance supports several system interfaces, such as the high-speed I/O interface, external memory interface, and the PCI/PCI-X bus interface. I/Os using the SSTL-18 Class I termination standard can achieve up to the stated DDR2 SDRAM interfacing speeds. I/Os using general-purpose I/O standards such as 3.3-, 3.0-, 2.5-, 1.8-, or 1.5-LVTTL/LVCMOS are capable of a typical 200 MHz interfacing frequency with a 10 pF load.

| Symbol                       | Modes | C6 C7, I7 |     |     | 1   | C8, A7 C8L, I8L |     |     |     | L   |     | Unit |     |     |     |     |      |

|------------------------------|-------|-----------|-----|-----|-----|-----------------|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|------|

|                              |       | Min       | Тур | Max | Min | Тур             | Max | Min | Тур | Max | Min | Тур  | Max | Min | Тур | Max | UIII |

| t <sub>LOCK</sub> <i>(2)</i> |       |           |     | 1   |     |                 | 1   |     |     | 1   |     | _    | 1   |     |     | 1   | ms   |

### Table 1–32. Emulated RSDS\_E\_1R Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

Notes to Table 1-32:

(1) Emulated RSDS\_E\_1R transmitter is supported at the output pin of all I/O Banks of Cyclone IV E devices and I/O Banks 3, 4, 5, 6, 7, 8, and 9 of Cyclone IV GX devices.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                             | Modes                                    |     | C6  |     |     | C7, 17 | 7     |     | C8, A | 7     |     | C8L, I | 8L    |     | C9L |       | Uit  |

|------------------------------------|------------------------------------------|-----|-----|-----|-----|--------|-------|-----|-------|-------|-----|--------|-------|-----|-----|-------|------|

| Symbol                             | wodes                                    | Min | Тур | Max | Min | Тур    | Max   | Min | Тур   | Max   | Min | Тур    | Max   | Min | Тур | Max   | Unit |

|                                    | ×10                                      | 5   |     | 200 | 5   |        | 155.5 | 5   |       | 155.5 | 5   | —      | 155.5 | 5   |     | 132.5 | MHz  |

|                                    | ×8                                       | 5   |     | 200 | 5   | _      | 155.5 | 5   | —     | 155.5 | 5   | —      | 155.5 | 5   | _   | 132.5 | MHz  |

| f <sub>HSCLK</sub> (input<br>clock | ×7                                       | 5   | _   | 200 | 5   | _      | 155.5 | 5   | _     | 155.5 | 5   | —      | 155.5 | 5   | _   | 132.5 | MHz  |

| frequency)                         | ×4                                       | 5   | _   | 200 | 5   | _      | 155.5 | 5   | _     | 155.5 | 5   | —      | 155.5 | 5   | _   | 132.5 | MHz  |

| ,                                  | ×2                                       | 5   |     | 200 | 5   | _      | 155.5 | 5   | —     | 155.5 | 5   | —      | 155.5 | 5   | _   | 132.5 | MHz  |

|                                    | ×1                                       | 5   | _   | 400 | 5   | _      | 311   | 5   | _     | 311   | 5   | —      | 311   | 5   | _   | 265   | MHz  |

|                                    | ×10                                      | 100 |     | 400 | 100 |        | 311   | 100 |       | 311   | 100 | _      | 311   | 100 |     | 265   | Mbps |

|                                    | ×8                                       | 80  |     | 400 | 80  | _      | 311   | 80  | —     | 311   | 80  | —      | 311   | 80  | _   | 265   | Mbps |

| Device<br>operation in             | ×7                                       | 70  | _   | 400 | 70  | _      | 311   | 70  | _     | 311   | 70  | —      | 311   | 70  | _   | 265   | Mbps |

| Mbps                               | ×4                                       | 40  |     | 400 | 40  |        | 311   | 40  |       | 311   | 40  | _      | 311   | 40  |     | 265   | Mbps |

|                                    | ×2                                       | 20  |     | 400 | 20  | _      | 311   | 20  | —     | 311   | 20  | —      | 311   | 20  | _   | 265   | Mbps |

|                                    | ×1                                       | 10  |     | 400 | 10  | _      | 311   | 10  | —     | 311   | 10  | —      | 311   | 10  | _   | 265   | Mbps |

| t <sub>DUTY</sub>                  | —                                        | 45  |     | 55  | 45  |        | 55    | 45  |       | 55    | 45  | _      | 55    | 45  |     | 55    | %    |

| TCCS                               | —                                        | —   |     | 200 | —   | _      | 200   | _   | —     | 200   | —   | —      | 200   | —   | _   | 200   | ps   |

| Output jitter<br>(peak to peak)    | —                                        | _   | _   | 500 | _   | _      | 500   | _   | _     | 550   | _   | _      | 600   | _   | _   | 700   | ps   |

| t <sub>RISE</sub>                  | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500    |       |     | 500   | _     | _   | 500    | _     | _   | 500 |       | ps   |

| t <sub>FALL</sub>                  | 20 - 80%,<br>C <sub>LOAD</sub> =<br>5 pF | _   | 500 | _   | _   | 500    | _     |     | 500   | _     | _   | 500    |       | _   | 500 | _     | ps   |

| t <sub>LOCK</sub> (3)              | —                                        | —   | —   | 1   | —   | —      | 1     |     | —     | 1     | —   | _      | 1     | —   | —   | 1     | ms   |

Table 1–33. Mini-LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (2), (4)

Notes to Table 1-33:

(1) Applicable for true and emulated mini-LVDS transmitter.

(2) Cyclone IV E—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 1, 2, 5, and 6. Emulated mini-LVDS transmitter is supported at the output pin of all I/O banks.

Cyclone IV GY—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of Row I/O Banks 5.

Cyclone IV GX—true mini-LVDS transmitter is only supported at the output pin of Row I/O Banks 5 and 6. Emulated mini-LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(3)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(4) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Symbol                          | Modes | C6  |     | C7, | , 17 | C8, | A7  | C8L, | , 18L | C   | 9L  | Unit |

|---------------------------------|-------|-----|-----|-----|------|-----|-----|------|-------|-----|-----|------|

|                                 |       | Min | Max | Min | Max  | Min | Max | Min  | Max   | Min | Max | Unit |

| t <sub>DUTY</sub>               | —     | 45  | 55  | 45  | 55   | 45  | 55  | 45   | 55    | 45  | 55  | %    |

| TCCS                            | —     | _   | 200 | —   | 200  | _   | 200 | _    | 200   | —   | 200 | ps   |

| Output jitter<br>(peak to peak) | _     |     | 500 | _   | 500  | _   | 550 | _    | 600   | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)           | _     |     | 1   | _   | 1    |     | 1   |      | 1     | _   | 1   | ms   |

### Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices <sup>(1), (3)</sup> (Part 2 of 2)

#### Notes to Table 1-35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

| Sumbol                    | Madaa | C   | 6     | C7, | , 17  | C8, | A7    | C8L | , 18L | CS  |     |      |

|---------------------------|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-----|------|

| Symbol                    | Modes | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Min | Max | Unit |

|                           | ×10   | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×8    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

| f <sub>HSCLK</sub> (input | ×7    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

| clock<br>frequency)       | ×4    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×2    | 10  | 437.5 | 10  | 370   | 10  | 320   | 10  | 320   | 10  | 250 | MHz  |

|                           | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265 | MHz  |

|                           | ×10   | 100 | 875   | 100 | 740   | 100 | 640   | 100 | 640   | 100 | 500 | Mbps |

|                           | ×8    | 80  | 875   | 80  | 740   | 80  | 640   | 80  | 640   | 80  | 500 | Mbps |

| HSIODR                    | ×7    | 70  | 875   | 70  | 740   | 70  | 640   | 70  | 640   | 70  | 500 | Mbps |

| HOIDDA                    | ×4    | 40  | 875   | 40  | 740   | 40  | 640   | 40  | 640   | 40  | 500 | Mbps |

|                           | ×2    | 20  | 875   | 20  | 740   | 20  | 640   | 20  | 640   | 20  | 500 | Mbps |

|                           | ×1    | 10  | 437.5 | 10  | 402.5 | 10  | 402.5 | 10  | 362   | 10  | 265 | Mbps |

| SW                        | —     | _   | 400   | _   | 400   | _   | 400   | _   | 550   | _   | 640 | ps   |

| Input jitter<br>tolerance | _     | _   | 500   | _   | 500   | _   | 550   | _   | 600   | _   | 700 | ps   |

| t <sub>LOCK</sub> (2)     | —     | _   | 1     | —   | 1     | _   | 1     | —   | 1     | —   | 1   | ms   |

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

#### Notes to Table 1-36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2)  $t_{LOCK}$  is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

## **External Memory Interface Specifications**

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy to implement.