## Intel - EP4CE15F17C7 Datasheet

Welcome to <u>E-XFL.COM</u>

## Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Product Status                 | Active                                                  |

|--------------------------------|---------------------------------------------------------|

| Number of LABs/CLBs            | 963                                                     |

| Number of Logic Elements/Cells | 15408                                                   |

| Total RAM Bits                 | 516096                                                  |

| Number of I/O                  | 165                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15f17c7 |

|                                |                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

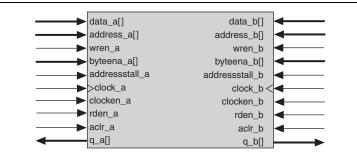

## **True Dual-Port Mode**

True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write, at two different clock frequencies. Figure 3–10 shows Cyclone IV devices true dual-port memory configuration.

## Note to Figure 3-10:

(1) True dual-port memory supports input or output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M9K blocks in true dual-port mode is 512 × 16-bit (18-bit with parity).

Table 3–4 lists the possible M9K block mixed-port width configurations.

| Dood Port | Write Port   |              |              |              |              |              |              |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 1024 × 9     | 512 × 18     |

| 8192 × 1  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 2048 × 4  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 1024 × 8  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |

| 512 × 16  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | —            |

| 1024 × 9  | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ |

| 512 × 18  | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ |

Table 3-4. Cyclone IV Devices M9K Block Mixed-Width Configurations (True Dual-Port Mode)

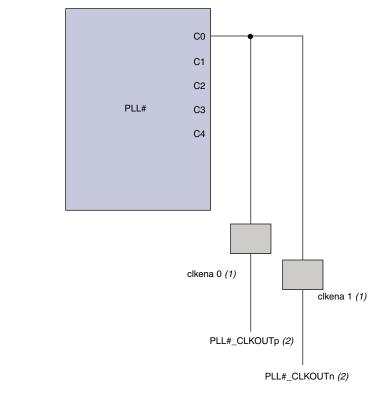

In true dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "New Data" at that location or "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15. Figure 5–11 shows the external clock outputs for PLLs.

#### Notes to Figure 5-11:

- (1) These external clock enable signals are available only when using the ALTCLKCTRL megafunction.

- (2) PLL#\_CLKOUTp and PLL#\_CLKOUTn pins are dual-purpose I/O pins that you can use as one single-ended clock output or one differential clock output. When using both pins as single-ended I/Os, one of them can be the clock output while the other pin is configured as a regular user I/O.

Each pin of a differential output pair is 180° out of phase. The Quartus II software places the NOT gate in your design into the I/O element to implement 180° phase with respect to the other pin in the pair. The clock output pin pairs support the same I/O standards as standard output pins.

To determine which I/O standards are supported by the PLL clock input and output pins, refer to the *Cyclone IV Device I/O Features* chapter.

Cyclone IV PLLs can drive out to any regular I/O pin through the GCLK. You can also use the external clock output pins as GPIO pins if external PLL clocking is not required.

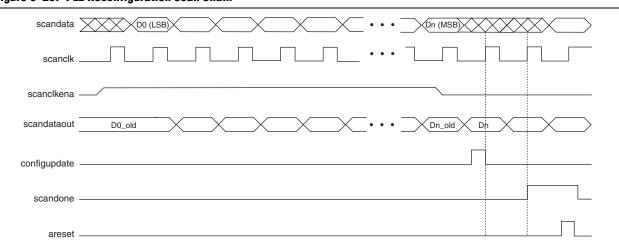

Figure 5–23 shows a functional simulation of the PLL reconfiguration feature.

Figure 5-23. PLL Reconfiguration Scan Chain

When reconfiguring the counter clock frequency, the corresponding counter phase shift settings cannot be reconfigured using the same interface. You can reconfigure phase shifts in real time using the dynamic phase shift reconfiguration interface. If you reconfigure the counter frequency, but wish to keep the same non-zero phase shift setting (for example, 90°) on the clock output, you must reconfigure the phase shift after reconfiguring the counter clock frequency.

## Post-Scale Counters (C0 to C4)

You can configure multiply or divide values and duty cycle of post-scale counters in real time. Each counter has an 8-bit high time setting and an 8-bit low time setting. The duty cycle is the ratio of output high or low time to the total cycle time, that is the sum of the two. Additionally, these counters have two control bits, rbypass, for bypassing the counter, and rselodd, to select the output clock duty cycle.

When the rbypass bit is set to 1, it bypasses the counter, resulting in a divide by one. When this bit is set to 0, the PLL computes the effective division of the VCO output frequency based on the high and low time counters. For example, if the post-scale divide factor is 10, the high and low count values are set to 5 and 5, to achieve a 50–50% duty cycle. The PLL implements this duty cycle by transitioning the output clock from high-to-low on the rising edge of the VCO output clock. However, a 4 and 6 setting for the high and low count values, respectively, would produce an output clock with a 40–60% duty cycle.

The rselodd bit indicates an odd divide factor for the VCO output frequency with a 50% duty cycle. For example, if the post-scale divide factor is three, the high and low time count values are 2 and 1, respectively, to achieve this division. This implies a 67%–33% duty cycle. If you need a 50%–50% duty cycle, you must set the rselodd control bit to 1 to achieve this duty cycle despite an odd division factor. The PLL implements this duty cycle by transitioning the output clock from high-to-low on a falling edge of the VCO output clock. When you set rselodd = 1, subtract 0.5 cycles from the high time and add 0.5 cycles to the low time.

For example:

■ High time count = 2 cycles

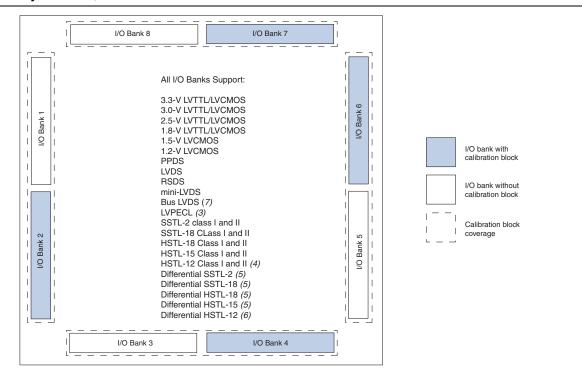

## Figure 6–9 shows the overview of Cyclone IV E I/O banks.

Figure 6–9. Cyclone IV E I/O Banks (1), (2)

#### Notes to Figure 6-9:

- (1) This is a top view of the silicon die. This is only a graphical representation. For exact pin locations, refer to the pin list and the Quartus II software.

- (2) True differential (PPDS, LVDS, mini-LVDS, and RSDS I/O standards) outputs are supported in row I/O banks 1, 2, 5, and 6 only. External resistors are needed for the differential outputs in column I/O banks.

- (3) The LVPECL I/O standard is only supported on clock input pins. This I/O standard is not supported on output pins.

- (4) The HSTL-12 Class II is supported in column I/O banks 3, 4, 7, and 8 only.

- (5) The differential SSTL-18 and SSTL-2, differential HSTL-18, and HSTL-15 I/O standards are supported only on clock input pins and phase-locked loops (PLLs) output clock pins. Differential SSTL-18, differential HSTL-18, and HSTL-15 I/O standards do not support Class II output.

- (6) The differential HSTL-12 I/O standard is only supported on clock input pins and PLL output clock pins. Differential HSTL-12 Class II is supported only in column I/O banks 3, 4, 7, and 8.

- (7) BLVDS output uses two single-ended outputs with the second output programmed as inverted. BLVDS input uses true LVDS input buffer.

| Date          | Version | Changes                                                                                                             |  |  |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------|--|--|

|               |         | <ul> <li>Added Cyclone IV E devices information for the Quartus II software version 9.1 SP1<br/>release.</li> </ul> |  |  |

|               |         | ■ Updated Table 6–2, Table 6–3, and Table 6–10.                                                                     |  |  |

| February 2010 | 2.0     | <ul> <li>Updated "I/O Banks" section.</li> </ul>                                                                    |  |  |

| -             |         | Added Figure 6–9.                                                                                                   |  |  |

|               |         | Updated Figure 6–10 and Figure 6–11.                                                                                |  |  |

|               |         | Added Table 6–4, Table 6–6, and Table 6–8.                                                                          |  |  |

| November 2009 | 1.0     | Initial release.                                                                                                    |  |  |

Table 6–12. Document Revision History (Part 2 of 2)

## 7. External Memory Interfaces in Cyclone IV Devices

CYIV-51007-2.6

This chapter describes the memory interface pin support and the external memory interface features of Cyclone<sup>®</sup> IV devices.

In addition to an abundant supply of on-chip memory, Cyclone IV devices can easily interface with a broad range of external memory devices, including DDR2 SDRAM, DDR SDRAM, and QDR II SRAM. External memory devices are an important system component of a wide range of image processing, storage, communications, and general embedded applications.

Altera recommends that you construct all DDR2 or DDR SDRAM external memory interfaces using the Altera<sup>®</sup> ALTMEMPHY megafunction. You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs. Cyclone IV devices support QDR II interfaces electrically, but Altera does not supply controller or physical layer (PHY) megafunctions for QDR II interfaces.

This chapter includes the following sections:

- "Cyclone IV Devices Memory Interfaces Pin Support" on page 7–2

- "Cyclone IV Devices Memory Interfaces Features" on page 7–12

• For more information about supported maximum clock rate, device and pin planning, IP implementation, and device termination, refer to the *External Memory Interface Handbook*.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

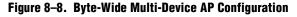

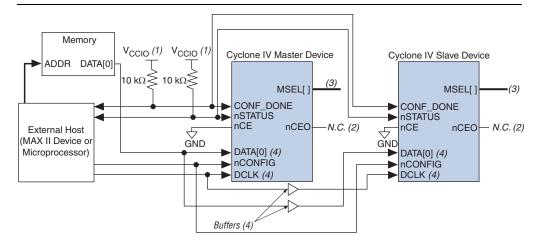

## **Byte-Wide Multi-Device AP Configuration**

The simpler method for multi-device AP configuration is the byte-wide multi-device AP configuration. In the byte-wide multi-device AP configuration, the LSB of the DATA [7..0] pin from the flash and master device (set to the AP configuration scheme) is connected to the slave devices set to the FPP configuration scheme, as shown in Figure 8–8.

## Notes to Figure 8-8:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the V<sub>CCIO</sub> supply voltage of the I/O bank in which the nCE pin resides.

- (3) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the master device in AP mode and the slave devices in FPP mode. To connect MSEL [3..0] for the master device in AP mode and the slave devices in FPP mode, refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (6) Connect the repeater buffers between the Cyclone IV E master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

## **Word-Wide Multi-Device AP Configuration**

The more efficient setup is one in which some of the slave devices are connected to the LSB of the DATA[7..0] and the remaining slave devices are connected to the MSB of the DATA[15..8]. In the word-wide multi-device AP configuration, the nCEO pin of the master device enables two separate daisy chains of slave devices, allowing both chains to be programmed concurrently, as shown in Figure 8–9.

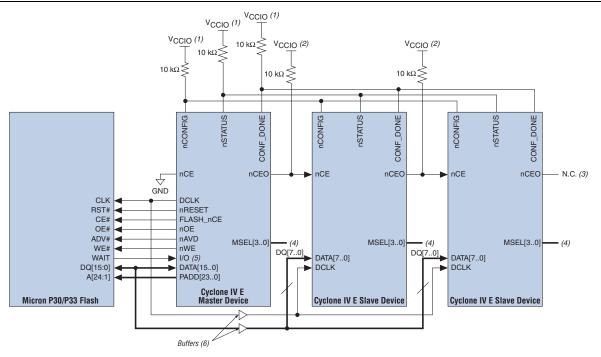

Figure 8–10 shows the AP configuration with multiple bus masters.

Figure 8–10. AP Configuration with Multiple Bus Masters

#### Notes to Figure 8–10:

- (1) Connect the pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) The nCEO pin is left unconnected or used as a user I/O pin when it does not feed the nCE pin of another device.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) The AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use the normal I/O to monitor the WAIT signal from the Micron P30 or P33 flash.

- (5) When cascading Cyclone IV E devices in a multi-device AP configuration, connect the repeater buffers between the master device and slave devices for DATA [15..0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8–5.

- (6) The other master device must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements" on page 8-5.

- (7) The other master device can control the AP configuration bus by driving the nCE to high with an output high on the I/O pin.

- (8) The other master device can pulse nCONFIG if it is under system control and not tied to  $V_{CCIO}$ .

After the first device completes configuration in a multi-device configuration chain, its nCEO pin drives low to activate the nCE pin of the second device, which prompts the second device to begin configuration. The second device in the chain begins configuration in one clock cycle. Therefore, the transfer of data destinations is transparent to the external host device. nCONFIG, nSTATUS, DCLK, DATA[0], and CONF\_DONE configuration pins are connected to every device in the chain. To ensure signal integrity and prevent clock skew problems, configuration signals may require buffering. Ensure that DCLK and DATA lines are buffered. All devices initialize and enter user mode at the same time because all CONF\_DONE pins are tied together.

If any device detects an error, configuration stops for the entire chain and you must reconfigure the entire chain because all nSTATUS and CONF\_DONE pins are tied together. For example, if the first device flags an error on nSTATUS, it resets the chain by pulling its nSTATUS pin low. This behavior is similar to a single device detecting an error.

You can have multiple devices that contain the same configuration data in your system. To support this configuration scheme, all device nCE inputs are tied to GND, while the nCEO pins are left floating. nCONFIG, nSTATUS, DCLK, DATA[0], and CONF\_DONE configuration pins are connected to every device in the chain. To ensure signal integrity and prevent clock skew problems, configuration signals may require buffering. Ensure that the DCLK and DATA lines are buffered. Devices must be of the same density and package. All devices start and complete configuration at the same time.

Figure 8–15 shows a multi-device PS configuration when both Cyclone IV devices are receiving the same configuration data.

## Figure 8-15. Multi-Device PS Configuration When Both Devices Receive the Same Data

#### Notes to Figure 8-15:

- (1) You must connect the pull-up resistor to a supply that provides an acceptable input signal for all devices in the chain.  $V_{CC}$  must be high enough to meet the  $V_{IH}$  specification of the I/O on the device and the external host.

- (2) The nCEO pins of both devices are left unconnected or used as user I/O pins when configuring the same configuration data into multiple devices.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect the MSEL pins, refer to Table 8–3 on page 8–8, Table 8–4 on page 8–8, and Table 8–5 on page 8–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) All I/O inputs must maintain a maximum AC voltage of 4.1 V. DATA [0] and DCLK must fit the maximum overshoot outlined in Equation 8–1 on page 8–5.

You can perform JTAG testing on Cyclone IV devices before, during, and after configuration. Cyclone IV devices support the BYPASS, IDCODE, and SAMPLE instructions during configuration without interrupting configuration. All other JTAG instructions can only be issued by first interrupting configuration and reprogramming I/O pins with the ACTIVE\_DISENGAGE and CONFIG\_IO instructions.

The CONFIG\_IO instruction allows you to configure the I/O buffers through the JTAG port and interrupts configuration when issued after the ACTIVE\_DISENGAGE instruction. This instruction allows you to perform board-level testing prior to configuring the Cyclone IV device or waiting for a configuration device to complete configuration. Prior to issuing the CONFIG\_IO instruction, you must issue the ACTIVE\_DISENGAGE instruction. This is because in Cyclone IV devices, the CONFIG\_IO instruction does not hold nSTATUS low until reconfiguration, so you must disengage the active configuration mode controller when active configuration is interrupted. The ACTIVE\_DISENGAGE instruction places the active configuration mode controllers in an idle state prior to JTAG programming. Additionally, the ACTIVE\_ENGAGE instruction allows you to re-engage a disengaged active configuration mode controller.

You must follow a specific flow when executing the ACTIVE\_DISENGAGE, CONFIG\_IO, and ACTIVE\_ENGAGE JTAG instructions in Cyclone IV devices.

The chip-wide reset (DEV\_CLRn) and chip-wide output enable (DEV\_OE) pins in Cyclone IV devices do not affect JTAG boundary-scan or programming operations. Toggling these pins do not affect JTAG operations (other than the usual boundary-scan operation).

When designing a board for JTAG configuration of Cyclone IV devices, consider the dedicated configuration pins. Table 8–15 describes how you must connect these pins during JTAG configuration.

Table 8–15. Dedicated Configuration Pin Connections During JTAG Configuration

| Signal    | Description                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nCE       | On all Cyclone IV devices in the chain, nCE must be driven low by connecting it to GND, pulling it low through a resistor, or driving it by some control circuitry. For devices that are also in multi-device AS, AP, PS, or FPP configuration chains, you must connect the nCE pins to GND during JTAG configuration or JTAG configured in the same order as the configuration chain. |

| nCEO      | On all Cyclone IV devices in the chain, $nCEO$ is left floating or connected to the $nCE$ of the next device.                                                                                                                                                                                                                                                                          |

| MSEL      | These pins must not be left floating. These pins support whichever non-JTAG configuration that you used in production. If you only use JTAG configuration, tie these pins to GND.                                                                                                                                                                                                      |

| nCONFIG   | Driven high by connecting to the $V_{CCIO}$ supply of the bank in which the pin resides and pulling up through a resistor or driven high by some control circuitry.                                                                                                                                                                                                                    |

| nSTATUS   | Pull to the V <sub>CCI0</sub> supply of the bank in which the pin resides through a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each nSTATUS pin must be pulled up to the V <sub>CCI0</sub> individually.                                                                                                                                        |

| CONF_DONE | Pull to the V <sub>CCIO</sub> supply of the bank in which the pin resides through a 10-k $\Omega$ resistor. When configuring multiple devices in the same JTAG chain, each CONF_DONE pin must be pulled up to V <sub>CCIO</sub> supply of the bank in which the pin resides individually. CONF_DONE going high at the end of JTAG configuration indicates successful configuration.    |

| DCLK      | Must not be left floating. Drive low or high, whichever is more convenient on your board.                                                                                                                                                                                                                                                                                              |

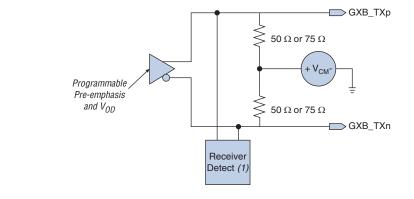

## **Transmitter Output Buffer**

Figure 1–11 shows the transmitter output buffer block diagram.

#### Note to Figure 1-11:

(1) Receiver detect function is specific for PCIe protocol implementation only. For more information, refer to "PCI Express (PIPE) Mode" on page 1–52.

The Cyclone IV GX transmitter output buffers support the **1.5-V PCML** I/O standard and are powered by VCCH\_GXB power pins with 2.5-V supply. The 2.5-V supply on VCCH\_GXB pins are regulated internally to 1.5-V for the transmitter output buffers. The transmitter output buffers support the following additional features:

- Programmable differential output voltage (V<sub>OD</sub>)—customizes the V<sub>OD</sub> up to 1200 mV to handle different trace lengths, various backplanes, and various receiver requirements.

- Programmable pre-emphasis—boosts high-frequency components in the transmitted signal to maximize the data eye opening at the far-end. The high-frequency components might be attenuated in the transmission media due to data-dependent jitter and intersymbol interference (ISI) effects. The requirement for pre-emphasis increases as the data rates through legacy backplanes increase.

- Programmable differential on-chip termination (OCT)—provides calibrated OCT at differential 100 Ω or 150 Ω with on-chip transmitter common mode voltage (V<sub>CM</sub>) at 0.65 V. V<sub>CM</sub> is tri-stated when you disable the OCT to use external termination.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- The Cyclone IV GX transmitter output buffers are current-mode drivers. The resulting V<sub>OD</sub> voltage is therefore a function of the transmitter termination value. For lists of supported V<sub>OD</sub> settings, refer to the *Cyclone IV Device Data Sheet*.

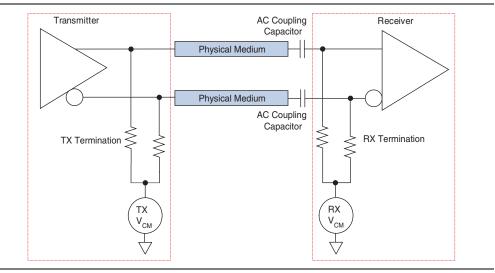

The high-speed serial link can be AC- or DC-coupled, depending on the serial protocol implementation. In an AC-coupled link, the AC-coupling capacitor blocks the transmitter DC common mode voltage as shown in Figure 1–12. Receiver OCT and on-chip biasing circuitry automatically restores the common mode voltage. The biasing circuitry is also enabled by enabling OCT. If you disable the OCT, then you must externally terminate and bias the receiver. AC-coupled links are required for PCIe, GbE, Serial RapidIO, SDI, XAUI, SATA, V-by-One and Display Port protocols.

Figure 1–12. AC-Coupled Link with OCT

| Block         | Port Name                 | Input/<br>Output | Clock Domain                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                         |  |  |

|---------------|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| rx_tec<br>rx_ | rx_syncstatus             | Output           | Synchronous to tx_clkout (non-<br>bonded modes with rate match<br>FIFO), rx_clkout (non-bonded<br>modes without rate match FIFO),<br>coreclkout (bonded modes), or<br>rx_coreclk (when using the<br>optional rx_coreclk input) | Word alignment synchronization status indicator. This signal passes through the RX Phase Compensation FIFO. <ul> <li>Not available in bit-slip mode</li> </ul>                                                                                                                                                      |  |  |

|               | rx_patternde<br>tect      | Output           | Synchronous to tx_clkout (non-<br>bonded modes with rate match<br>FIFO), rx_clkout (non-bonded<br>modes without rate match FIFO),<br>coreclkout (bonded modes), or<br>rx_coreclk (when using the<br>optional rx_coreclk input) | Indicates when the word alignment logic detects the<br>alignment pattern in the current word boundary. This<br>signal passes through the RX Phase Compensation FIFO.                                                                                                                                                |  |  |

|               | rx_bitslip                | Input            | Asynchronous signal. Minimum<br>pulse width is two<br>parallel clock cycles.                                                                                                                                                   | <ul> <li>Bit-slip control for the word aligner configured in bit-s mode.</li> <li>At every rising edge, word aligner slips one bit into the received data stream, effectively shifting the word boundary by one bit.</li> </ul>                                                                                     |  |  |

|               | rx_rlv                    | Output           | Asynchronous signal. Driven for a<br>minimum of two recovered clock<br>cycles in configurations without<br>byte serializer and a minimum of<br>three recovered clock cycles in<br>configurations with byte serializer.         | <ul> <li>Run-length violation indicator.</li> <li>A high pulse indicates that the number of consecutive 1s or 0s in the received data stream exceeds the programmed run length violation threshold.</li> </ul>                                                                                                      |  |  |

|               | rx_invpolarity            | Input            | Asynchronous signal. Minimum<br>pulse width is two parallel clock<br>cycles.                                                                                                                                                   | <ul> <li>Generic receiver polarity inversion control.</li> <li>A high level to invert the polarity of every bit of the 8-<br/>or 10-bit data to the word aligner.</li> </ul>                                                                                                                                        |  |  |

|               | rx_enapattern<br>align    | Input            | Asynchronous signal.                                                                                                                                                                                                           | Controls the word aligner operation configured in manual alignment mode.                                                                                                                                                                                                                                            |  |  |

|               | rx_rmfifodata<br>inserted | Output           | Synchronous to tx_clkout<br>(non-bonded modes) or<br>coreclkout (bonded modes)                                                                                                                                                 | <ul> <li>Rate match FIFO insertion status indicator.</li> <li>A high level indicates the rate match pattern byte is inserted to compensate for the ppm difference in the reference clock frequencies between the upstream</li> </ul>                                                                                |  |  |

|               | rx_rmfifodata<br>deleted  | Output           | Synchronous to tx_clkout<br>(non-bonded modes) or<br>coreclkout (bonded modes)                                                                                                                                                 | <ul> <li>transmitter and the local receiver.</li> <li>Rate match FIFO deletion status indicator.</li> <li>A high level indicates the rate match pattern byte is deleted to compensate for the ppm difference in the reference clock frequencies between the upstream transmitter and the local receiver.</li> </ul> |  |  |

Table 3–4 describes the tx\_datainfull[21..0] FPGA fabric-transceiver channel interface signals.

| FPGA Fabric-Transceiver Channel<br>Interface Description             | Transmit Signal Description (Based on Cyclone IV GX Supported FPGA<br>Fabric-Transceiver Channel Interface Widths)                                                                                           |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                      | <pre>tx_datainfull[7:0]: 8-bit data (tx_datain)</pre>                                                                                                                                                        |  |  |

|                                                                      | The following signals are used only in 8B/10B modes:                                                                                                                                                         |  |  |

|                                                                      | <pre>tx_datainfull[8]: Control bit (tx_ctrlenable)</pre>                                                                                                                                                     |  |  |

|                                                                      | tx_datainfull[9]                                                                                                                                                                                             |  |  |

| 8-bit FPGA fabric-Transceiver Channel<br>Interface                   | Transmitter force disparity Compliance (PCI Express [PIPE]) (tx_forcedisp) in all modes except PCI Express (PIPE) functional mode. For PCI Express (PIPE) functional mode, (tx_forcedispcompliance) is used. |  |  |

|                                                                      | For non-PIPE:                                                                                                                                                                                                |  |  |

|                                                                      | <pre>tx_datainfull[10]: Forced disparity value (tx_dispval)</pre>                                                                                                                                            |  |  |

|                                                                      | For PCIe:                                                                                                                                                                                                    |  |  |

|                                                                      | <pre>tx_datainfull[10]: Forced electrical idle (tx_forceelecidle)</pre>                                                                                                                                      |  |  |

| 10-bit FPGA fabric-Transceiver<br>Channel Interface                  | <pre>tx_datainfull[9:0]:10-bit data (tx_datain)</pre>                                                                                                                                                        |  |  |

|                                                                      | Two 8-bit Data (tx_datain)                                                                                                                                                                                   |  |  |

|                                                                      | <pre>tx_datainfull[7:0] - tx_datain (LSByte) and tx_datainfull[18:11] - tx_datain (MSByte)</pre>                                                                                                             |  |  |

|                                                                      | The following signals are used only in 8B/10B modes:                                                                                                                                                         |  |  |

|                                                                      | <pre>tx_datainfull[8] - tx_ctrlenable (LSB) and tx_datainfull[19] -<br/>tx_ctrlenable (MSB)</pre>                                                                                                            |  |  |

|                                                                      | Force Disparity Enable                                                                                                                                                                                       |  |  |

|                                                                      | For non-PIPE:                                                                                                                                                                                                |  |  |

| 16-bit FPGA fabric-Transceiver<br>Channel Interface with PCS-PMA set | <pre>tx_datainfull[9] - tx_forcedisp (LSB) and tx_datainfull[20] - tx_forcedisp (MSB)</pre>                                                                                                                  |  |  |

| to 8/10 bits                                                         | For PCIe:                                                                                                                                                                                                    |  |  |

|                                                                      | <pre>tx_datainfull[9] - tx_forcedispcompliance and tx_datainfull[20] - 0</pre>                                                                                                                               |  |  |

|                                                                      | Force Disparity Value                                                                                                                                                                                        |  |  |

|                                                                      | For non-PIPE:                                                                                                                                                                                                |  |  |

|                                                                      | <pre>tx_datainfull[10] - tx_dispval (LSB) and tx_datainfull[21] - tx_dispval (MSB)</pre>                                                                                                                     |  |  |

|                                                                      | For PCIe:                                                                                                                                                                                                    |  |  |

|                                                                      | <pre>tx_datainfull[10] - tx_forceelecidle and tx_datainfull[21] -<br/>tx_forceelecidle</pre>                                                                                                                 |  |  |

| 20-bit FPGA fabric-Transceiver                                       | Two 10-bit Data (tx_datain)                                                                                                                                                                                  |  |  |

| Channel Interface with PCS-PMA set to 10 bits                        | <pre>tx_datainfull[9:0] - tx_datain (LSByte) and tx_datainfull[20:11] - tx_datain (MSByte)</pre>                                                                                                             |  |  |

## Table 3–4. tx\_datainfull[21..0] FPGA Fabric-Transceiver Channel Interface Signal Descriptions <sup>(1)</sup>

Note to Table 3-4:

(1) For all transceiver-related ports, refer to the "Transceiver Port Lists" section in the Cyclone IV GX Transceiver Architecture chapter.

## **Clocking/Interface Options**

The following describes the **Clocking/Interface** options available in Cyclone IV GX devices. The core clocking setup describes the transceiver core clocks that are the write and read clocks of the Transmit Phase Compensation FIFO and the Receive Phase Compensation FIFO, respectively. Core clocking is classified as transmitter core clocking and receiver core clocking.

Table 3–6 lists the supported clocking interface settings for channel reconfiguration mode in Cyclone IV GX devices.

| Mode                                                            |                                                                        |  |  |

|-----------------------------------------------------------------|------------------------------------------------------------------------|--|--|

| ALTGX Setting                                                   | Description                                                            |  |  |

| Dynamic Reconfiguration Channel Internal and Interface Settings |                                                                        |  |  |

|                                                                 | Select one of the available options:                                   |  |  |

| How should the receivers be                                     | Share a single transmitter core clock between receivers                |  |  |

| clocked?                                                        | <ul> <li>Use the respective channel transmitter core clocks</li> </ul> |  |  |

|                                                                 | <ul> <li>Use the respective channel receiver core clocks</li> </ul>    |  |  |

|                                                                 | Select one of the available options:                                   |  |  |

| How should the transmitters be<br>clocked?                      | Share a single transmitter core clock between transmitters             |  |  |

Table 3–6. Dynamic Reconfiguration Clocking Interface Settings in Channel Reconfiguration

Mode

Transmitter core clocking refers to the clock that is used to write the parallel data from the FPGA fabric into the Transmit Phase Compensation FIFO. You can use one of the following clocks to write into the Transmit Phase Compensation FIFO:

Use the respective channel transmitter core clocks

- tx\_coreclk—you can use a clock of the same frequency as tx\_clkout from the FPGA fabric to provide the write clock to the Transmit Phase Compensation FIFO. If you use tx\_coreclk, it overrides the tx\_clkout options in the ALTGX MegaWizard Plug-In Manager.

- tx\_clkout—the Quartus II software automatically routes tx\_clkout to the FPGA fabric and back into the Transmit Phase Compensation FIFO.

# **Contents**

| Chapter Revision Dates                                                                              |

|-----------------------------------------------------------------------------------------------------|

| Additional Information         How to Contact Altera         Typographic Conventions         Info-1 |

| Section I. Device Datasheet                                                                         |

| Chapter 1. Cyclone IV Device Datasheet                                                              |

| Operating Conditions                                                                                |

| Absolute Maximum Ratings                                                                            |

| Maximum Allowed Overshoot or Undershoot Voltage                                                     |

| Recommended Operating Conditions                                                                    |

| ESD Performance                                                                                     |

| DC Characteristics                                                                                  |

| Supply Current                                                                                      |

| Bus Hold                                                                                            |

| OCT Specifications                                                                                  |

| Pin Capacitance                                                                                     |

| Internal Weak Pull-Up and Weak Pull-Down Resistor                                                   |

| Hot-Socketing                                                                                       |

| Schmitt Trigger Input                                                                               |

| I/O Standard Specifications                                                                         |

| Power Consumption                                                                                   |

| Switching Characteristics                                                                           |

| Transceiver Performance Specifications1–17                                                          |

| Core Performance Specifications1–23                                                                 |

| Clock Tree Specifications                                                                           |

| PLL Specifications                                                                                  |

| Embedded Multiplier Specifications 1–26                                                             |

Memory Block Specifications1–26Configuration and JTAG Specifications1–26Periphery Performance1–27High-Speed I/O Specifications1–28External Memory Interface Specifications1–32Duty Cycle Distortion Specifications1–33OCT Calibration Timing Specification1–34I/O Timing1–37Glossary1–37Document Revision History1–42

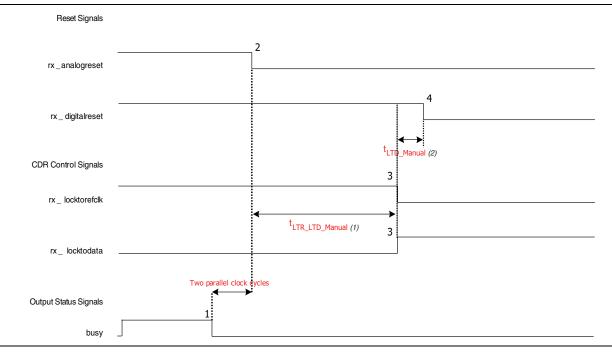

Figure 1–2 shows the lock time parameters in manual mode.

LTD = lock-to-data. LTR = lock-to-reference.

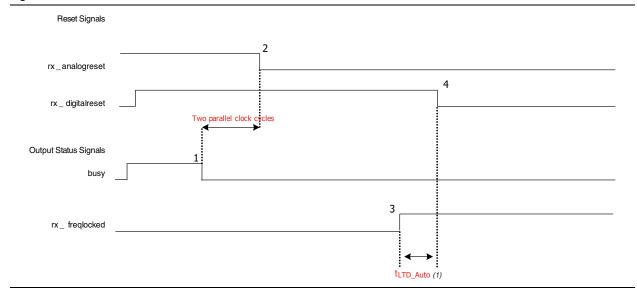

Figure 1–3 shows the lock time parameters in automatic mode.

Figure 1–3. Lock Time Parameters for Automatic Mode

# I/O Timing

Use the following methods to determine I/O timing:

- the Excel-based I/O Timing

- the Quartus II timing analyzer

The Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get a timing budget estimation as part of the link timing analysis. The Quartus II timing analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after place-and-route is complete.

**The Excel-based I/O Timing spreadsheet is downloadable from Cyclone IV Devices** Literature website.

## Glossary

Table 1–46 lists the glossary for this chapter.

| Letter | Term                                                            | Definitions                                                                             |  |  |

|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| Α      | —                                                               | —                                                                                       |  |  |

| В      | —                                                               | _                                                                                       |  |  |

| C      |                                                                 | _                                                                                       |  |  |

| D      | —                                                               |                                                                                         |  |  |

| E      |                                                                 | —                                                                                       |  |  |

| F      | f <sub>HSCLK</sub>                                              | High-speed I/O block: High-speed receiver/transmitter input and output clock frequency. |  |  |

| G      | GCLK                                                            | Input pin directly to Global Clock network.                                             |  |  |

| u      | GCLK PLL                                                        | Input pin to Global Clock network through the PLL.                                      |  |  |

| Н      | HSIODR                                                          | High-speed I/O block: Maximum/minimum LVDS data transfer rate (HSIODR = 1/TUI).         |  |  |

| I      | Input Waveforms<br>for the SSTL<br>Differential I/O<br>Standard | Vswing<br>Vswing<br>V <sub>REF</sub>                                                    |  |  |

## Table 1-46. Glossary (Part 1 of 5)