Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Active                                                  |

| Number of LABs/CLBs            | 963                                                     |

| Number of Logic Elements/Cells | 15408                                                   |

| Total RAM Bits                 | 516096                                                  |

| Number of I/O                  | 165                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 256-LBGA                                                |

| Supplier Device Package        | 256-FBGA (17x17)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce15f17c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Cyclone IV Device Family Architecture**

This section describes Cyclone IV device architecture and contains the following topics:

- "FPGA Core Fabric"

- "I/O Features"

- "Clock Management"

- "External Memory Interfaces"

- "Configuration"

- "High-Speed Transceivers (Cyclone IV GX Devices Only)"

- "Hard IP for PCI Express (Cyclone IV GX Devices Only)"

## **FPGA Core Fabric**

Cyclone IV devices leverage the same core fabric as the very successful Cyclone series devices. The fabric consists of LEs, made of 4-input look up tables (LUTs), memory blocks, and multipliers.

Each Cyclone IV device M9K memory block provides 9 Kbits of embedded SRAM memory. You can configure the M9K blocks as single port, simple dual port, or true dual port RAM, as well as FIFO buffers or ROM. They can also be configured to implement any of the data widths in Table 1–7.

Table 1-7. M9K Block Data Widths for Cyclone IV Device Family

| Mode                            | Data Width Configurations            |

|---------------------------------|--------------------------------------|

| Single port or simple dual port | ×1, ×2, ×4, ×8/9, ×16/18, and ×32/36 |

| True dual port                  | ×1, ×2, ×4, ×8/9, and ×16/18         |

The multiplier architecture in Cyclone IV devices is the same as in the existing Cyclone series devices. The embedded multiplier blocks can implement an  $18 \times 18$  or two  $9 \times 9$  multipliers in a single block. Altera offers a complete suite of DSP IP including finite impulse response (FIR), fast Fourier transform (FFT), and numerically controlled oscillator (NCO) functions for use with the multiplier blocks. The Quartus® II design software's DSP Builder tool integrates MathWorks Simulink and MATLAB design environments for a streamlined DSP design flow.

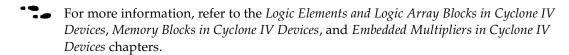

# **Address Clock Enable Support**

Cyclone IV devices M9K memory blocks support an active-low address clock enable, which holds the previous address value for as long as the addressstall signal is high (addressstall = '1'). When you configure M9K memory blocks in dual-port mode, each port has its own independent address clock enable.

Figure 3–2 shows an address clock enable block diagram. The address register output feeds back to its input using a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal.

Figure 3–2. Cyclone IV Devices Address Clock Enable Block Diagram

The address clock enable is typically used to improve the effectiveness of cache memory applications during a cache-miss. The default value for the address clock enable signals is low.

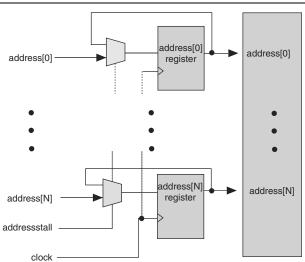

# **GCLK Network Clock Source Generation**

Figure 5–2, Figure 5–3, and Figure 5–4 on page 5–14 show the Cyclone IV PLLs, clock inputs, and clock control block location for different Cyclone IV device densities.

Figure 5-2. Clock Networks and Clock Control Block Locations in EP4CGX15, EP4CGX22, and EP4CGX30 Devices (1), (2)

#### Notes to Figure 5-2:

- (1) The clock networks and clock control block locations apply to all EP4CGX15, EP4CGX22, and EP4CGX30 devices except EP4CGX30 device in F484 package.

- (2) PLL 1 and PLL 2 are multipurpose PLLs while PLL 3 and PLL 4 are general purpose PLLs.

- (3) There are five clock control blocks on each side.

- (4) PLL 4 is only available in EP4CGX22 and EP4CGX30 devices in F324 package.

- (5) The EP4CGX15 device has two DPCLK pins on three sides of the device: DPCLK2 and DPCLK5 on bottom side, DPCLK7 and DPCLK8 on the right side, DPCLK10 and DPCLK13 on the top side of device.

- (6) Dedicated clock pins can feed into this PLL. However, these paths are not fully compensated.

| Table 5-12. | <b>Dynamic Phase</b> | <b>Shifting Control</b> | Signals | (Part 2 of 2) |

|-------------|----------------------|-------------------------|---------|---------------|

|             |                      |                         |         |               |

| Signal Name | Signal Name Description                                                                                                                                                                                                        |                             | Destination                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|

| scanclk     | Free running clock from core used in combination with phasestep to enable or disable dynamic phase shifting. Shared with scanclk for dynamic reconfiguration.                                                                  | GCLK or I/O pins            | PLL<br>reconfiguration<br>circuit |

| phasedone   | When asserted, it indicates to core logic that the phase adjustment is complete and PLL is ready to act on a possible second adjustment pulse. Asserts based on internal PLL timing. De-asserts on the rising edge of scanclk. | PLL reconfiguration circuit | Logic array or<br>I/O pins        |

Table 5–13 lists the PLL counter selection based on the corresponding PHASECOUNTERSELECT setting.

Table 5-13. Phase Counter Select Mapping

|     | phasecounterselec | Colonia |                     |

|-----|-------------------|---------|---------------------|

| [2] | [1]               | [0]     | Selects             |

| 0   | 0                 | 0       | All Output Counters |

| 0   | 0                 | 1       | M Counter           |

| 0   | 1                 | 0       | CO Counter          |

| 0   | 1                 | 1       | C1 Counter          |

| 1   | 0                 | 0       | C2 Counter          |

| 1   | 0                 | 1       | C3 Counter          |

| 1   | 1                 | 0       | C4 Counter          |

To perform one dynamic phase-shift, follow these steps:

- 1. Set Phaseupdown and Phasecounterselect as required.

- 2. Assert PHASESTEP for at least two SCANCLK cycles. Each PHASESTEP pulse allows one phase shift.

- 3. Deassert Phasestep after phasedone goes low.

- 4. Wait for PHASEDONE to go high.

- 5. Repeat steps 1 through 4 as many times as required to perform multiple phase-shifts.

PHASEUPDOWN and PHASECOUNTERSELECT signals are synchronous to SCANCLK and must meet the  $t_{\rm su}$  and  $t_{\rm h}$  requirements with respect to the SCANCLK edges.

You can repeat dynamic phase-shifting indefinitely. For example, in a design where the VCO frequency is set to 1,000 MHz and the output clock frequency is set to 100 MHz, performing 40 dynamic phase shifts (each one yields 125 ps phase shift) results in shifting the output clock by 180°, in other words, a phase shift of 5 ns.

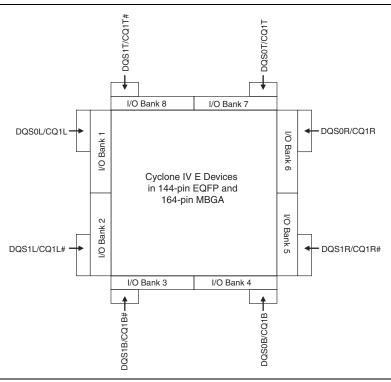

Figure 7–6 shows the location and numbering of the DQS, DQ, or CQ# pins in I/O banks of the Cyclone IV E device in the 144-pin EQFP and 164-pin MBGA packages.

Figure 7–6. DQS, CQ, or CQ# Pins for Cyclone IV E Devices in the 144-Pin EQFP and 164-pin MBGA Packages

In Cyclone IV devices, the  $\times 9$  mode uses the same DQ and DQS pins as the  $\times 8$  mode, and one additional DQ pin that serves as a regular I/O pin in the  $\times 8$  mode. The  $\times 18$  mode uses the same DQ and DQS pins as  $\times 16$  mode, with two additional DQ pins that serve as regular I/O pins in the  $\times 16$  mode. Similarly, the  $\times 36$  mode uses the same DQ and DQS pins as the  $\times 32$  mode, with four additional DQ pins that serve as regular I/O pins in the  $\times 32$  mode. When not used as DQ or DQS pins, the memory interface pins are available as regular I/O pins.

# **Optional Parity, DM, and Error Correction Coding Pins**

Cyclone IV devices support parity in  $\times 9$ ,  $\times 18$ , and  $\times 36$  modes. One parity bit is available per eight bits of data pins. You can use any of the DQ pins for parity in Cyclone IV devices because the parity pins are treated and configured similarly to DQ pins.

DM pins are only required when writing to DDR2 and DDR SDRAM devices. QDR II SRAM devices use the BWS# signal to select the byte to be written into memory. A low signal on the DM or BWS# pin indicates the write is valid. Driving the DM or BWS# pin high causes the memory to mask the DQ signals. Each group of DQS and DQ signals has one DM pin. Similar to the DQ output signals, the DM signals are clocked by the  $-90^{\circ}$  shifted clock.

# **Device Configuration Pins**

Table 8–18 through Table 8–21 describe the connections and functionality of all the configuration related pins on Cyclone IV devices. Table 8–18 and Table 8–19 list the device pin configuration for the Cyclone IV GX and Cyclone IV E, respectively.

Table 8–18. Configuration Pin Summary for Cyclone IV GX Devices

| Bank | Description      | Input/Output  | Dedicated | Powered By                     | Configuration Mode  |

|------|------------------|---------------|-----------|--------------------------------|---------------------|

| 8    | Data[4:2]        | Input         |           | V <sub>ccio</sub>              | FPP                 |

| 3    | Data[7:5]        | Input         | _         | V <sub>CCIO</sub>              | FPP                 |

| 9    | nCSO (2)         | Output        | _         | V <sub>ccio</sub>              | AS                  |

| 3    | CRC_ERROR        | Output        | _         | V <sub>CCIO</sub> /Pull-up (1) | Optional, all modes |

| 9    | DATA [0] (2)     | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP, AS         |

| 9    | DATA[1]/ASDO (2) | Input         |           | V <sub>ccio</sub>              | FPP                 |

| 9    | DATA[1]/ASDO (2) | Output        |           | V <sub>CCIO</sub>              | AS                  |

| 3    | INIT_DONE        | Output        | _         | Pull-up                        | Optional, all modes |

| 3    | nSTATUS          | Bidirectional | Yes       | Pull-up                        | All modes           |

| 9    | nCE              | Input         | Yes       | V <sub>ccio</sub>              | All modes           |

| 9    | (2)              | Input         | Yes       | V <sub>CCIO</sub>              | PS, FPP             |

| 9    | DCLK (2)         | Output        | 162       | V <sub>CCIO</sub>              | AS                  |

| 3    | CONF_DONE        | Bidirectional | Yes       | Pull-up                        | All modes           |

| 9    | TDI              | Input         | Yes       | V <sub>CCIO</sub>              | JTAG                |

| 9    | TMS              | Input         | Yes       | V <sub>ccio</sub>              | JTAG                |

| 9    | TCK              | Input         | Yes       | V <sub>ccio</sub>              | JTAG                |

| 9    | nCONFIG          | Input         | Yes       | V <sub>CCIO</sub>              | All modes           |

| 8    | CLKUSR           | Input         | _         | V <sub>CCIO</sub>              | Optional            |

| 3    | nCEO             | Output        | _         | V <sub>ccio</sub>              | Optional, all modes |

| 3    | MSEL             | Input         | Yes       | V <sub>CCINT</sub>             | All modes           |

| 9    | TDO              | Output        | Yes       | V <sub>CCIO</sub>              | JTAG                |

| 6    | DEV_OE           | Input         | _         | V <sub>CCIO</sub>              | Optional            |

| 6    | DEV_CLRn         | Input         | _         | V <sub>CCIO</sub>              | Optional            |

#### Notes to Table 8-18:

- (1) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

- (2) To tri-state AS configuration pins in the AS configuration scheme, turn on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

Table 8–19. Configuration Pin Summary for Cyclone IV E Devices (Part 1 of 3)

| Bank | Description               | Input/Output | Dedicated | Powered By                     | Configuration Mode  |

|------|---------------------------|--------------|-----------|--------------------------------|---------------------|

| 1    | nCSO (1)<br>FLASH_nCE (2) | Output       | _         | V <sub>CCIO</sub>              | AS, AP              |

| 6    | CRC_ERROR (3)             | Output       | _         | V <sub>CCIO</sub> /Pull-up (4) | Optional, all modes |

Table 8–19. Configuration Pin Summary for Cyclone IV E Devices (Part 3 of 3)

| Bank | Description | Input/Output | Dedicated | Powered By        | Configuration Mode |

|------|-------------|--------------|-----------|-------------------|--------------------|

| 5    | DEV_CLRn    | Input        | 1         | V <sub>CCIO</sub> | Optional, AP       |

#### Notes to Table 8-19:

- (1) To tri-state AS configuration pins in the AS configuration scheme, turn-on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, nCSO, Data[0], and Data[1]/ASDO pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

- (2) To tri-state AP configuration pins in the AP configuration scheme, turn-on the **Enable input tri-state on active configuration pins in user mode** option from the **Device and Pin Options** dialog box. This tri-states DCLK, Data[0..15], FLASH\_nCE, and other AP pins. Dual-purpose pins settings for these pins are ignored. To set these pins to different settings, turn off the **Enable input tri-state on active configuration pins in user mode** option and set the desired setting from the Dual-purpose Pins Setting menu.

- (3) The CRC\_ERROR pin is not available in Cyclone IV E devices with 1.0-V core voltage.

- (4) The CRC\_ERROR pin is a dedicated open-drain output or an optional user I/O pin. Active high signal indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled in the Quartus II software from the Error Detection CRC tab of the Device and Pin Options dialog box. When using this pin, connect it to an external 10-kΩ pull-up resistor to an acceptable voltage that satisfies the input voltage of the receiving device.

Table 8–20 describes the dedicated configuration pins. You must properly connect these pins on your board for successful configuration. You may not need some of these pins for your configuration schemes.

Table 8-20. Dedicated Configuration Pins on the Cyclone IV Device (Part 1 of 4)

| Pin Name | User Mode | Configuration<br>Scheme | Pin Type                    | Description                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|-------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSEL     | N/A       | All                     | Input                       | Configuration input that sets the Cyclone IV device configuration scheme. You must hardwire these pins to $V_{CCA}$ or GND. The MSEL pins have internal 9-k $\Omega$ pull-down resistors that are always active.                                                                                                                                                                         |

| nCONFIG  | N/A       | All                     | Input                       | Configuration control input. Pulling this pin low with external circuitry during user mode causes the Cyclone IV device to lose its configuration data, enter a reset state, and tri-state all I/O pins. Returning this pin to a logic-high level starts a reconfiguration.                                                                                                              |

|          |           |                         |                             | The Cyclone IV device drives nstatus low immediately after power-up and releases it after the POR time.  Status output—if an error occurs during configuration, nstatus is pulled low by the target device.                                                                                                                                                                              |

| nSTATUS  | N/A       | All                     | Bidirectional<br>open-drain | ■ Status input—if an external source (for example, another Cyclone IV device) drives the nstatus pin low during configuration or initialization, the target device enters an error state.                                                                                                                                                                                                |

|          |           |                         |                             | Driving nSTATUS low after configuration and initialization does not affect the configured device. If you use a configuration device, driving nSTATUS low causes the configuration device to attempt to configure the device, but because the device ignores transitions on nSTATUS in user mode, the device does not reconfigure. To start a reconfiguration, you must pull nCONFIG low. |

- External configuration reset (nCONFIG) assertion

- User watchdog timer time out

Table 8–24 lists the contents of the current state logic in the status register, when the remote system upgrade master state machine is in factory configuration or application configuration accessing the factory information or application information, respectively. The status register bit in Table 8–24 lists the bit positions in a 32-bit logic.

Table 8-24. Remote System Upgrade Current State Logic Contents In Status Register

| Remote System Upgrade<br>Master State Machine | Status<br>Register Bit | Definition                         | Description                                                                                                                       |

|-----------------------------------------------|------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                               | 31:30                  | Master state machine current state | The current state of the remote system upgrade master state machine                                                               |

| Factory information (1)                       | 29:24                  | Reserved bits                      | Padding bits that are set to all 0's                                                                                              |

| Table 17 miles markets                        | 23:0                   | Boot address                       | The current 24-bit boot address that was used by the configuration scheme as the start address to load the current configuration. |

| Application information 1 (2)                 | 31:30                  | Master state machine current state | The current state of the remote system upgrade master state machine                                                               |

|                                               | 29                     | User watchdog timer enable bit     | The current state of the user watchdog enable, which is active high                                                               |

|                                               | 28:0                   | User watchdog timer time-out value | The current entire 29-bit watchdog time-out value.                                                                                |

|                                               | 31:30                  | Master state machine current state | The current state of the remote system upgrade master state machine                                                               |

| Application information 2 (2)                 | 29:24                  | Reserved bits                      | Padding bits that are set to all 0's                                                                                              |

|                                               | 23:0                   | Boot address                       | The current 24-bit boot address that was used as the start address to load the current configuration                              |

#### Notes to Table 8-24:

- (1) The remote system upgrade master state machine is in factory configuration.

- (2) The remote system upgrade master state machine is in application configuration.

The previous two application configurations are available in the previous state registers (previous state register 1 and previous state register 2), but only for debugging purposes.

May 2013 Altera Corporation

# **Transmitter Output Buffer**

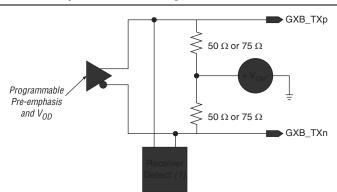

Figure 1–11 shows the transmitter output buffer block diagram.

Figure 1–11. Transmitter Output Buffer Block Diagram

#### Note to Figure 1-11:

Receiver detect function is specific for PCle protocol implementation only. For more information, refer to "PCl Express (PIPE) Mode" on page 1–52.

The Cyclone IV GX transmitter output buffers support the **1.5-V PCML** I/O standard and are powered by VCCH\_GXB power pins with 2.5-V supply. The 2.5-V supply on VCCH\_GXB pins are regulated internally to 1.5-V for the transmitter output buffers. The transmitter output buffers support the following additional features:

- Programmable differential output voltage  $(V_{OD})$ —customizes the  $V_{OD}$  up to 1200 mV to handle different trace lengths, various backplanes, and various receiver requirements.

- Programmable pre-emphasis—boosts high-frequency components in the transmitted signal to maximize the data eye opening at the far-end. The high-frequency components might be attenuated in the transmission media due to data-dependent jitter and intersymbol interference (ISI) effects. The requirement for pre-emphasis increases as the data rates through legacy backplanes increase.

- Programmable differential on-chip termination (OCT)—provides calibrated OCT at differential  $100~\Omega$  or  $150~\Omega$  with on-chip transmitter common mode voltage ( $V_{CM}$ ) at 0.65~V.  $V_{CM}$  is tri-stated when you disable the OCT to use external termination.

- Disable OCT to use external termination if the link requires a 85  $\Omega$  termination, such as when you are interfacing with certain PCIe Gen1 or Gen2 capable devices.

- The Cyclone IV GX transmitter output buffers are current-mode drivers. The resulting  $V_{OD}$  voltage is therefore a function of the transmitter termination value. For lists of supported  $V_{OD}$  settings, refer to the *Cyclone IV Device Data Sheet*.

Actual lock time depends on the transition density of the incoming data and the ppm difference between the receiver input reference clock and the upstream transmitter reference clock.

Transition from the LTD state to the LTR state occurs when either of the following conditions is met:

- Signal detection circuitry indicates the absence of valid signal levels at the receiver input buffer. This condition is valid for PCI Express (PIPE) mode only. CDR transitions are not dependent on signal detection circuitry in other modes.

- The recovered clock is not within the configured ppm frequency threshold setting with respect to CDR clocks from multipurpose PLLs.

In automatic lock mode, the switch from LTR to LTD states is indicated by the assertion of the rx\_freqlocked signal and the switch from LTD to LTR states indicated by the de-assertion of the rx\_freqlocked signal.

#### **Manual Lock Mode**

State transitions are controlled manually by using rx\_locktorefclk and rx\_locktodata ports. The LTR/LTD controller sets the CDR state depending on the logic level on the rx\_locktorefclk and rx\_locktodata ports. This mode provides the flexibility to control the CDR for a reduced lock time compared to the automatic lock mode. In automatic lock mode, the LTR/LTD controller relies on the ppm detector and the phase relationship detector to set the CDR in LTR or LTD mode. The ppm detector and phase relationship detector reaction times can be too long for some applications that require faster CDR lock time.

In manual lock mode, the rx\_freqlocked signal is asserted when the CDR is in LTD state and de-asserted when CDR is in LTR state. For descriptions of rx\_locktorefclk and rx\_locktodata port controls, refer to Table 1–27 on page 1–87.

The recommended transceiver reset sequence varies depending on the CDR lock mode. For more information about the reset sequence recommendations, refer to the *Reset Control and Power Down for Cyclone IV GX Devices* chapter.

## **Deserializer**

The deserializer converts received serial data from the receiver input buffer to parallel 8- or 10-bit data. Serial data is assumed to be received from the LSB to the MSB. The deserializer operates with the high-speed recovered clock from the CDR with the frequency at half of the serial data rate.

# **Transceiver Clocking Architecture**

The multipurpose PLLs and general-purpose PLLs located on the left side of the device generate the clocks required for the transceiver operation. The following sections describe the Cyclone IV GX transceiver clocking architecture:

- "Input Reference Clocking" on page 1–27

- "Transceiver Channel Datapath Clocking" on page 1–29

- "FPGA Fabric-Transceiver Interface Clocking" on page 1–43

# **Input Reference Clocking**

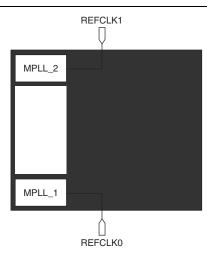

When used for transceiver, the left PLLs synthesize the input reference clock to generate the required clocks for the transceiver channels. Figure 1–25 and Figure 1–26 show the sources of input reference clocks for PLLs used in the transceiver operation.

Clock output from PLLs in the FPGA core cannot feed into PLLs used by the transceiver as input reference clock.

Figure 1–25. PLL Input Reference Clocks in Transceiver Operation for F324 and Smaller Packages  $^{(1)}$ ,  $^{(2)}$

#### Notes to Figure 1-25:

- The REFCLKO and REFCLK1 pins are dual-purpose CLK, REFCLK, or DIFFCLK pins that reside in banks 3A and 8A

respectively.

- (2) Using any clock input pins other than the designated REFCLK pins as shown here to drive the MPLLs may have reduced jitter performance.

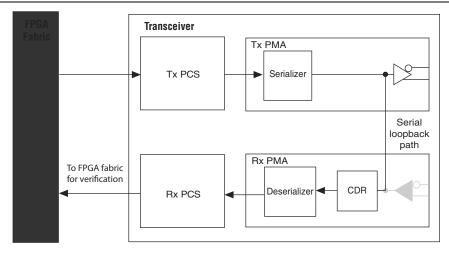

Serial loopback mode can only be dynamically enabled or disabled during user mode by performing a dynamic channel reconfiguration.

Figure 1–71. Serial Loopback Path (1)

#### Note to Figure 1-71:

(1) Grayed-Out Blocks are Not Active in this mode.

# **Reverse Serial Loopback**

The reverse serial loopback mode is available for all functional modes except for XAUI mode. The two reverse serial loopback options from the receiver to the transmitter are:

- Pre-CDR mode where data received through the RX input buffer is looped back to the TX output buffer using the Reverse serial loopback (pre-CDR) option

- Post-CDR mode where retimed data through the receiver CDR from the RX input buffer is looped back to the TX output buffer using the **Reverse serial loopback** option

The received data is also available to the FPGA logic. In the transmitter channel, only the transmitter buffer is active.

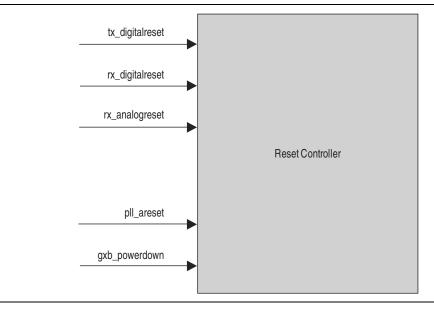

# 2. Cyclone IV Reset Control and Power Down

#### CYIV-52002-1.4

Cyclone<sup>®</sup> IV GX devices offer multiple reset signals to control transceiver channels independently. The ALTGX Transceiver MegaWizard<sup>™</sup> Plug-In Manager provides individual reset signals for each channel instantiated in your design. It also provides one power-down signal for each transceiver block.

This chapter includes the following sections:

- "User Reset and Power-Down Signals" on page 2–2

- "Transceiver Reset Sequences" on page 2–4

- "Dynamic Reconfiguration Reset Sequences" on page 2–19

- "Power Down" on page 2–21

- "Simulation Requirements" on page 2–22

- "Reference Information" on page 2–23

Figure 2–1 shows the reset control and power-down block for a Cyclone IV GX device.

Figure 2-1. Reset Control and Power-Down Block

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **All Supported Functional Modes Except the PCIe Functional Mode**

This section describes reset sequences for transceiver channels in bonded and non-bonded configurations. Timing diagrams of some typical configurations are shown to facilitate proper reset sequence implementation. In these functional modes, you can set the receiver CDR either in automatic lock or manual lock mode.

In manual lock mode, the receiver CDR locks to the reference clock (lock-to-reference) or the incoming serial data (lock-to-data), depending on the logic levels on the rx\_locktorefclk and rx\_locktodata signals. With the receiver CDR in manual lock mode, you can either configure the transceiver channels in the Cyclone IV GX device in a non-bonded configuration or a bonded configuration. In a bonded configuration, for example in XAUI mode, four channels are bonded together.

Table 2–4 lists the lock-to-reference (LTR) and lock-to-data (LTD) controller lock modes for the rx locktorefclk and rx locktodata signals.

Table 2-4. Lock-To-Reference and Lock-To-Data Modes

| rx_locktorefclk | rx_locktodata | LTR/LTD Controller Lock Mode |

|-----------------|---------------|------------------------------|

| 1               | 0             | Manual, LTR Mode             |

| _               | 1             | Manual, LTD Mode             |

| 0               | 0             | Automatic Lock Mode          |

# **Bonded Channel Configuration**

In a bonded channel configuration, you can reset all the bonded channels simultaneously. Examples of bonded channel configurations are the XAUI, PCIe Gen1 ×2 and ×4, and Basic ×2 and ×4 functional modes. In Basic ×2 and ×4 functional mode, you can bond **Transmitter Only** channels together.

In XAUI mode, the receiver and transmitter channels are bonded. Each of the receiver channels in this mode has its own rx\_freqlocked output status signals. You must consider the timing of these signals in the reset sequence.

Table 2–5 lists the reset and power-down sequences for bonded configurations under the stated functional modes.

Table 2–5. Reset and Power-Down Sequences for Bonded Channel Configurations

| Channel Set Up Receiver CDR Mode |                                           | Refer to                                                                              |

|----------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|

| Transmitter Only                 | Basic ×2 and ×4                           | "Transmitter Only Channel" on page 2–7                                                |

| Receiver and Transmitter         |                                           | "Receiver and Transmitter Channel—Receiver<br>CDR in Automatic Lock Mode" on page 2–8 |

| Receiver and Transmitter         | Manual lock mode for XAUI functional mode | "Receiver and Transmitter Channel—Receiver<br>CDR in Manual Lock Mode" on page 2–9    |

# **Dynamic Reconfiguration Controller Port List**

Table 3–2 lists the input control ports and output status ports of the dynamic reconfiguration controller.

Table 3–2. Dynamic Reconfiguration Controller Port List (ALTGX\_RECONFIG Instance) (Part 1 of 7)

| Port Name              | Input/<br>Output | Description                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Clock Inputs to ALTGX_ | RECONFIG         | Instance                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                        |                  | The frequency range of this clock depends on the following transceiver channel configuration modes:                                                                                                                                                                                                 |  |  |  |  |  |

|                        |                  | Receiver only (37.5 MHz to 50 MHz)                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| reconfig_clk           | Input            | Receiver and Transmitter (37.5 MHz to 50 MHz)                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                        |                  | ■ Transmitter only (2.5 MHz to 50 MHz)  By default, the Quartus <sup>®</sup> II software assigns a global clock resource to this port. This clock must be a free-running clock sourced from an I/O clock pin. Do not use dedicated transceiver REFCLK pins or any clocks generated by transceivers. |  |  |  |  |  |

| ALTGX and ALTGX_RECO   | NFIG Inte        |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ALTUA dilu ALTUA_IILU  |                  | An output port in the ALTGX instance and an input port in the ALTGX_RECONFIG instance. This signal is transceiver-block based. Therefore, the width of this signal increases in steps of 5 bits per transceiver block.                                                                              |  |  |  |  |  |

|                        |                  | In the ALTGX MegaWizard Plug-In Manager, the width of this signal depends on the number of channels you select in the <b>What is the number of channels?</b> option in the <b>General</b> screen.                                                                                                   |  |  |  |  |  |

|                        |                  | For example, if you select the number of channels in the ALTGX instance as follows:                                                                                                                                                                                                                 |  |  |  |  |  |

|                        |                  | $1 \le \text{Channels} \le 4$ , then the output port reconfig_fromgxb [40] = 5 bits                                                                                                                                                                                                                 |  |  |  |  |  |

|                        |                  | $5 \le \text{Channels} \le 8$ , then the output port reconfig_fromgxb[90] = 10 bits                                                                                                                                                                                                                 |  |  |  |  |  |

|                        |                  | $9 \le \text{Channels} \le 12$ , then the output port reconfig_fromgxb[140] = 15 bits                                                                                                                                                                                                               |  |  |  |  |  |

| reconfig_fromgxb       | Input            | $13 \le \text{Channels} \le 16$ , then the output port reconfig_fromgx[190] = 20 bits                                                                                                                                                                                                               |  |  |  |  |  |

| [n0]                   | IIIput           | To connect the reconfig_fromgxb port between the ALTGX_RECONFIG instance and multiple ALTGX instances, follow these rules:                                                                                                                                                                          |  |  |  |  |  |

|                        |                  | ■ Connect the reconfig_fromgxb[40] of ALTGX Instance 1 to the reconfig_fromgxb[40] of the ALTGX_RECONFIG instance. Connect the reconfig_fromgxb[] port of the next ALTGX instance to the next available bits of the ALTGX_RECONFIG instance, and so on.                                             |  |  |  |  |  |

|                        |                  | ■ Connect the reconfig_fromgxb port of the ALTGX instance, which has the highest What is the starting channel number? option, to the MSB of the reconfig_fromgxb port of the ALTGX_RECONFIG instance.                                                                                               |  |  |  |  |  |

|                        |                  | The Quartus II Fitter produces a warning if the dynamic reconfiguration option is enabled in the ALTGX instance but the reconfig_fromgxb and reconfig_togxb ports are not connected to the ALTGX_RECONFIG instance.                                                                                 |  |  |  |  |  |

| reconfig_togxb [30]    | Output           | An input port of the ALTGX instance and an output port of the ALTGX_RECONFIG instance. You must connect the reconfig_togxb[30] input port of every ALTGX instance controlled by the dynamic reconfiguration controller to the reconfig_togxb[30] output port of the ALTGX_RECONFIG instance.        |  |  |  |  |  |

|                        |                  | The width of this port is always fixed to 4 bits.                                                                                                                                                                                                                                                   |  |  |  |  |  |

Cyclone IV E industrial devices I7 are offered with extended operating temperature range.

# **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Cyclone IV devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied at these conditions. Table 1–1 lists the absolute maximum ratings for Cyclone IV devices.

Conditions beyond those listed in Table 1–1 cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time have adverse effects on the device.

Table 1–1. Absolute Maximum Ratings for Cyclone IV Devices (1)

| Symbol                | Parameter                                                                                                     | Min  | Max  | Unit |

|-----------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>CCINT</sub>    | Core voltage, PCI Express® (PCIe®) hard IP block, and transceiver physical coding sublayer (PCS) power supply | -0.5 | 1.8  | V    |

| V <sub>CCA</sub>      | Phase-locked loop (PLL) analog power supply                                                                   | -0.5 | 3.75 | V    |

| V <sub>CCD_PLL</sub>  | PLL digital power supply                                                                                      | -0.5 | 1.8  | V    |

| V <sub>CCIO</sub>     | I/O banks power supply                                                                                        | -0.5 | 3.75 | V    |

| V <sub>CC_CLKIN</sub> | Differential clock input pins power supply                                                                    | -0.5 | 4.5  | V    |

| V <sub>CCH_GXB</sub>  | Transceiver output buffer power supply                                                                        | -0.5 | 3.75 | V    |

| V <sub>CCA_GXB</sub>  | Transceiver physical medium attachment (PMA) and auxiliary power supply                                       | -0.5 | 3.75 | V    |

| V <sub>CCL_GXB</sub>  | Transceiver PMA and auxiliary power supply                                                                    | -0.5 | 1.8  | V    |

| VI                    | DC input voltage                                                                                              | -0.5 | 4.2  | V    |

| I <sub>OUT</sub>      | DC output current, per pin                                                                                    | -25  | 40   | mA   |

| T <sub>STG</sub>      | Storage temperature                                                                                           | -65  | 150  | °C   |

| T <sub>J</sub>        | Operating junction temperature                                                                                | -40  | 125  | °C   |

#### Note to Table 1-1:

# **Maximum Allowed Overshoot or Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 1–2 and undershoot to -2.0 V for a magnitude of currents less than 100 mA and for periods shorter than 20 ns. Table 1-2 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage over the lifetime of the device. The maximum allowed overshoot duration is specified as a percentage of high-time over the lifetime of the device.

<sup>(1)</sup> Supply voltage specifications apply to voltage readings taken at the device pins with respect to ground, not at the power supply.

| Symbol               | Parameter                                                   | Conditions                        | Min   | Тур | Max               | Unit |

|----------------------|-------------------------------------------------------------|-----------------------------------|-------|-----|-------------------|------|

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                  | _                                 | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                  | _                                 | 1.16  | 1.2 | 1.24              | V    |

| V <sub>I</sub>       | DC input voltage                                            | _                                 | -0.5  |     | 3.6               | V    |

| V <sub>0</sub>       | DC output voltage                                           | _                                 | 0     | _   | V <sub>CCIO</sub> | V    |

| т                    | Operating junction temperature                              | For commercial use                | 0     | _   | 85                | °C   |

| T <sub>J</sub>       | Operating junction temperature                              | For industrial use                | -40   |     | 100               | °C   |

| t <sub>RAMP</sub>    | Power supply ramp time                                      | Standard power-on reset (POR) (7) | 50 μs | _   | 50 ms             | _    |

|                      |                                                             | Fast POR (8)                      | 50 μs | _   | 3 ms              | _    |

| I <sub>Diode</sub>   | Magnitude of DC current across PCI-clamp diode when enabled | _                                 | _     | _   | 10                | mA   |

#### Notes to Table 1-4:

- (1) All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (2) You must connect V<sub>CCD PLL</sub> to V<sub>CCINT</sub> through a decoupling capacitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up by V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 where I/O Banks 3 and 9 only support V<sub>CCIO</sub> of 1.5, 1.8, 2.5, 3.0, and 3.3 V. For fast passive parallel (FPP) configuration mode, the V<sub>CCIO</sub> level of I/O Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $V_{CC\_CLKIN}$  to 2.5 V if you use CLKIN as a high-speed serial interface (HSSI) refclk or as a DIFFCLK input.

- (6) The CLKIN pins in I/O Banks 3B and 8B can support single-ended I/O standard when the pins are used to clock left PLLs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and 200 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and 9 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

#### **ESD Performance**

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5 lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

Table 1-5. ESD for Cyclone IV Devices GPIOs and HSSI I/Os

| Symbol  | Parameter                                        | Passing Voltage | Unit |

|---------|--------------------------------------------------|-----------------|------|

| V       | ESD voltage using the HBM (GPIOs) <sup>(1)</sup> | ± 2000          | V    |

| VESDHBM | ESD using the HBM (HSSI I/Os) (2)                | ± 1000          | V    |

| V       | ESD using the CDM (GPIOs)                        | ± 500           | V    |

| VESDCDM | ESD using the CDM (HSSI I/Os) (2)                | ± 250           | V    |

#### Notes to Table 1-5:

- (1) The passing voltage for EP4CGX15 and EP4CGX30 row I/Os is ±1000V.

- (2) This value is applicable only to Cyclone IV GX devices.

## **DC** Characteristics

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

# **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1-6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                         | Conditions                                 | Device | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|--------------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current         | $V_I = 0 V \text{ to } V_{CCIOMAX}$        |        | -10 | _   | 10  | μΑ   |

| I <sub>OZ</sub> | Tristated I/O pin leakage current | $V_0 = 0 \text{ V to } V_{\text{CCIOMAX}}$ |        | -10 | _   | 10  | μΑ   |

#### Notes to Table 1-6:

- This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

- (2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

#### **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2) (1)

|                                            |                                                | V <sub>CCIO</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1.2                   |      | 1.5 |      | 1.8 |      | 2.5 |      | 3.0 |      | 3.3 |      | Unit |

|                                            |                                                | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μА   |

| Bus hold<br>low,<br>overdrive<br>current   | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | 125  | _   | 175  | _   | 200  | _   | 300  | _   | 500  | _   | 500  | μА   |

| Bus hold<br>high,<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | -125 | _   | -175 | —   | -200 | _   | -300 | —   | -500 | —   | -500 | μА   |

# **Document Revision History**

Table 1–47 lists the revision history for this chapter.

Table 1-47. Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2016 | 2.1     | Added note to Table 1–9 and Table 1–10.                                                                                                                                                                                |

| March 2016    | 2.0     | Updated note (5) in Table 1–21 to remove support for the N148 package.                                                                                                                                                 |

| October 2014  | 1.0     | Updated maximum value for V <sub>CCD_PLL</sub> in Table 1–1.                                                                                                                                                           |

| October 2014  | 1.9     | Removed extended temperature note in Table 1–3.                                                                                                                                                                        |

| December 2013 | 1.8     | Updated Table 1–21 by adding Note (15).                                                                                                                                                                                |

| May 2013      | 1.7     | Updated Table 1–15 by adding Note (4).                                                                                                                                                                                 |

|               |         | ■ Updated the maximum value for V <sub>I</sub> , V <sub>CCD_PLL</sub> , V <sub>CCIO</sub> , V <sub>CC_CLKIN</sub> , V <sub>CCH_GXB</sub> , and V <sub>CCA_GXB</sub> Table 1–1.                                         |

|               |         | ■ Updated Table 1–11 and Table 1–22.                                                                                                                                                                                   |

| October 2012  | 1.6     | ■ Updated Table 1–21 to include peak-to-peak differential input voltage for the Cyclone IV GX transceiver input reference clock.                                                                                       |

|               |         | ■ Updated Table 1–29 to include the typical DCLK value.                                                                                                                                                                |

|               |         | ■ Updated the minimum f <sub>HSCLK</sub> value in Table 1–31, Table 1–32, Table 1–33, Table 1–34, and Table 1–35.                                                                                                      |

|               |         | <ul> <li>Updated "Maximum Allowed Overshoot or Undershoot Voltage", "Operating<br/>Conditions", and "PLL Specifications" sections.</li> </ul>                                                                          |

| November 2011 | 1.5     | ■ Updated Table 1–2, Table 1–3, Table 1–4, Table 1–5, Table 1–8, Table 1–9, Table 1–15, Table 1–18, Table 1–19, and Table 1–21.                                                                                        |

|               |         | ■ Updated Figure 1–1.                                                                                                                                                                                                  |

|               |         | ■ Updated for the Quartus II software version 10.1 release.                                                                                                                                                            |

| December 2010 | 1.4     | ■ Updated Table 1–21 and Table 1–25.                                                                                                                                                                                   |

|               |         | ■ Minor text edits.                                                                                                                                                                                                    |

|               |         | Updated for the Quartus II software version 10.0 release:                                                                                                                                                              |

| 1.1. 0040     | 4.0     | ■ Updated Table 1–3, Table 1–4, Table 1–21, Table 1–25, Table 1–28, Table 1–30, Table 1–40, Table 1–41, Table 1–42, Table 1–43, Table 1–44, and Table 1–45.                                                            |

| July 2010     | 1.3     | ■ Updated Figure 1–2 and Figure 1–3.                                                                                                                                                                                   |

|               |         | <ul><li>Removed SW Requirement and TCCS for Cyclone IV Devices tables.</li></ul>                                                                                                                                       |

|               |         | ■ Minor text edits.                                                                                                                                                                                                    |

|               |         | Updated to include automotive devices:                                                                                                                                                                                 |

|               |         | <ul><li>Updated the "Operating Conditions" and "PLL Specifications" sections.</li></ul>                                                                                                                                |

| March 2010    | 1.2     | ■ Updated Table 1–1, Table 1–8, Table 1–9, Table 1–21, Table 1–26, Table 1–27, Table 1–31, Table 1–32, Table 1–33, Table 1–34, Table 1–35, Table 1–36, Table 1–37, Table 1–38, Table 1–40, Table 1–42, and Table 1–43. |

|               |         | ■ Added Table 1–5 to include ESD for Cyclone IV devices GPIOs and HSSI I/Os.                                                                                                                                           |

|               |         | <ul> <li>Added Table 1–44 and Table 1–45 to include IOE programmable delay for<br/>Cyclone IV E 1.2 V core voltage devices.</li> </ul>                                                                                 |

|               |         | ■ Minor text edits.                                                                                                                                                                                                    |